-

-

-

Design Resources

- Design & Development

- Featured Design Tools

- Partners

- Content & Training

-

Support

-

Support Forums

Get help from our expert Renesas technical staff and community.

- Technical Support

- Training & Events

- Quality & Packaging

-

Support Forums

-

Sample & Buy

-

Buy Direct from Renesas

Customers can now choose the convenience of buying direct from Renesas.

- Ordering Resources

-

Buy Direct from Renesas

Clock Jitter Attenuators, Jitter Cleaners

Renesas jitter attenuators make use of a low-jitter external reference and control circuitry to remove unwanted noise from one or more input clock signals. Different members of this category of products make use of VCXOs or simple crystals as this reference. Innovative techniques allow the use of fixed-frequency crystals rather than hard-to-find pullable crystal devices. In addition, the jitter attenuator products also include a frequency translation stage that allows the output frequency or frequencies to be different than the input frequency. This input-output frequency may be an integer or non-integer ratio depending on the device selected. Several devices within the family will allow multiple such ratios to be supported, resulting in multiple independent frequencies or even non-integer relationships between output frequencies.

The integration of a jitter attenuator and frequency translator simplifies the circuit and minimizes the bill-of-materials (BOM). Renesas' rich portfolio of jitter attenuators and frequency translators come in varying levels of performance, power, and programmability to address the needs of virtually any application. Renesas jitter attenuators support various single-ended and differential signaling levels such as LVCMOS, LVPECL, LVDS, HCSL, HSTL, or SSTL.

Customers looking for application-specific signal repeaters and retimers for PCIe, SAS/SATA, USB 3.0, and XAUI applications, please visit our Signal Integrity Products page.

What is a Jitter Cleaner?

A jitter cleaner (a.k.a. jitter attenuator) is a device that is used to reduce the magnitude of noise (jitter) on a given timing signal. Jitter can be described as the undesired deviation from an ideal periodic timing signal. Jitter is commonly observed in characteristics such as the phase, or amplitude of successive pulses, and/or changes in frequency over a given time frame. High levels of jitter often result from long traces, cabling, and noisy system environments. Excessive levels of Jitter cause undesired system behavior in high-performance applications. Renesas jitter cleaners (jitter attenuators) rely on stable reference sources and innovative control circuitry to lock on to the phase and average frequency of a noisy clock signal and then output a high-quality (low jitter) signal to be sourced to ‘downstream’ devices within the clock network.

Featured Products

Product Selection Table

Inputs (#) |

Input Type |

Product Category |

Diff. Outputs |

Outputs (#) |

Output Type |

Output Voltage (V) |

Input Freq (MHz) |

Phase Jitter Typ RMS (ps) |

Output Freq Range (MHz) |

Fractional Output Dividers (#) |

Core Voltage (V) |

Output Banks (#) |

Loop Bandwidth Range (Hz) |

Xtal Freq (KHz) |

Advanced Features |

Temp. Range |

Pkg. Dimensions (mm) |

Abs. Pull Range Min. (± PPM) |

Pkg. Type |

Lead Count (#) |

105°C Max. Case Temp. |

Price (USD) | 1ku |

|

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Part Number | |||||||||||||||||||||||

| FemtoClock™ 3 Ultra-Low Noise Jitter Attenuator and Multi-Frequency Clock Synthesizer | 3 | Crystal, LP-HCSL, LVCMOS, LVDS | FemtoClock 3 | 8, 12 | 16, 8 | LP-HCSL, LVCMOS, LVDS | 1.8, 2.5, 3.3 | 1 - 650 | 0.15 | 0.001 - 650 | 3 | 1.8, 2.5, 3.3 | 6, 8, 12 | Hitless Switching, JESD204B/C, Spread Spectrum | -40 to 85°C | 7.0 x 7.0 x 0.9, 9.0 x 9.0 x 0.9 | VFQFPN | 48, 64 | 15.33 | ||||

| Jitter Attenuator & FemtoClock NG® Multiplier | 2 | HCSL, LVDS, LVHSTL, LVPECL, SSTL | FemtoClock NG | 2 | LVPECL | 3.3 | 0.008 - 155.52 | 0.6 | 25 - 312.5 | 0 | 3.3 | 2 | 8 - 75 | 25000 | VCXO-based APLL | -40 to 85°C | 5.0 x 5.0 x 0.9 | 100 | VFQFPN | 32 | 28.85 | ||

| VCXO Jitter Attenuator & FemtoClock® Multiplier | 2 | HCSL, HSTL, LVDS, LVPECL, SSTL | FemtoClock NG | 2 | 2 | LVPECL | 3.3 | 0.008 - 155.52 | 0.3 | 25 - 312.5 | 0 | 3.3 | 2 | 0 - 75 | 25000 | VCXO-based APLL | -40 to 85°C | 5.0 x 5.0 x 0.9 | 50 | VFQFPN | 32 | ||

| System Synchronizer for IEEE 1588 - Eight Channels | 16 | HCSL, LVDS, LVHSTL, LVPECL, SSTL | IEEE 1588 | 12 | 24 | HSTL, LVCMOS, LVDS, LVHSTL, LVPECL, LVTTL | 1.2, 1.5, 1.8, 2.5, 3.3 | 0.0000005 - 1000 | 0.15 | 0.0000005 - 1000 | 8 | 2.5, 3.3 | 8 | 25 - 54 | -40 to 85°C | 10.0 x 10.0 x 1.2 | CABGA | 144 | 54.23 | ||||

| System Synchronizer for IEEE 1588 - Four Channels | 14 | HCSL, LVDS, LVHSTL, LVPECL, SSTL | IEEE 1588 | 8 | 16 | HSTL, LVCMOS, LVDS, LVHSTL, LVPECL, LVTTL | 1.2, 1.5, 1.8, 2.5, 3.3 | 0.0000005 - 1000 | 0.15 | 0.0000005 - 1000 | 4 | 2.5, 3.3 | 4 | 25 - 54 | -40 to 85°C | 10.0 x 10.0 x 1.0 | VFQFPN | 72 | 35.53 | ||||

| System Synchronizer for IEEE 1588 - Four Channels | 4 | HCSL, LVDS, LVHSTL, LVPECL, SSTL | IEEE 1588 | 4 | 8 | HSTL, LVCMOS, LVDS, LVHSTL, LVPECL, LVTTL | 1.2, 1.5, 1.8, 2.5, 3.3 | 0.0000005 - 1000 | 0.15 | 0.0000005 - 1000 | 4 | 2.5, 3.3 | 4 | 25 - 54 | -40 to 85°C | 7.0 x 7.0 x 0.8 | VFQFPN | 48 | 41.34 | ||||

| System Synchronizer for IEEE 1588 - Two Channels | 4 | HCSL, LVDS, LVHSTL, LVPECL, SSTL | IEEE 1588 | 4 | 8 | HSTL, LVCMOS, LVDS, LVHSTL, LVPECL, LVTTL | 1.2, 1.5, 1.8, 2.5, 3.3 | 0.0000005 - 1000 | 0.15 | 0.0000005 - 1000 | 4 | 2.5, 3.3 | 4 | 25 - 54 | -40 to 85°C | 7.0 x 7.0 x 0.8 | VFQFPN | 48 | |||||

| System Synchronizer for IEEE 1588 - Four Channels | 4 | HCSL, LVDS, LVHSTL, LVPECL, SSTL | IEEE 1588 | 12 | 24 | HSTL, LVCMOS, LVDS, LVHSTL, LVPECL, LVTTL | 1.2, 1.5, 1.8, 2.5, 3.3 | 0.0000005 - 1000 | 0.15 | 0.0000005 - 1000 | 4 | 2.5, 3.3 | 4 | 25 - 54 | -40 to 85°C | 7.0 x 7.0 x 0.8, 10.0 x 10.0 x 1.0 | VFQFPN | 72 | |||||

| Line Card Synchronizer for IEEE 1588 - Eight Channels | 16 | HCSL, LVDS, LVHSTL, LVPECL, SSTL | IEEE 1588 | 12 | 24 | HSTL, LVCMOS, LVDS, LVHSTL, LVPECL, LVTTL | 1.2, 1.5, 1.8, 2.5, 3.3 | 0.001 - 1000 | 0.15 | 0.0000005 - 1000 | 8 | 2.5, 3.3 | 8 | 25 - 54 | -40 to 85°C | 10.0 x 10.0 x 1.2 | CABGA | 144 | 43.8 | ||||

| Line Card Synchronizer for IEEE 1588 - Four Channels | 14 | HCSL, LVDS, LVHSTL, LVPECL, SSTL | IEEE 1588 | 8 | 16 | HSTL, LVCMOS, LVDS, LVHSTL, LVPECL, LVTTL | 1.2, 1.5, 1.8, 2.5, 3.3 | 0.001 - 1000 | 0.15 | 0.0000005 - 1000 | 4 | 2.5, 3.3 | 4 | 25 - 54 | -40 to 85°C | 10.0 x 10.0 x 1.0 | VFQFPN | 72 | 34.81 | ||||

| Line Card Synchronizer for IEEE 1588 - Four Channels | 4 | HCSL, LVDS, LVHSTL, LVPECL, SSTL | IEEE 1588 | 4 | 8 | HSTL, LVCMOS, LVDS, LVHSTL, LVPECL, LVTTL | 1.2, 1.5, 1.8, 2.5, 3.3 | 0.001 - 1000 | 0.15 | 0.0000005 - 1000 | 4 | 2.5, 3.3 | 4 | 25 - 54 | -40 to 85°C | 7.0 x 7.0 x 0.8 | VFQFPN | 48 | |||||

| Multichannel DPLL / DCO - Eight Channels | 16 | HCSL, LVDS, LVHSTL, LVPECL, SSTL | Clock Matrix | 12 | 24 | HSTL, LVCMOS, LVDS, LVHSTL, LVPECL, LVTTL | 1.2, 1.5, 1.8, 2.5, 3.3 | 0.001 - 1000 | 0.15 | 0.0000005 - 1000 | 8 | 2.5, 3.3 | 8 | 25 - 54 | -40 to 85°C | 10.0 x 10.0 x 1.2 | CABGA | 144 | 38.88 | ||||

| Multichannel DPLL / DCO - Four Channels | 14 | HCSL, LVDS, LVHSTL, LVPECL, SSTL | Clock Matrix | 8 | 16 | HSTL, LVCMOS, LVDS, LVHSTL, LVPECL, LVTTL | 1.2, 1.5, 1.8, 2.5, 3.3 | 0.001 - 1000 | 0.15 | 0.0000005 - 1000 | 4 | 2.5, 3.3 | 4 | 25 - 54 | -40 to 85°C | 10.0 x 10.0 x 1.0 | VFQFPN | 72 | 28.28 | ||||

| Multichannel DPLL / DCO - Four Channels | 4 | HCSL, LVDS, LVHSTL, LVPECL, SSTL | Clock Matrix | 4 | 8 | HSTL, LVCMOS, LVDS, LVHSTL, LVPECL, LVTTL | 1.2, 1.5, 1.8, 2.5, 3.3 | 0.001 - 1000 | 0.15 | 0.0000005 - 1000 | 4 | 2.5, 3.3 | 4 | 25 - 54 | -40 to 85°C | 7.0 x 7.0 x 0.8 | VFQFPN | 48 | 23.93 | ||||

| Multichannel DPLL / DCO - Four / Eight Channels | 8 | HCSL, LVDS, LVHSTL, LVPECL, SSTL | Clock Matrix | 12 | 24 | HSTL, LVCMOS, LVDS, LVHSTL, LVPECL, LVTTL | 1.2, 1.5, 1.8, 2.5, 3.3 | 0.001 - 1000 | 0.15 | 0.0000005 - 1000 | 8 | 2.5, 3.3 | 8 | 25 - 54 | -40 to 85°C | 10.0 x 10.0 x 1.0 | VFQFPN | 72 | 28.35 | ||||

| Multichannel DPLL / DCO - Two / Eight Channels | 4 | HCSL, LVDS, LVHSTL, LVPECL, SSTL | Clock Matrix | 12 | 24 | HSTL, LVCMOS, LVDS, LVHSTL, LVPECL, LVTTL | 1.2, 1.5, 1.8, 2.5, 3.3 | 0.001 - 1000 | 0.15 | 0.0000005 - 1000 | 8 | 2.5, 3.3 | 8 | 25 - 54 | -40 to 85°C | 10.0 x 10.0 x 1.0 | VFQFPN | 72 | |||||

| FemtoClock™ NG Universal Frequency Translator | 2 | HCSL, LVCMOS, LVDS, LVHSTL, LVPECL, LVTTL | FemtoClock NG | 4 | 4 | HCSL, LVCMOS, LVDS, LVPECL | 1.8, 2.5, 3.3 | 0.008 - 875 | 0.2 | 0.008 - 1000 | 3 | 2.5, 3.3 | 4 | 0.2 - 6400 | 10000 - 50000 | External Feedback, Fractional-N PLL, OTP and more... |

-40 to 85°C | 6.0 x 6.0 x 0.9 | VFQFPN | 40 | 9.551 | ||

| FemtoClock™ NG Universal Frequency Translator | 2 | HCSL, LVCMOS, LVDS, LVHSTL, LVPECL, LVTTL | FemtoClock NG | 4 | 4 | HCSL, LVCMOS, LVDS, LVPECL | 1.8, 2.5, 3.3 | 0.008 - 875 | 0.35 | 0.008 - 1000 | 3 | 2.5, 3.3 | 4 | 0.2 - 6400 | 10000 - 50000 | External Feedback, Fractional-N PLL, OTP and more... |

-40 to 85°C | 6.0 x 6.0 x 0.9 | VFQFPN | 40 | 6.081 | ||

| FemtoClock™ NG Universal Frequency Translator | 2 | HCSL, LVCMOS, LVDS, LVHSTL, LVPECL, LVTTL | FemtoClock NG | 4 | 4 | HCSL, LVCMOS, LVDS, LVPECL | 1.8, 2.5, 3.3 | 0.008 - 875 | 0.276 | 0.008 - 1000 | 0 | 2.5, 3.3 | 4 | 0.2 - 6400 | 10000 - 50000 | External Feedback, Fractional-N PLL, OTP and more... |

-40 to 85°C | 6.0 x 6.0 x 0.9 | VFQFPN | 40 | 5.795 | ||

| FemtoClock NG Universal Frequency Translator (2-in/1-PLL/8-out) | 2 | HCSL, LVCMOS, LVDS, LVHSTL, LVPECL, LVTTL | FemtoClock NG | 8 | 8 | LVCMOS, LVDS, LVPECL | 2.5, 3.3 | 0.008 - 875 | 0.27, 0.28 | 0.008 - 1000 | 2 | 2.5, 3.3 | 4 | 0.25 - 512 | 10000 - 40000 | External Feedback, Fractional-N PLL and more... |

-40 to 85°C | 8.0 x 8.0 x 0.85 | VFQFPN | 56 | 14.19 | ||

| FemtoClock NG Dual Universal Frequency Translator (4-in/2-PLL/8-out) | 4 | HCSL, LVCMOS, LVDS, LVHSTL, LVPECL, LVTTL | FemtoClock NG | 8 | 8 | LVCMOS, LVDS, LVPECL | 2.5, 3.3 | 0.008 - 875 | 0.26, 0.28 | 0.008 - 1000 | 2 | 2.5, 3.3 | 4 | 0.25 - 512 | 10000 - 40000 | External Feedback, Fractional-N PLL, Programmable Clock and more... |

-40 to 85°C | 10.0 x 10.0 x 1.0 | VFQFPN | 72 | 29.23 | ||

| FemtoClock NG Dual Universal Frequency Translator (2-in/2-PLL/8-out) | 2 | HCSL, LVCMOS, LVDS, LVHSTL, LVPECL, LVTTL | FemtoClock NG | 8 | 8 | LVCMOS, LVDS, LVPECL | 2.5, 3.3 | 0.008 - 875 | 0.24, 0.28 | 0.008 - 1000 | 2 | 2.5, 3.3 | 4 | 0.25 - 512 | 10000 - 40000 | External Feedback, Fractional-N PLL, Programmable Clock and more... |

-40 to 85°C | 8.0 x 8.0 x 0.85 | VFQFPN | 56 | 23.46 | ||

| FemtoClock NG Universal Frequency Translator (2-in/1-PLL/8-out) | 2 | HCSL, LVCMOS, LVDS, LVHSTL, LVPECL | FemtoClock NG | 8 | 8 | HCSL, LVCMOS, LVDS, LVPECL | 1.8, 2.5, 3.3 | 0.008 - 875 | 0.28 | 0.008 - 1000 | 2 | 2.5, 3.3 | 4 | 0.25 - 512 | 10000 - 40000 | External Feedback, Fractional-N PLL and more... |

-40 to 85°C | 8.0 x 8.0 x 0.85 | VFQFPN | 56 | 9.973 | ||

| FemtoClock NG Universal Frequency Translator (4-in/2-PLL/8-out) | 4 | HCSL, LVCMOS, LVDS, LVHSTL, LVPECL, LVTTL | FemtoClock NG | 8 | 8 | HCSL, LVCMOS, LVDS, LVPECL | 2.5, 3.3 | 0.008 - 875 | 0.28 | 0.008 - 1000 | 2 | 2.5, 3.3 | 4 | 0.5 - 360 | 10000 - 40000 | External Feedback, Fractional-N PLL and more... |

-40 to 85°C | 10.0 x 10.0 x 1.0 | VFQFPN | 72 | 12.73 | ||

| FemtoClock NG Universal Frequency Translator (2-in/2-PLL/8-out) | 2 | HCSL, LVCMOS, LVDS, LVHSTL, LVPECL, LVTTL | FemtoClock NG | 8 | 8 | HCSL, LVCMOS, LVDS, LVPECL | 2.5, 3.3 | 0.008 - 875 | 0.28 | 0.008 - 1000 | 2 | 2.5, 3.3 | 4 | 0.5 - 360 | 10000 - 40000 | External Feedback, Fractional-N PLL and more... |

-40 to 85°C | 8.0 x 8.0 x 0.85 | VFQFPN | 56 | 12.99 | ||

| FemtoClock NG Triple Universal Frequency Translator | 7 | HCSL, LVCMOS, LVDS, LVHSTL, LVPECL, LVTTL | FemtoClock NG | 6 | LVDS, LVPECL | 2.5 | 0.008 - 710 | 0.333 | 0.98 - 1300 | 0 | 2.5 | 3 | 10 - 580 | 16000 - 40000 | Fractional-N PLL, Smooth Reference Switching | -40 to 85°C | 10.0 x 10.0 x 1.4 | CABGA | 80 | 72.42 | |||

| Clock Jitter Attenuator | 2 | LVDS, LVPECL | FemtoClock 2 | 10 | LVDS, LVPECL | 1.8, 2.5, 3.3 | 0.008 - 307.2 | 0.073 | 15.36 - 2949.12 | 0 | 3.3 | 4 | 20 - 100 | 30720 - 250000 | Holdover, Input Switching, JESD204B, Phase Delay, Programmable Clock | -40 to 85°C | 8.0 x 8.0 x 1.35 | CABGA | 81 | ||||

| Clock Jitter Attenuator | 2 | LVDS, LVPECL | FemtoClock 2 | 11 | LVDS, LVPECL | 3.3 | 0.008 - 307.2 | 0.075 | 15.36 - 2949.12 | 1 | 3.3 | 5 | Holdover, Input Switching, Phase Delay, Programmable Clock | -40 to 85°C | 8.0 x 8.0 x 1.35 | CABGA | 81 | ||||||

| JESD204B/C Clock Jitter Attenuator | 2 | LVDS, LVPECL | FemtoClock 2 | 12 | LVDS, LVPECL | 3.3 | 0.008 - 250 | 0.075 | 15.625 - 2500 | 1 | 3.3 | 5 | Holdover, Input Switching, Phase Delay | -40 to 85°C | 8.0 x 8.0 x 1.35 | CABGA | 81 | 23.07 | |||||

| JESD204B/C Clock Jitter Attenuator | 4 | LVDS, LVPECL | JESD204B/C | 18 | LVDS, LVPECL | 3.3 | 30.72 - 500 | 0.075 | 20.48 - 1474.56 | 0 | 3.3 | 5 | 20 - 100 | 30720 - 250000 | Holdover, Input Switching, JESD204B, Phase Delay, Programmable Clock | -40 to 85°C | 11.0 x 11.0 x 1.2 | CABGA | 100 | ||||

| JESD204B/C Clock Jitter Attenuator | 4 | LVDS, LVPECL | JESD204B/C | 18 | LVDS, LVPECL | 3.3 | 1.92 - 2000 | 0.052 | 18.432 - 2949.12 | 0 | 3.3 | 5 | 20 - 100 | 30720 - 250000 | Holdover, Input Switching, JESD204B, Phase Delay, Programmable Clock | -40 to 85°C | 11.0 x 11.0 x 1.2 | CABGA | 100 | ||||

| JESD204B/C Clock Jitter Attenuator | 4 | LVDS, LVPECL | JESD204B/C | 18 | LVDS, LVPECL | 3.3 | 1.92 - 2000 | 0.057 | 12.288 - 1966.08 | 0 | 3.3 | 5 | 20 - 100 | 30720 - 250000 | Holdover, Input Switching, JESD204B, Phase Delay, Programmable Clock | -40 to 85°C | 11.0 x 11.0 x 1.2 | CABGA | 100 | ||||

| JESD204B/C Clock Jitter Attenuator | 4 | LVDS, LVPECL | JESD204B/C | 18 | LVDS, LVPECL | 3.3 | 1.92 - 2000 | 0.057 | 15.36 - 2457.6 | 0 | 3.3 | 5 | 20 - 100 | 30720 - 250000 | Holdover, Input Switching, JESD204B, Phase Delay, Programmable Clock | -40 to 85°C | 11.0 x 11.0 x 1.2 | CABGA | 100 | ||||

| JESD204B/C Clock Jitter Attenuator | 4 | LVDS, LVPECL | JESD204B/C | 18 | LVDS, LVPECL | 3.3 | 1.92 - 2000 | 0.052 | 18.432 - 2949.12 | 0 | 3.3 | 5 | 20 - 100 | 30720 - 250000 | Holdover, Input Switching, JESD204B, Phase Delay, Programmable Clock | -40 to 85°C | 11.0 x 11.0 x 1.2 | CABGA | 100 | ||||

| JESD204B/C Clock Jitter Attenuator | 4 | LVDS, LVPECL | JESD204B/C | 18 | LVDS, LVPECL | 3.3 | 1.92 - 2000 | 0.052 | 18.432 - 2949.12 | 0 | 3.3 | 5 | 20 - 100 | 30720 - 250000 | Holdover, Input Switching, JESD204B, Phase Delay, Programmable Clock | -40 to 85°C | 11.0 x 11.0 x 1.2 | CABGA | 100 | ||||

| JESD204B/C Clock Jitter Attenuator | 2 | LVDS, LVPECL | JESD204B/C | 15 | LVDS, LVPECL | 3.3 | 1.92 - 2000 | 0.061 | 12.288 - 2457.6 | 0 | 3.3 | 5 | 20 - 100 | 30720 - 491520 | Holdover, Input Switching, JESD204B, Phase Delay, Programmable Clock | -40 to 85°C | 10.0 x 10.0 x 0.9 | VFQFPN | 88 | ||||

| JESD204B/C Clock Jitter Attenuator | 4 | LVDS, LVPECL | JESD204B/C | 18 | LVDS, LVPECL | 3.3 | 30.72 - 2000 | 0.065 | 18.432 - 3686.4 | 0 | 3.3 | 5 | 20 - 100 | 30720 - 245760 | Holdover, Input Switching, JESD204B, Phase Delay, Programmable Clock | -40 to 85°C | 11.0 x 11.0 x 1.2 | CABGA | 100 | ||||

| JESD204B/C Clock Jitter Attenuator | 2 | LVDS, LVPECL | JESD204B/C | 15 | LVDS, LVPECL | 3.3 | 1.92 - 2000 | 0.063 | 18.432 - 2949.12 | 0 | 3.3 | 5 | 20 - 100 | 30720 - 250000 | Holdover, Input Switching, JESD204B, Phase Delay, Programmable Clock | -40 to 85°C | 10.0 x 10.0 x 0.9 | VFQFPN | 88 | 14.32 | |||

| JESD204B/C Clock Jitter Attenuator | 2 | LVDS, LVPECL | JESD204B/C | 15 | LVDS, LVPECL | 3.3 | 30.72 - 2000 | 0.046 | 19.6608 - 3932.16 | 0 | 3.3 | 5 | 20 - 100 | 30720 - 500000 | Holdover, Input Switching, JESD204B, Phase Delay, Programmable Clock | -40 to 85°C | 10.0 x 10.0 x 0.9 | VFQFPN | 88 | ||||

| FemtoClock™ NG 12-Output Clock Generator | 2 | Crystal, HCSL, HSTL, LVCMOS, LVDS, LVHSTL, LVPECL | FemtoClock 2 | 11 | 12 | HCSL | 3.3 | 5 - 1000 | 0.095 | 10.91 - 2500 | 3.3 | 4 | 0 - 50 | 12-Output Clock Generator with Four Dividers, Programmable Clock | -40 to 85°C | 9.0 x 9.0 x 0.9 | VFQFPN | 64 | |||||

| Synchronous Ethernet PLL | 3 | LVCMOS, LVDS, LVPECL | FemtoClock NG | 3 | LVCMOS, LVDS, LVPECL | 3.3 | 1 - 625 | 1 | 1 - 644.531 | 3 | 3.3 | 3 | 15 - 560 | 12800 | JTAG boundary scan, Microprocessor interface modes | 0 to 70°C | 10.0 x 10.0 x 1.0 | VFQFPN | 72 | 43.11 | |||

| VersaClock® 7 Programmable Jitter Attenuator Family | 2 | LP-HCSL, LVCMOS, LVDS | VersaClock | 8, 12, 5 | 16, 24 | LP-HCSL, LVCMOS, LVDS | 1.8, 2.5, 3.3 | 1 - 650 | 0.15 | 0.001 - 650 | 3 | 1.8, 2.5, 3.3 | 6 | Hitless Switching, JESD204B/C, Spread Spectrum | -40 to 85°C | 4.0 x 4.0 x 1.0, 5.0 x 5.0 x 1.7, 6.0 x 6.0 x 0.9 | LGA | 32, 40, 48 | |||||

| FemtoClock Jitter Attenuator or Clock Generator | 10 | HCSL, LVDS, LVHSTL, LVPECL, SSTL | FemtoClock NG | 12 | 24 | HSTL, LVCMOS, LVDS, LVHSTL, LVPECL, LVTTL | 1.2, 1.5, 1.8, 2.5, 3.3 | 0.001 - 1000 | 0.15 | 0.0000005 - 1000 | 6 | 2.5, 3.3 | 6 | 0.0001 - 12000 | 25 - 54 | 1PPS, DCO, IEEE 1588, JESD204B, JESD204C, PWM Encoder/Decoder and more... |

-40 to 85°C | 10.0 x 10.0 x 1.0 | VFQFPN | 72 | No | ||

| FemtoClock Jitter Attenuator or Clock Generator | -40 to 85°C | 10.0 x 10.0 x 1.0 | QFN, VFQFPN | 72 | |||||||||||||||||||

| FemtoClock™ 2 Jitter Attenuator or Clock Generator | 3 | Crystal, HCSL, LVCMOS, LVDS | FemtoClock 2 | 4 | 4 | HCSL, LVCMOS, LVDS | 1.8 | 5 - 1000 | 0.079 | 10 - 1000 | 1 | 1.8, 3.3 | 4 | 25 - 80 | 4-Output Jitter Attenuator or Clock Generator | -40 to 85°C | 4.0 x 4.0 x 0.8 | VFQFPN | 24 | 9.497 | |||

| FemtoClock 2 Jitter Attenuator or Clock Generator | 3 | Crystal, HCSL, LVCMOS, LVDS | FemtoClock 2 | 8 | 8 | HCSL, LVCMOS, LVDS | 1.8 | 1 - 800 | 0.067 | 10 - 1000 | 2 | 1.8, 3.3 | 8 | 0.1 - 12000 | 25 - 80 | 8-Output Jitter Attenuator and Clock Generator | -40 to 85°C | 7.0 x 7.0 x 0.9 | VFQFPN | 48 | No | ||

| FemtoClock™ 2 Jitter Attenuator or Clock Generator | 3 | Crystal, HCSL, LVCMOS, LVDS | FemtoClock 2 | 4 | 4 | HCSL, LVCMOS, LVDS | 1.8 | 1 - 800 | 0.079 | 10 - 1000 | 1 | 1.8, 3.3 | 4 | 4-Output Jitter Attenuator or Clock Generator | -40 to 85°C | 4.0 x 4.0 x 1.5 | VFQFPN | 28 | |||||

| System Synchronizer for IEEE 1588 - Six Channels | 8 | HCSL, LVDS, LVHSTL, LVPECL, SSTL | IEEE 1588 | 14 | 24 | HSTL, LVCMOS, LVDS, LVHSTL, LVPECL, LVTTL | 1.2, 1.5, 1.8, 2.5, 3.3 | 0.0000005 - 1000 | 0.1 | 0.0000005 - 1000 | 8 | 2.5, 3.3 | 8 | 25 - 54 | -40 to 85°C | 10.0 x 10.0 x 1.2 | CABGA | 144 | |||||

| Radio Access Network Equipment Synchronizer - Six Channels | 10 | HCSL, LVDS, LVHSTL, LVPECL, SSTL | Clock Matrix | 12 | 24 | HSTL, LVCMOS, LVDS, LVHSTL, LVPECL, LVTTL | 1.2, 1.5, 1.8, 2.5, 3.3 | 0.001 - 1000 | 0.15 | 0.0000005 - 1000 | 6 | 2.5, 3.3 | 6 | 0.0001 - 12000 | 25 - 54 | 1PPS, DCO, IEEE 1588, JESD204B, JESD204C, PWM Encoder/Decoder and more... |

-40 to 85°C | 10.0 x 10.0 x 1.0 | VFQFPN | 72 | No |

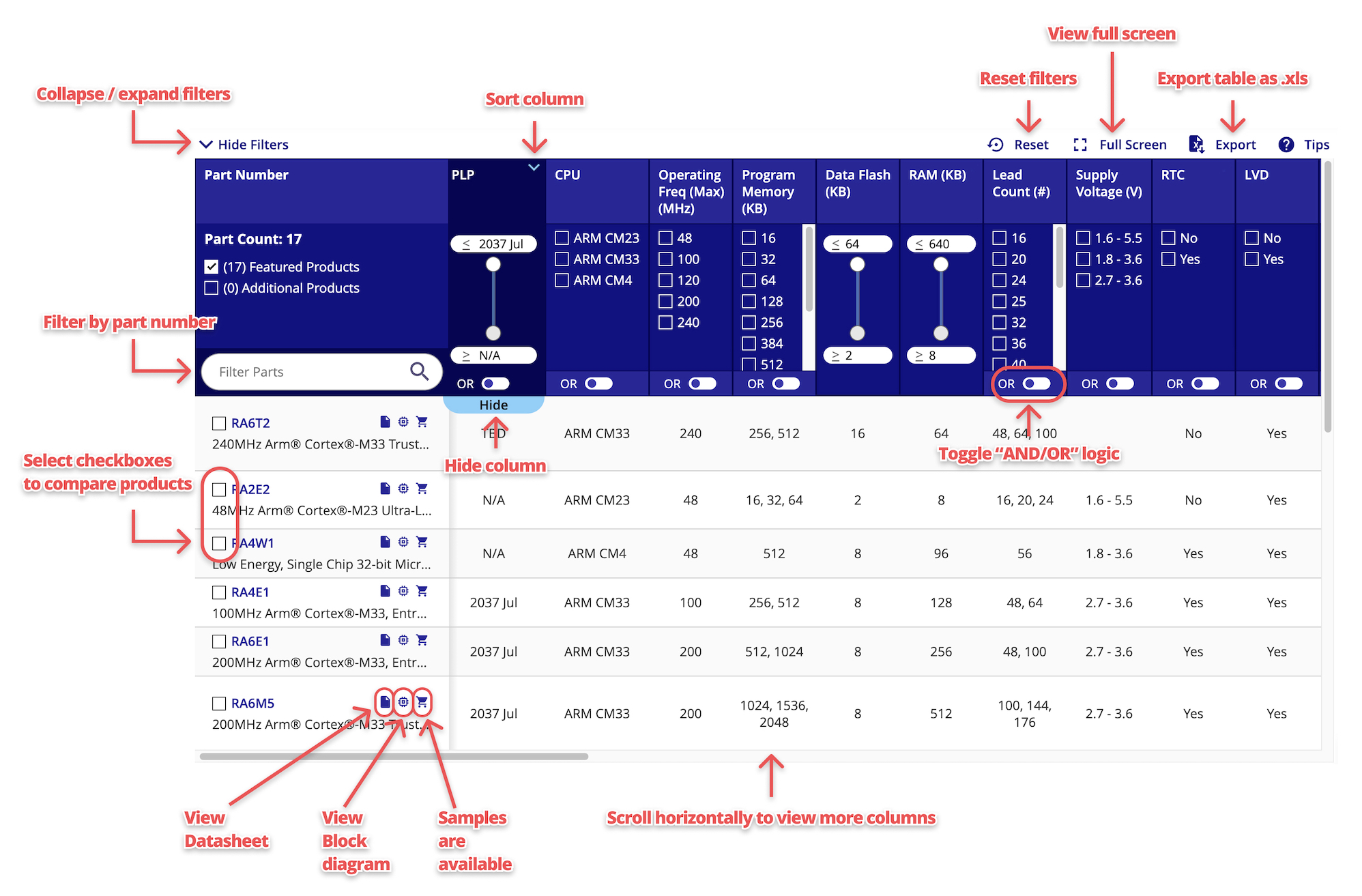

Tips for Using This Parametric Table:

- Hide Filters button in header: Collapse or expands filters

- Column sort buttons in header: Sort Column alphabetically / numerically descending or ascending

- Reset button in header: Reset all filters to the page default

- Full Screen button in header: Expand the table to full screen view (user must close out of full screen before they can interact with rest of page)

- Export button in header: Export the filtered results of the table to an Excel document

- Filter parts search bar in header: Type to filter table results by part number

- Hide column button in column headers: Select to hide columns in table

- AND / OR toggle switches in header: Toggles the logic of this particular filter to be “AND” or “OR” logic for filtering results

- Multiselect checkboxes at beginning of each row in table: Select these checkboxes to compare products against each other

- Document icon next to product name in row: View the featured document for this product

- Chip icon next to the right of the document icon in row: View the block diagram for this product

- Cart icon to the right of the chip icon: Indicates that samples are available for this product

Videos & Training

The ClockMatrix™ 2 family of devices are high-performance, precision timing solutions designed to simplify clock designs for applications with up to 800Gbps interface speeds. This second-generation family delivers improved performance with phase jitter as low as 88fs RMS. The highly integrated devices serve as full-function IEEE 1588 synchronization clocks and ultra-low jitter reference clocks for synchronous Ethernet PHYs with data rates up to 112Gbps PAM-4, reducing design complexity and bill of materials (BOM). Visit renesas.com/clockmatrix to learn more.