-

-

-

Design Resources

- Design & Development

- Featured Design Tools

- Partners

- Content & Training

-

Support

-

Support Forums

Get help from our expert Renesas technical staff and community.

- Technical Support

- Training & Events

- Quality & Packaging

-

Support Forums

-

Sample & Buy

-

Buy Direct from Renesas

Customers can now choose the convenience of buying direct from Renesas.

- Ordering Resources

-

Buy Direct from Renesas

8V89307

circleActiveSamples AvailableSynchronous Ethernet PLL

Overview

Description

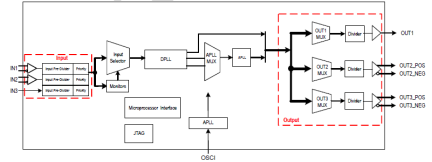

The 8V89307 is an integrated solution for the Synchronous Equipment Timing Source supporting EEC-Option1, EEC-Option2 clocks in Synchronous Ethernet equipment.

The device has a high quality DPLL to provide system clocks for node timing synchronization within a Synchronous Ethernet network. It also integrates an APLL for better jitter performance.

An input clock is automatically or manually selected. It supports three primary operating modes: Free-Run, Locked and Holdover. In Free-Run mode, the DPLL refers to the master clock. In Locked mode, the DPLL locks to the selected input clock. In Holdover mode, the DPLL resorts to the frequency data acquired in Locked mode. Whatever the operating mode is, the DPLL gives a stable performance without being affected by operating conditions or silicon process variations.

The device provides programmable DPLL bandwidths: 15mHz to 560Hz and damping factors: 1.2 to 20 in 5 steps. Different settings cover all clock synchronization requirements.

A stable oscillator is required for the master clock in different applications. The master clock is used as a reference clock for all the internal circuits in the device. It can be calibrated within ±741ppm.

All the read/write registers are accessed through a microprocessor interface. The device supports Serial and I2C interfaces.

Features

- Features 15mHz to 560Hz bandwidth

- Provides node clock for ITU-T G.8261/G.8262 Synchronous Ethernet (SyncE)

- Supports GR-253-CORE (OC-192) and ITU-T G.813 (STM-64) jitter generation requirements

- Provides clocks for 1 Gigabit and 10 Gigabit Ethernet applications

- 3.3V supply voltage

- -40°C to 85°C ambient operating temperature

- Available in lead-free (RoHS 6) package

Comparison

Applications

Design & Development

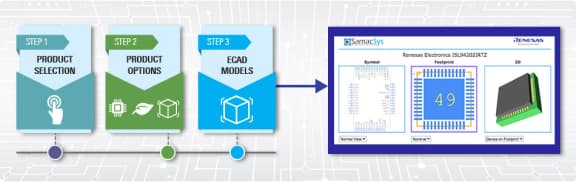

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.

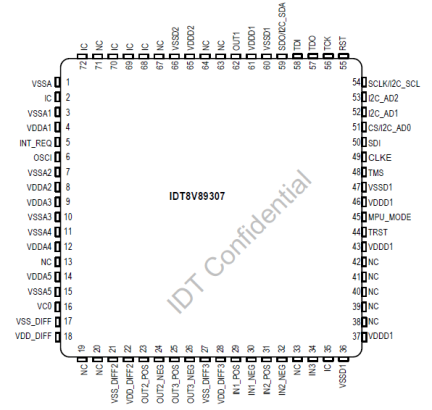

Product Options

Pkg. Type |

Lead Count (#) |

Temp. Grade |

Pb (Lead) Free |

Carrier Type |

Moisture Sensitivity Level (MSL) |

Price (USD) | 1ku |

Buy / Sample |

|

|---|---|---|---|---|---|---|---|---|

| Part Number | ||||||||

8V89307BNLG circleActive Samples Available |

VFQFPN | 72 | C | Yes | Tray | 3 | 43.11 | Get Samples, |

| VFQFPN | 72 | C | Yes | Reel | 3 |

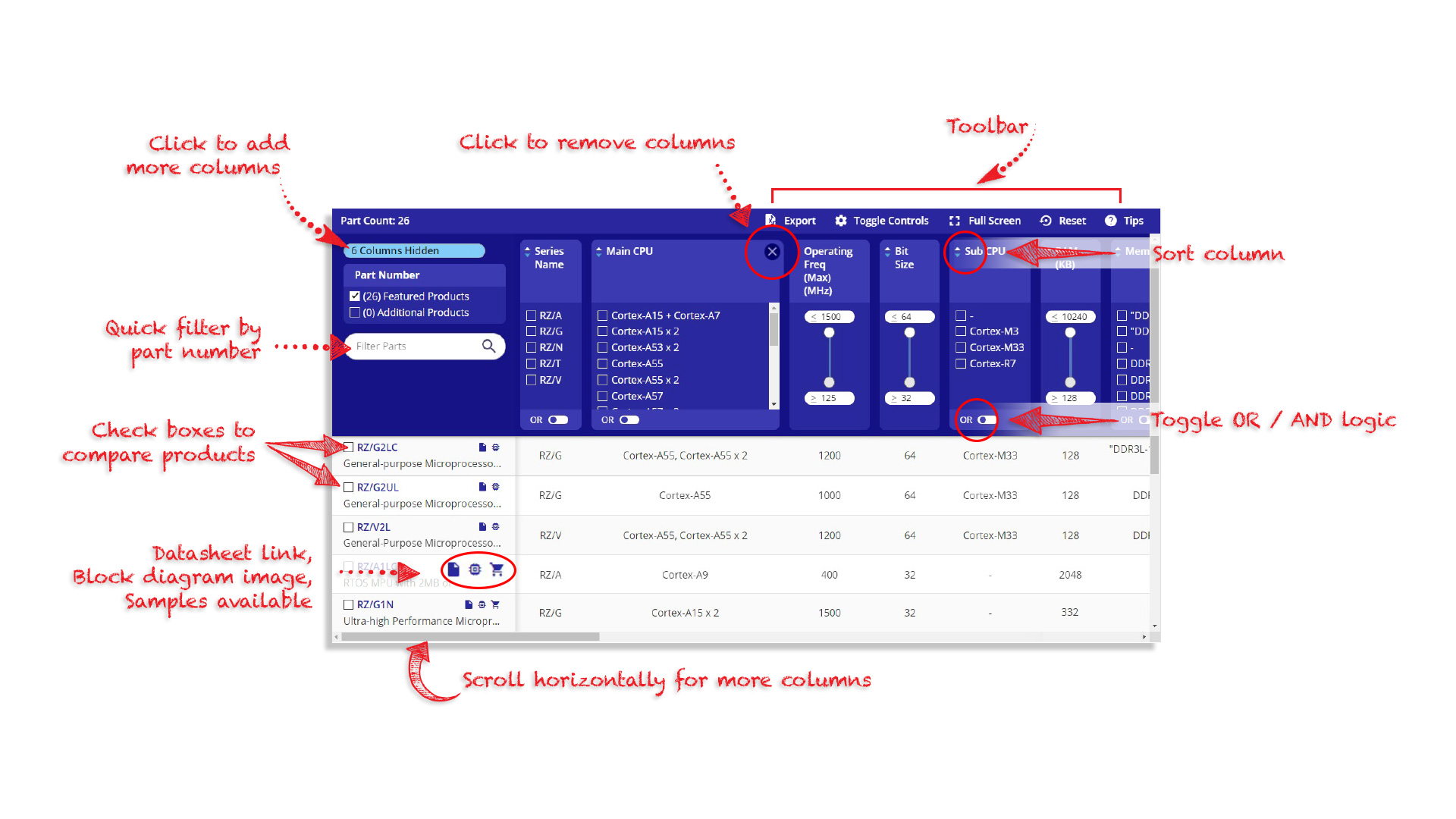

Tips for Using This Parametric Table:

- Hide Filters button in header: Collapse or expands filters

- Column sort buttons in header: Sort Column alphabetically / numerically descending or ascending

- Reset button in header: Reset all filters to the page default

- Full Screen button in header: Expand the table to full screen view (user must close out of full screen before they can interact with rest of page)

- Export button in header: Export the filtered results of the table to an Excel document

- Filter parts search bar in header: Type to filter table results by part number

- Hide column button in column headers: Select to hide columns in table

- AND / OR toggle switches in header: Toggles the logic of this particular filter to be “AND” or “OR” logic for filtering results

- Multiselect checkboxes at beginning of each row in table: Select these checkboxes to compare products against each other

- Document icon next to product name in row: View the featured document for this product

- Chip icon next to the right of the document icon in row: View the block diagram for this product

- Cart icon to the right of the chip icon: Indicates that samples are available for this product