# 关于产品目录等资料中的旧公司名称

NEC电子公司与株式会社瑞萨科技于2010年4月1日进行业务整合(合并),整合后的新公司暨"瑞萨电子公司"继承两家公司的所有业务。因此,本资料中虽还保留有旧公司名称等标识,但是并不妨碍本资料的有效性,敬请谅解。

瑞萨电子公司网址: http://www.renesas.com

2010年4月1日 瑞萨电子公司

【发行】瑞萨电子公司(http://www.renesas.com)

【业务咨询】http://www.renesas.com/inquiry

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# SH7203群

瑞萨32位RISC单片机

SuperH<sup>TM</sup> RISC engine族/SH7200系列

SH7203 R5S72030W200FP

#### Notes regarding these materials

- This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of Renesas or any third party with respect to the information in this document.

- 2. Renesas shall have no liability for damages or infringement of any intellectual property or other rights arising out of the use of any information in this document, including, but not limited to, product data, diagrams, charts, programs, algorithms, and application circuit examples.

- 3. You should not use the products or the technology described in this document for the purpose of military applications such as the development of weapons of mass destruction or for the purpose of any other military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations.

- 4. All information included in this document such as product data, diagrams, charts, programs, algorithms, and application circuit examples, is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas products listed in this document, please confirm the latest product information with a Renesas sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas such as that disclosed through our website. (http://www.renesas.com)

- 5. Renesas has used reasonable care in compiling the information included in this document, but Renesas assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the information included in this document.

- 6. When using or otherwise relying on the information in this document, you should evaluate the information in light of the total system before deciding about the applicability of such information to the intended application. Renesas makes no representations, warranties or guaranties regarding the suitability of its products for any particular application and specifically disclaims any liability arising out of the application and use of the information in this document or Renesas products.

- 7. With the exception of products specified by Renesas as suitable for automobile applications, Renesas products are not designed, manufactured or tested for applications or otherwise in systems the failure or malfunction of which may cause a direct threat to human life or create a risk of human injury or which require especially high quality and reliability such as safety systems, or equipment or systems for transportation and traffic, healthcare, combustion control, aerospace and aeronautics, nuclear power, or undersea communication transmission. If you are considering the use of our products for such purposes, please contact a Renesas sales office beforehand. Renesas shall have no liability for damages arising out of the uses set forth above.

- 8. Notwithstanding the preceding paragraph, you should not use Renesas products for the purposes listed below:

- (1) artificial life support devices or systems

- (2) surgical implantations

- (3) healthcare intervention (e.g., excision, administration of medication, etc.)

- (4) any other purposes that pose a direct threat to human life

- Renesas shall have no liability for damages arising out of the uses set forth in the above and purchasers who elect to use Renesas products in any of the foregoing applications shall indemnify and hold harmless Renesas Technology Corp., its affiliated companies and their officers, directors, and employees against any and all damages arising out of such applications.

- 9. You should use the products described herein within the range specified by Renesas, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas shall have no liability for malfunctions or damages arising out of the use of Renesas products beyond such specified ranges.

- 10. Although Renesas endeavors to improve the quality and reliability of its products, IC products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Please be sure to implement safety measures to guard against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other applicable measures. Among others, since the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 11. In case Renesas products listed in this document are detached from the products to which the Renesas products are attached or affixed, the risk of accident such as swallowing by infants and small children is very high. You should implement safety measures so that Renesas products may not be easily detached from your products. Renesas shall have no liability for damages arising out of such detachment.

- 12. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written approval from Renesas.

- 13. Please contact a Renesas sales office if you have any questions regarding the information contained in this document, Renesas semiconductor products, or if you have any other inquiries.

# 注意

本文只是参考译文,前页所载英文版"Cautions"具有正式效力。

#### 关于利用本资料时的注意事项

- 本资料是为了让用户根据用途选择合适的本公司产品的参考资料,对于本资料中所记载的技术信息,并非意味着对本公司或者第三者的知识产权及其他权利做出保证或对实施权力进行的承诺。

- 2. 对于因使用本资料所记载的产品数据、图、表、程序、算法及其他应用电路例而引起的损害或者对第三者的知识产权及其他权利造成侵犯,本公司不承担任何责任。

- 3. 不能将本资料所记载的产品和技术用于大规模破坏性武器的开发等目的、军事目的或其他的军需用途方面。 另外,在出口时必须遵守日本的《外汇及外国贸易法》及其他出口的相关法令并履行这些法令中规定的必要 手续。

- 4. 本资料所记载的产品数据、图、表、程序、算法以及其他应用电路例等所有信息均为本资料发行时的内容,本公司有可能在未做事先通知的情况下,对本资料所记载的产品或者产品规格进行更改。所以在购买和使用本公司的半导体产品之前,请事先向本公司的营业窗口确认最新的信息并经常留意本公司通过公司主页(http://www.renesas.com)等公开的最新信息。

- 对于本资料中所记载的信息,制作时我们尽力保证出版时的精确性,但不承担因本资料的叙述不当而致使顾客遭受损失等的任何相关责任。

- 6. 在使用本资料所记载的产品数据、图、表等所示的技术内容、程序、算法及其他应用电路例时,不仅要对所使用的技术信息进行单独评价,还要对整个系统进行充分的评价。请顾客自行负责,进行是否适用的判断。本公司对于是否适用不负任何责任。

- 7. 本资料中所记载的产品并非针对万一出现故障或是错误运行就会威胁到人的生命或给人体带来危害的机器、系统(如各种安全装置或者运输交通用的、医疗、燃烧控制、航天器械、核能、海底中继用的机器和系统等)而设计和制造的,特别是对于品质和可靠性要求极高的机器和系统等(将本公司指定用于汽车方面的产品用于汽车时除外)。如果要用于上述的目的,请务必事先向本公司的营业窗口咨询。另外,对于用于上述目的而造成的损失等,本公司概不负责。

- 8. 除上述第7项内容外,不能将本资料中记载的产品用于以下用途。如果用于以下用途而造成的损失,本公司概不负责。

- 1) 生命维持装置。

- 2) 植埋于人体使用的装置。

- 3) 用于治疗(切除患部、给药等)的装置。

- 4) 其他直接影响到人的生命的装置。

- 9. 在使用本资料所记载的产品时,对于最大额定值、工作电源电压的范围、放热特性、安装条件及其他条件请在本公司规定的保证范围内使用。如果超出了本公司规定的保证范围使用时,对于由此而造成的故障和出现的事故,本公司将不承担任何责任。

- 10. 本公司一直致力于提高产品的质量和可靠性,但一般来说,半导体产品总会以一定的概率发生故障、或者由于使用条件不同而出现错误运行等。为了避免因本公司的产品发生故障或者错误运行而导致人身事故和火灾或造成社会性的损失,希望客户能自行负责进行冗余设计、采取延烧对策及进行防止错误运行等的安全设计(包括硬件和软件两方面的设计)以及老化处理等,这是作为机器和系统的出厂保证。特别是单片机的软件,由于单独进行验证很困难,所以要求在顾客制造的最终的机器及系统上进行安全检验工作。

- 11. 如果把本资料所记载的产品从其载体设备上卸下,有可能造成婴儿误吞的危险。顾客在将本公司产品安装到顾客的设备上时,请顾客自行负责将本公司产品设置为不容易剥落的安全设计。如果从顾客的设备上剥落而造成事故时,本公司将不承担任何责任。

- 12. 在未得到本公司的事先书面认可时,不可将本资料的一部分或者全部转载或者复制。

- 13. 如果需要了解关于本资料的详细内容,或者有其他关心的问题,请向本公司的营业窗口咨询。

# 产品使用时的注意事项

本文对适用于单片机所有产品的"使用时的注意事项"进行说明。有关个别的使用时的注意事项请参照 正文。此外,如果在记载上有与本手册的正文有差异之处,请以正文为准。

#### 1. 未使用的引脚的处理

【注意】将未使用的引脚按照正文的"未使用引脚的处理"进行处理。

CMOS产品的输入引脚的阻抗一般为高阻抗。如果在开路的状态下运行未使用的引脚,由于感应现象,外加LSI周围的噪声,在LSI内部产生穿透电流,有可能被误认为是输入信号而引起误动作。 未使用的引脚,请按照正文的"未使用引脚的处理"中的指示进行处理。

#### 2. 通电时的处理

【注意】通电时产品处于不定状态。

通电时,LSI内部电路处于不确定状态,寄存器的设定和各引脚的状态不定。通过外部复位引脚对产品进行复位时,从通电到复位有效之前的期间,不能保证引脚的状态。

同样,使用内部上电复位功能对产品进行复位时,从通电到达到复位产生的一定电压的期间,不能保证引脚的状态。

3. 禁止存取保留地址 (保留区)

【注意】禁止存取保留地址 (保留区)

在地址区域中,有被分配将来用作功能扩展的保留地址 (保留区)。因为无法保证存取这些地址时的运行,所以不能对保留地址 (保留区)进行存取。

4. 关于时钟

【注意】复位时,请在时钟稳定后解除复位。

在程序运行中转换时钟时,请在要转换成的时钟稳定之后进行。复位时,在通过使用外部振荡器(或者外部振荡电路)的时钟开始运行的系统中,必须在时钟充分稳定后解除复位。另外,在程序运行中,转换成使用外部振荡器(或者外部振荡电路)的时钟时,在要转换成的时钟充分稳定后再进行转换。

5. 关于产品间的差异

【注意】在变更不同型号的产品时,请对每一个产品型号进行系统评价测试。

即使是同一个群的单片机,如果产品型号不同,由于内部ROM、版本模式等不同,在电特性范围内有时特性值、动作容限、噪声耐量、噪声辐射量等也不同。因此,在变更不认同型号的产品时,请对每一个型号的产品进行系统评价测试。

# 本手册的结构

# 1 本手册的结构

本手册的内容结构如下:

- 1. 产品使用时的注意事项

- 2. 本手册的结构

- 3. 前言

- 4. 目录

- 5. 概要

- 6. 各功能模块的说明

- · CPU 及系统控制

- 内部外围模块

各模块功能说明的结构因模块而异,一般由: ①特点、②输入/输出引脚、③寄存器说明、④运行说明、⑤使用时的注意事项等章节构成。

采用本 LSI 设计应用系统时,首先需充分确认注意事项。 各章正文记载有关于说明的注意事项,各章的末尾记载有使用时的注意事项。 必须仔细阅读。(各章节根据需要记载使用时的注意事项)。

- 7. 寄存器一览表

- 8. 电特性

- 9. 附录

- 产品型号、封装尺寸图等

- 10. 本版的修订部分 (仅适用于修订版)

修订履历汇总了修正/追加前版内容的主要部分,并未记载所有修订内容,详情参阅本手册的正文。

11. 索引

# 2 凡例

本手册中使用的寄存器名、位名、数字和符号的表示范例说明如下。

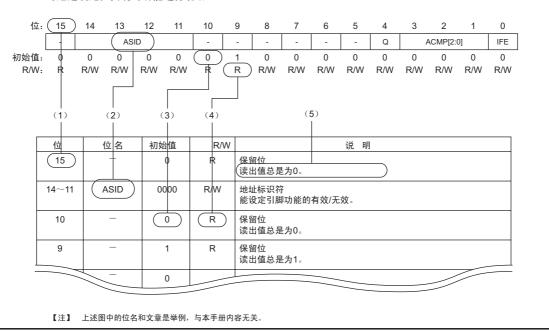

# (1) 寄存器的表示 相同或类似的功能存在于多个通道时,使用"寄存器名称\_通道号"的表示方法。 (例) CMCSR 0 (2) 位的表示 本文中所述位名以左侧为高位、右侧为低位的顺序表示。 (例) CKS1、CKS0 (3) 数字的表示 2进制数为B'xxxx或者xxxx,16进制数为H'xxxx,10进制数为xxxx (例) B'11或者11、H'EFA0、1234 (4) 符号的表示 对低电平有效的信号加上划线。 (例) WDTOVF (1) (4) 14. 比较匹配定时器 (CMT) 14.2.2 比较匹配定时器的控制/状态寄存器\_0、1 (CMCSR\_0)、1) CMCSR表示比较匹配的产生以及设定中断的允许/禁止和累加计数用的时钟。WDTOVF 信号或中断产生时,TCNT的初始值返回到0 14.3. 运行识明 14.3.1 周期计数运行 如果通过CMCSR寄存鑑的CKS1、OKS0位选择内部时钟,并且将CMSTR寄存器的 STR位设定为1、CMCNT计数器都通过所选的时钟开始累加计数。当CMCNT计数器的值 和比较匹配常数寄存器(CMCOR)的值匹配时,CMCNT计数器被清除为H'0000,并且 CMCSR寄存器的CMF标志被置1 此时,CKS1、CKS0位的设定为(2010时,选择4)4的时

(2)

【注】 上述图中的位名和文章是举例,与本手册内容无关。

(3)

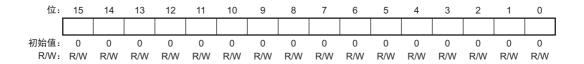

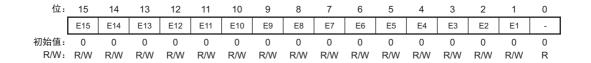

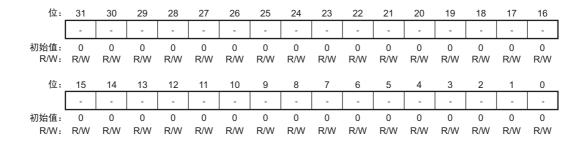

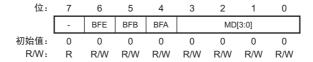

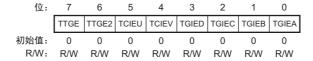

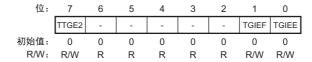

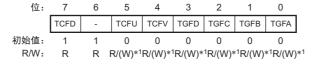

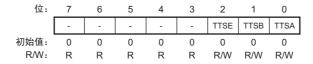

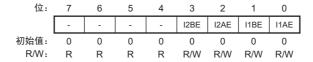

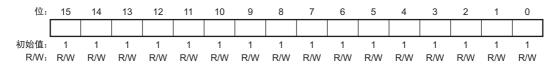

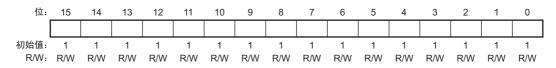

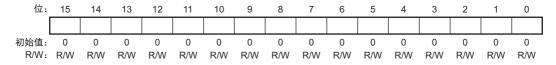

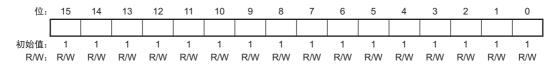

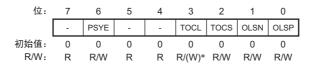

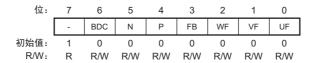

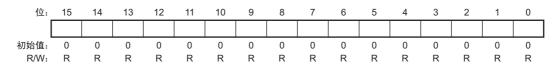

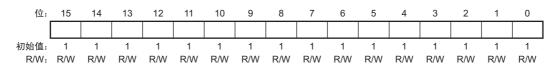

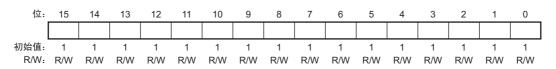

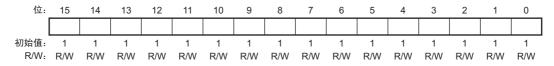

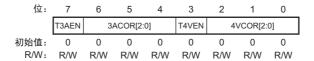

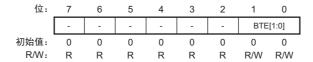

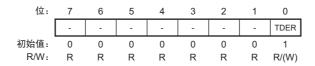

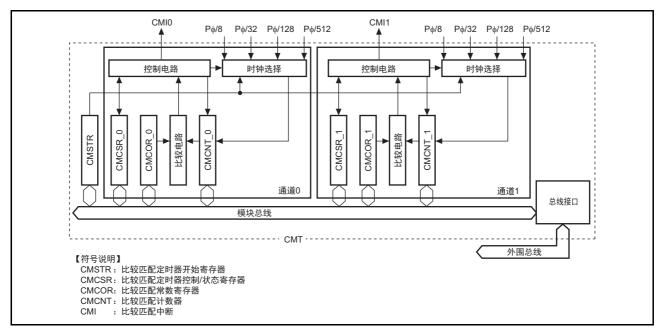

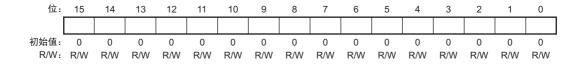

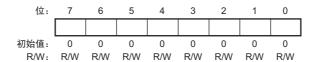

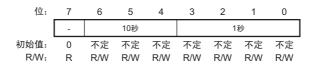

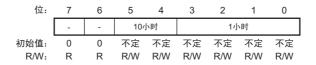

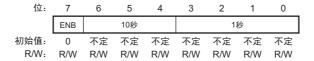

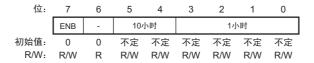

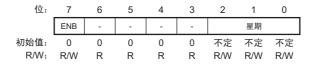

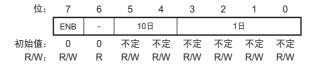

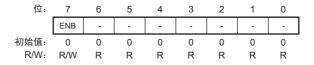

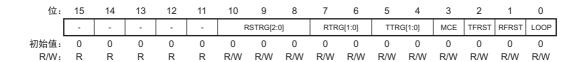

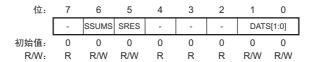

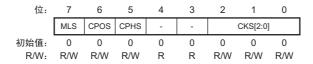

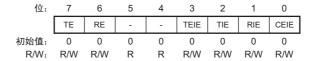

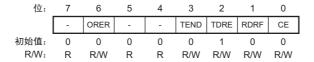

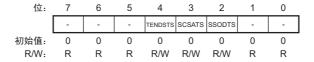

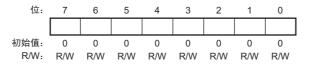

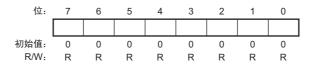

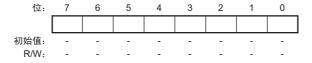

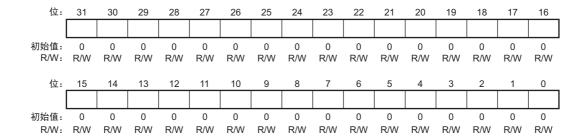

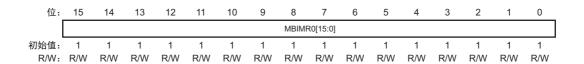

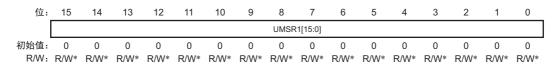

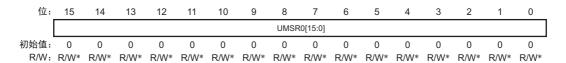

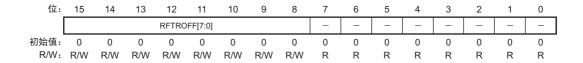

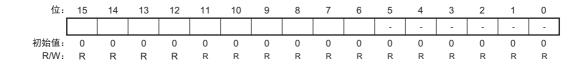

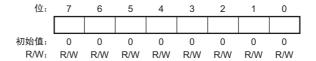

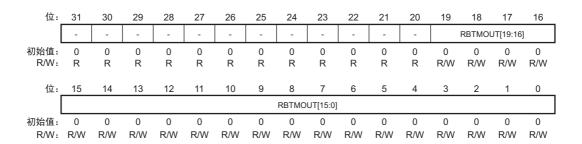

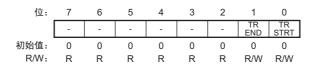

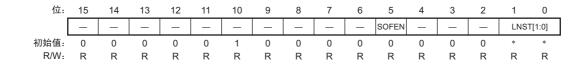

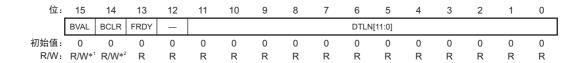

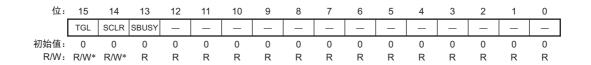

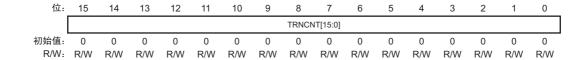

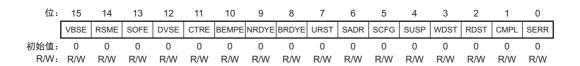

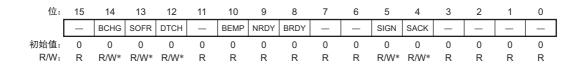

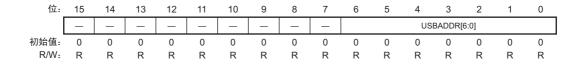

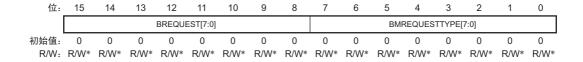

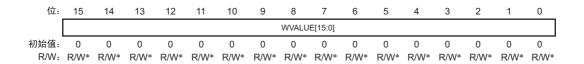

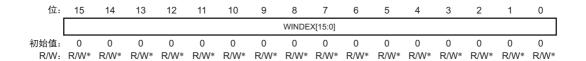

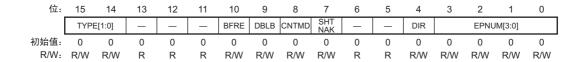

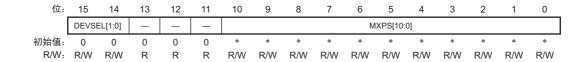

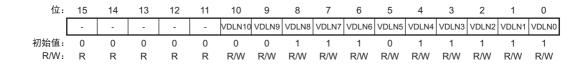

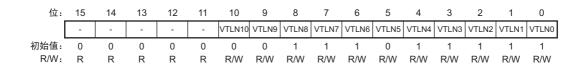

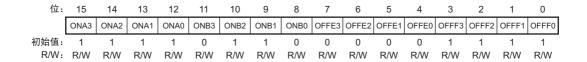

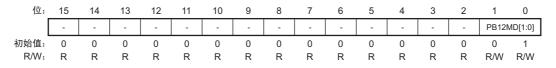

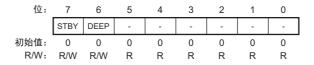

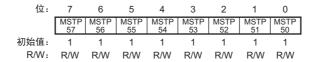

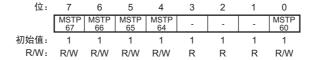

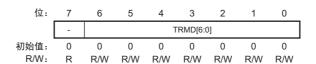

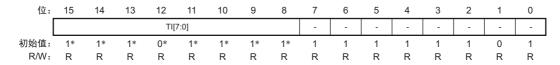

## 3 位图和位表的表示

各寄存器的说明中,有表示位排列的位图和说明位设定内容的位表。

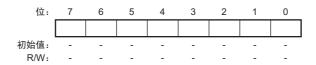

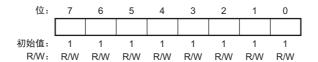

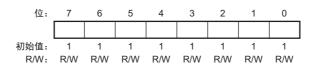

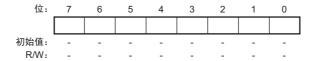

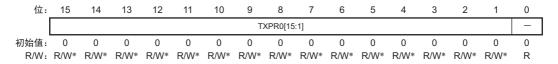

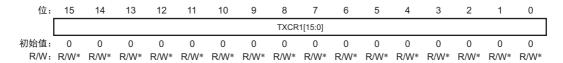

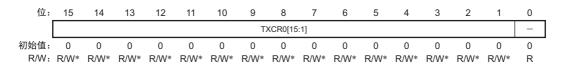

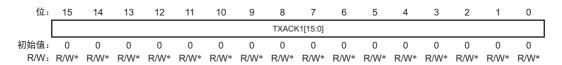

(1) 位

表示位号码。

32位寄存器按31到0的顺序表示,16位寄存器按15到0的顺序表示。

#### (2) 位名

表示寄存器的位名或者字段名。

在字段需要明示位的位数时,追加如同ASID[3:0]一样的位数表示法。

保留位用"一"表示。

但也有不描述位名而表示为空白的情况,例如时间计数器等。

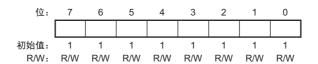

#### (3) 初始值

各位上电复位后的值作为初始值表示。

0 :表示初始值为0。

1 :表示初始值为1。

一 :表示初始值不定。

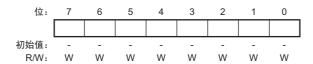

#### (4) R/W

表示各位可读出、写入或者不能读出、写入。

使用的表示法说明如下。

R/W: 可读出以及写入的位或者字段。

R/(W) : 可读出以及写入的位或者字段。

但仅是为了清除标志的写入才能进行。

R:可读出位或者字段。

但保留位全部表示为"R"。需要写入时,

请写入位表指定的值或者初始值。

W: 可写入的位或者字段。

但读出的值是位表记载以外的情况时,不被保证。

#### (5) 说明

对通过设定位实现的功能进行说明。

所有商标及注册商标分别归属于其所有者。

# 前言

本 LSI 以瑞萨科技独创的 RISC 结构 CPU 为内核,是集成了系统构成所需外围功能的 RISC 单片机。

对象:本手册以使用本 LSI 设计应用系统的用户为对象。使用本手册的读者需具备电路、逻辑电路及单片机的相关基础知识。

目的:本手册以让用户了解本 LSI 的硬件功能与电特性为目的。

## 阅读方法

- 希望了解全部功能时

- → 请按照目录阅读。 本手册大致以CPU、系统控制功能、外围功能、电特性的顺序构成。

- · 希望了解CPU功能的详细内容时

- → 请参阅 "SH-2A、SH2A-FPU软件手册"。

- 己知寄存器名称,希望了解详细功能时

- → 本手册后面附有"索引"。请从索引查找页码。

- "第30章 寄存器一览表"汇总了地址、位、初始化等内容。

# 目 录

| 第1章               | 概要                   | 1  |

|-------------------|----------------------|----|

| 1.1 SH            | I7203 的特点            | 1  |

| 1.2 产             | ·品一览表                | 6  |

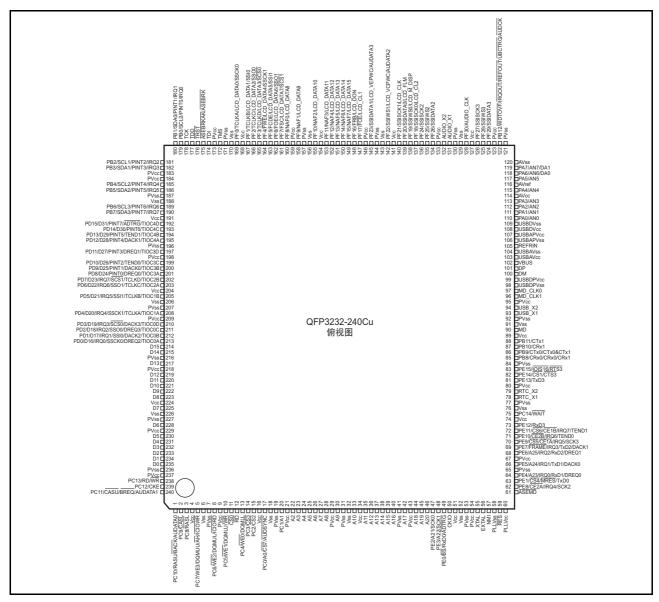

| 1.3 框             | 图                    | 6  |

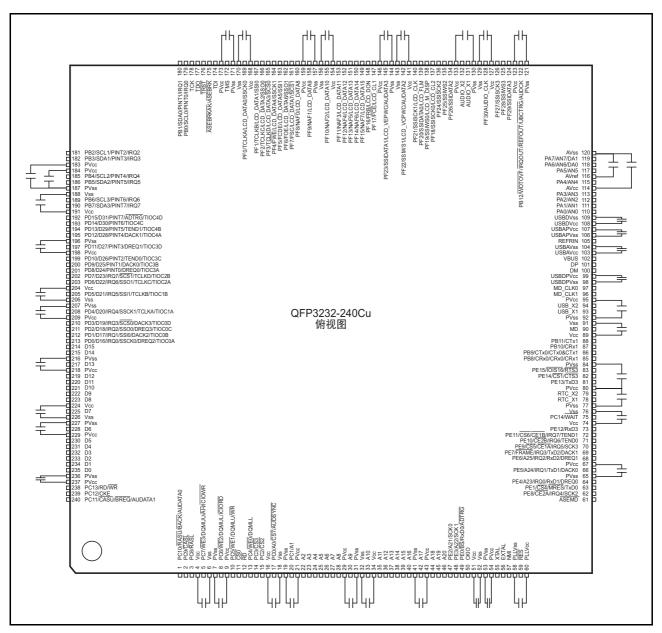

| 1.4 引             | 脚排列图                 | 7  |

| 1.5 引             | 脚功能                  | 8  |

| 1.6 引             | 脚一览表                 | 13 |

| ## 6 <del>*</del> |                      |    |

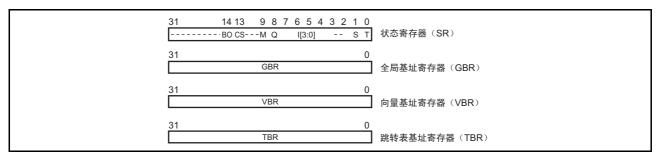

| 第2章               | CPU                  |    |

|                   | 存器结构                 |    |

| 2.1.1             | 通用寄存器                |    |

| 2.1.2             | 控制寄存器                |    |

| 2.1.3             | 系统寄存器                |    |

| 2.1.4             | 寄存器存储体               |    |

| 2.1.5             | 寄存器的初始值              |    |

|                   | 据格式                  |    |

| 2.2.1<br>2.2.2    | 寄存器的数据格式             |    |

|                   | 仔储备的数据格式             |    |

| 2.2.3             |                      |    |

|                   | 令特点                  |    |

| 2.3.1             | RISC 结构              |    |

| 2.3.2<br>2.3.3    | 寻址方式<br>指令格式         |    |

|                   |                      |    |

| 2.4 指·<br>2.4.1   | 令系统                  |    |

| 2.4.1             | 指令系统分类               |    |

| 2.4.2             | 数据传送指令               |    |

| 2.4.3             | 逻辑运算指令               |    |

| 2.4.4             | 及再应身指令               |    |

| 2.4.5             | <b>移位</b> 指令         |    |

| 2.4.6             | れが指す<br>系统控制指令       |    |

| 2.4.7             | 深坑在前有令               |    |

| 2.4.8             | FPU 相关的 CPU 指令       |    |

| 2.4.9             | fPU 相关的 CPU 指令       |    |

|                   | 型状态                  |    |

| 2.3 XL            | <u> </u>             | 00 |

| 第3章               | 浮点单元 (FPU)           | 62 |

| 3.1 特             | 点                    | 62 |

| 3.2 数             | 据格式                  | 62 |

| 3.2.1             | 浮点格式                 | 62 |

| 3.2.2             | 非数 (NaN)             | 64 |

| 3.2.3             | 非规格化数                | 64 |

| 3.3 寄             | 存器说明                 | 65 |

| 3.3.1             | 浮点寄存器                | 65 |

| 3.3.2             | 浮点状态 / 控制寄存器 (FPSCR) | 66 |

| 3.3.3             | 浮点通信寄存器 (FPUL)       | 67 |

| 3.4 舍             | λ                    | 67 |

| 3.5 FP            | 'U 异常                | 68 |

| 3.5.1             | FPU 异常源              | 68 |

| 3.5.2             | FPU 异常处理             | 68 |

|                   |                      |    |

| 第4章   | 时钟脉冲振荡器 (CPG)                                                 | 69  |

|-------|---------------------------------------------------------------|-----|

| 4.1 特 | 点                                                             | 69  |

| 4.2 输 | 入 / 输出引脚                                                      | 72  |

| 4.3 时 | 钟运行模式                                                         | 73  |

| 4.4 寄 | 存器说明                                                          | 76  |

| 4.4.1 | 频率控制寄存器 (FRQCR)                                               | 76  |

| 4.5 频 | 率更改方法                                                         | 78  |

| 4.5.1 | 倍频比的更改                                                        | 78  |

| 4.5.2 | 分频比的更改                                                        | 78  |

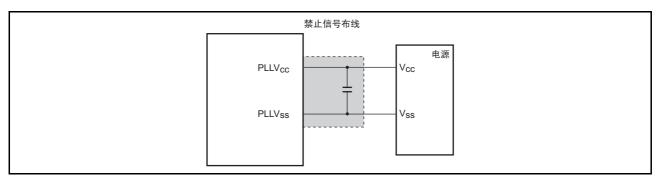

| 4.5.3 | PLL 振荡电路使用时的注意事项                                              | 79  |

| 4.6 使 | 用时的注意事项                                                       | 79  |

| 第 5 章 | 异常处理                                                          | 80  |

| 5.1 概 | 要                                                             | 80  |

| 5.1.1 | 异常处理的种类与优先顺序                                                  | 80  |

| 5.1.2 | 异常处理的运行                                                       | 81  |

| 5.1.3 | 异常处理向量表                                                       | 82  |

| 5.2 复 | 位                                                             | 83  |

| 5.2.1 | 输入/输出引脚                                                       | 83  |

| 5.2.2 | 复位种类                                                          | 84  |

| 5.2.3 | 上电复位                                                          | 84  |

| 5.2.4 | 手动复位                                                          | 85  |

| 5.3 地 | 址错误                                                           | 86  |

| 5.3.1 | 地址错误的产生源                                                      | 86  |

| 5.3.2 | 地址错误异常处理                                                      | 86  |

| 5.4 寄 | 存器存储体错误                                                       | 87  |

| 5.4.1 | 寄存器存储体错误的产生源                                                  |     |

| 5.4.2 | 寄存器存储体错误异常处理                                                  |     |

| 5.5 中 | 断                                                             |     |

| 5.5.1 | 中断源                                                           |     |

| 5.5.2 | 中断优先顺序                                                        |     |

| 5.5.3 | 中断异常处理                                                        | 89  |

| 5.6 指 | 令引起的异常                                                        |     |

| 5.6.1 | 指令引起的异常种类                                                     |     |

| 5.6.2 | 陷阱指令                                                          | 90  |

| 5.6.3 | 槽非法指令                                                         |     |

| 5.6.4 | 一般非法指令                                                        |     |

| 5.6.5 | 整数除法异常                                                        |     |

| 5.6.6 | FPU 异常                                                        |     |

|       | 接受异常处理时                                                       |     |

|       | 常处理后的堆栈状态                                                     |     |

|       | 用时的注意事项                                                       |     |

| 5.9.1 | 堆栈指针 (SP) 的值                                                  |     |

| 5.9.2 | 向量基址寄存器 (VBR)的值                                               |     |

| 5.9.3 | 在地址错误异常处理的堆栈存取时产生的地址错误                                        | 94  |

| 第6章   | 中断控制器 (INTC)                                                  |     |

|       | 点                                                             |     |

|       | 入 / 输出引脚                                                      |     |

| 6.3 寄 | 存器说明                                                          |     |

| 6.3.1 | 中断优先级设定寄存器 01、02、05 $\sim$ 17(IPR01、IPR02、IPR05 $\sim$ IPR17) |     |

| 6.3.2 | 中断控制寄存器 0 (ICR0)                                              |     |

| 6.3.3 | 中断控制寄存器 1 (ICR1)                                              | 100 |

| 6.3.4   | 中断控制寄存器 2 (ICR2)             | 101 |

|---------|------------------------------|-----|

| 6.3.5   | IRQ 中断请求寄存器 (IRQRR)          | 102 |

| 6.3.6   | PINT 中断允许寄存器 (PINTER)        | 103 |

| 6.3.7   | PINT 中断请求寄存器 (PIRR)          | 104 |

| 6.3.8   | 存储体控制寄存器 (IBCR)              |     |

| 6.3.9   | 存储体编号寄存器(IBNR)               | 106 |

| 6.4 中國  | <b>断源</b>                    | 107 |

| 6.4.1   | NMI 中断                       | 107 |

| 6.4.2   | 用户断点中断                       | 107 |

| 6.4.3   | H-UDI 中断                     | 107 |

| 6.4.4   | IRQ 中断                       | 107 |

| 6.4.5   | PINT 中断                      |     |

| 6.4.6   | 内部外围模块中断                     | 108 |

| 6.5 中国  | 新异常处理向量表与优先顺序                |     |

| 6.6 运行  | 行说明                          | 113 |

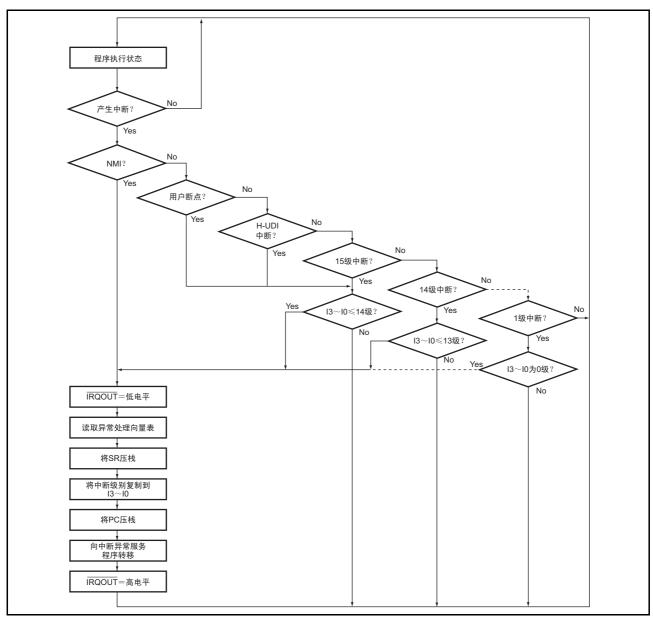

| 6.6.1   | 中断运行的流程                      |     |

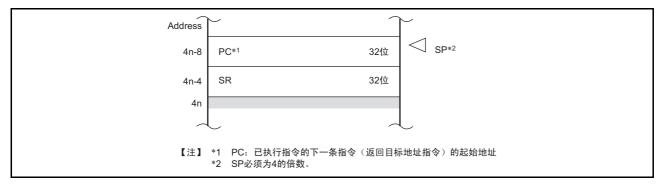

| 6.6.2   | 中断异常处理结束后的堆栈状态               |     |

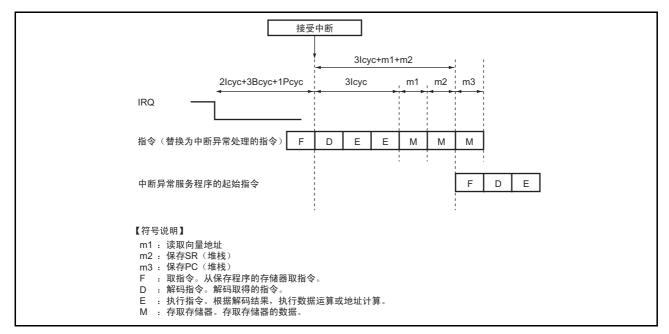

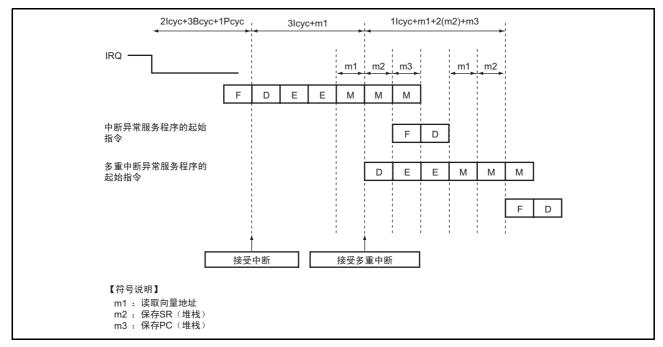

| 6.7 中國  | 断响应时间                        | 115 |

| 6.8 寄石  | 存器存储器                        |     |

| 6.8.1   | 存储体的对象寄存器与输入/输出方式            |     |

| 6.8.2   | 存储体保存、返回的运行                  |     |

| 6.8.3   | 在保存至所有存储体的状态下执行的保存、返回        | 122 |

| 6.8.4   | 寄存器存储体异常                     |     |

| 6.8.5   | 寄存器存储体错误异常处理                 |     |

| 6.9 通知  | 过中断请求信号传送数据                  | 123 |

| 6.9.1   | 中断请求信号作为 CPU 中断源而非 DMAC 启动源时 | 124 |

| 6.9.2   | 中断请求信号作为 DMAC 启动源而非 CPU 中断源时 |     |

| 6.10 使月 | 用时的注意事项                      | 124 |

| 6.10.1  | 清除中断源的时序                     | 124 |

| 6.10.2  |                              |     |

|         |                              |     |

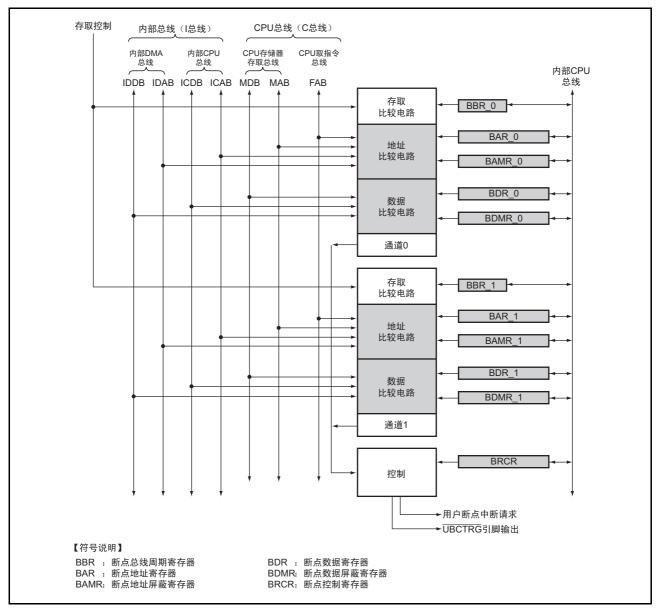

| 第7章     | 用户断点控制器 (UBC)                |     |

|         | 点                            |     |

|         | 入/输出引脚                       |     |

|         | 存器说明                         |     |

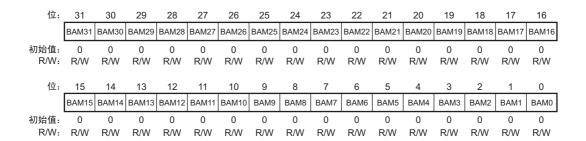

| 7.3.1   | 断点地址寄存器 (BAR)                |     |

| 7.3.2   | 断点地址屏蔽寄存器 (BAMR)             |     |

| 7.3.3   | 断点数据寄存器 (BDR)                |     |

| 7.3.4   | 断点数据屏蔽寄存器 (BDMR)             |     |

| 7.3.5   | 断点总线周期寄存器 (BBR)              |     |

| 7.3.6   | 断点控制寄存器 (BRCR)               |     |

|         | 行说明                          |     |

| 7.4.1   | 用户断点运行的流程                    |     |

| 7.4.2   | 取指令周期的断点                     |     |

| 7.4.3   | 数据存取周期的断点                    |     |

| 7.4.4   | 被保存的程序计数器值                   |     |

| 7.4.5   | 使用例                          |     |

| 7.5 使月  | 用时的注意事项                      | 137 |

| 第8章     | 高速缓存                         | 120 |

|         |                              |     |

|         | 点                            |     |

| 8.1.1   | 高速缓存的结构<br>存器说明              |     |

| 0.2 前4  | [十百章 [/T. P/]                |     |

| 8.2.1  | 高速缓存控制寄存器 1 (CCR1)               | 140 |

|--------|----------------------------------|-----|

| 8.2.2  | 高速缓存控制寄存器 2 (CCR2)               | 141 |

| 8.3 运  | 行说明                              | 143 |

| 8.3.1  | 高速缓存的搜索                          | 143 |

| 8.3.2  | 读取操作                             |     |

| 8.3.3  | 预取操作 (仅限操作数高速缓存)                 | 144 |

| 8.3.4  | 写入操作 (仅限操作数高速缓存)                 | 144 |

| 8.3.5  | 回写缓冲器 (仅限操作数高速缓存)                | 145 |

| 8.3.6  | 高速缓存与外部存储器的比配                    |     |

| 8.4 存  | 储器分配高速缓存的结构                      | 146 |

| 8.4.1  | 地址阵列                             | 146 |

| 8.4.2  | 数据阵列                             | 147 |

| 8.4.3  | 使用例                              | 148 |

| 8.4.4  | 注意事项                             | 148 |

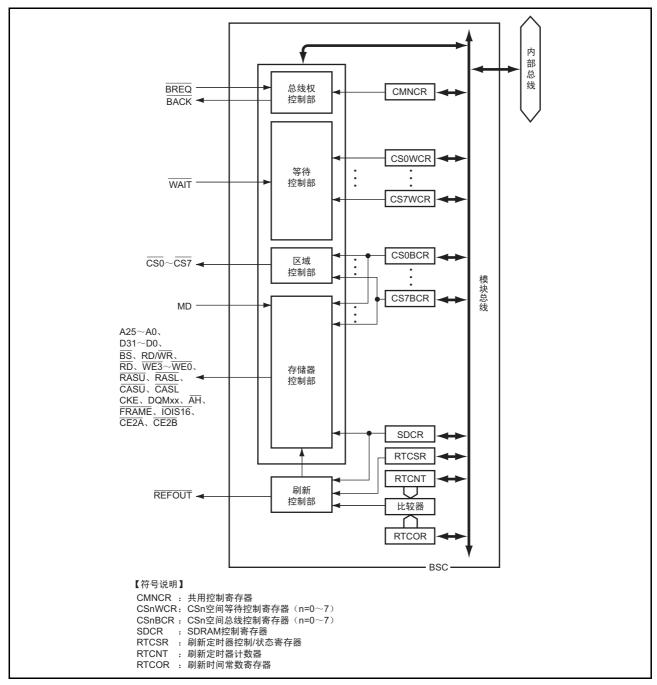

| 第 9 章  | 总线状态控制器 (BSC)                    | 149 |

| 9.1 特  | 占                                | 149 |

|        | 入 / 输出引脚                         | •   |

|        | 域概要                              |     |

| 9.3.1  | 地址映射                             |     |

| 9.3.2  | 各区域的数据总线宽度与引脚功能设定                |     |

| 9.4 寄  | 存器说明                             |     |

| 9.4.1  | 共用控制寄存器 (CMNCR)                  |     |

| 9.4.2  | CSn 空间总线控制寄存器 (CSnBCR) (n=0 ~ 7) | 158 |

| 9.4.3  | CSn 空间等待控制寄存器 (CSnWCR) (n=0 ~ 7) | 161 |

| 9.4.4  | SDRAM 控制寄存器 (SDCR)               | 184 |

| 9.4.5  | 刷新定时器控制 / 状态寄存器 (RTCSR)          | 186 |

| 9.4.6  | 刷新定时器计数器 (RTCNT)                 | 187 |

| 9.4.7  | 刷新时间常数寄存器 (RTCOR)                | 187 |

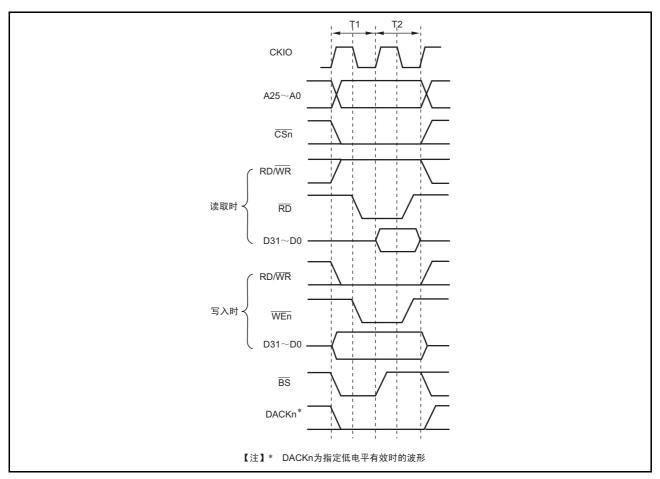

| 9.5 运  | 行说明                              | 188 |

| 9.5.1  | 字节序 / 存取长度与数据对齐                  | 188 |

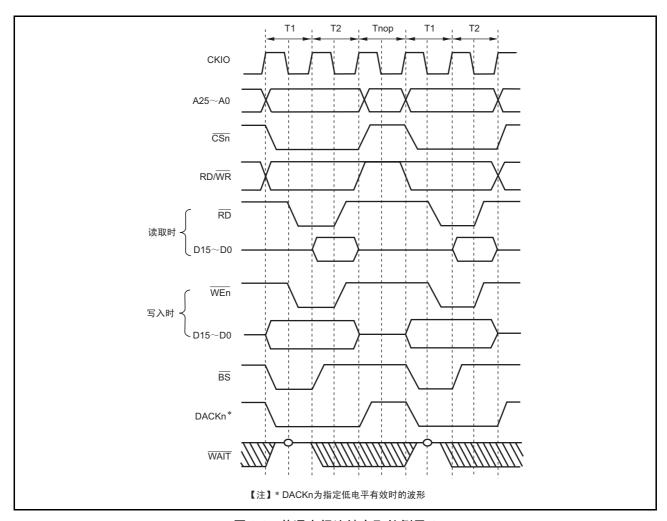

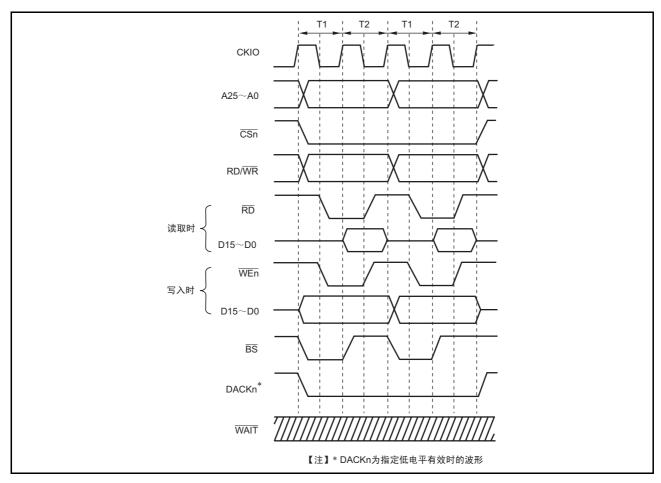

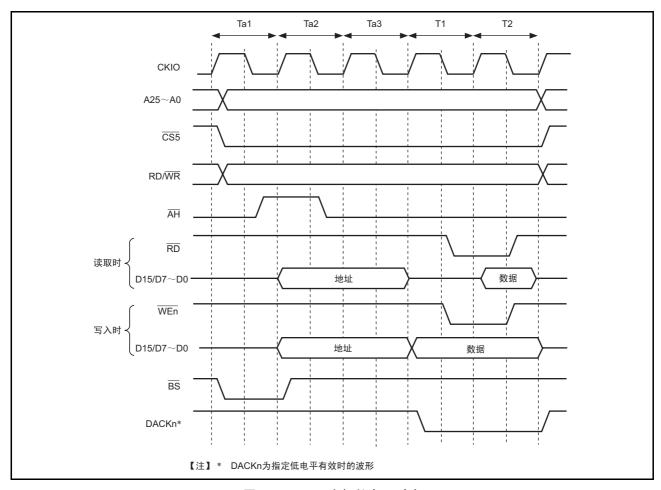

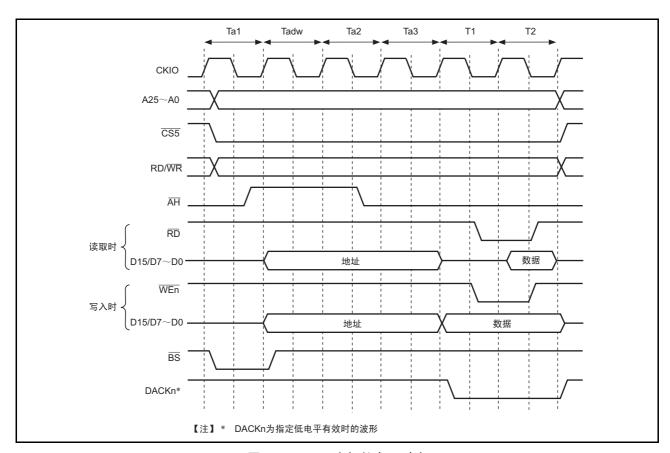

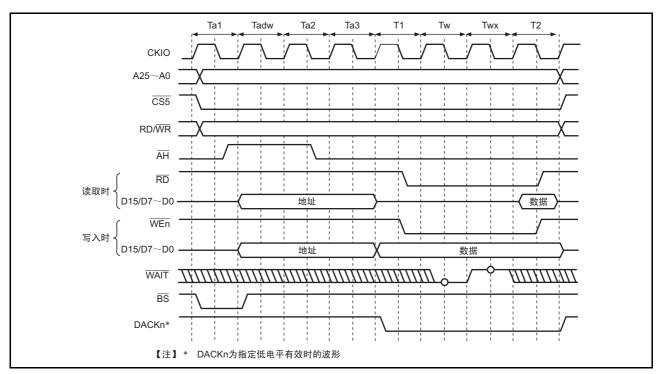

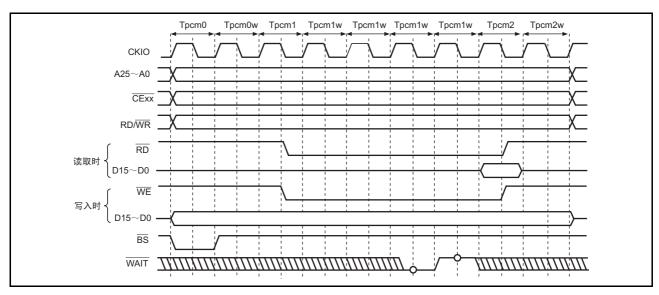

| 9.5.2  | 普通空间接口                           |     |

| 9.5.3  | 存取等待控制                           | 197 |

| 9.5.4  |                                  | 199 |

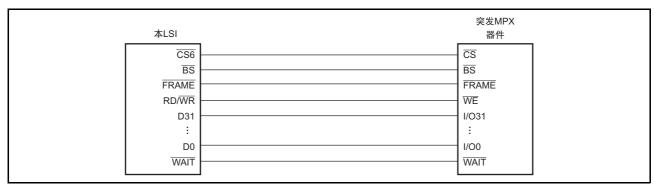

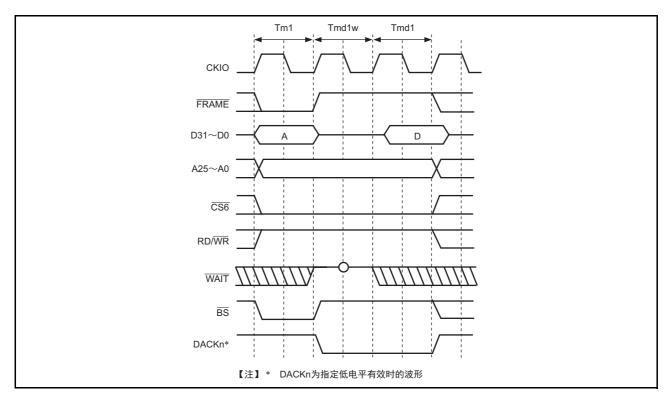

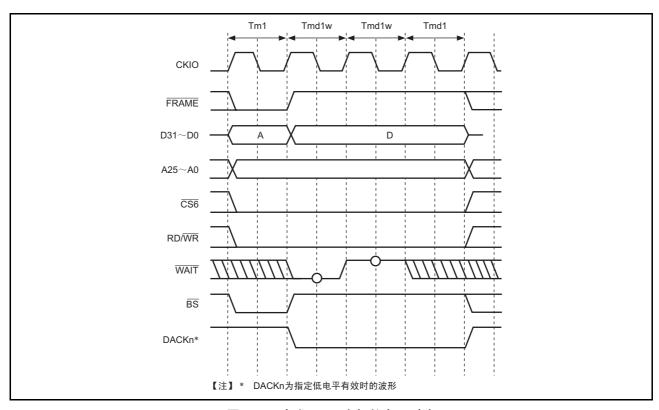

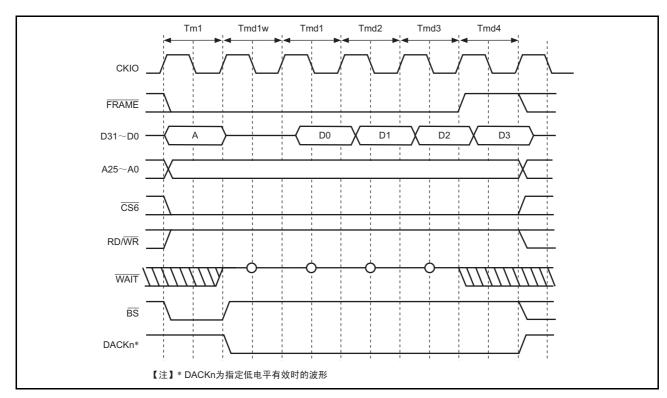

| 9.5.5  | MPX-I/O 接口                       | 200 |

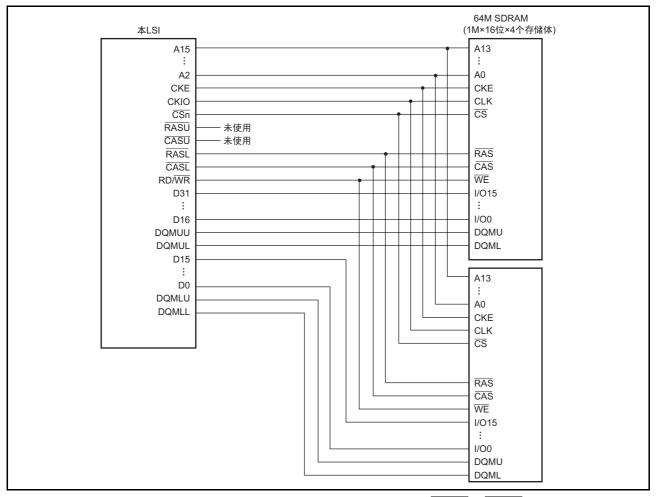

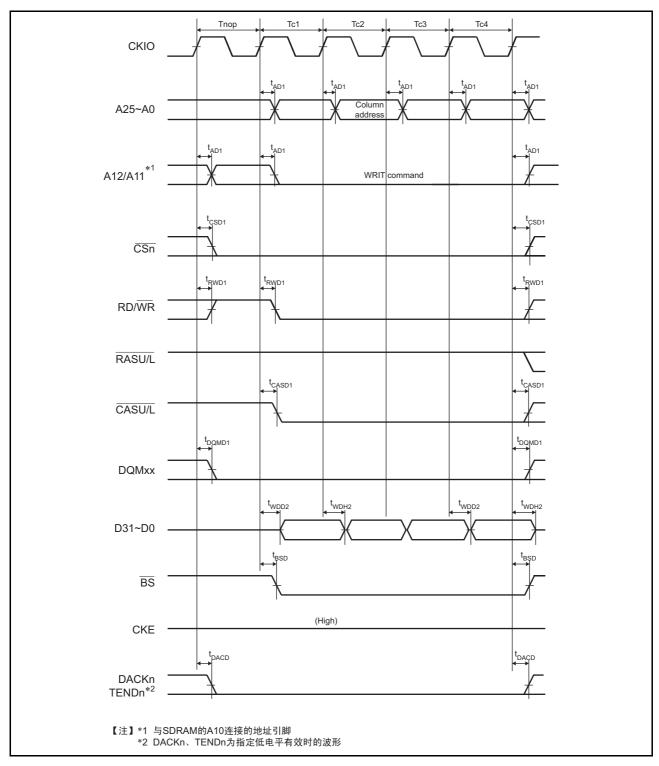

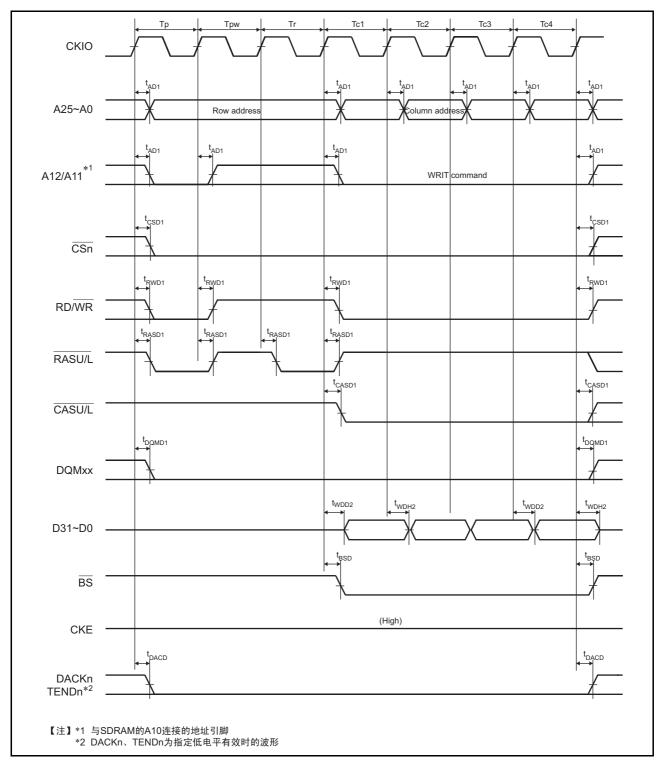

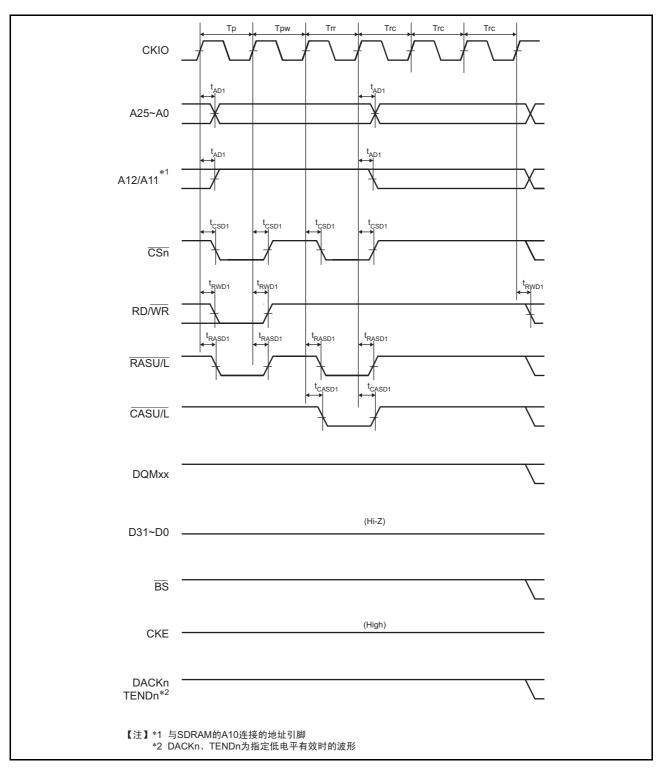

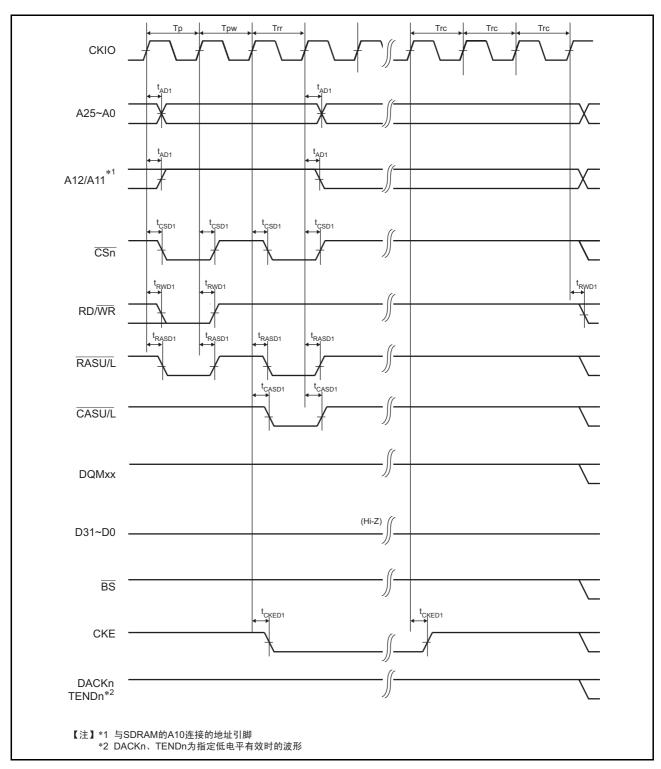

| 9.5.6  | SDRAM 接口                         | 202 |

| 9.5.7  | 突发 ROM (时钟异步) 接口                 | 228 |

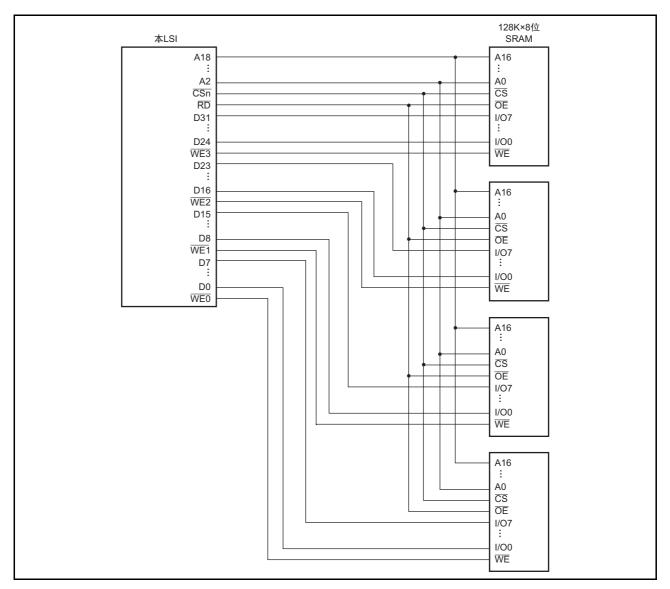

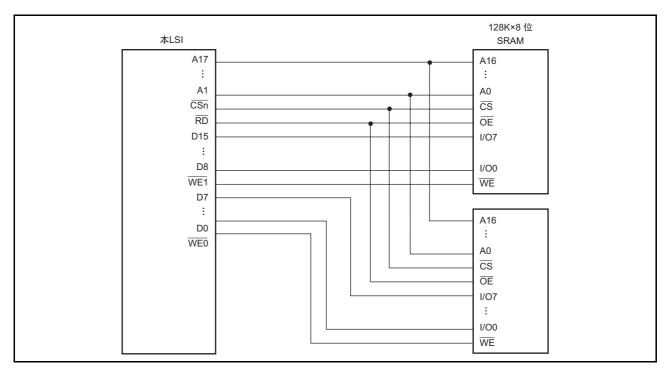

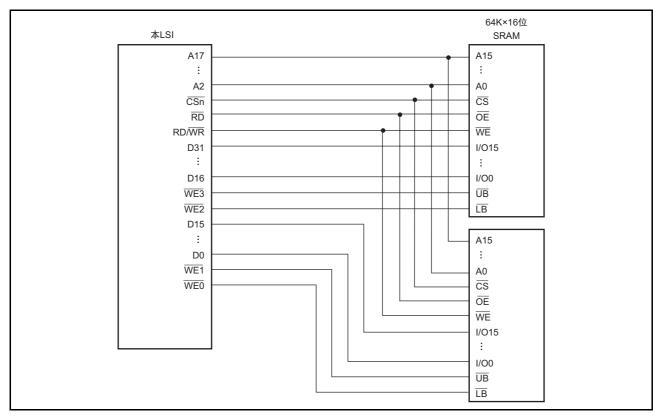

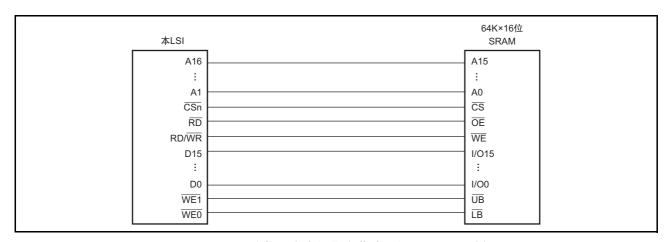

| 9.5.8  | 带字节选择的 SRAM 接口                   | 230 |

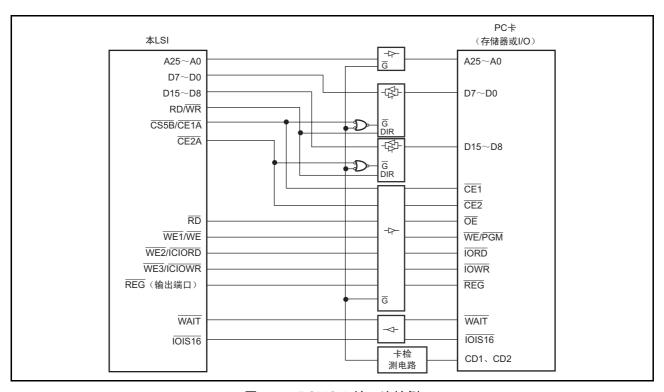

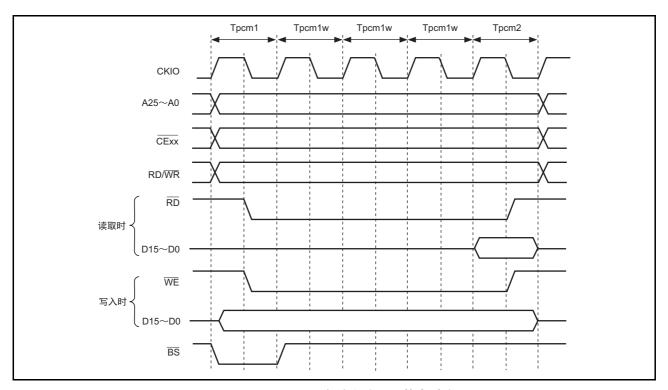

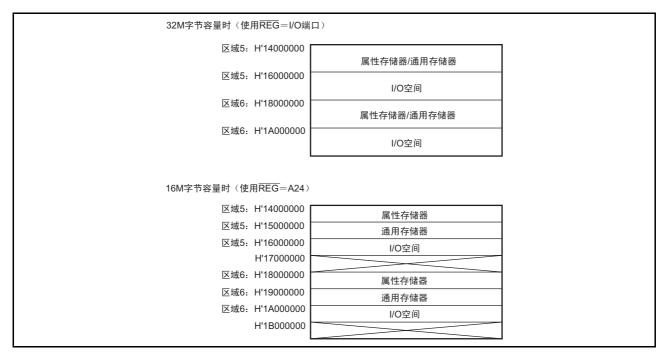

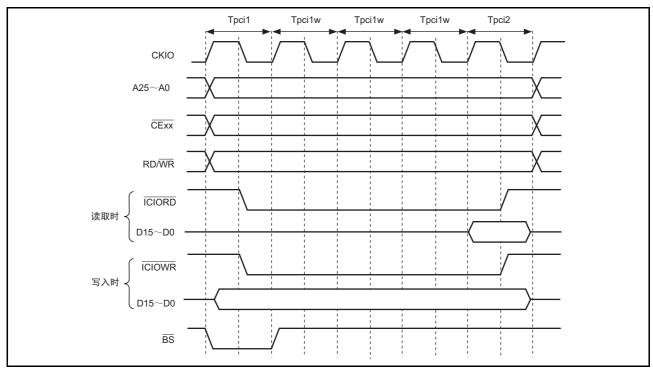

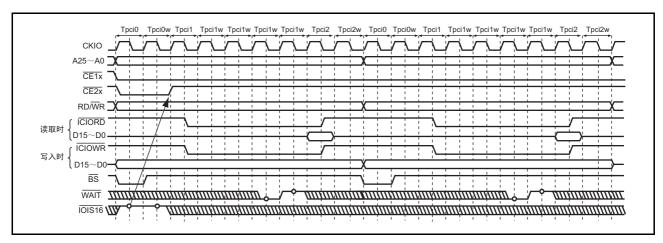

| 9.5.9  | PCMCIA 接口                        | 234 |

| 9.5.10 | 突发 MPX-I/O 接口                    | 238 |

| 9.5.11 | 突发 ROM (时钟同步)接口                  | 241 |

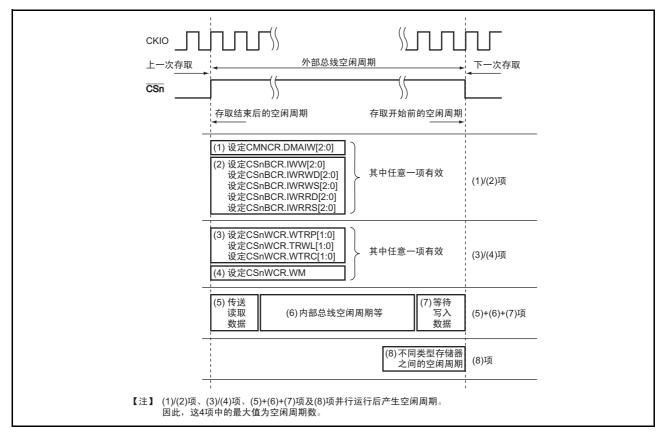

| 9.5.12 | 存取周期之间的空闲周期                      | 242 |

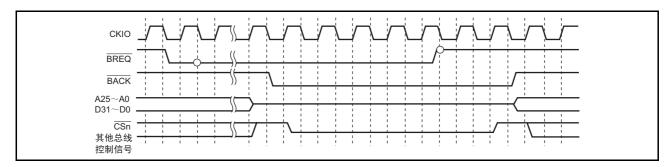

| 9.5.13 | 总线仲裁                             | 248 |

| 9.5.14 | 其他                               | 249 |

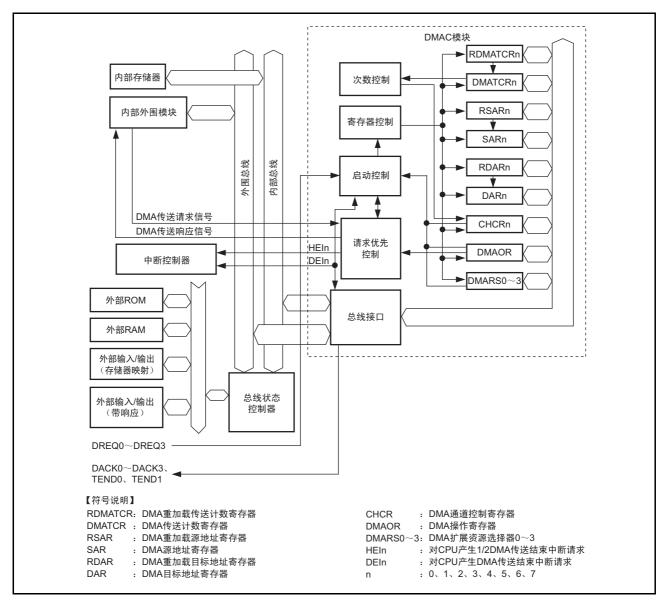

| 第 10 章 | 直接存储器存取控制器 (DMAC)                | 251 |

|        | 点                                |     |

| 10.2 输 | 入/输出引脚                           | 253 |

| 10.3 寄 | 存器说明                             | 253 |

| 10.3.1 | DMA 源地址寄存器 (SAR)                 | 256 |

| 10.3.2 | DMA 目标地址寄存器 (DAR)                | 256 |

| 10.3.3 | DMA 传送计数寄存器 (DMATCR)             | 256 |

| 10.3.4 | DMA 通道控制寄存器 (CHCR)               | 257 |

| 10.3.5  | DMA 重加载源地址寄存器 (RSAR)                   | 261 |

|---------|----------------------------------------|-----|

| 10.3.6  | DMA 重加载目标地址寄存器 (RDAR)                  |     |

| 10.3.7  | DMA 重加载传送计数寄存器 (RDMATCR)               |     |

| 10.3.8  | DMA 操作寄存器(DMAOR)                       |     |

| 10.3.9  | DMA 扩展资源选择器 0 ~ 3 (DMARS0 ~ DMARS3)    |     |

|         | F说明                                    |     |

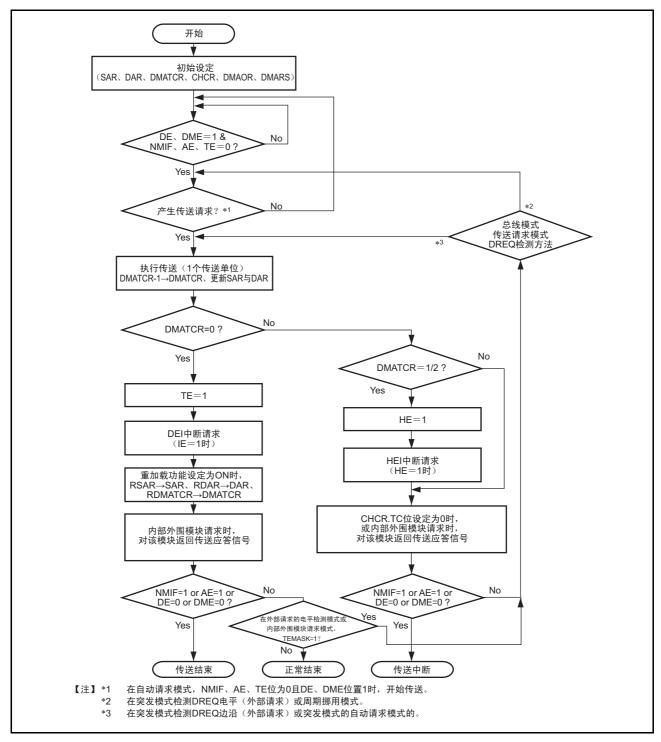

| 10.4.1  | 传送流程                                   |     |

| 10.4.2  | DMA 传送请求                               |     |

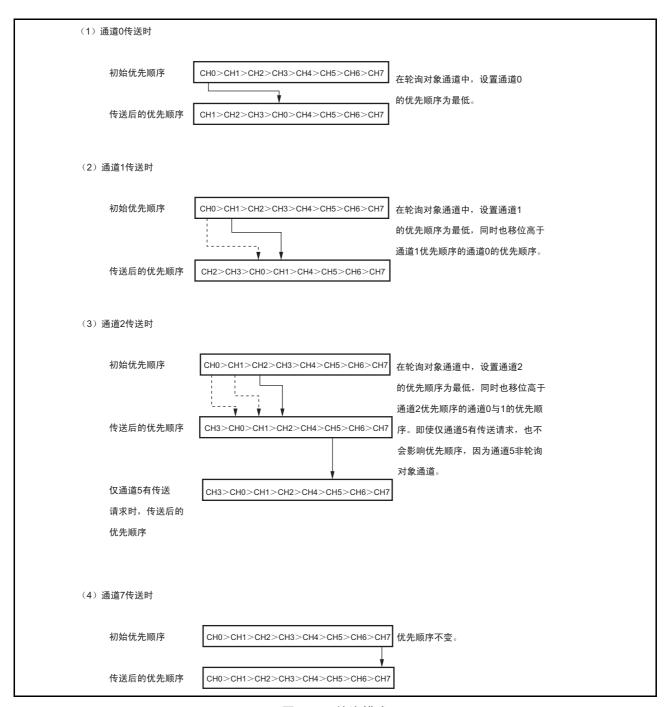

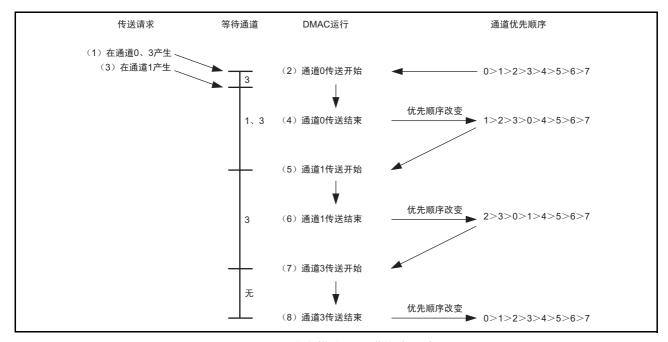

| 10.4.3  | 通道的优先顺序                                |     |

| 10.4.4  | DMA 传送的种类                              |     |

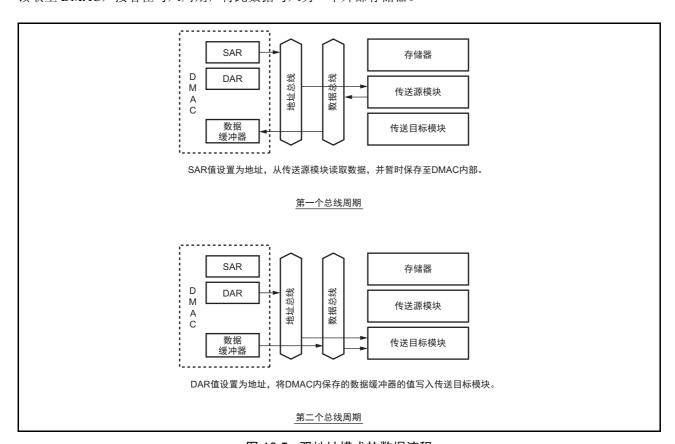

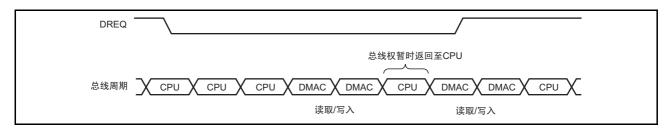

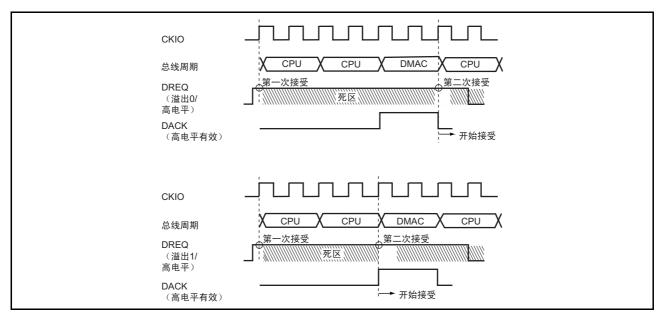

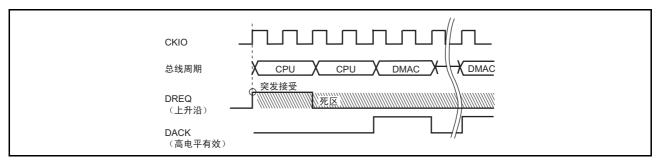

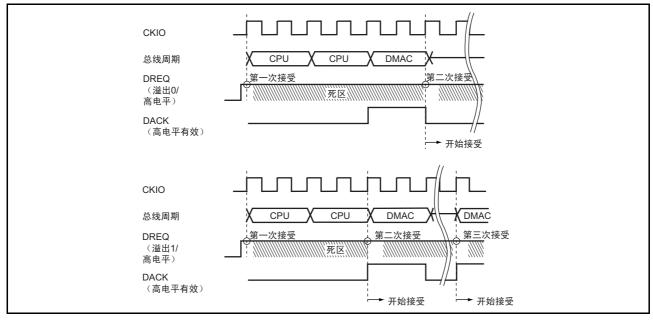

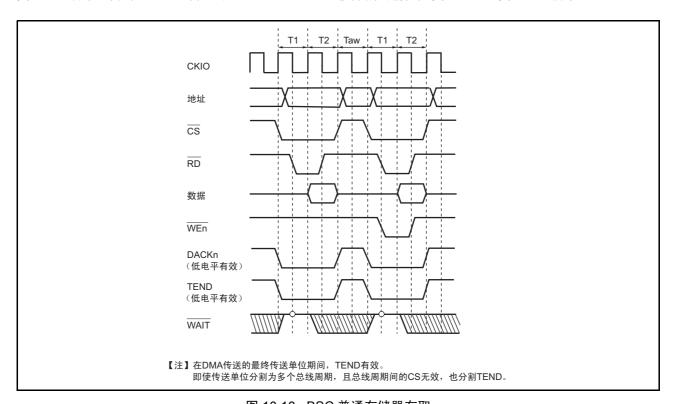

| 10.4.5  | 总线周期的状态数和 DREQ 引脚的采样时序                 |     |

|         | 时的注意事项                                 |     |

| 10.5.1  | 半结束标志的置位及半结束中断                         |     |

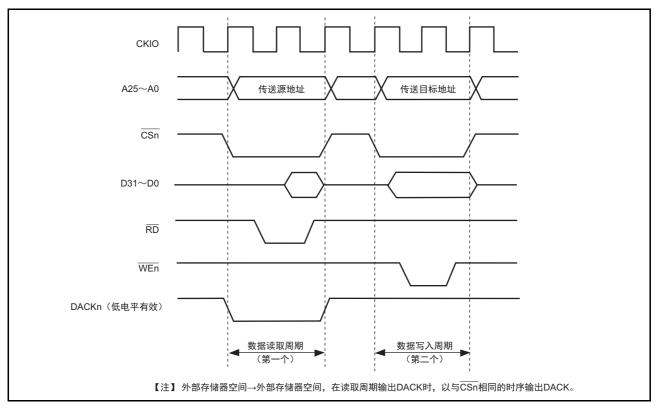

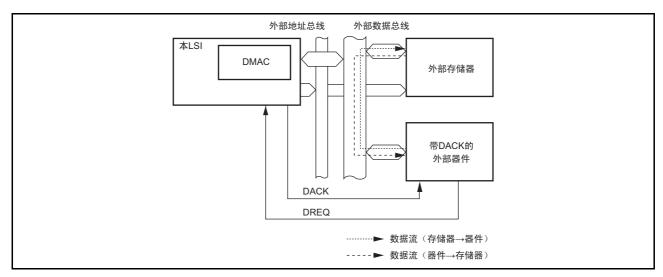

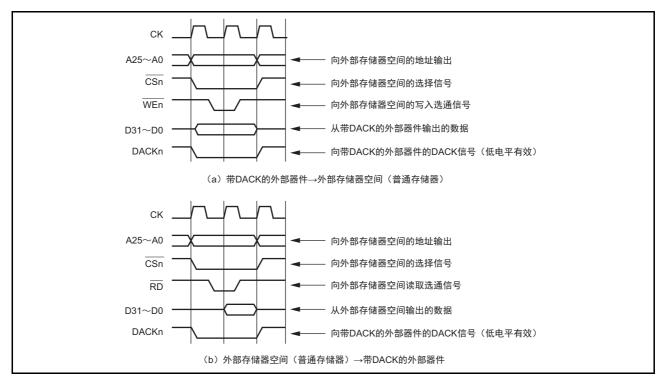

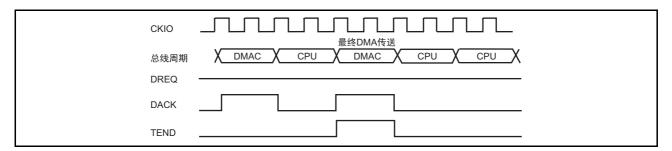

| 10.5.2  | DACK 输出及 TEND 输出的时序                    |     |

| 10.5.3  | 使用外部请求模式的注意事项                          |     |

| 10.5.4  | 使用内部外围模块请求模式或自动请求模式时的注意事项              |     |

|         |                                        |     |

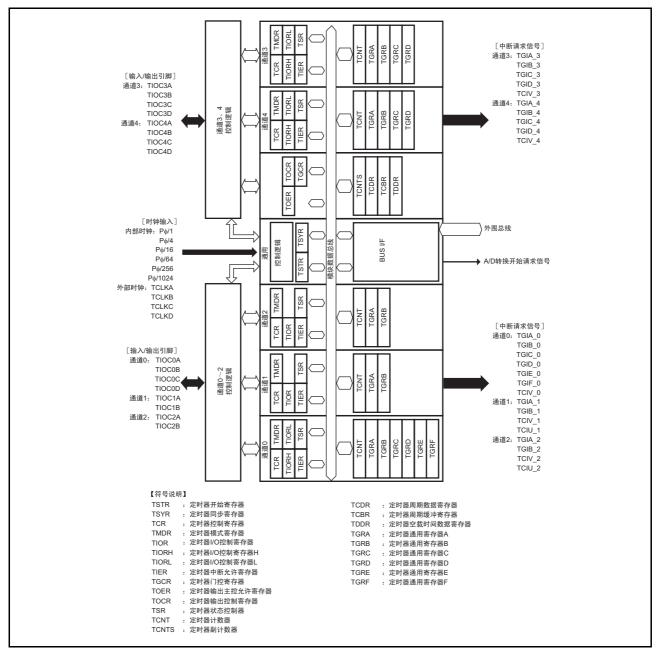

| 第 11 章  | 多功能定时器脉冲单元 2 (MTU2)                    | 286 |

| 11.1 特  | 点                                      | 286 |

| 11.2 箱  | ì入/输出引脚                                | 289 |

| 11.3 寄  | 存器说明                                   | 290 |

| 11.3.1  | 定时器控制寄存器 (TCR)                         | 293 |

| 11.3.2  | 定时器模式寄存器 (TMDR)                        | 296 |

| 11.3.3  | 定时器 I/O 控制寄存器 (TIOR)                   | 298 |

| 11.3.4  | 定时器中断允许寄存器 (TIER)                      | 307 |

| 11.3.5  | 定时器状态寄存器 (TSR)                         | 309 |

| 11.3.6  | 定时器缓冲运行传送模式寄存器 (TBTM)                  | 312 |

| 11.3.7  | 定时器输入捕捉控制寄存器 (TICCR)                   | 313 |

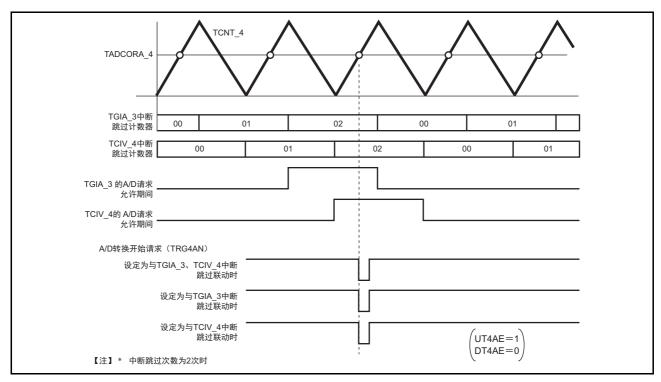

| 11.3.8  | 定时器 A/D 转换开始请求控制寄存器(TADCR)             | 314 |

| 11.3.9  | 定时器 A/D 转换开始请求周期设定寄存器 (TADCORA/B_4)    | 315 |

| 11.3.10 | 定时器 A/D 转换开始请求周期设定缓冲寄存器 (TADCOBRA/B_4) | 316 |

| 11.3.11 | 定时器计数器 (TCNT)                          | 316 |

| 11.3.12 | 定时器通用寄存器 (TGR)                         | 316 |

| 11.3.13 | 定时器开始寄存器 (TSTR)                        | 317 |

| 11.3.14 | 定时器同步寄存器 (TSYR)                        | 318 |

| 11.3.15 | 定时器读取 / 写入允许寄存器 (TRWER)                | 319 |

| 11.3.16 | 定时器输出主控允许寄存器 (TOER)                    | 320 |

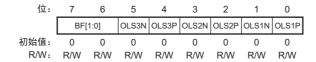

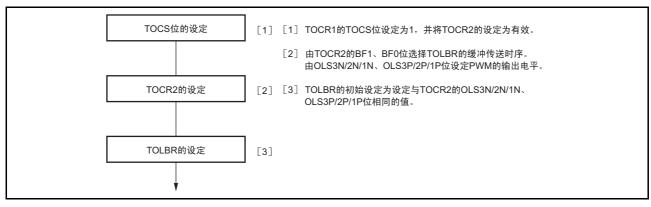

| 11.3.17 | 定时器输出控制寄存器 1 (TOCR1)                   | 321 |

| 11.3.18 | 定时器输出控制寄存器 2 (TOCR2)                   | 323 |

| 11.3.19 | 定时器输出电平缓冲寄存器 (TOLBR)                   | 325 |

| 11.3.20 | 定时器门控寄存器 (TGCR)                        | 326 |

| 11.3.21 | 定时器副计数器 (TCNTS)                        | 327 |

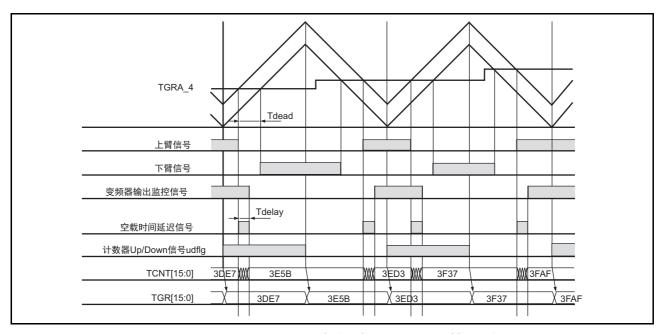

| 11.3.22 | 定时器空载时间数据寄存器(TDDR)                     | 327 |

| 11.3.23 | 定时器周期数据寄存器 (TCDR)                      | 327 |

| 11.3.24 | 定时器周期缓冲寄存器 (TCBR)                      | 328 |

| 11.3.25 | 定时器中断跳过设定寄存器 (TITCR)                   | 328 |

| 11.3.26 | 定时器中断跳过次数计数器 (TITCNT)                  | 330 |

| 11.3.27 | 定时器缓冲传送设定寄存器 (TBTER)                   | 331 |

| 11.3.28 | 定时器空载时间允许寄存器 (TDER)                    | 332 |

| 11.3.29 | 定时器波形控制寄存器 (TWCR)                      |     |

| 11.3.30 | 与总线主控器的接口                              |     |

|         | · 说明                                   |     |

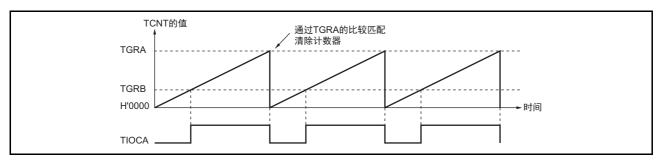

|         | 基本运行                                   |     |

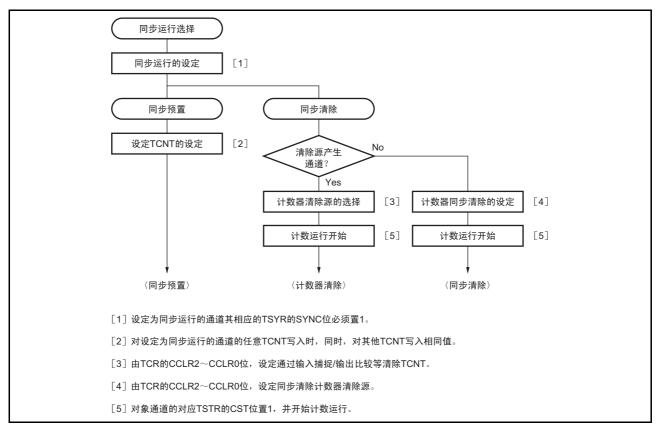

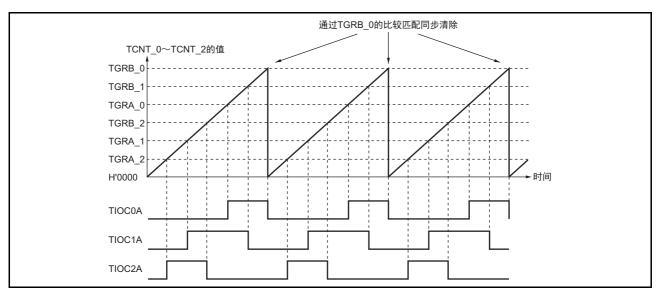

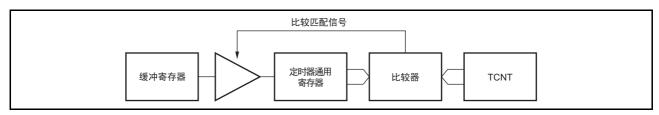

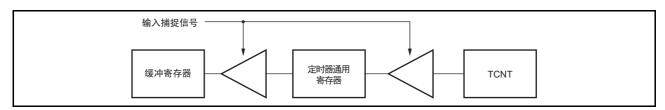

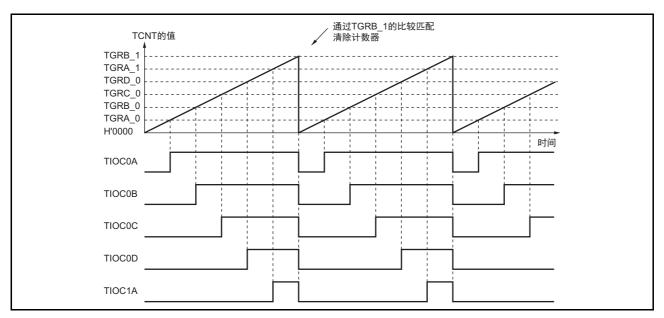

| 11.4.2  | 同步运行                                 | 339 |

|---------|--------------------------------------|-----|

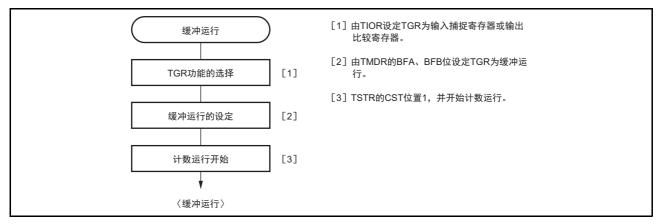

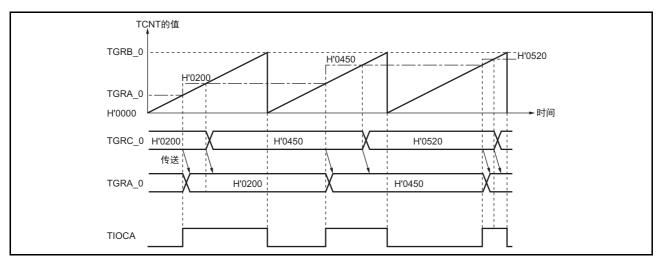

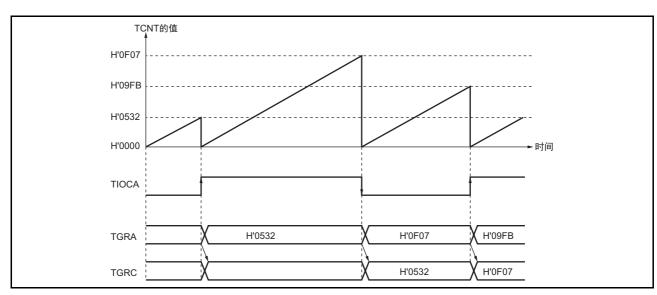

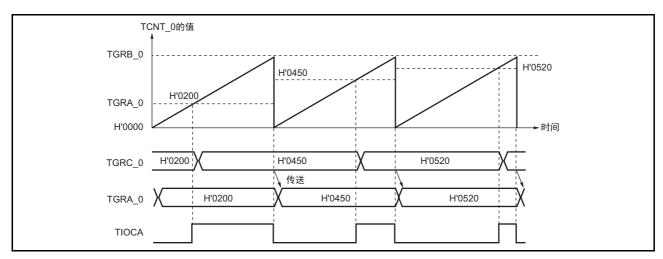

| 11.4.3  | 缓冲运行                                 | 340 |

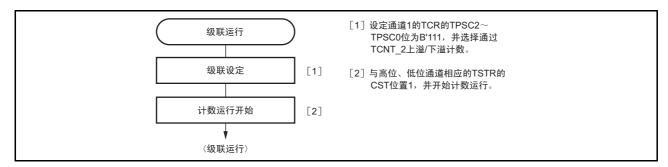

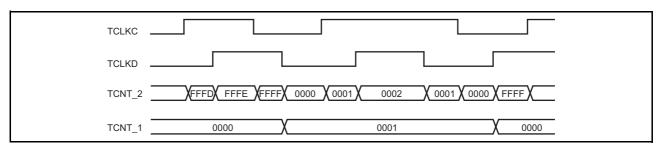

| 11.4.4  | 级联运行                                 | 344 |

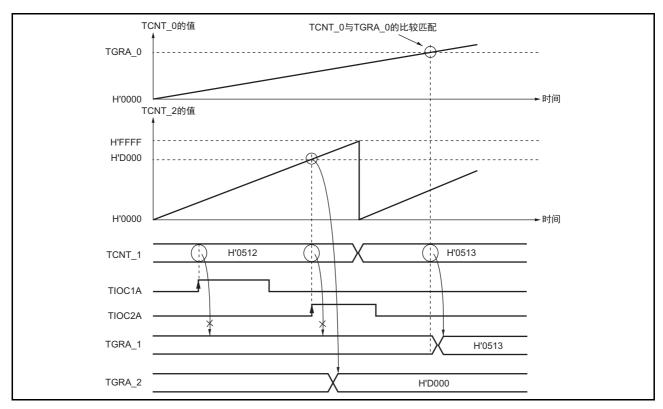

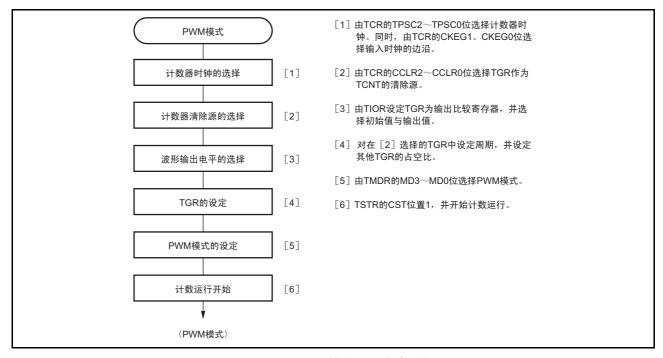

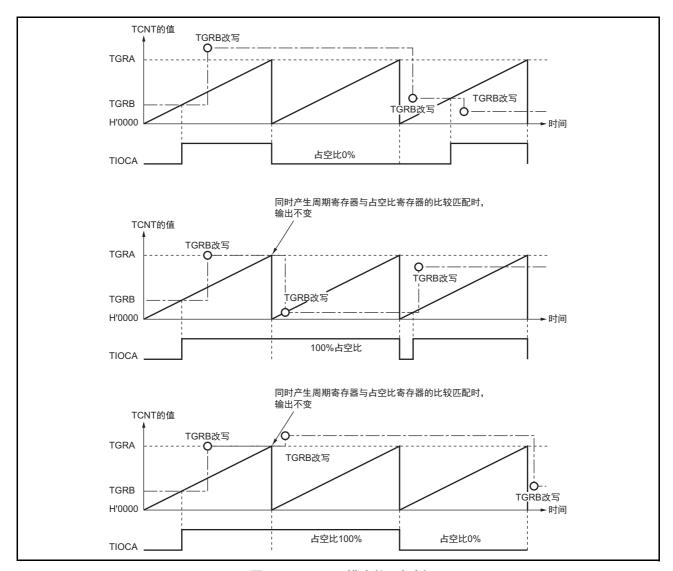

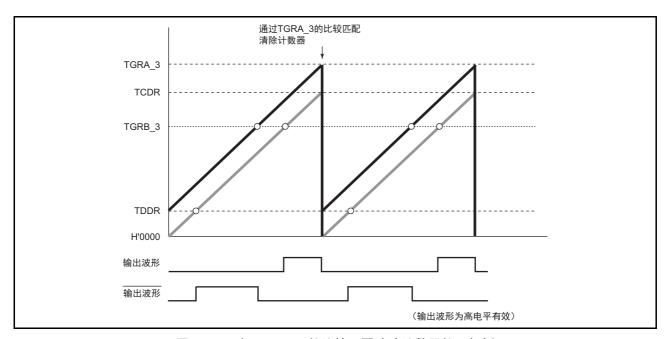

| 11.4.5  | PWM 模式                               | 348 |

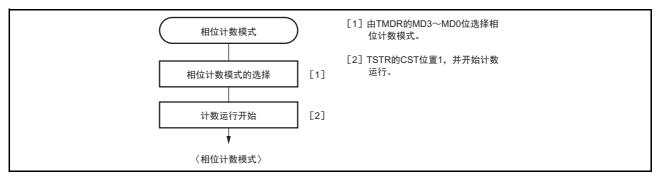

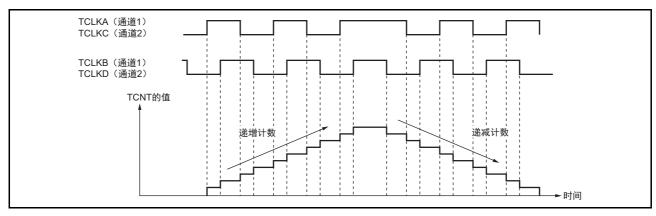

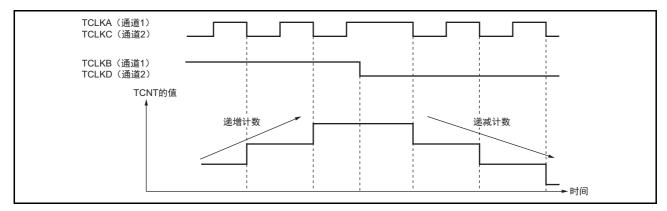

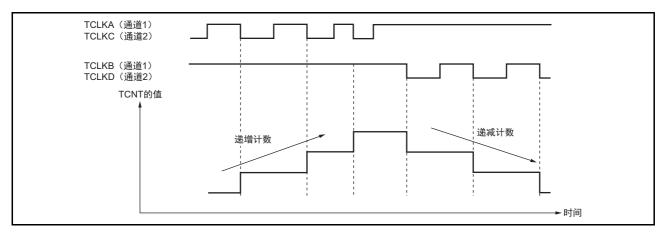

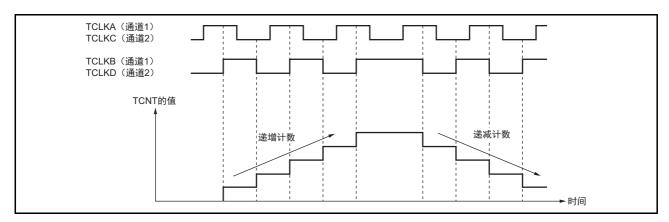

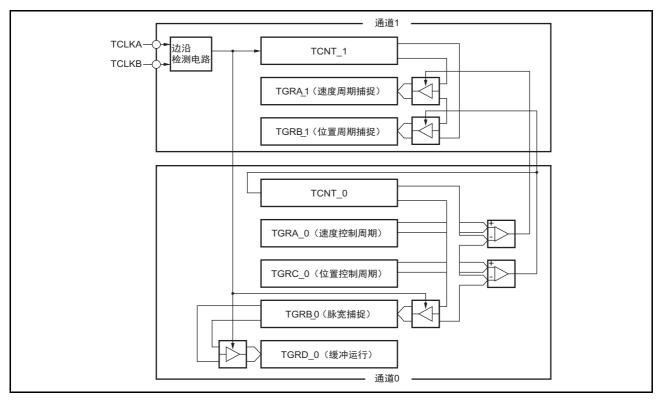

| 11.4.6  | 相位计数模式                               | 352 |

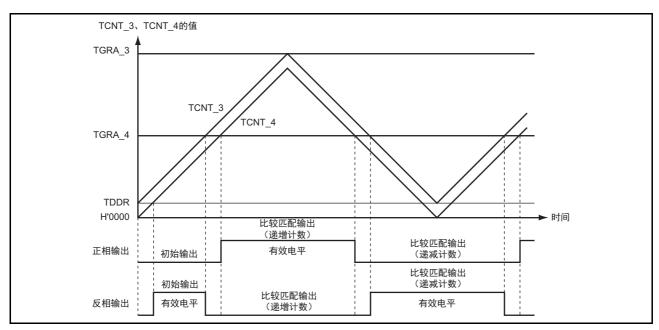

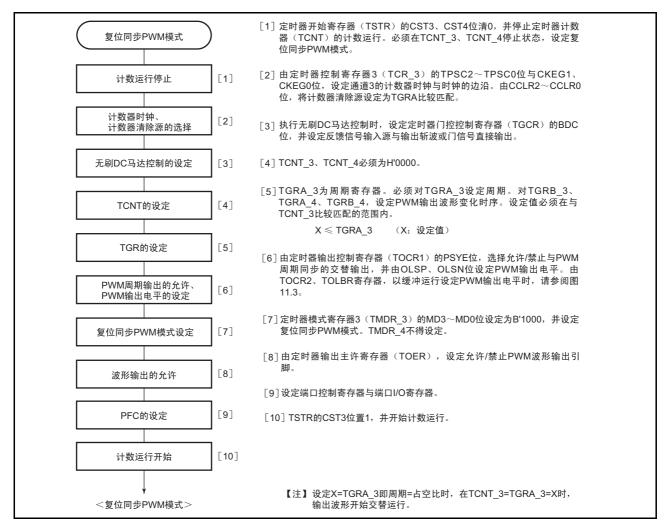

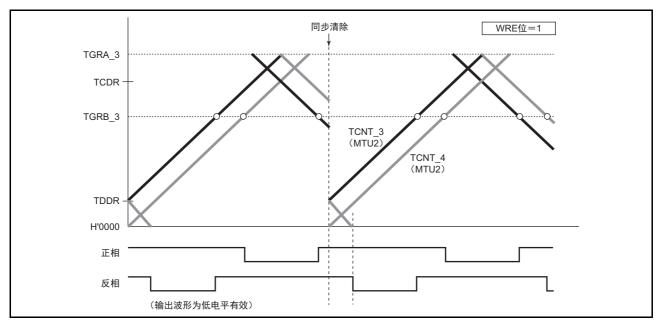

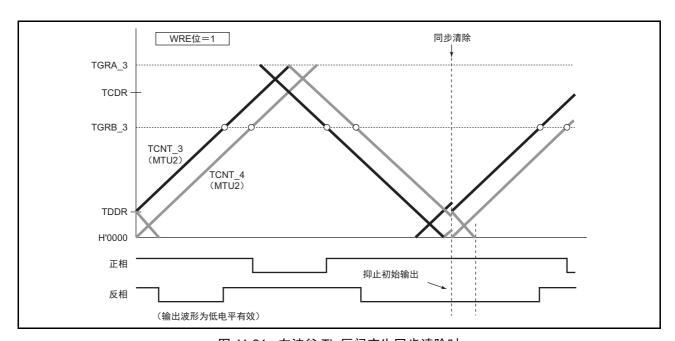

| 11.4.7  | 复位同步 PWM 模式                          | 358 |

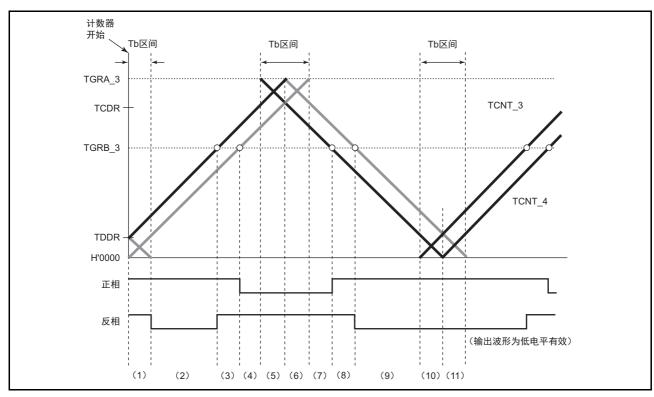

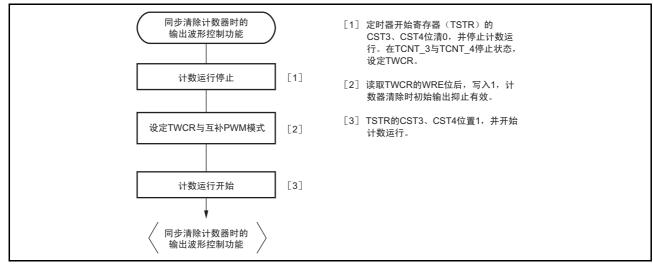

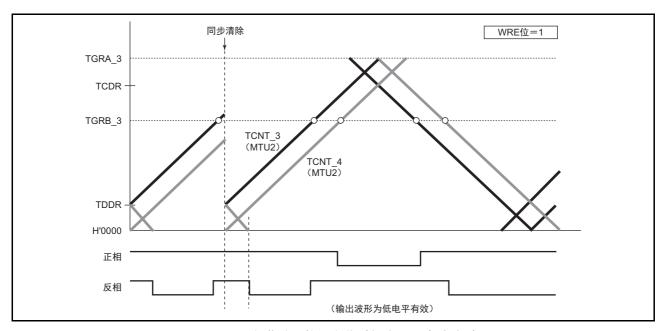

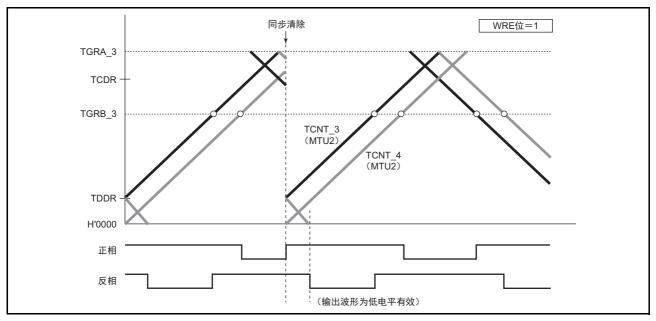

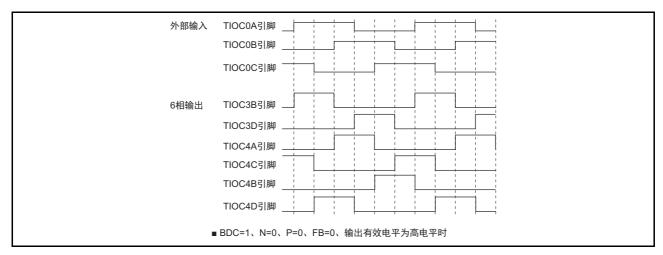

| 11.4.8  | 互补 PWM 模式                            | 360 |

| 11.4.9  | A/D 转换开始请求延迟功能                       | 388 |

| 11.4.10 | 互补 PWM 的 "波峰 / 波谷"的 TCNT 捕捉运行        | 391 |

| 11.5 中路 | <b>斤源</b>                            | 392 |

| 11.5.1  | 中断源和优先顺序                             | 392 |

| 11.5.2  | DMAC 的启动                             | 393 |

| 11.5.3  | A/D 转换器的启动                           | 393 |

| 11.6 运行 | f时序                                  | 395 |

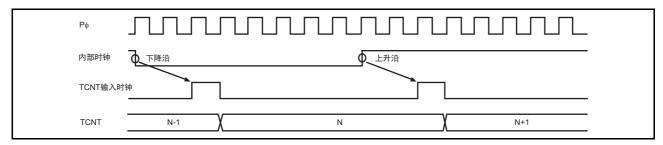

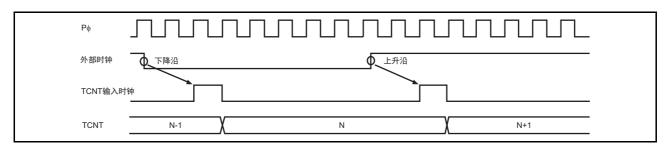

| 11.6.1  | 输入/输出时序                              | 395 |

| 11.6.2  | 中断信号时序                               | 400 |

| 11.7 使月 | ]时的注意事项                              | 403 |

| 11.7.1  | 模块待机模式的设定                            | 403 |

| 11.7.2  | 输入时钟的限制事项                            | 403 |

| 11.7.3  | 周期设定时的注意事项                           | 403 |

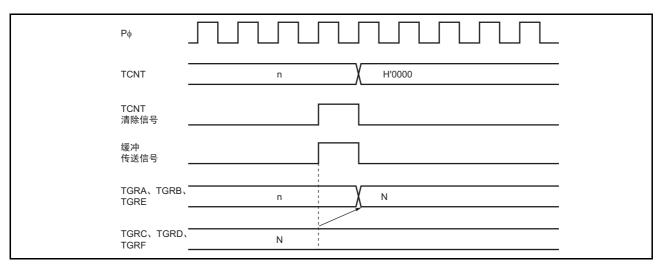

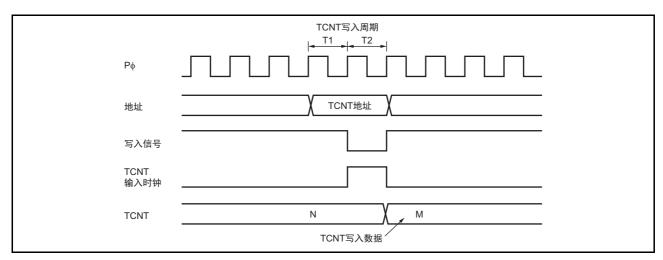

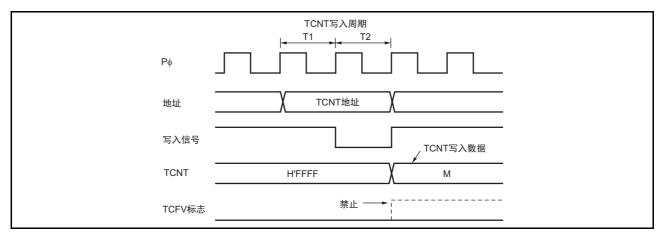

| 11.7.4  | TCNT 的写入和清除的竞争                       | 404 |

| 11.7.5  | TCNT 的写入和递增计数的竞争                     | 404 |

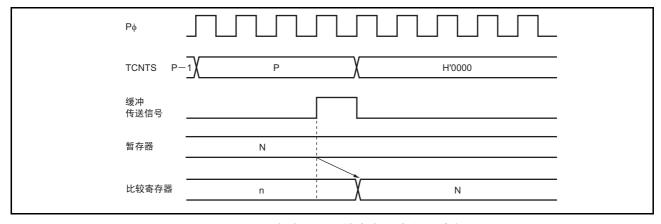

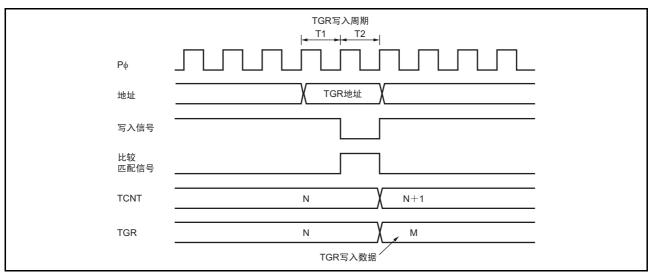

| 11.7.6  | TGR 的写入和比较匹配的竞争                      | 405 |

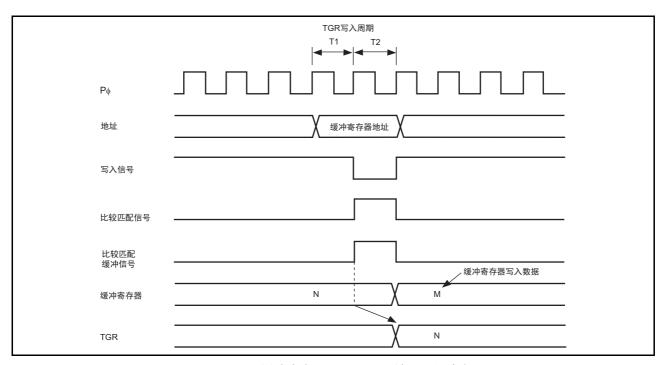

| 11.7.7  | 缓冲寄存器的写入和比较匹配的竞争                     | 405 |

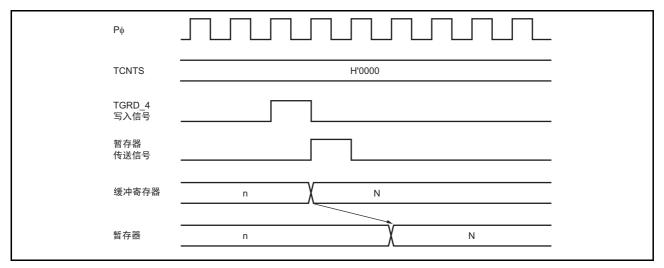

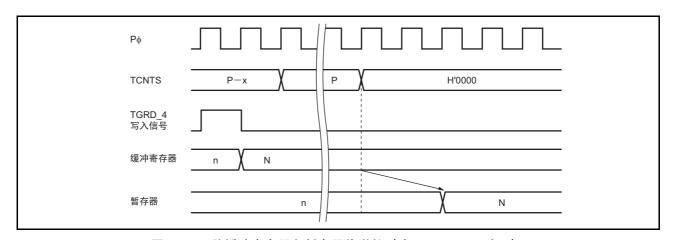

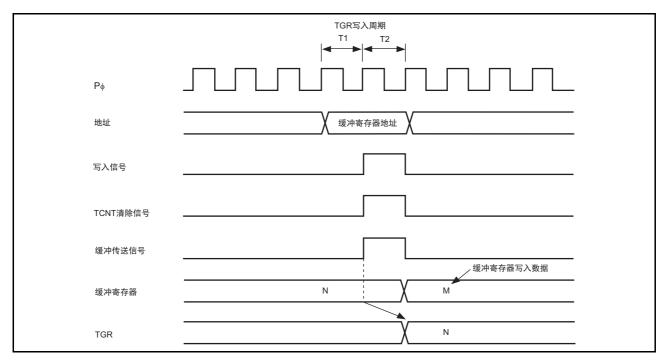

| 11.7.8  | 缓冲寄存器的写入和 TCNT 清除的竞争                 | 406 |

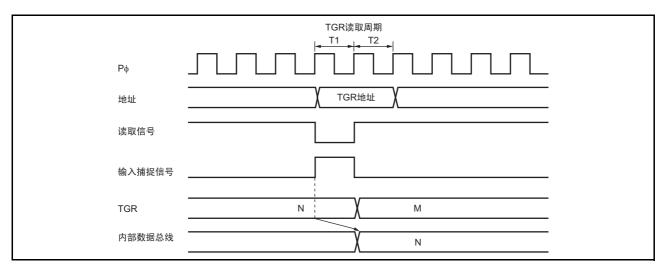

| 11.7.9  | TGR 的读取和输入捕捉的竞争                      | 406 |

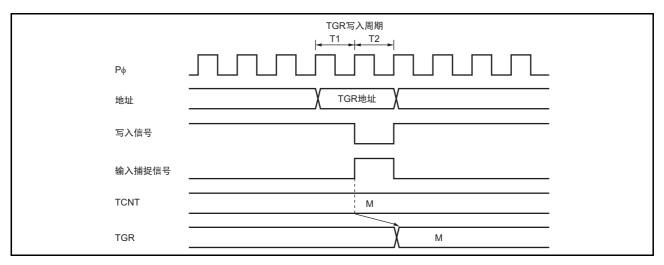

| 11.7.10 | TGR 的写入和输入捕捉的竞争                      | 407 |

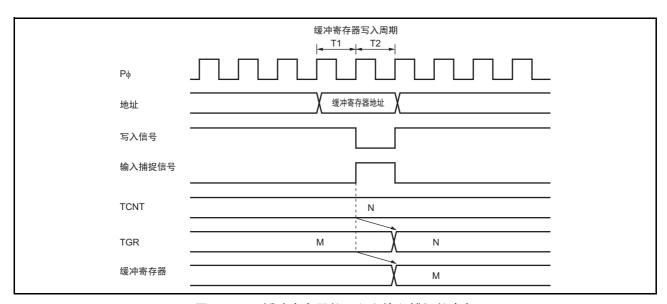

| 11.7.11 | 缓冲寄存器的写入和输入捕捉的竞争                     | 407 |

| 11.7.12 | 级联中 TCNT_2 的写入和上溢 / 下溢的竞争            | 408 |

| 11.7.13 | 互补 PWM 模式停止时的计数器值                    | 409 |

| 11.7.14 | 互补 PWM 模式时的缓冲运行的设定                   | 409 |

| 11.7.15 | 复位同步 PWM 模式的缓冲运行和比较匹配标志              | 410 |

| 11.7.16 | 复位同步 PWM 模式的上溢标志                     | 411 |

| 11.7.17 | 上溢 / 下溢和计数器清除的竞争                     | 411 |

| 11.7.18 | TCNT 的写入和上溢 / 下溢的竞争                  | 412 |

| 11.7.19 | 从普通运行或 PWM 模式 1 转移至复位同步 PWM 模式时的注意事项 | 412 |

| 11.7.20 | 互补 PWM 模式、复位同步 PWM 模式的输出电平           | 412 |

| 11.7.21 | 模块待机时的中断                             | 412 |

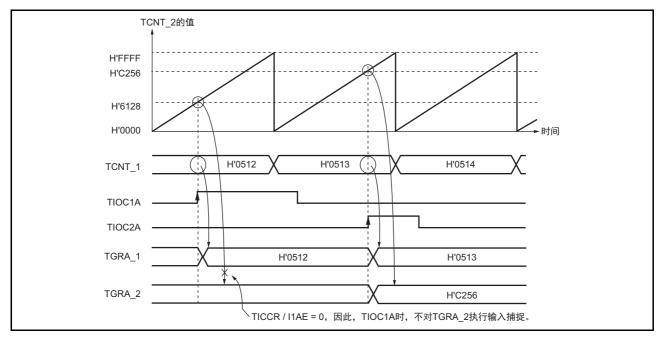

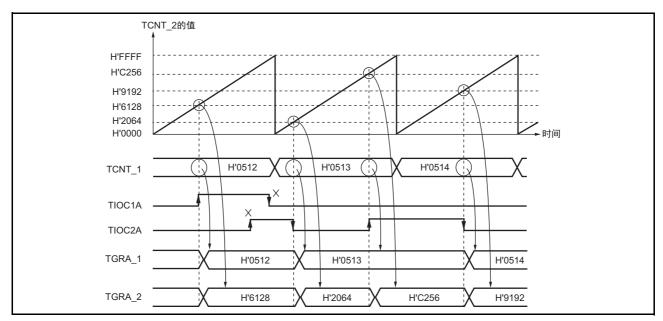

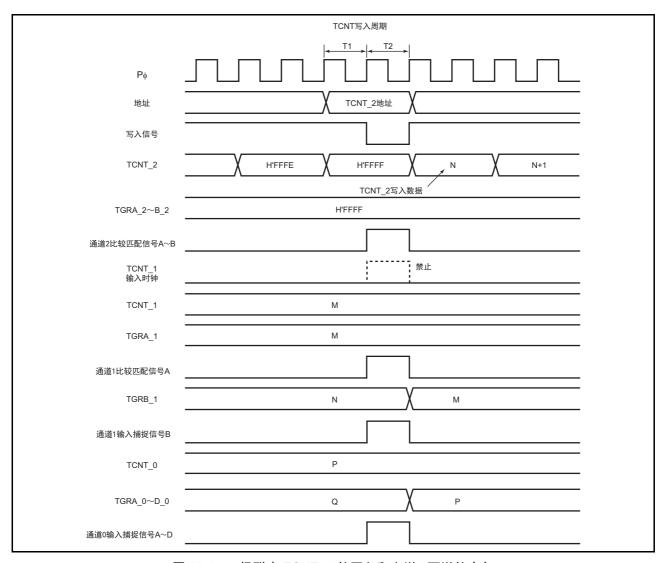

| 11.7.22 | 级联时 TCNT_1 和 TCNT_2 同时输入捕捉           | 413 |

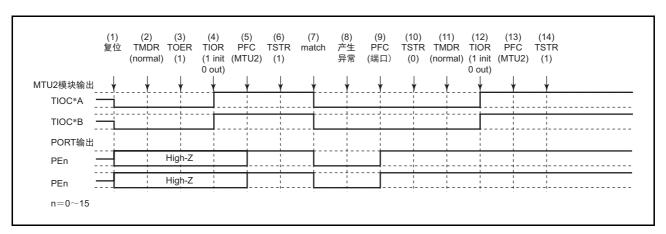

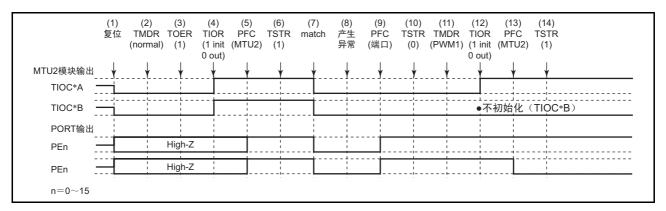

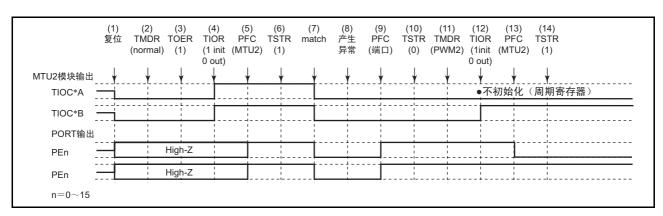

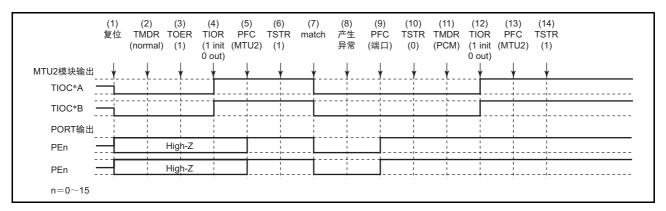

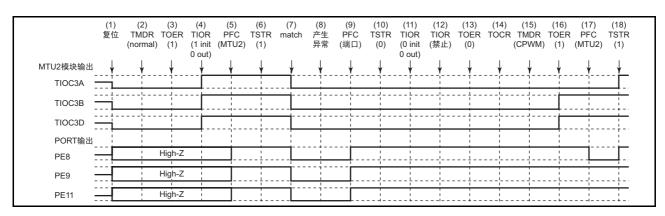

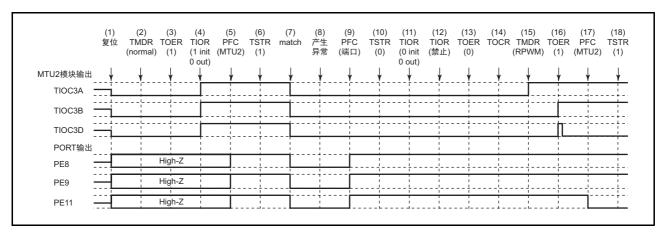

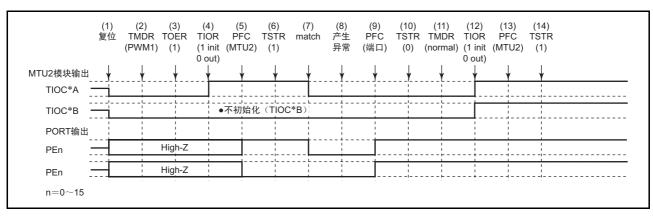

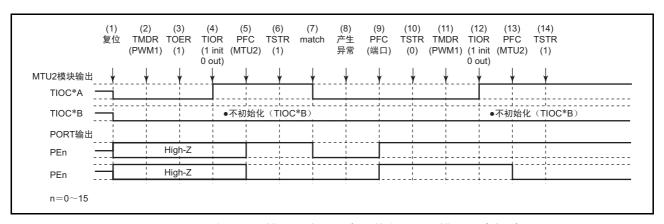

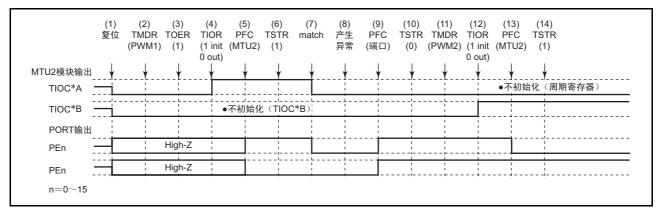

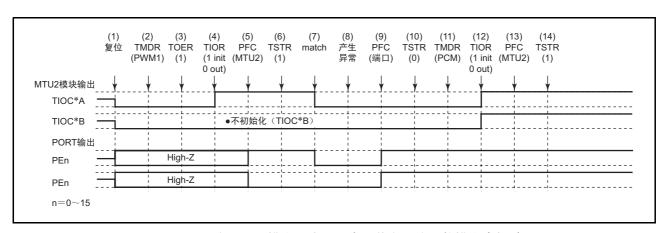

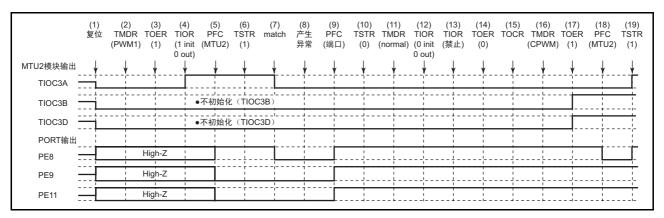

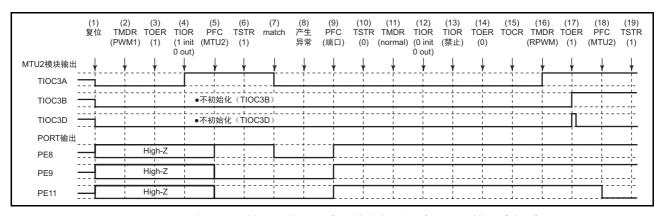

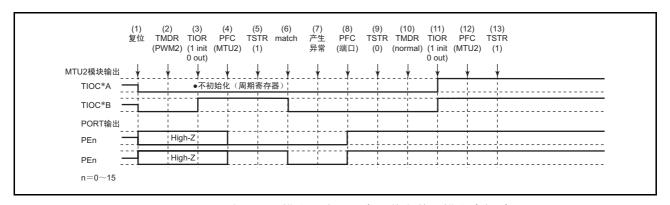

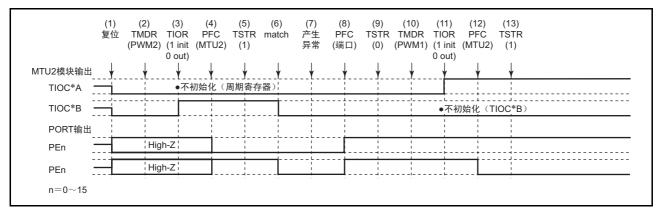

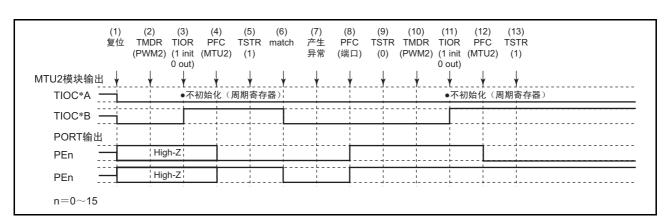

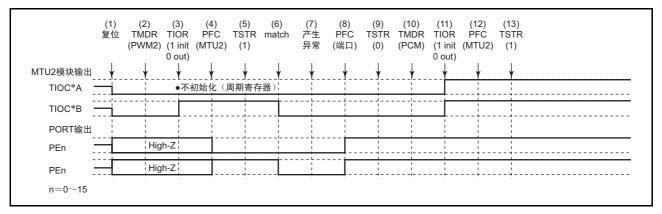

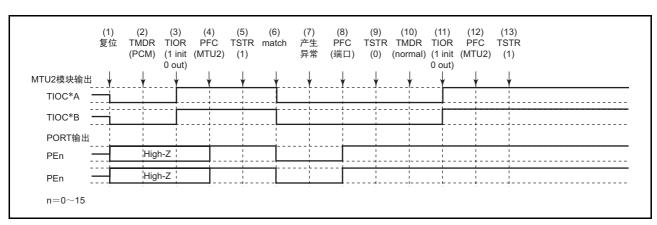

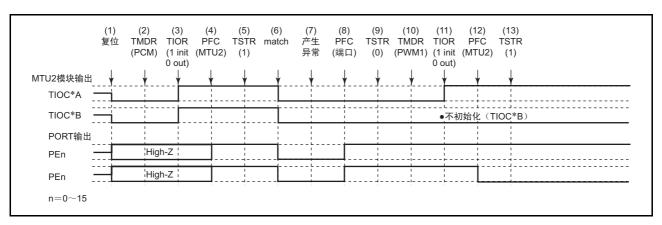

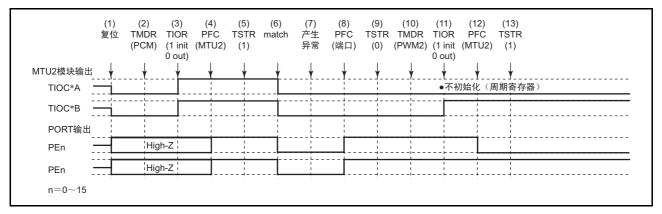

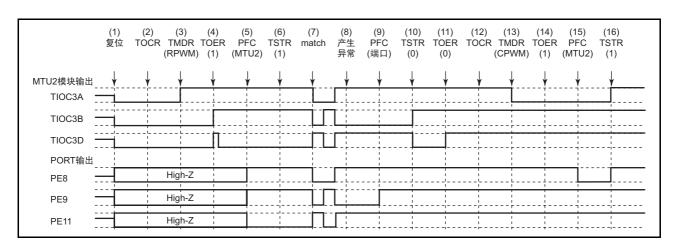

| 11.8 MT | U2 输出引脚的初始化方法                        | 413 |

| 11.8.1  | 运行模式                                 | 413 |

| 11.8.2  | 复位开始时的运行                             |     |

| 11.8.3  | 运行过程中因异常等而重新设定时的运行                   |     |

| 11.8.4  | 因运行过程中的异常等引起引脚初始化的步骤、模式转移的概要         | 414 |

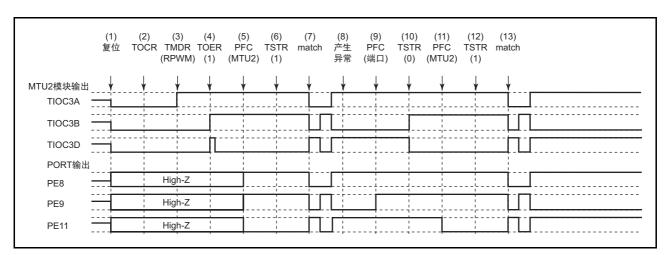

| 第 12 章  | 比较匹配定时器 (CMT)                        | 433 |

|         | 70 K = 20 K = 1                      |     |

|         | F器说明                                 |     |

| 12.2.1  | 比较匹配定时器开始寄存器 (CMSTR)                 |     |

| 12.2.2  | 比较匹配定时器控制 / 状态寄存器 (CMCSR)            |     |

| 12.2.3  | 比较匹配计数器(CMCNT)                       |     |

| 12.2.4  | 比较匹配常数寄存器(CMCOR)                     |     |

| 12.2.1  |                                      | 136 |

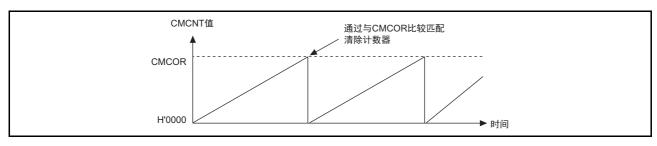

| 12.3.1  | 期间计数运行                   | 436 |

|---------|--------------------------|-----|

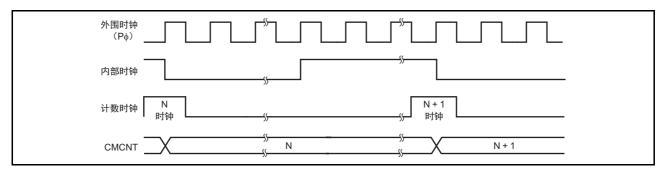

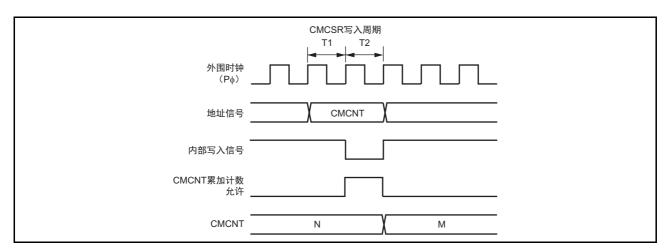

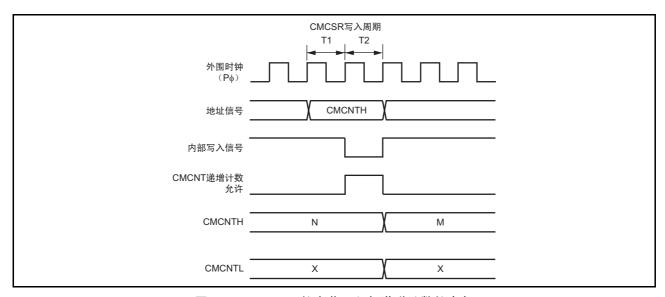

| 12.3.2  | CMCNT 计数时序               | 437 |

| 12.4 中勝 | ff                       | 437 |

| 12.4.1  | 中断源与 DMA 传送请求            | 437 |

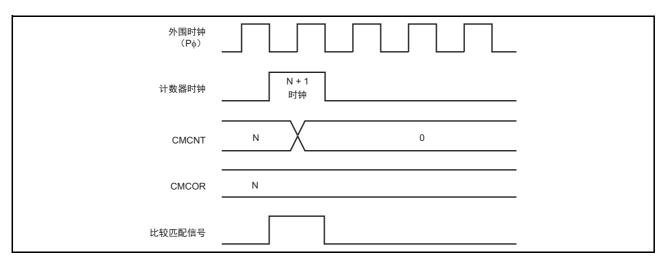

| 12.4.2  | 比较匹配标志的置位时序              | 437 |

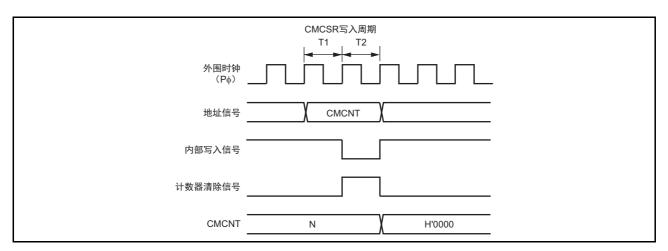

| 12.4.3  | 比较匹配标志的清除时序              | 438 |

| 12.5 使月 | 目时的注意事项                  | 438 |

| 12.5.1  | CMCNT 的写入与比较匹配的竞争        | 438 |

| 12.5.2  | CMCNT 的字写入与递增计数的竞争       | 438 |

| 12.5.3  | CMCNT 的字节写入与递增计数的竞争      | 439 |

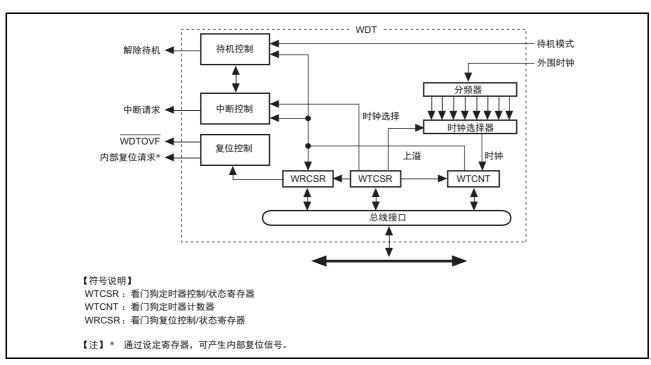

| 第 13 章  | 看门狗定时器 (WDT)             | 440 |

| , , ,   | <u> </u>                 |     |

|         | ∖/输出引脚                   |     |

| 13.3 寄有 | 字器说明                     |     |

| 13.3.1  | 看门狗定时器计数器 (WTCNT)        |     |

| 13.3.2  | 看门狗定时器控制 / 状态寄存器 (WTCSR) |     |

| 13.3.3  | 看门狗复位控制 / 状态寄存器 (WRCSR)  | 443 |

| 13.3.4  | 寄存器存取时的注意事项              | 444 |

| 13.4 WD | <b>)T</b> 的使用方法          |     |

| 13.4.1  | 软件待机模式的解除步骤              | 445 |

| 13.4.2  | 频率更改步骤                   |     |

| 13.4.3  | 看门狗定时器模式的使用方法            | 445 |

| 13.4.4  | 间隔定时器模式的使用方法             |     |

| 13.5 使用 | 月时的注意事项                  | 447 |

| 13.5.1  | 定时器误差                    | 447 |

| 13.5.2  | 禁止设定 H'FF 为 WTCNT 的设定值   |     |

| 13.5.3  | 间隔定时器上溢标志                |     |

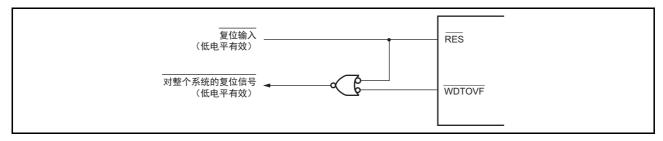

| 13.5.4  | WDTOVF 信号引起的系统复位         | 447 |

| 13.5.5  | 看门狗定时器模式的手动复位            | 447 |

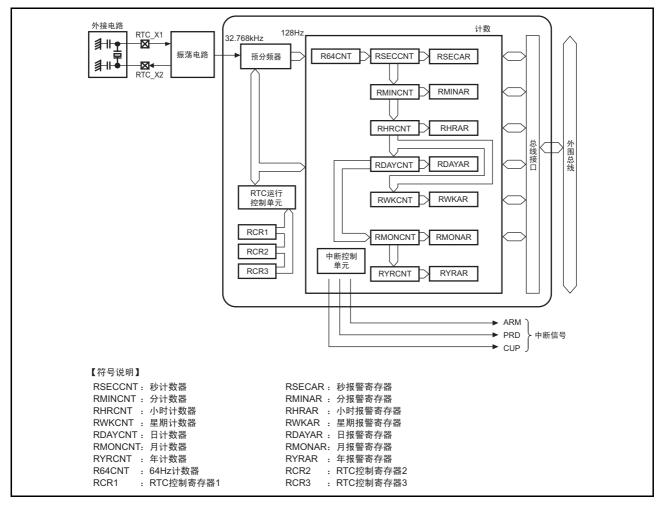

| 第 14 章  | 实时时钟 (RTC)               |     |

|         | 点                        |     |

|         | ∖/输出引脚                   |     |

| 14.3 寄有 | 字器说明                     |     |

| 14.3.1  | 64Hz 计数器 (R64CNT)        |     |

| 14.3.2  | 秒计数器(RSECCNT)            |     |

| 14.3.3  | 分计数器 (RMINCNT)           |     |

| 14.3.4  | 小时计数器(RHRCNT)            |     |

| 14.3.5  | 星期计数器(RWKCNT)            |     |

| 14.3.6  | 日计数器 (RDAYCNT)           |     |

| 14.3.7  | 月计数器 (RMONCNT)           |     |

| 14.3.8  | 年计数器(RYRCNT)             |     |

| 14.3.9  | 秒报警寄存器 (RSECAR)          |     |

| 14.3.10 | 分报警寄存器(RMINAR)           |     |

| 14.3.11 | 小时报警寄存器 (RHRAR)          |     |

| 14.3.12 | 星期报警寄存器 (RWKAR)          | 456 |

| 14.3.13 | 日报警寄存器 (RDAYAR)          | 457 |

| 14.3.14 | 月报警寄存器 (RMONAR)          | 457 |

| 14.3.15 | 年报警寄存器(RYRAR)            | 458 |

| 14.3.16 | RTC 控制寄存器 1 (RCR1)       | 458 |

| 14.3.17 | RTC 控制寄存器 2 (RCR2)       | 459 |

| 14.3.18 | RTC 控制寄存器 3 (RCR3)       | 460 |

| 14.4 运行 | 行说明                                |     |

|---------|------------------------------------|-----|

| 14.4.1  | 上电后寄存器的初始设定                        | 460 |

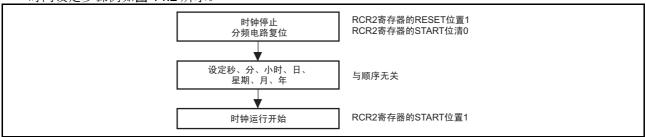

| 14.4.2  | 时间设定步骤                             | 461 |

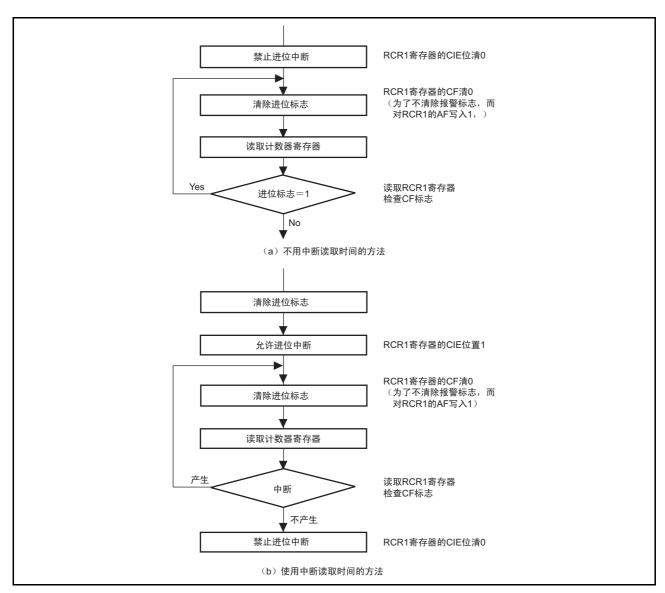

| 14.4.3  | 时间读取步骤                             | 461 |

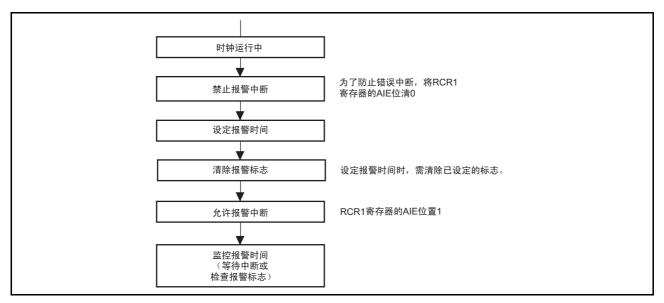

| 14.4.4  | 报警功能                               | 462 |

| 14.5 使月 | 用时的注意事项                            |     |

| 14.5.1  | 关于 RTC 计数运行时的寄存器写入                 | 463 |

| 14.5.2  | 关于实时时钟 (RTC) 周期中断的使用               | 463 |

| 14.5.3  | 寄存器设定后的待机转移                        | 463 |

| 14.5.4  | 读取/写入寄存器时的注意事项                     | 463 |

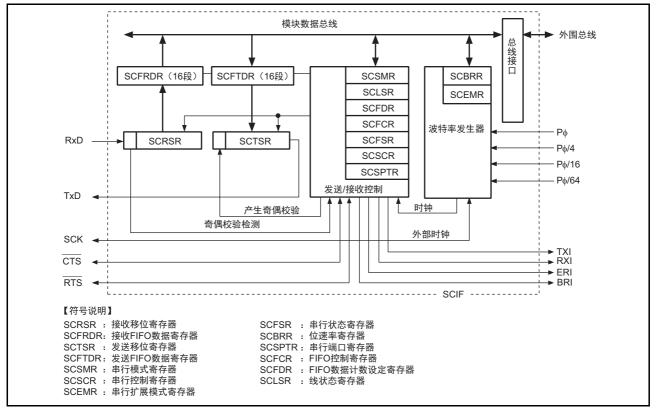

| 第 15 章  | 带 FIFO 的串行通信接口 (SCIF)              | 464 |

| ,       | 点                                  |     |

|         | 入 / 输出引脚                           |     |

| 15.3 寄花 | 存器说明                               |     |

| 15.3.1  | 接收移位寄存器 (SCRSR)                    |     |

| 15.3.2  | 接收 FIFO 数据寄存器 (SCFRDR)             |     |

| 15.3.3  | 发送移位寄存器 (SCTSR)                    |     |

| 15.3.4  | 发送 FIFO 数据寄存器 (SCFTDR)             |     |

| 15.3.5  | 串行模式寄存器 (SCSMR)                    |     |

| 15.3.6  | 串行控制寄存器 (SCSCR)                    |     |

| 15.3.7  | 串行状态寄存器 (SCFSR)                    | 472 |

| 15.3.8  | 位速率寄存器 (SCBRR)                     | 476 |

| 15.3.9  | FIFO 控制寄存器 (SCFCR)                 |     |

| 15.3.10 | FIFO 数据计数设定寄存器 (SCFDR)             | 485 |

| 15.3.11 | 串行端口寄存器 (SCSPTR)                   |     |

| 15.3.12 | 线状态寄存器 (SCLSR)                     | 487 |

| 15.3.13 | 串行扩展模式寄存器 (SCEMR)                  | 488 |

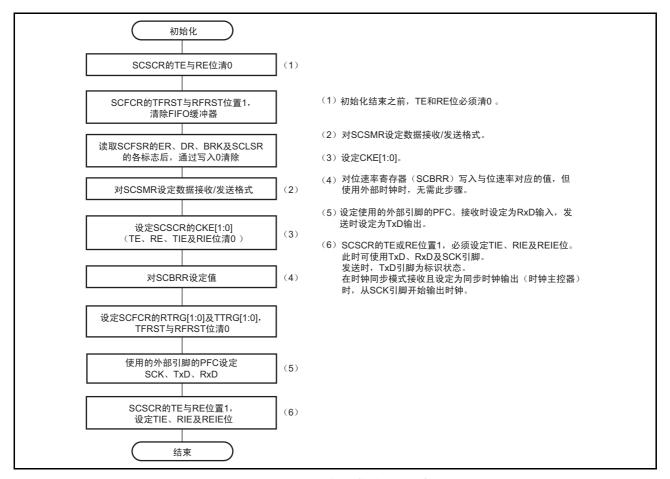

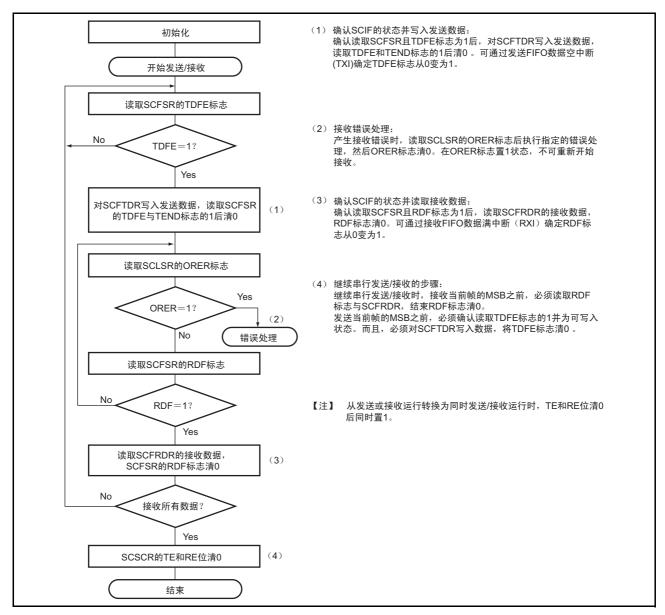

| 15.4 运行 | 行说明                                | 489 |

| 15.4.1  | 概要                                 | 489 |

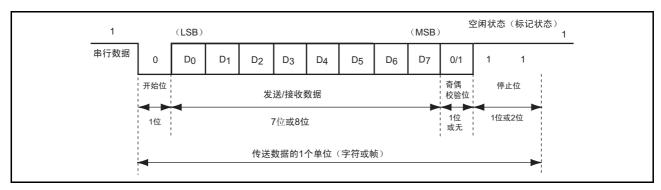

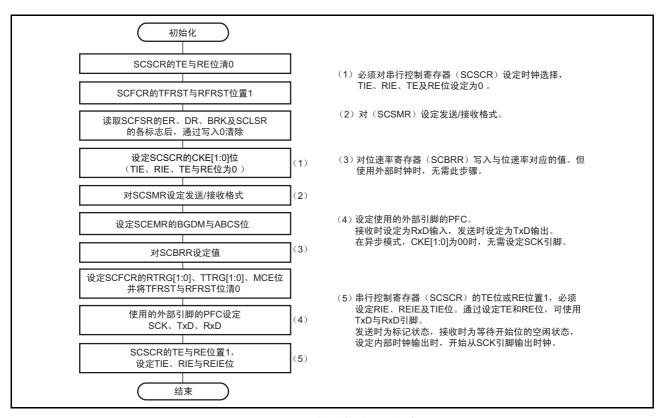

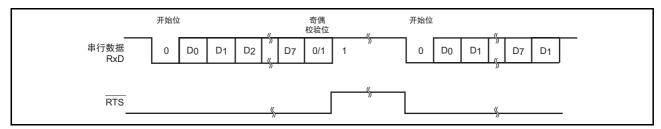

| 15.4.2  | 异步模式时的运行                           |     |

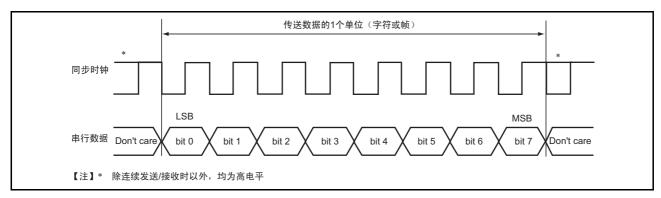

| 15.4.3  | 时钟同步模式时的运行                         | 498 |

| 15.5 SC | IF 的中断                             | 505 |

| 15.6 使月 | 用时的注意事项                            | 505 |

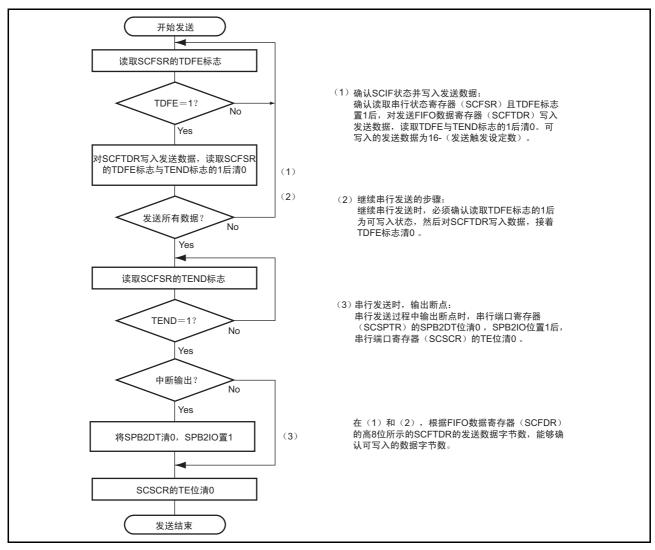

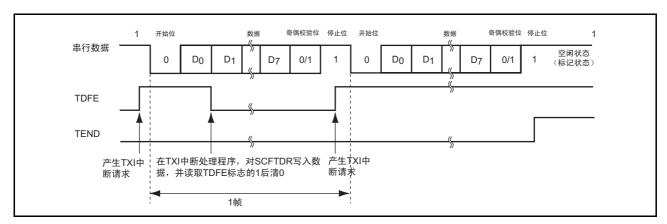

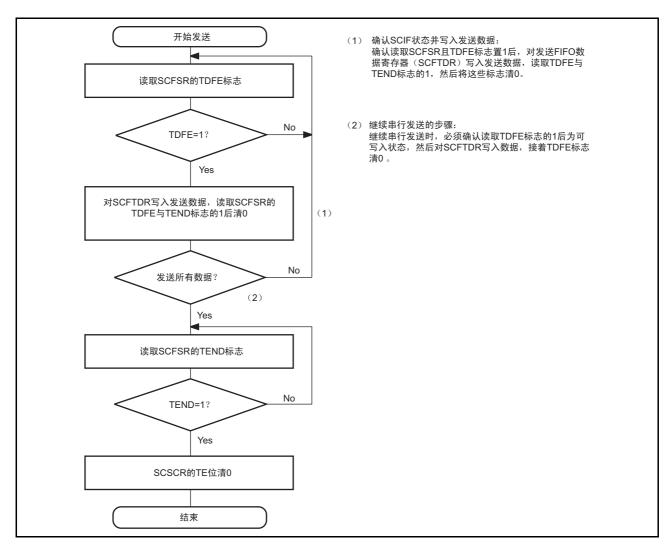

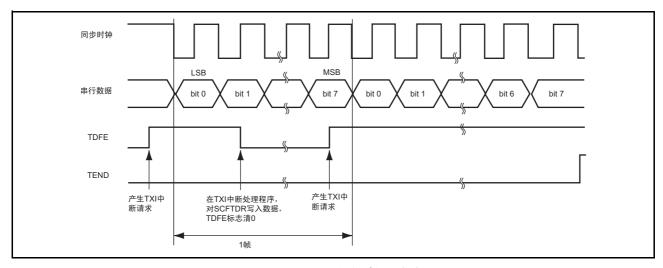

| 15.6.1  | 向 SCFTDR 的写入和 TDFE 标志              | 505 |

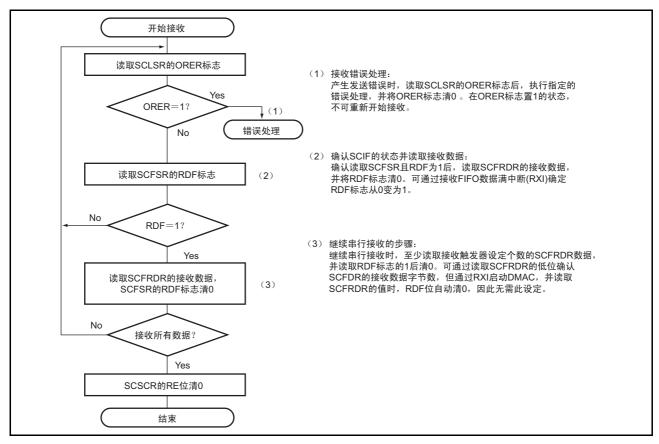

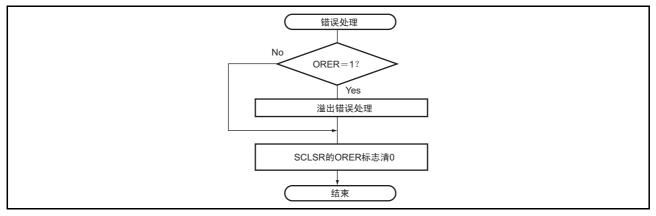

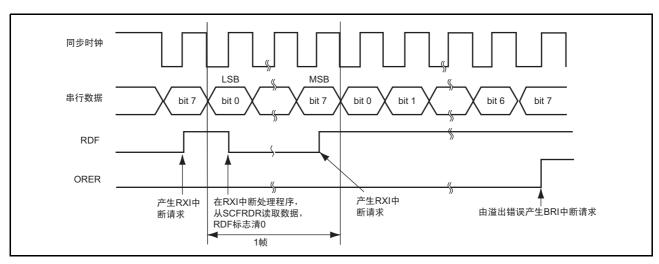

| 15.6.2  | SCFRDR 的读取和 RDF 标志                 | 505 |

| 15.6.3  | DMAC 使用时的限制事项                      | 506 |

| 15.6.4  | 断点的检测和处理                           | 506 |

| 15.6.5  | 断点的发送                              | 506 |

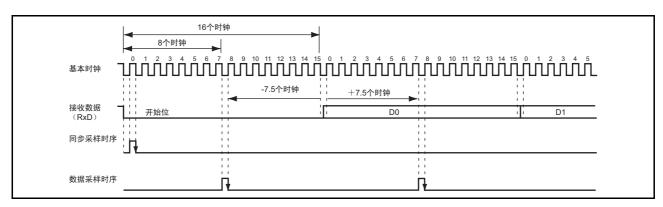

| 15.6.6  | 异步模式的接收数据采样时序与接收容限                 | 506 |

| 15.6.7  | 选择异步基本时钟                           | 507 |

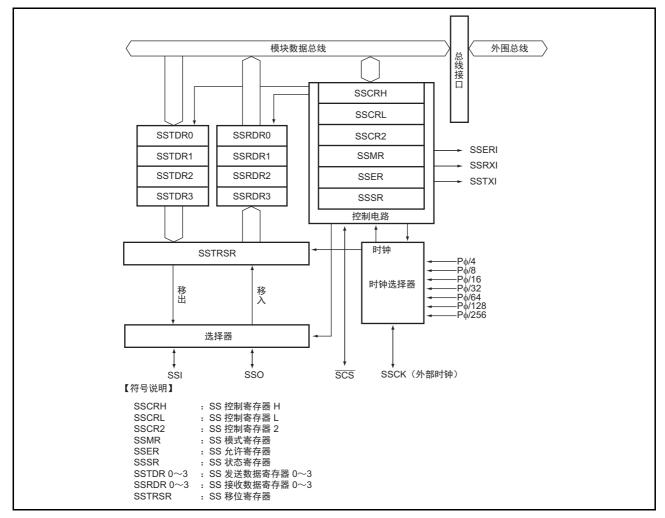

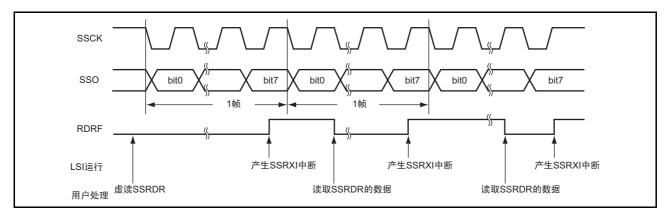

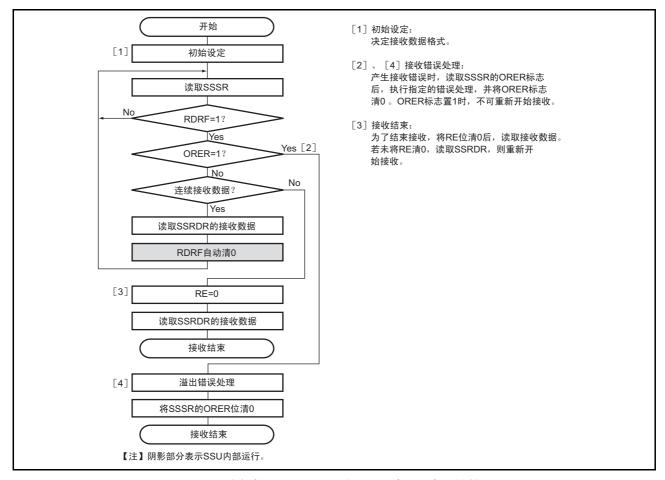

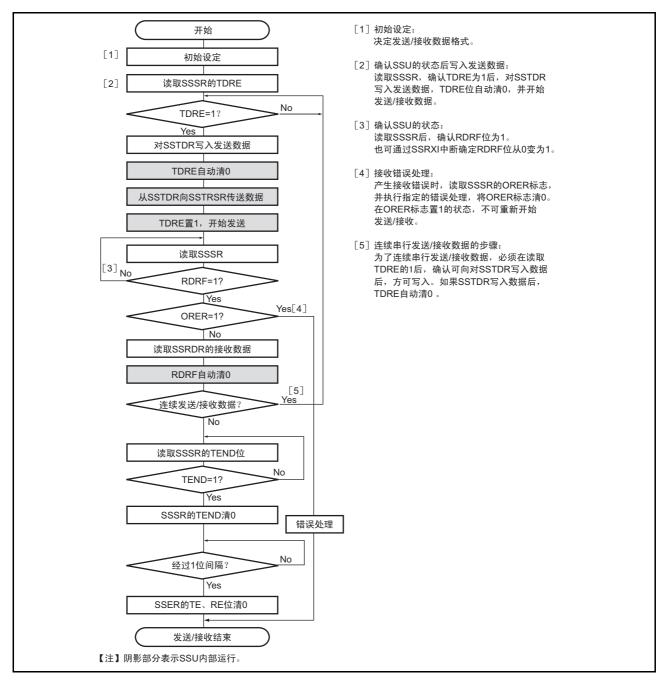

| 第 16 章  | 同步串行通信单元 (SSU)                     | 508 |

| 16.1 特力 | 点                                  | 508 |

| 16.2 输力 | 入 / 输出引脚                           | 510 |

| 16.3 寄花 | 存器说明                               | 510 |

| 16.3.1  | SS 控制寄存器 H (SSCRH)                 | 511 |

| 16.3.2  | SS 控制寄存器 L (SSCRL)                 | 512 |

| 16.3.3  | SS 模式寄存器 (SSMR)                    | 513 |

| 16.3.4  | SS 允许寄存器 (SSER)                    | 514 |

| 16.3.5  | SS 状态寄存器 (SSSR)                    | 515 |

| 16.3.6  | SS 控制寄存器 2 (SSCR2)                 | 517 |

| 16.3.7  | SS 发送数据寄存器 0 ~ 3 (SSTDR0 ~ SSTDR3) | 518 |

| 16.3.8   | SS 接收数据寄存器 0~3 (SSRDR0~ SSRDR3)    | 519 |

|----------|------------------------------------|-----|

| 16.3.9   | SS 移位寄存器 (SSTRSR)                  | 519 |

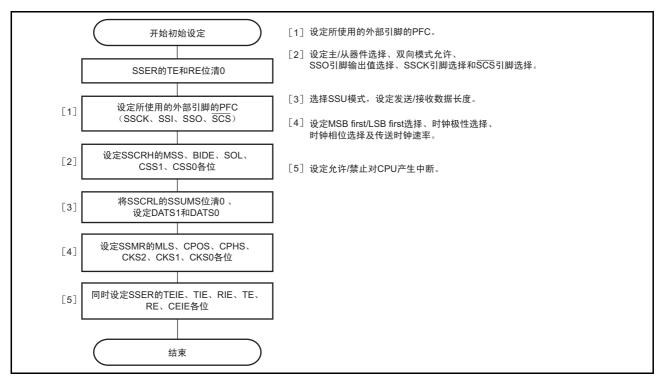

| 16.4 运行  | 行说明                                | 520 |

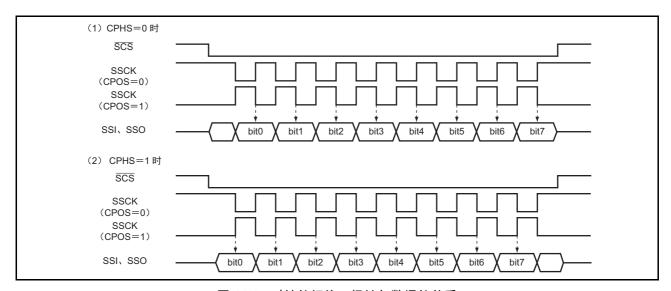

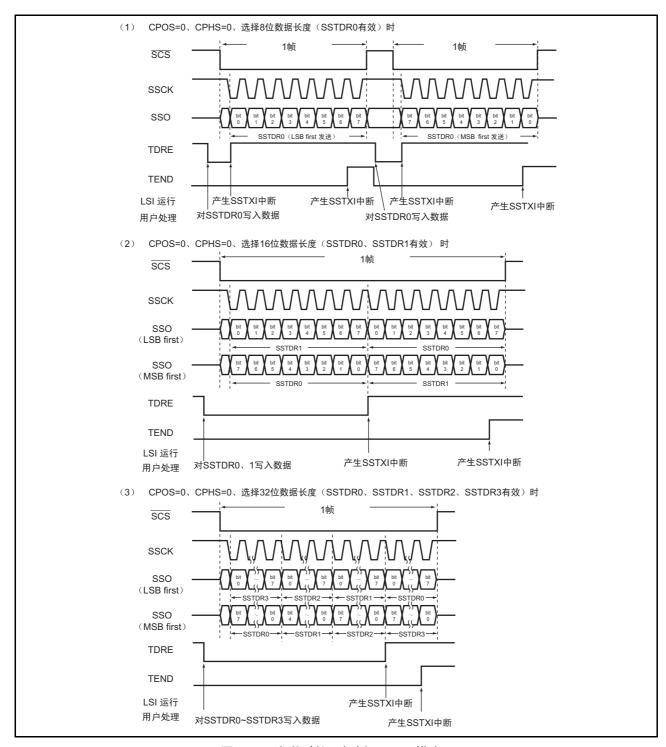

| 16.4.1   | 传送时钟                               | 520 |

| 16.4.2   | 时钟的相位、极性与数据的关系                     |     |

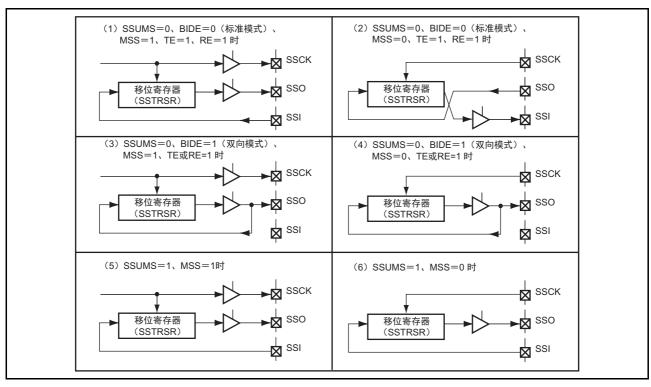

| 16.4.3   | 数据输入/输出引脚与移位寄存器的关系                 | 521 |

| 16.4.4   | 各通信模式与引脚功能                         | 522 |

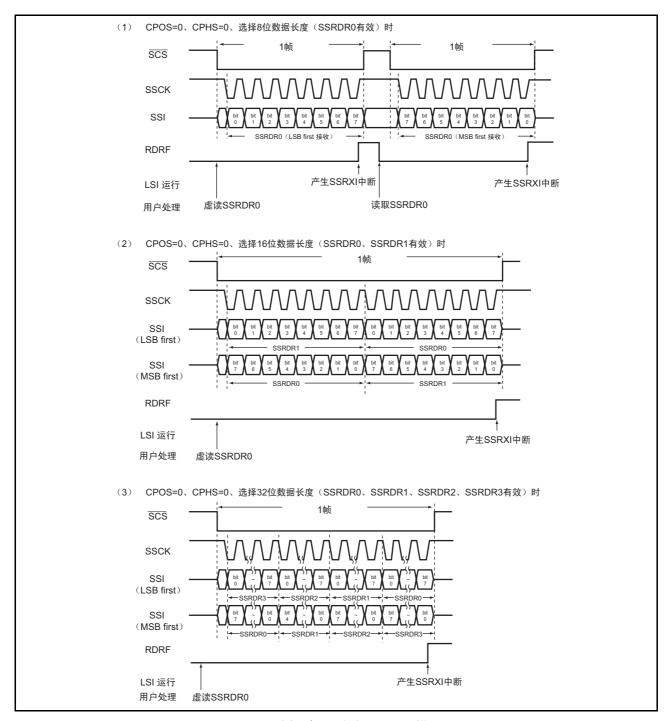

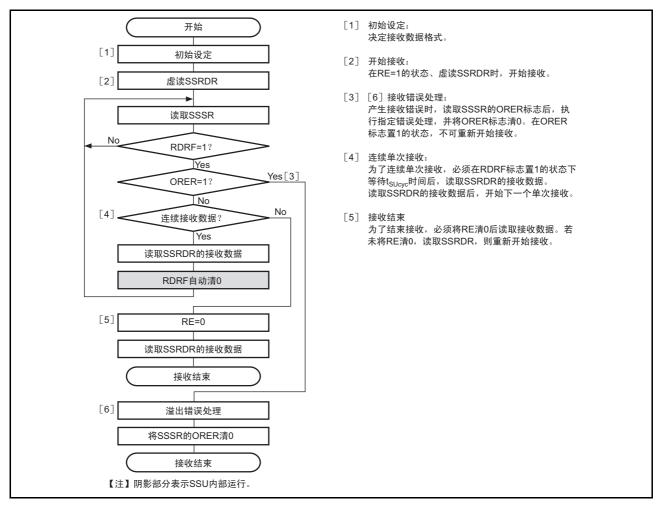

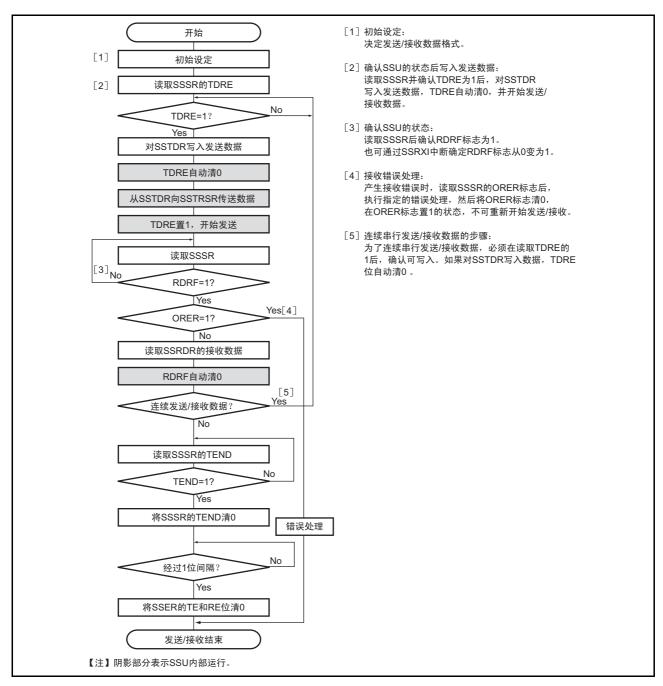

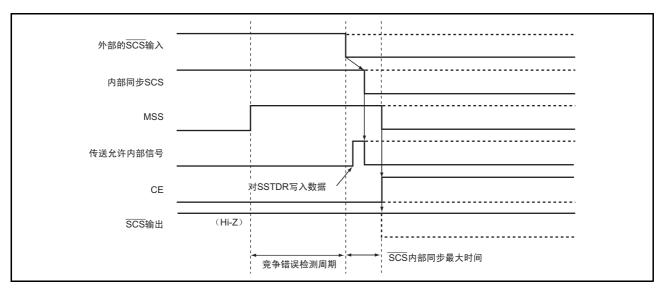

| 16.4.5   | SSU 模式                             |     |

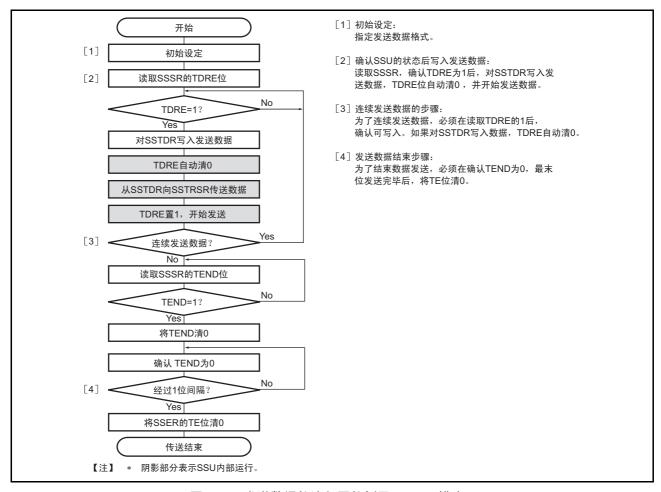

| 16.4.6   |                                    | 530 |

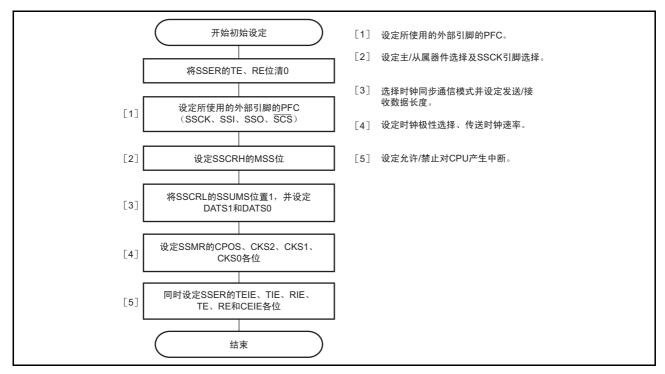

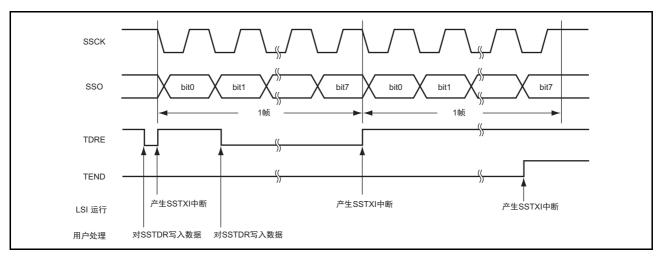

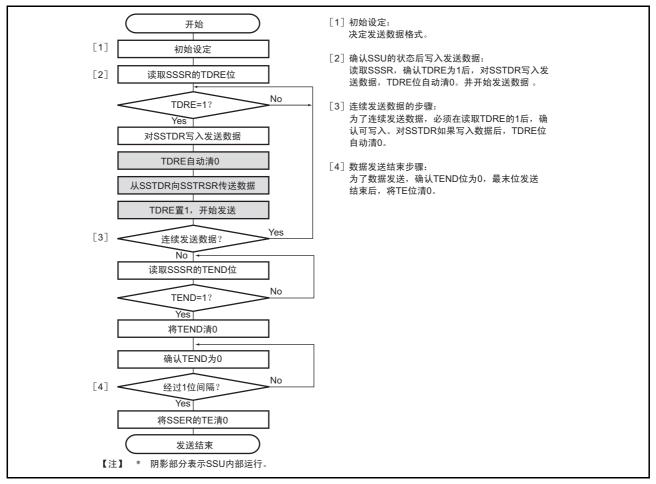

| 16.4.7   | 时钟同步通信模式                           | 531 |

| 16.5 SSU | U 的中断源与 DMAC                       | 536 |

| 16.6 使月  | 用时的注意事项                            | 536 |

| 16.6.1   | 模块待机模式的设定                          | 536 |

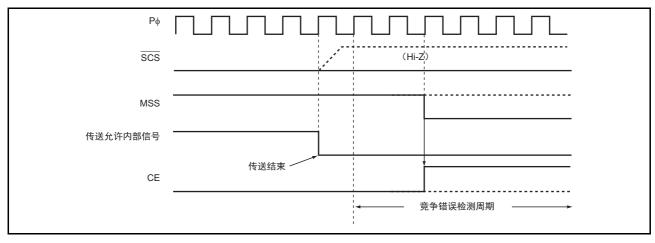

| 16.6.2   | 在 SSU 从属模式连续发送 / 接收时的注意事项          | 536 |

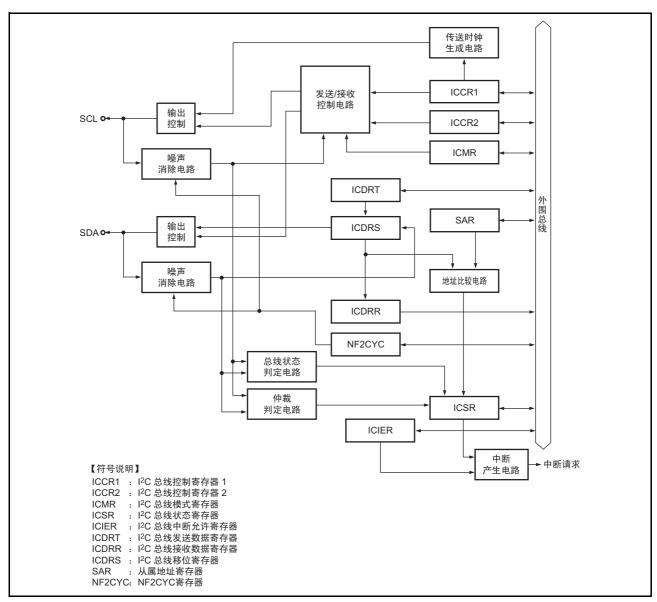

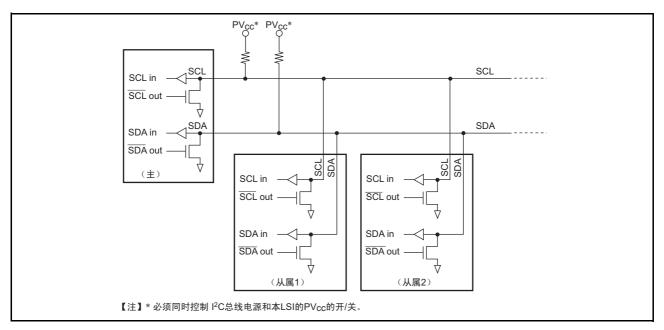

| 第 17 章   | I <sup>2</sup> C 总线接口 3 (IIC3)     | 537 |

|          | 点                                  |     |

| 17.2 输力  | 入 / 输出引脚                           | 539 |

| 17.3 寄石  | 存器说明                               |     |

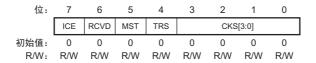

| 17.3.1   | I <sup>2</sup> C 总线控制寄存器 1 (ICCR1) | 541 |

| 17.3.2   | I <sup>2</sup> C 总线控制寄存器 2 (ICCR2) | 543 |

| 17.3.3   | I <sup>2</sup> C 总线模式寄存器 (ICMR)    | 544 |

| 17.3.4   | I <sup>2</sup> C 总线中断允许寄存器 (ICIER) | 545 |

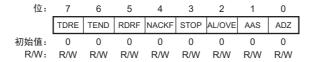

| 17.3.5   | I <sup>2</sup> C 总线状态寄存器 (ICSR)    | 546 |

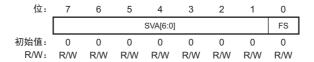

| 17.3.6   | 从属地址寄存器 (SAR)                      | 548 |

| 17.3.7   | I <sup>2</sup> C 总线发送数据寄存器 (ICDRT) | 548 |

| 17.3.8   | I <sup>2</sup> C 总线接收数据寄存器 (ICDRR) | 548 |

| 17.3.9   | I <sup>2</sup> C 总线移位寄存器 (ICDRS)   | 549 |

| 17.3.10  | NF2CYC 寄存器 (NF2CYC)                | 549 |

| 17.4 运行  | 行说明                                | 550 |

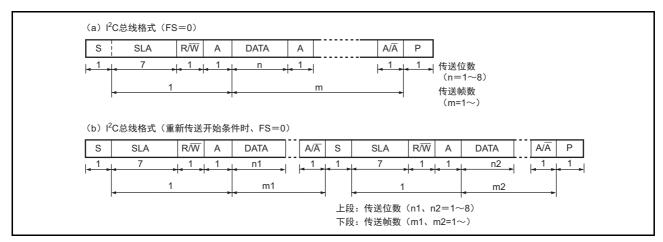

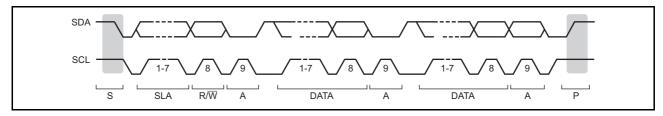

| 17.4.1   | I <sup>2</sup> C 总线格式              | 550 |

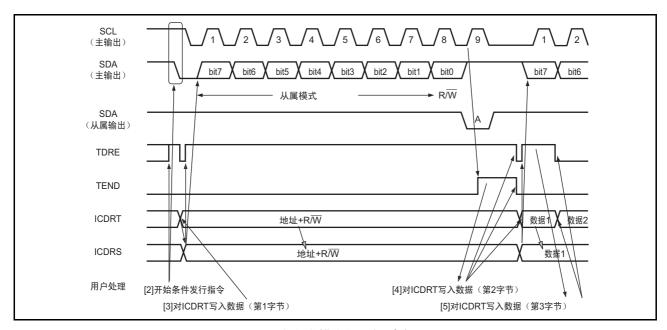

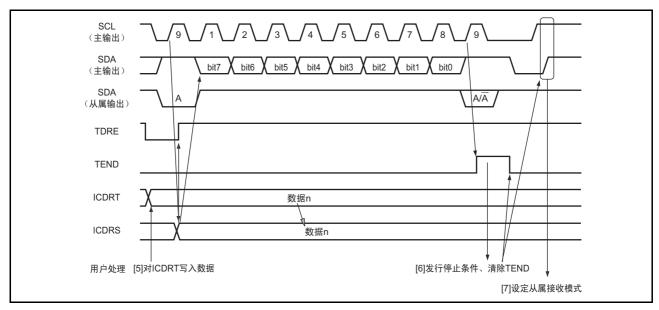

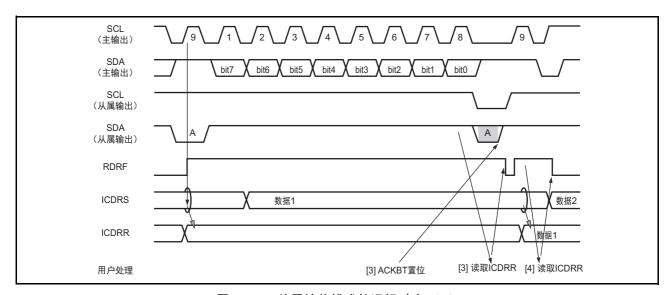

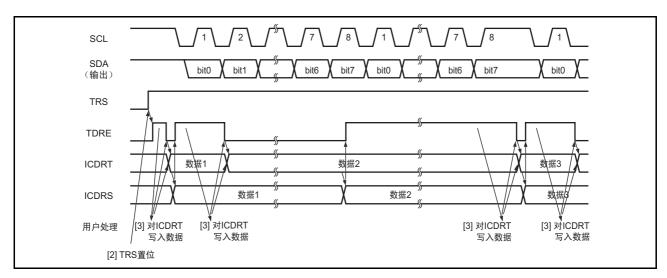

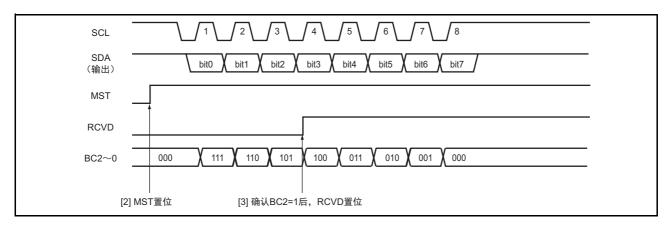

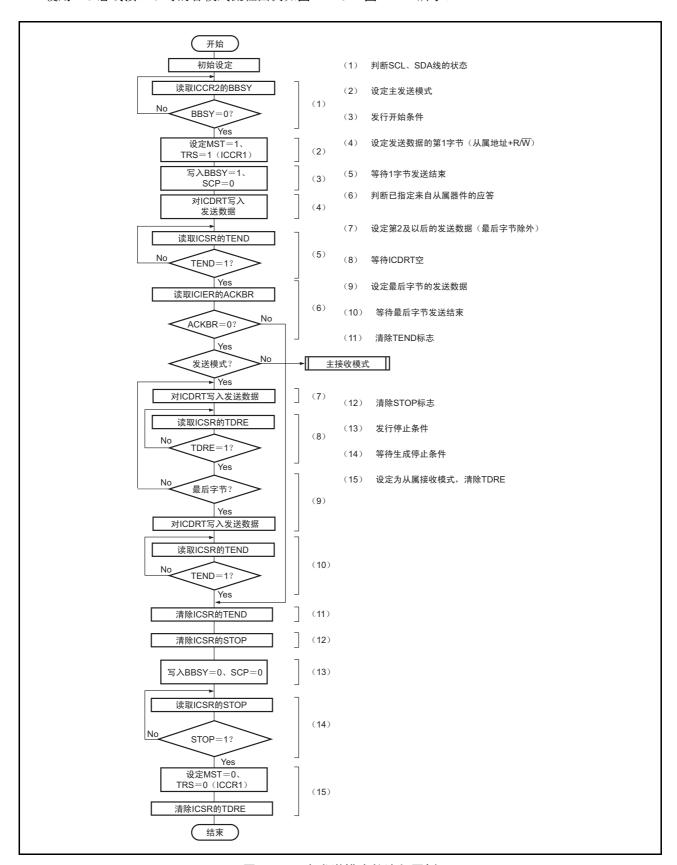

| 17.4.2   | 主发送运行                              | 551 |

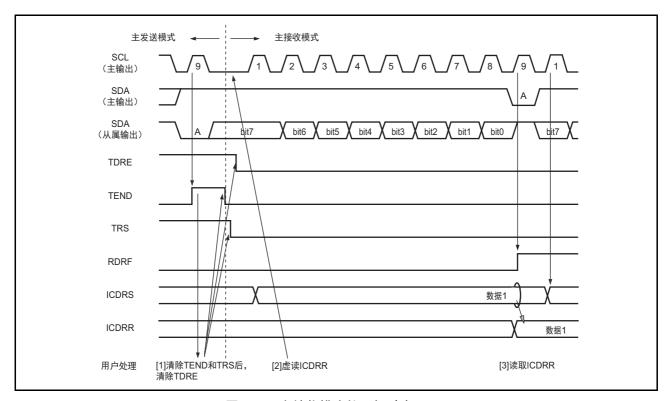

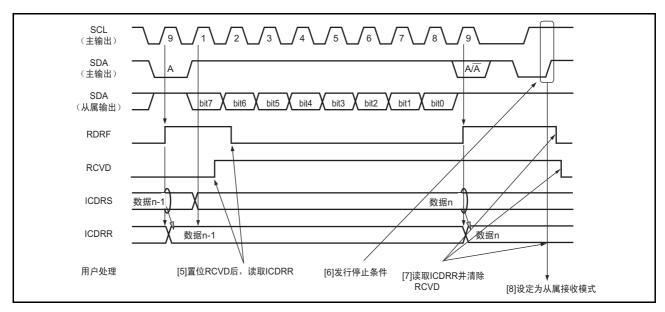

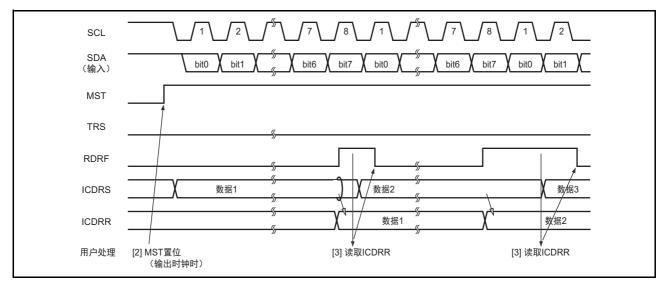

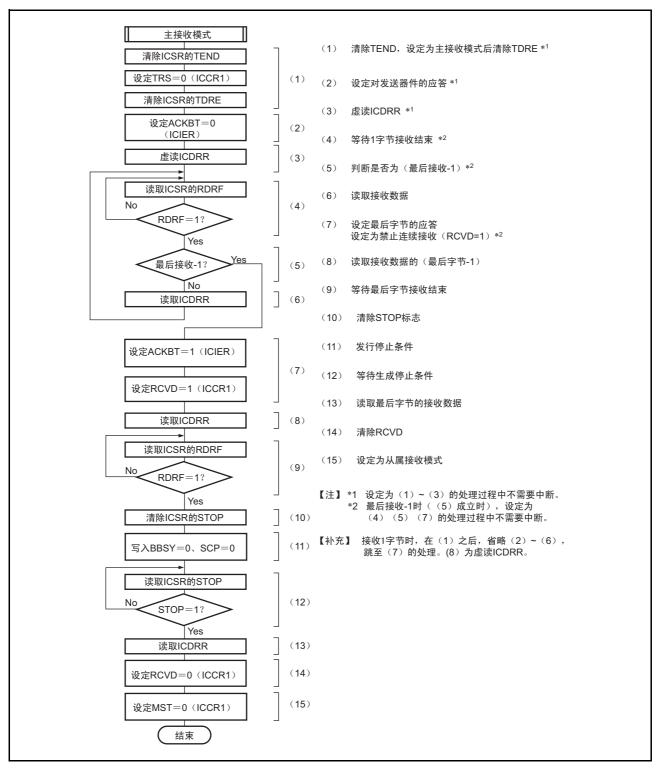

| 17.4.3   | 主接收运行                              | 552 |

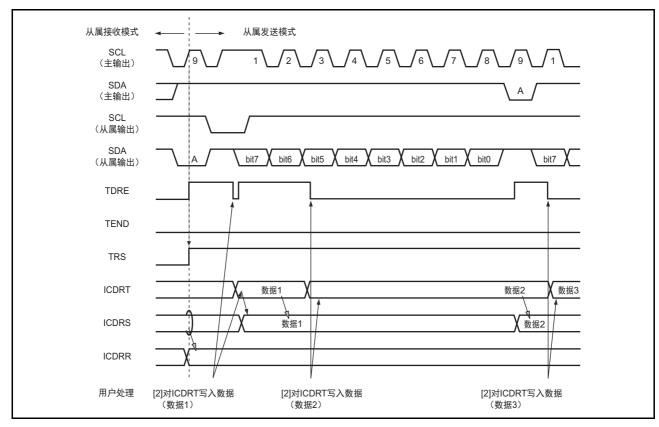

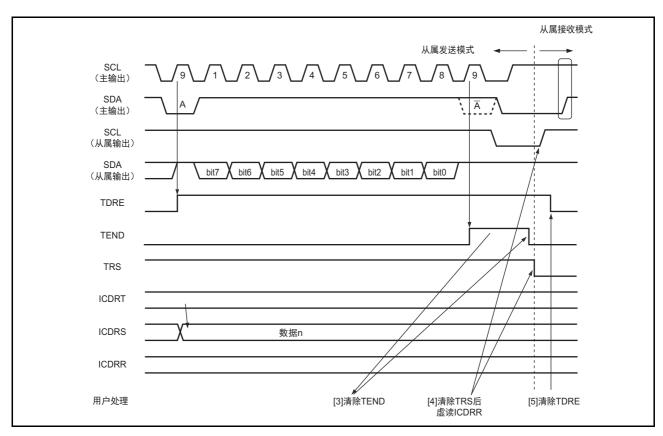

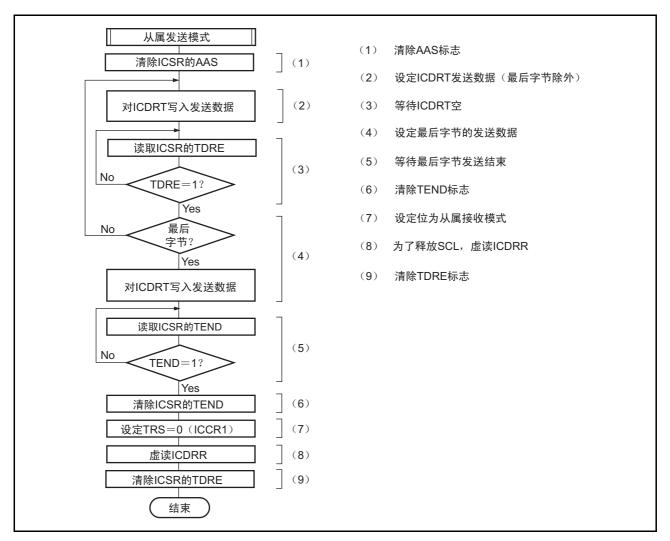

| 17.4.4   | 从属发送运行                             | 554 |

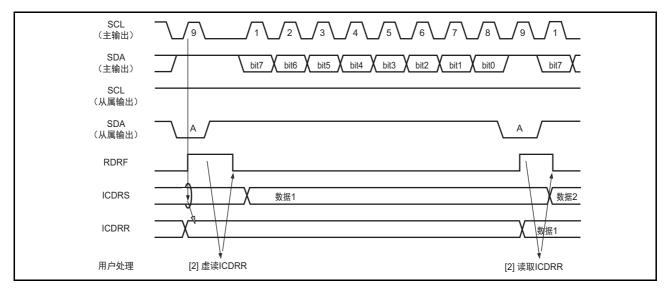

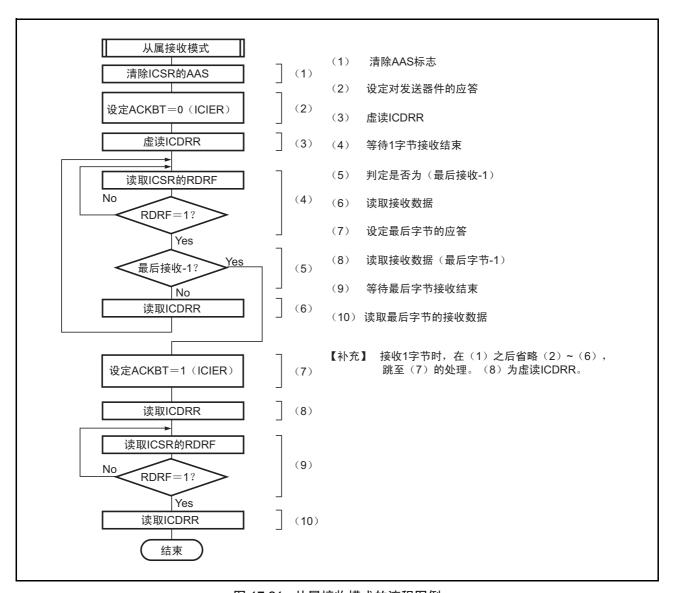

| 17.4.5   | 从属接收运行                             |     |

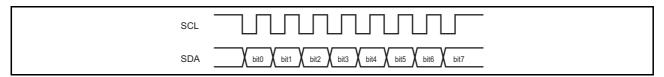

| 17.4.6   | 时钟同步串行格式                           |     |

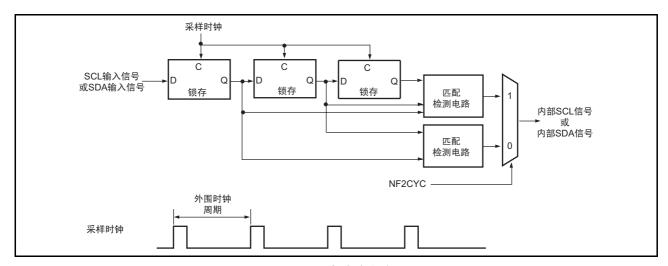

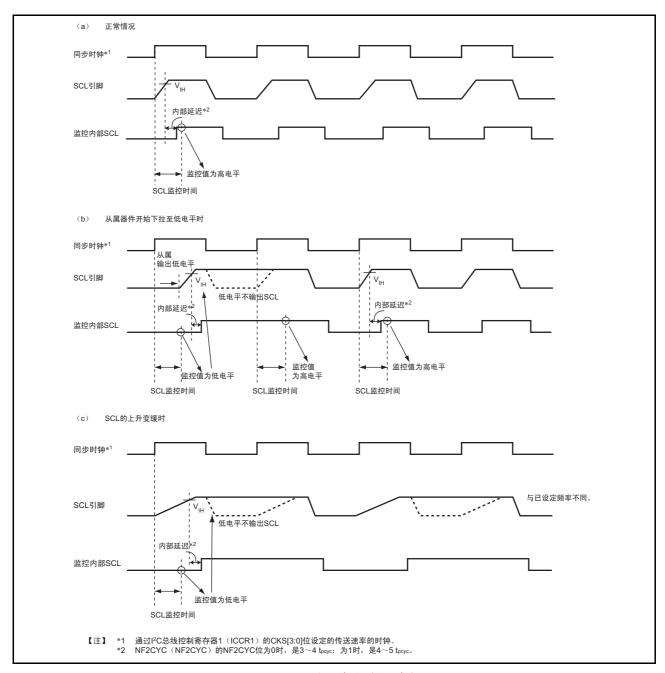

| 17.4.7   | 噪声消除电路                             | 559 |

| 17.4.8   | 使用例                                |     |

| 17.5 中国  | 断请求                                | 564 |

|          | ,<br>同步电路                          |     |

|          | 用时的注意事项                            |     |

| 17.7.1   | 设定 ICCR1.CKS[3:0] 时的注意事项           |     |

| 17.7.2   | 用作多主器件时的注意事项                       |     |

| 17.7.3   | 主接收模式时的注意事项                        |     |

| 17.7.4   | 主接收模式、 ACKBT 设定时的注意事项              |     |

| 17.7.5   | 仲裁失败时 MST 与 TRN 位状态的注意事项           |     |

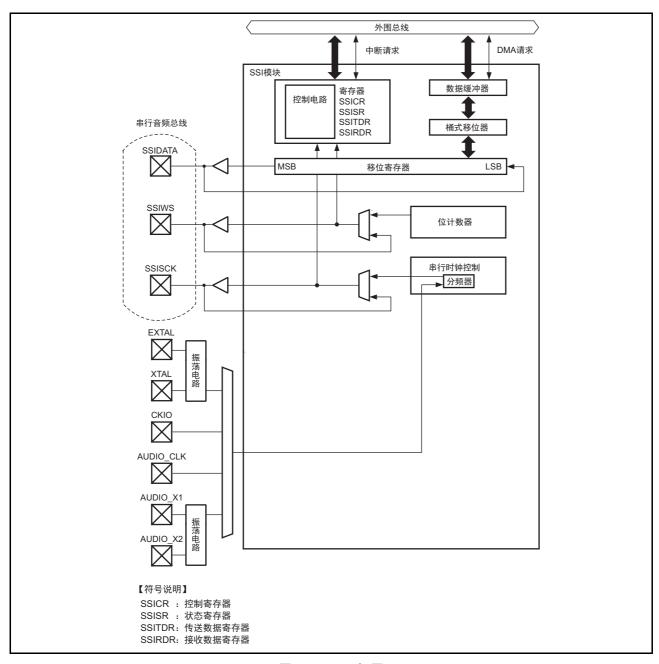

| 第 18 章   | 串行音频接口 (SSI)                       | 567 |

|          | <u> </u>                           |     |

|          | <br>入 / 输出引脚                       |     |

|          | 存器说明                               |     |

| 18.3.1   | 控制寄存器 (SSICR)                      |     |

|          | 状态寄存器(SSISR)                       |     |

| 18.3.3  | 发送数据寄存器 (SSITDR)                      | 577 |

|---------|---------------------------------------|-----|

| 18.3.4  | 接收数据寄存器 (SSIRDR)                      | 578 |

| 18.4 运行 | 行说明                                   | 578 |

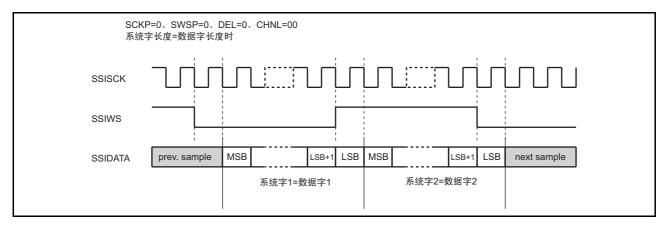

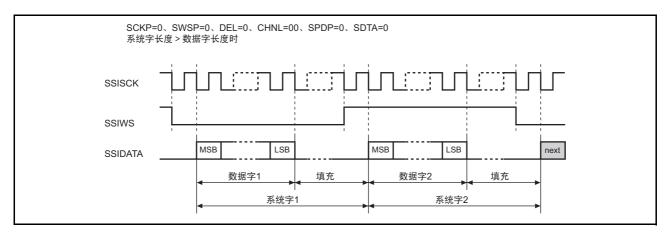

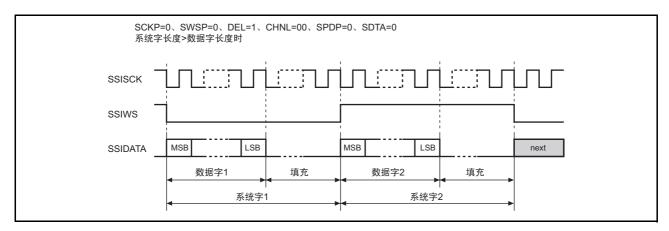

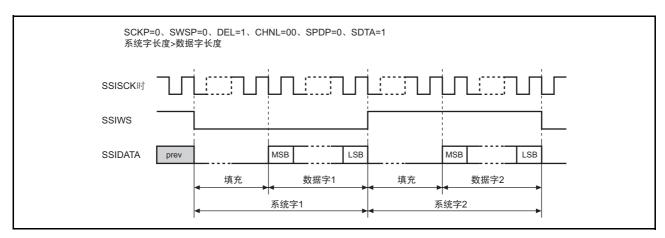

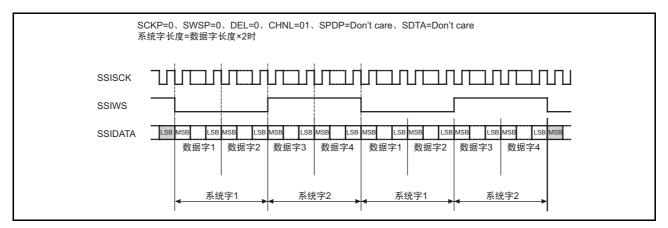

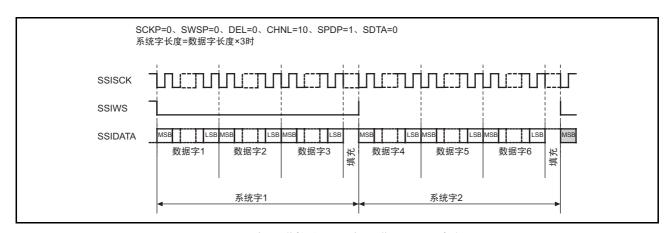

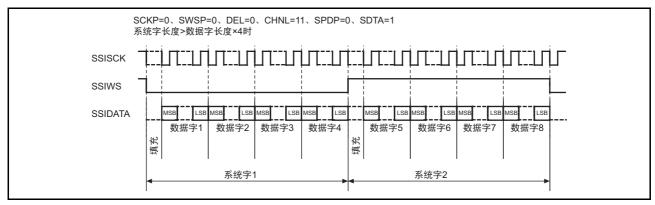

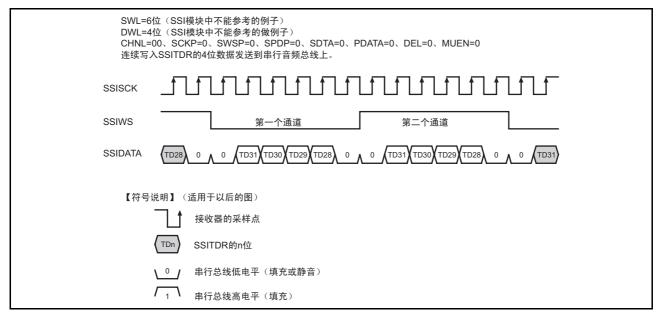

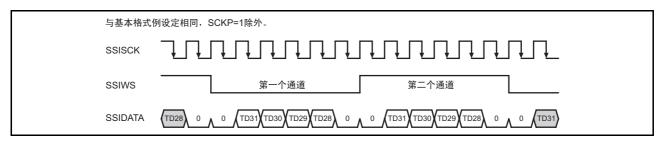

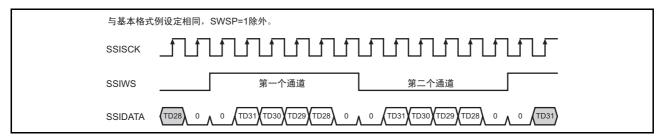

| 18.4.1  | 总线格式                                  | 578 |

| 18.4.2  | 非压缩模式                                 | 578 |

| 18.4.3  | 运行模式                                  | 586 |

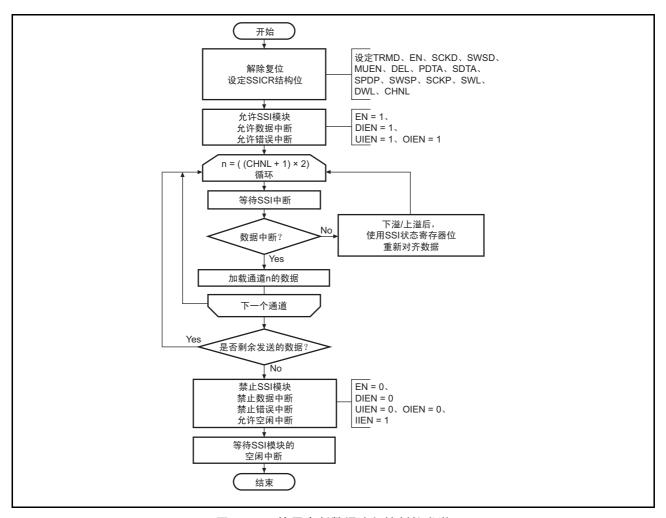

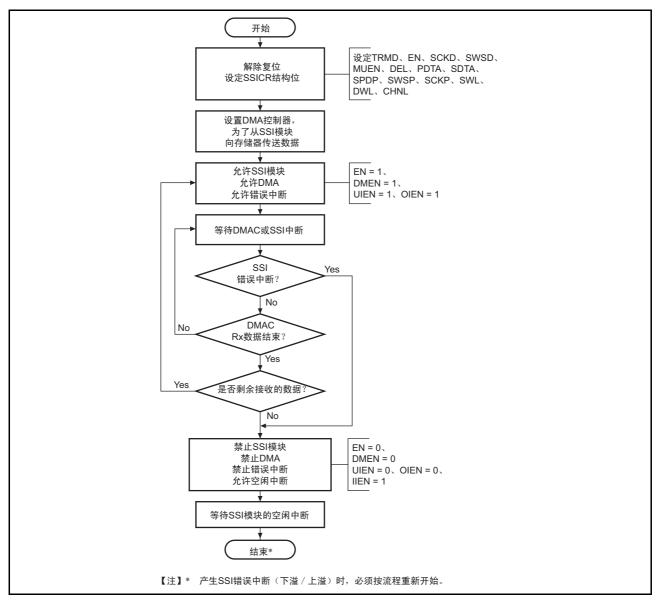

| 18.4.4  | 发送运行                                  | 587 |

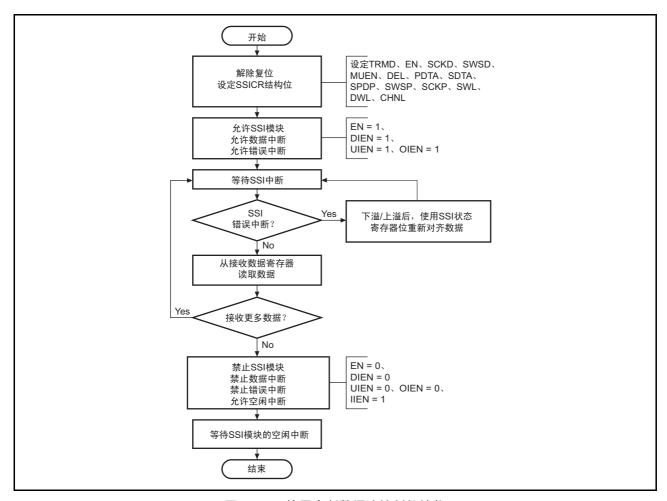

| 18.4.5  | 接收运行                                  | 589 |

| 18.4.6  | 发送时暂时停止、重新开始步骤                        | 591 |

| 18.4.7  | 串行位时钟控制                               | 591 |

| 18.5 使月 | <b>目时的注意事项</b>                        | 591 |

| 18.5.1  | 接收 DMA 运行过程中产生上溢时的限制事项                | 591 |

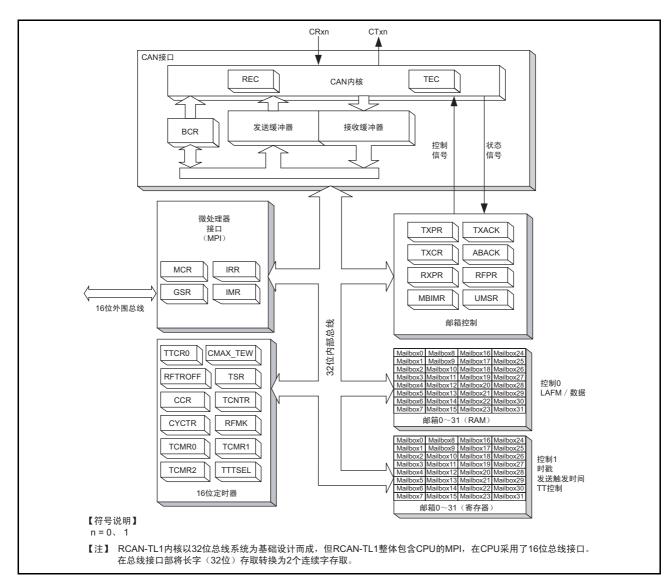

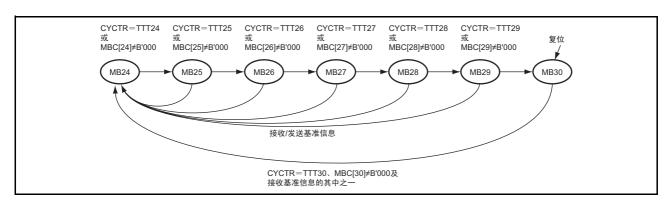

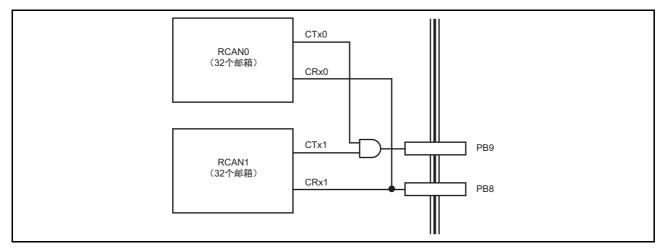

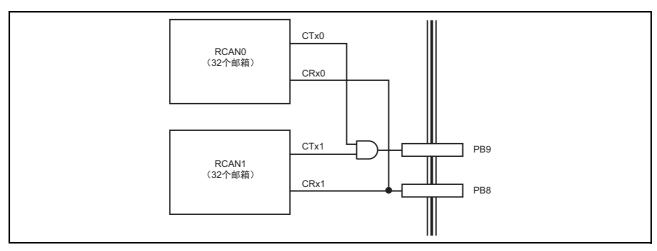

| 第 19 章  | 控制器局域网 (RCAN-TL1)                     | 592 |

| 19.1 特点 | <u> </u>                              | 592 |

| 19.1.1  | RCAN-TL1 的特点                          | 592 |

| 19.1.2  | 本单片机的特点                               | 593 |

| 19.2 结构 | 勾                                     | 593 |

| 19.2.1  | 框图                                    | 593 |

| 19.2.2  | 各块的功能                                 | 594 |

| 19.2.3  | 引脚结构                                  | 595 |

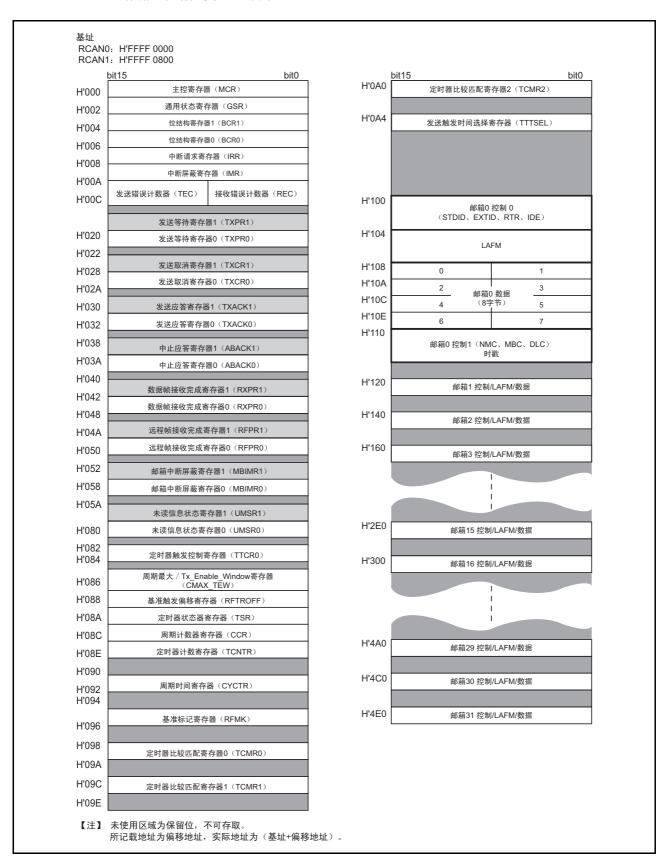

| 19.2.4  | 存储器映射                                 | 596 |

| 19.3 邮  | 箱                                     | 597 |

| 19.3.1  | 邮箱结构                                  | 597 |

| 19.3.2  | 信息控制字段                                | 601 |

| 19.3.3  | 局部接收过滤器屏蔽 (LAFM)                      | 604 |

| 19.3.4  | 信息数据字段                                | 605 |

| 19.3.5  | 时戳                                    |     |

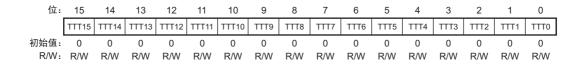

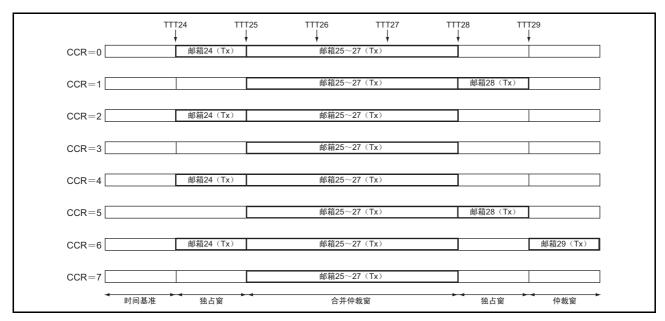

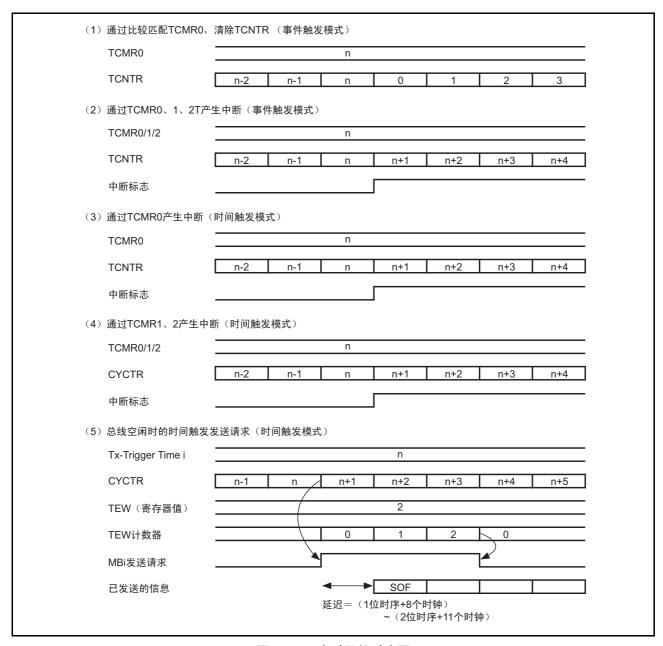

| 19.3.6  | 发送触发时间 (TTT)与时间触发控制                   | 607 |

| 19.4 RC | AN-TL1 的控制寄存器                         |     |

| 19.4.1  | 主控寄存器 (MCR)                           | 610 |

| 19.4.2  | 通用状态寄存器 (GSR)                         | 614 |

| 19.4.3  | 位结构寄存器 0、1 (BCR0、BCR1)                | 615 |

| 19.4.4  | 中断请求寄存器 (IRR)                         | 619 |

| 19.4.5  | 中断屏蔽寄存器 (IMR)                         | 623 |

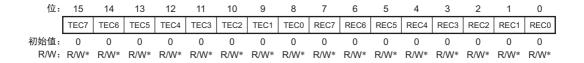

| 19.4.6  | 发送错误计数器 (TEC) / 接收错误计数器 (REC)         | 623 |

|         | AN-TL1 邮箱寄存器                          |     |

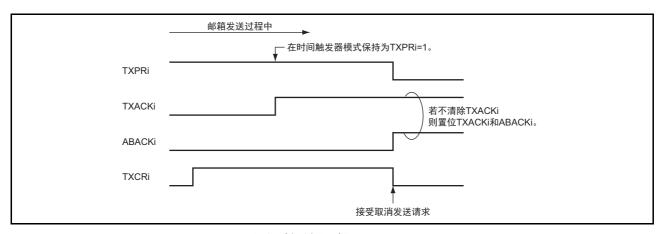

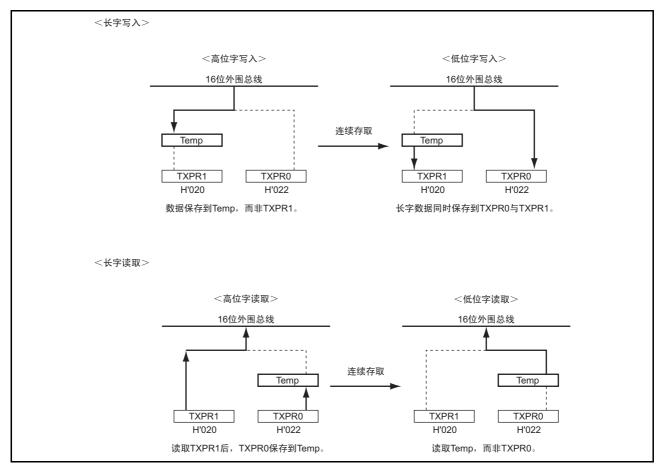

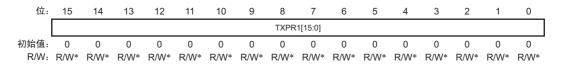

| 19.5.1  | 发送等待寄存器 1、0 (TXPR1、TXPR0)             |     |

| 19.5.2  | 发送取消寄存器 1、0 (TXCR1、TXCR0)             | 627 |

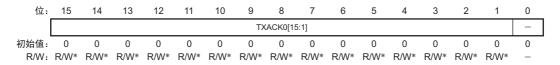

| 19.5.3  | 发送应答寄存器 1、0 (TXACK1、 TXACK0)          |     |

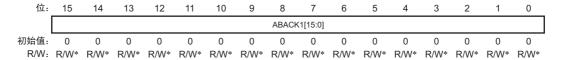

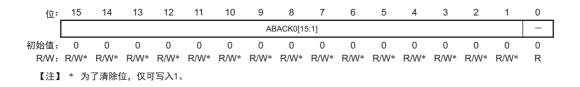

| 19.5.4  | 中止应答寄存器 1、0(ABACK1、ABACK0)            |     |

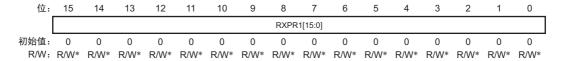

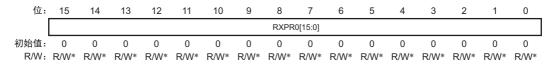

| 19.5.5  | 数据帧接收完成寄存器 1、0 (RXPR1、RXPR0)          |     |

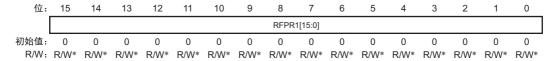

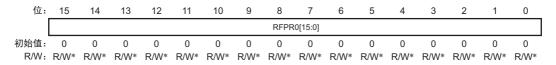

| 19.5.6  | 远程帧接收完成寄存器 1、0(RFPR1、RFPR0)           |     |

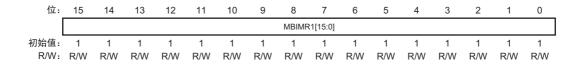

| 19.5.7  | 邮箱中断屏蔽寄存器 1、0(MBIMR1、MBIMR0)          |     |

| 19.5.8  | 未读信息状态寄存器 1、0(UMSR1、UMSR0)            |     |

|         | 村器寄存器                                 |     |

| 19.6.1  | 时间触发控制寄存器 0 (TTCR0)                   |     |

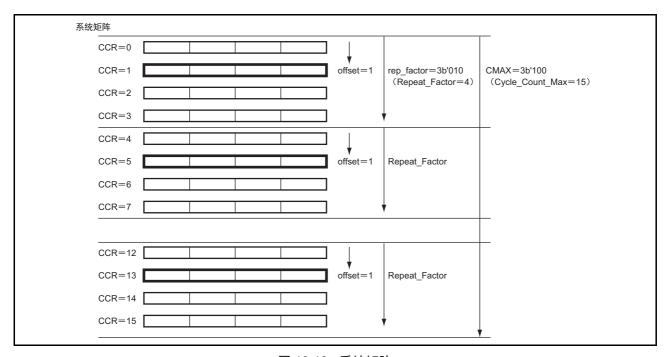

| 19.6.2  | 最大周期 /Tx_Enable_Window 寄存器 (CMAX_TEW) |     |

| 19.6.3  | 基准触发偏移寄存器(RFTROFF)基准触发偏移寄存器(RFTROFF)  |     |

| 19.6.4  | 定时器状态寄存器(TSR)                         |     |

| 19.6.5  | 周期计数器寄存器 (CCR)                        |     |

| 19.6.6  | 定时器计数器寄存器(TCNTR)                      |     |

| 19.6.7  | 周期时间寄存器(CYCTR)                        |     |

| 17.0.7  | /『J/yJ『J『J HJ TJ HF ( C I C I IX /    | 0+1 |

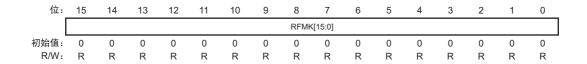

| 19.6.8  | 基准标记寄存器 (RFMK)                         |     |

|---------|----------------------------------------|-----|

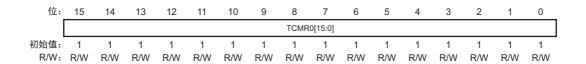

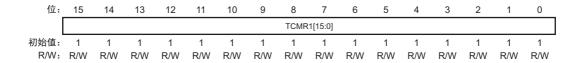

| 19.6.9  | 定时器比较匹配寄存器 $0\sim 2$ (TCMR $0\sim 2$ ) | 642 |

| 19.6.10 | 发送触发时间选择寄存器 (TTTSEL)                   | 644 |

| 19.7 运行 | <b>厅说明</b>                             |     |

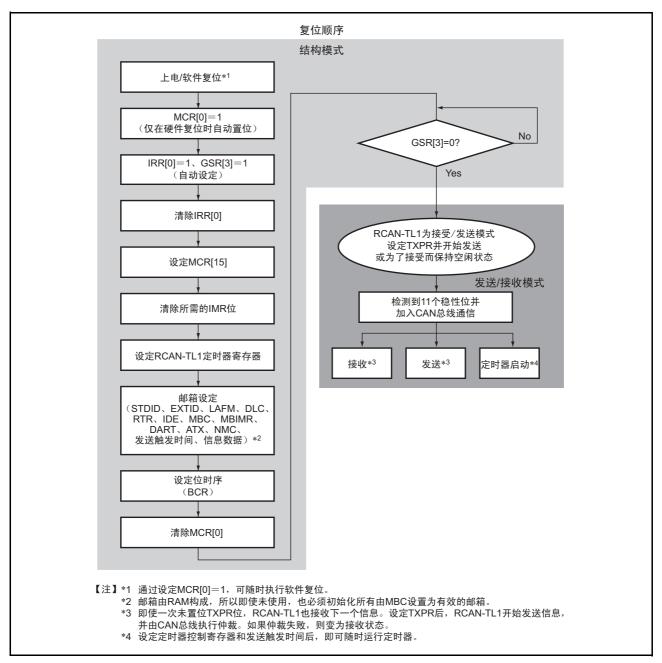

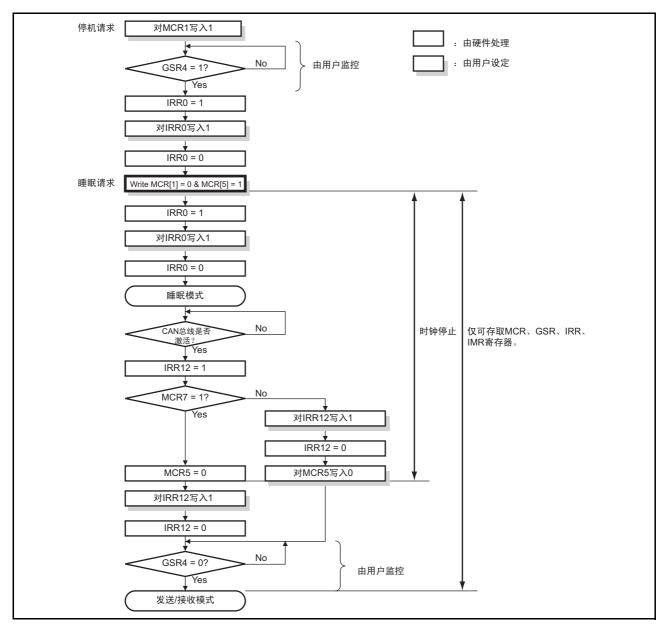

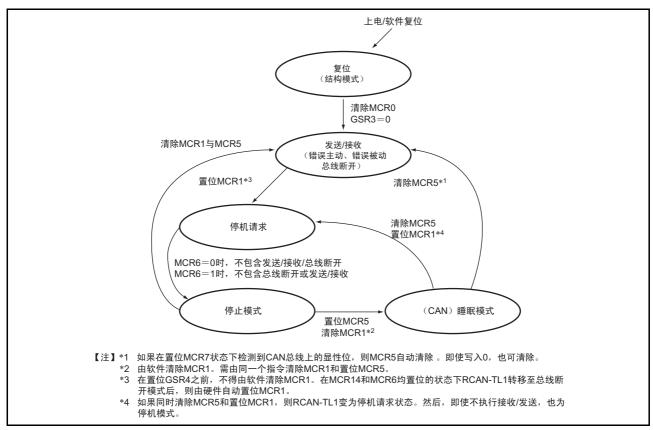

| 19.7.1  | RCAN-TL1 的设定                           | 645 |

| 19.7.2  | 测试模式的设定                                | 648 |

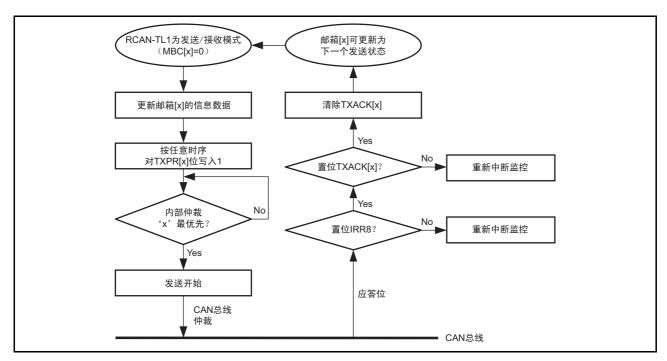

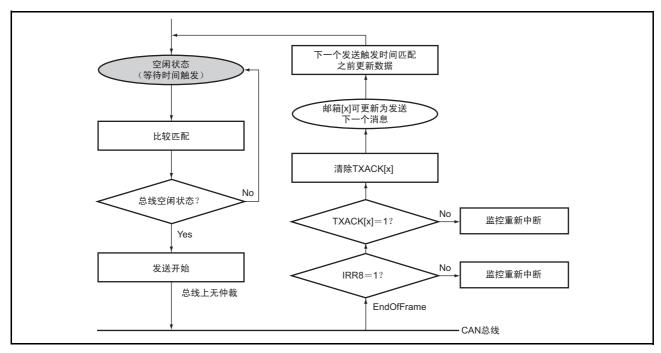

| 19.7.3  | 信息发送顺序                                 | 649 |

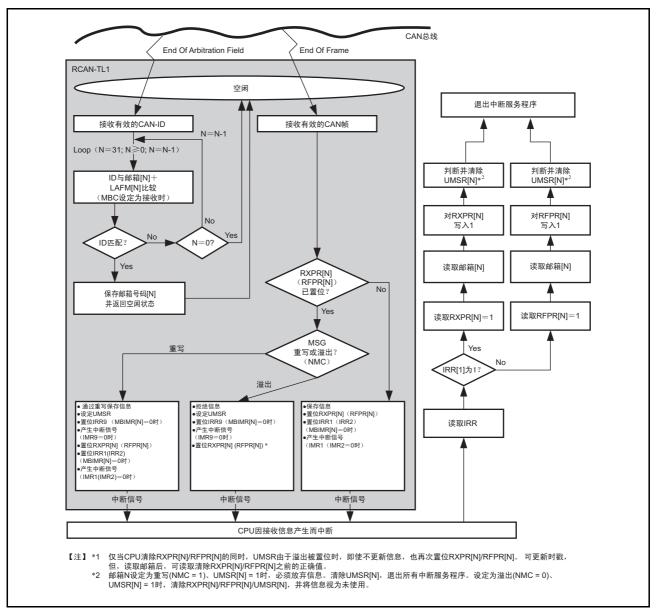

| 19.7.4  | 信息接收顺序                                 | 659 |

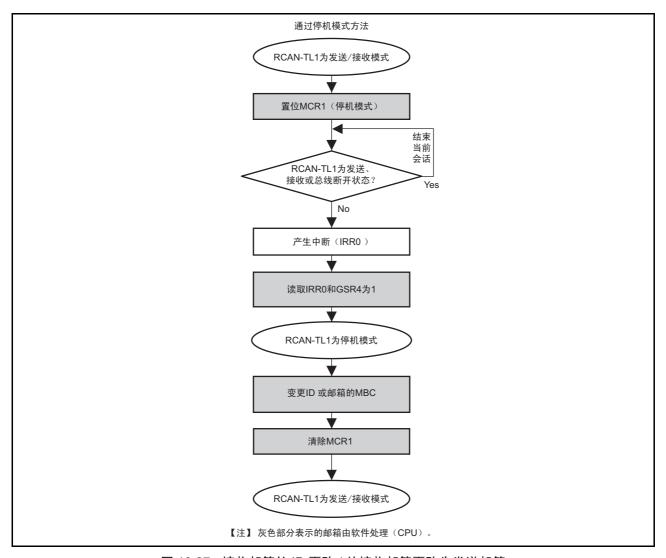

| 19.7.5  | 邮箱的重新设定                                | 660 |

|         | 析源                                     |     |

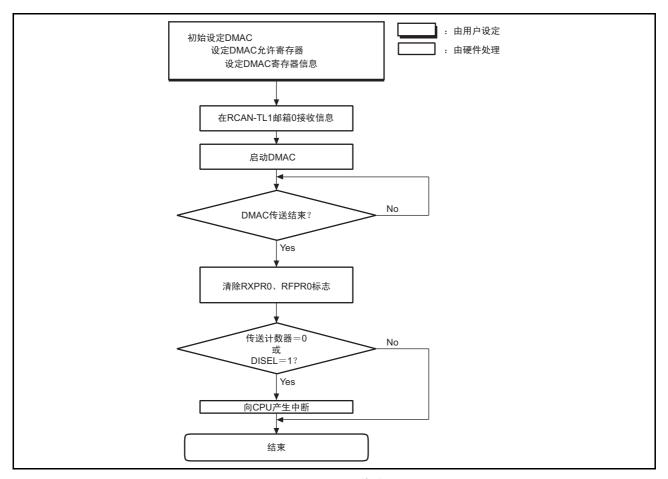

|         | IAC 接口                                 |     |

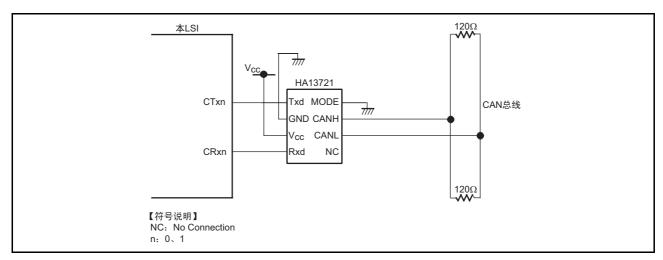

|         | N 总线接口                                 |     |

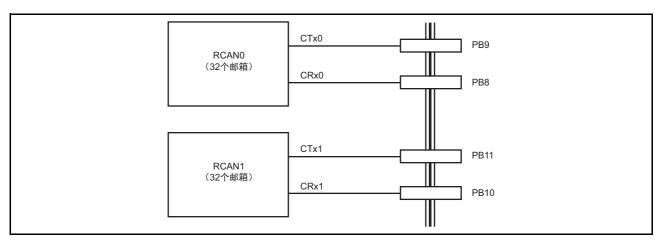

|         | AN-TL1 引脚端口设定                          |     |

|         | <b>目时的注意事项</b>                         |     |

| 19.12.1 | 设定 1 个通道 64 个邮箱的端口时的注意事项               | 665 |

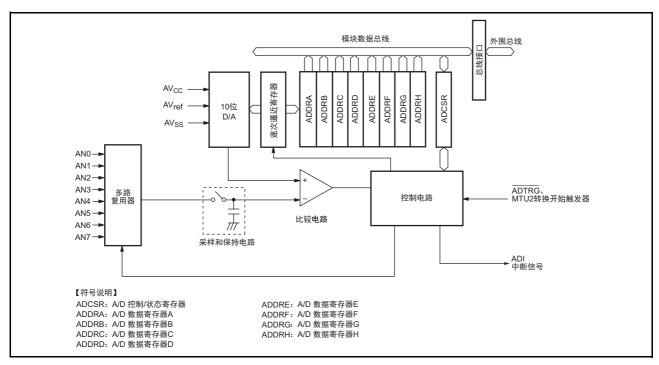

| 第 20 章  | A/D 转换器 (ADC)                          | 666 |

| , , .   | <u> </u>                               |     |

|         | 入/输出引脚                                 |     |

|         | 存器说明                                   |     |

| 20.3.1  | A/D 数据寄存器 A ~ H (ADDRA ~ ADDRH)        |     |

| 20.3.2  | A/D 控制 / 状态寄存器 (ADCSR)                 |     |

|         | 行说明                                    |     |

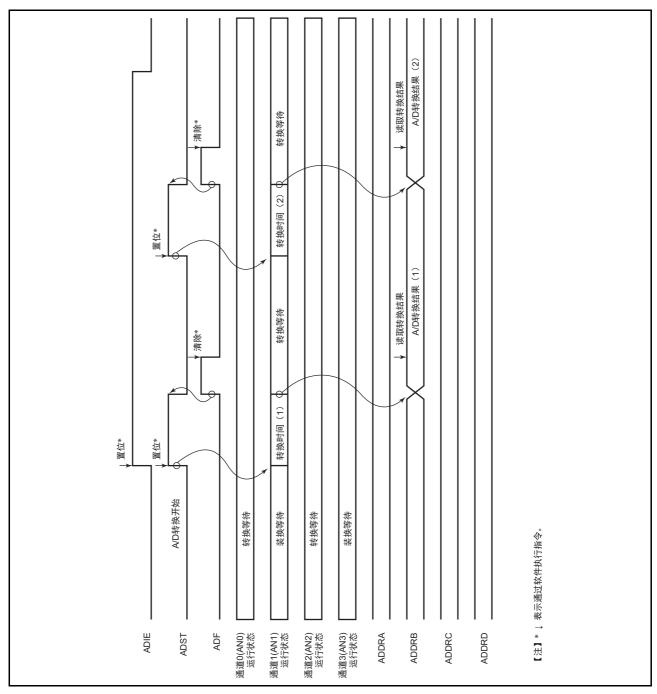

| 20.4.1  | 单通道模式                                  |     |

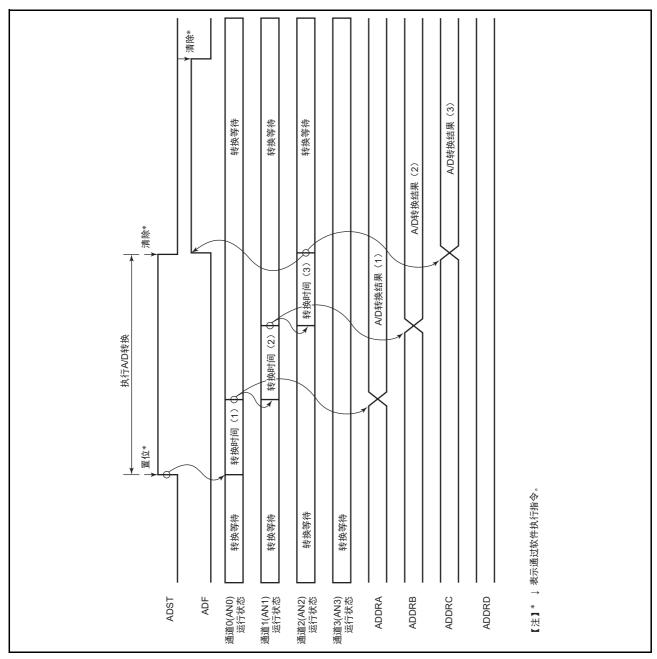

| 20.4.2  | 多通道模式                                  |     |

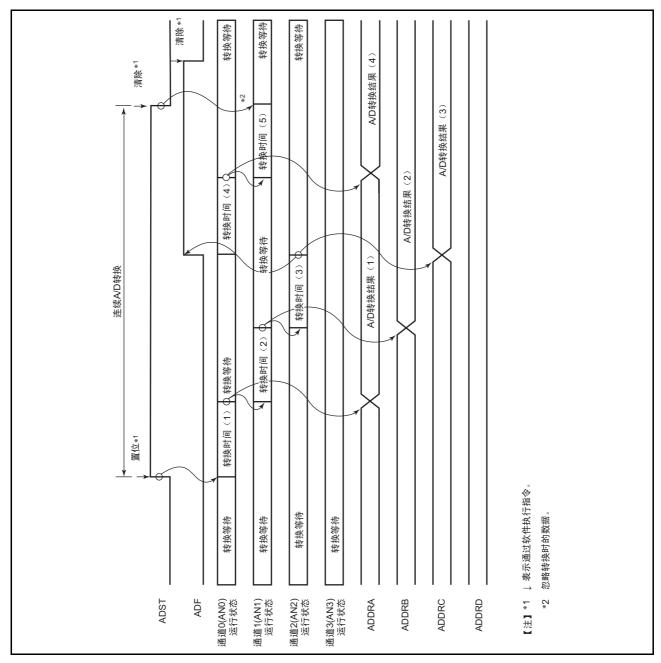

| 20.4.3  | 扫描模式                                   |     |

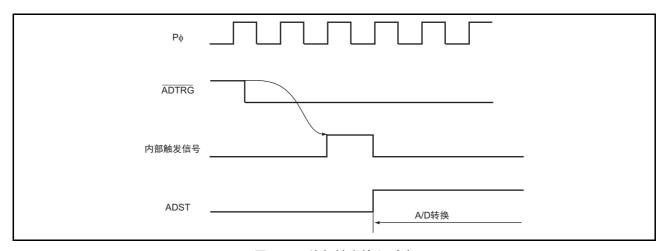

| 20.4.4  | 由外部触发、 MTU2 启动 A/D 转换器                 |     |

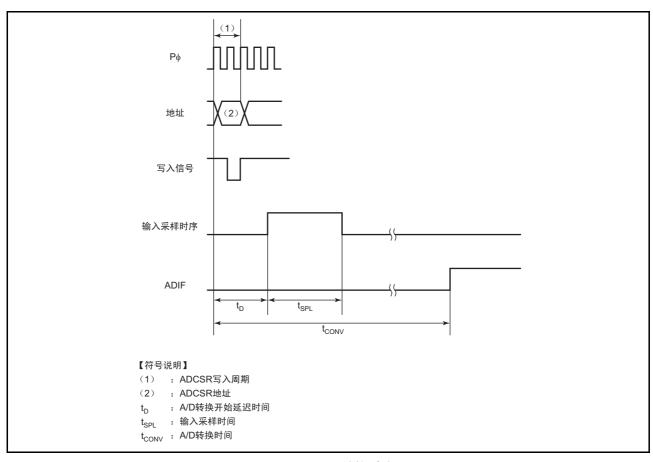

| 20.4.5  | 输入采样和 A/D 转换时间                         |     |

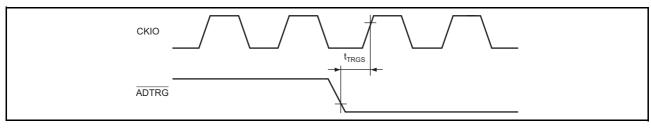

| 20.4.6  | 外部触发输入时序                               |     |

|         | 断源和 DMAC 传送请求                          |     |

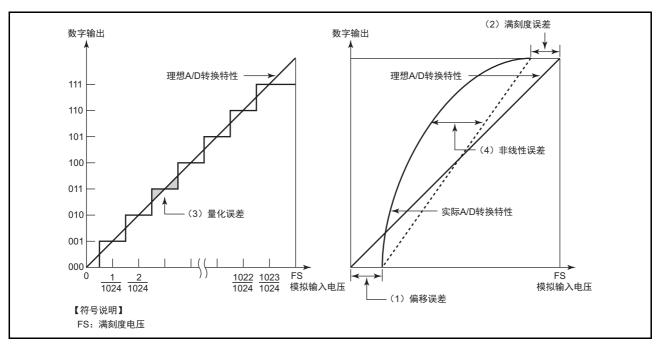

|         | <b>)</b> 转换精度的定义                       |     |

|         | 目时的注意事项                                |     |

| 20.7.1  | 模块待机模式的设定                              |     |

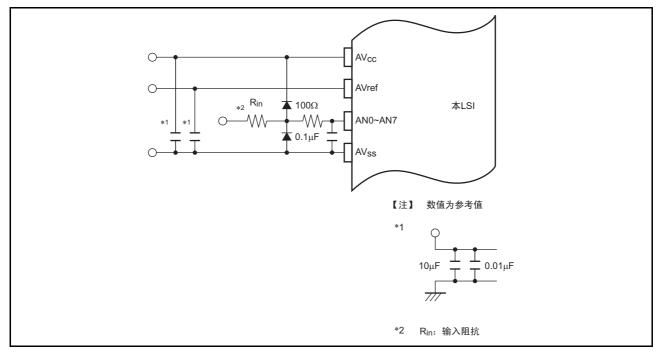

| 20.7.2  | 模拟电压的设定                                |     |

| 20.7.3  | 电路板设计的注意事项                             |     |

| 20.7.4  | 模拟输入引脚的处理                              |     |

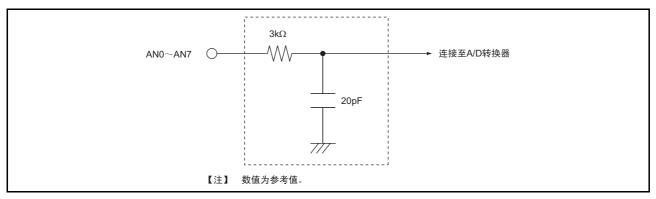

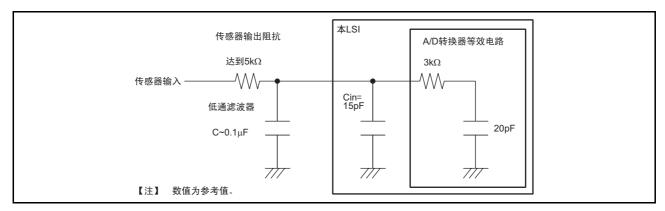

| 20.7.5  | 容许信号源阻抗                                |     |

| 20.7.6  | 对绝对精度的影响                               |     |

| 20.7.7  | 深度待机模式时的 A/D 转换                        |     |

| 20.7.8  | 使用扫描模式及多通道模式时的注意事项                     | 682 |

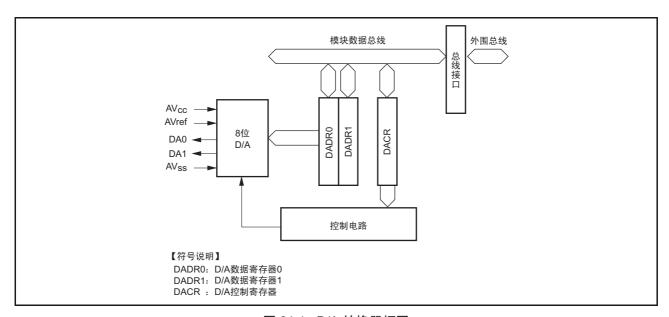

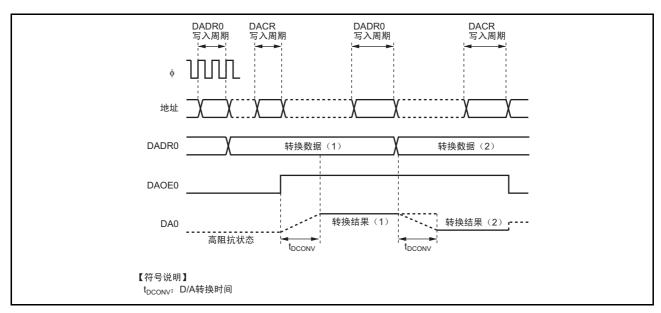

| 第 21 章  | D/A 转换器 (DAC)                          |     |

|         | <u> </u>                               |     |

|         | 入/输出引脚                                 |     |

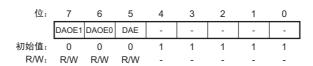

| 21.3 寄花 | 存器说明                                   |     |

| 21.3.1  | D/A 数据寄存器 0、1(DADR0、DADR1)             |     |

| 21.3.2  | D/A 控制寄存器 (DACR)                       |     |

|         | 厅说明                                    |     |

| 21.5 使月 | <b>刊时的注意事项</b>                         |     |

| 21.5.1  | 模块待机模式的设定                              |     |

| 21.5.2  | 软件待机模式时的 D/A 输出保持功能                    |     |

| 21.5.3  | 模拟输入电压的设定                              |     |

| 21.5.4  | 深度待机模式时的 D/A 转换                        | 686 |

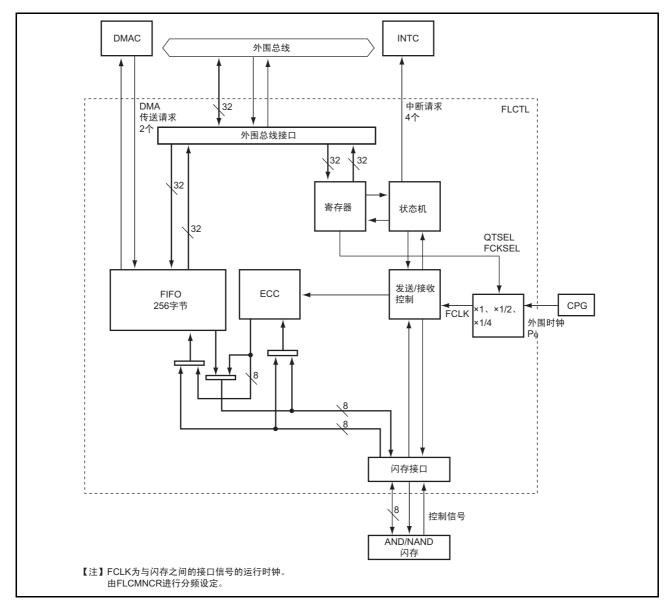

| 第 22 章           | AND/NAND 闪存控制器 (FLCTL)                                        | 687 |

|------------------|---------------------------------------------------------------|-----|

| 22.1 特点          |                                                               | 687 |

| 22.2 输入          | 、/ 输出引脚                                                       | 690 |

| 22.3 寄存          | - 器说明                                                         |     |

| 22.3.1           | 共用控制寄存器 (FLCMNCR)                                             |     |

| 22.3.2           | 命令控制寄存器(FLCMDCR)                                              |     |

| 22.3.3           | 命令码寄存器(FLCMCDR)                                               |     |

| 22.3.4           | 地址寄存器(FLADR)                                                  |     |

| 22.3.5           | 地址寄存器 2 (FLADR2)                                              |     |

| 22.3.6           | 数据计数器寄存器(FLDTCNTR)                                            |     |

| 22.3.7           | 数据寄存器(FLDATAR)                                                |     |

| 22.3.8           | 中断 DMA 控制寄存器 (FLINTDMACR)                                     |     |

| 22.3.9           | 就绪/忙超时设定寄存器(FLBSYTMR)                                         |     |

| 22.3.10          | 就绪/忙超时计数器(FLBSYCNT)                                           |     |

| 22.3.11          | 数据 FIFO 寄存器 (FLDTFIFO)                                        |     |

| 22.3.12          | 管理码 FIFO 寄存器(FLECFIFO)                                        |     |

| 22.3.13          | · '' '' '' '                                                  |     |

| 22.4 E1          | 存取步骤                                                          |     |

| 22.4.1           | 运行模式                                                          |     |

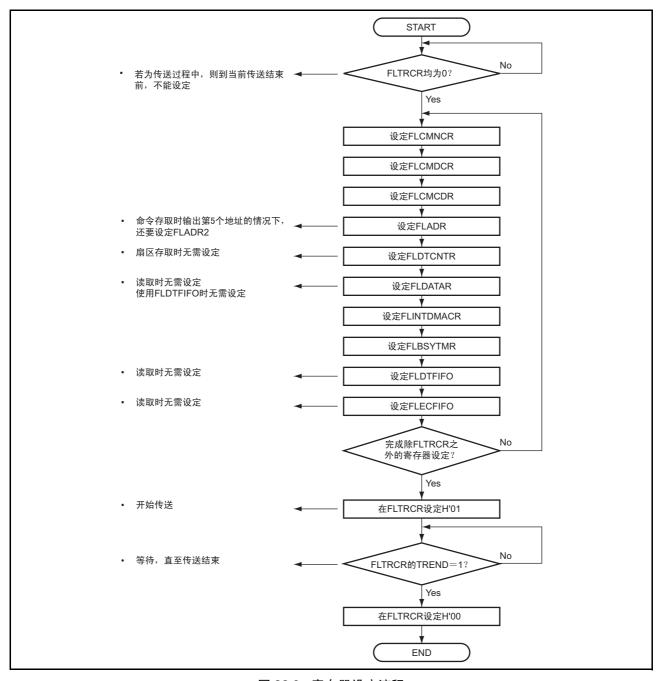

| 22.4.2           | 寄存器设定步骤                                                       |     |

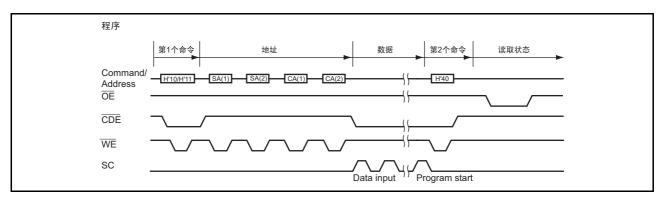

| 22.4.4           | 命令存取模式                                                        |     |

| 22.4.5           | 扇区存取模式                                                        |     |

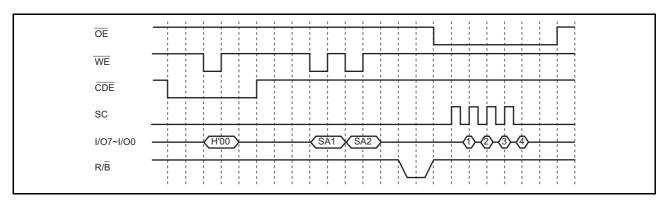

| 22.4.6           | ECC 的纠错                                                       |     |

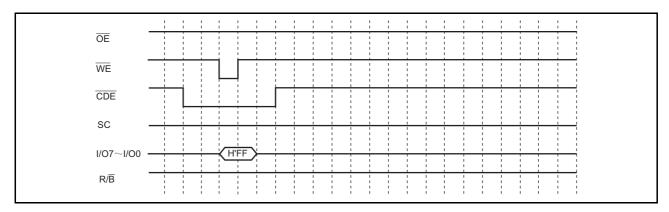

| 22.4.7           | 状态读取                                                          |     |

|                  | f处理                                                           |     |

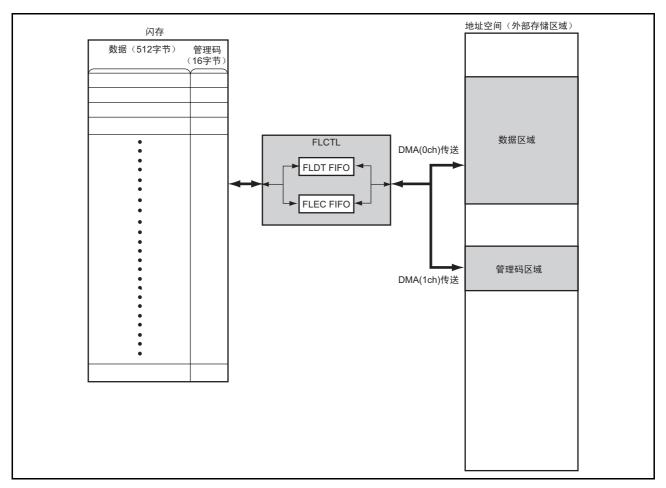

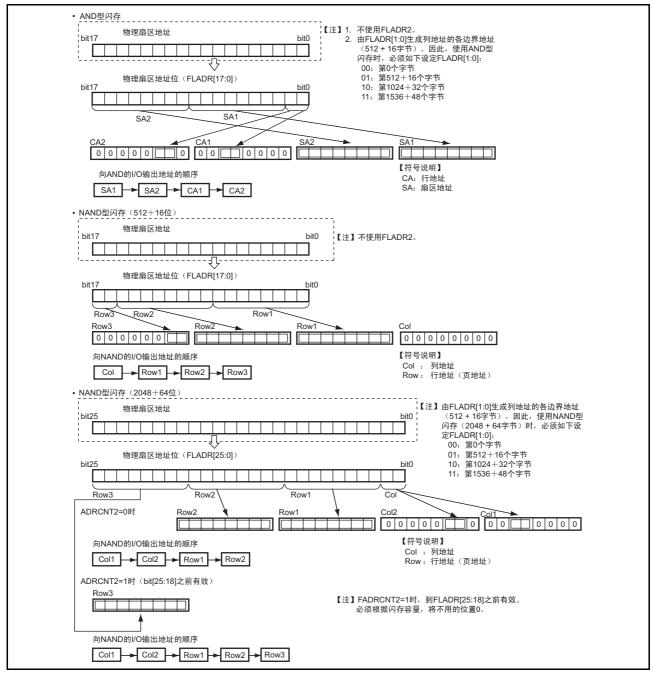

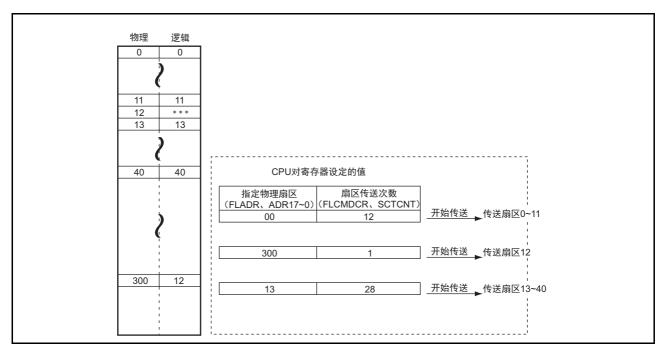

|                  | A 传送设定                                                        |     |

|                  |                                                               |     |

|                  | USB2.0 主机 / 功能模块 (USB)                                        |     |

|                  | į                                                             |     |

|                  | 、/ 输出引脚                                                       |     |

|                  | - 器说明                                                         |     |

| 23.3.1           | 系统结构控制寄存器(SYSCFG)                                             |     |

| 23.3.2           | 系统结构状态寄存器(SYSSTS)                                             |     |

| 23.3.3           | 器件状态控制寄存器 (DVSTCTR)测试模式寄存器 (TESTMODE)                         |     |

| 23.3.4<br>23.3.5 | 例以僕式奇存器 (TESTMODE)<br>FIFO 端口结构寄存器 (CFBCFG、 D0FBCFG、 D1FBCFG) |     |

| 23.3.6           | FIFO 端口结构 (CFBCFG、D0FBCFG、D1FBCFG)                            |     |

| 23.3.7           | FIFO 端口选择寄存器 (CFIFOSEL、 D0FIFOSEL、 D1FIFOSEL)                 |     |

| 23.3.7           | FIFO 端口控制寄存器(CFIFOCTR、 D0FIFOCTR、 D1FIFOCTR)                  |     |

| 23.3.9           | CFIFO 端口 SIE 寄存器 (CFIFOSIE)                                   |     |

| 23.3.10          | 处理计数器寄存器 (D0FIFOTRN、D1FIFOTRN)                                |     |

| 23.3.11          | 中断允许寄存器 0 (INTENBO)                                           |     |

| 23.3.12          | 中断允许寄存器 1 (INTENB1)                                           |     |

| 23.3.13          | BRDY 中断允许寄存器 (BRDYENB)                                        |     |

| 23.3.14          | NRDY 中断允许寄存器 (NRDYENB)                                        |     |

| 23.3.15          | BEMP 中断允许寄存器 (BEMPENB)                                        |     |

| 23.3.16          | 中断状态寄存器 0(INTSTS0)                                            |     |

| 23.3.17          | 中断状态寄存器 1 (INTSTS1)                                           |     |

| 23.3.18          | BRDY 中断状态寄存器 (BRDYSTS)                                        | 742 |

| 23.3.19          | NRDY 中断状态寄存器 (NRDYSTS)                                        | 743 |

| 23.3.20          | BEMP 中断状态寄存器 (BEMPSTS)                                        | 744 |

| 23.3.21          | 帧编号寄存器 (FRMNUM)                                               | 745 |

|                       | Liston III about a BB                   |     |

|-----------------------|-----------------------------------------|-----|

| 23.3.22               | μ帧编号寄存器(UFRMNUM)                        |     |

| 23.3.23               | USB 地址寄存器 (USBADDR)                     |     |

| 23.3.24               | USB 请求类型寄存器 (USBREQ)                    |     |

| 23.3.25               | USB 请求值寄存器 (USBVAL)                     |     |

| 23.3.26               | USB 请求变址寄存器 (USBINDX)                   | 748 |

| 23.3.27               | USB 请求长度寄存器 (USBLENG)                   | 748 |

| 23.3.28               | DCP 结构寄存器 (DCPCFG)                      | 749 |

| 23.3.29               | DCP Max 包大小寄存器 (DCPMAXP)                | 750 |

| 23.3.30               | DCP 控制寄存器 (DCPCTR)                      | 750 |

| 23.3.31               | 管道窗口选择寄存器 (PIPESEL)                     |     |

| 23.3.32               | 管道结构寄存器 (PIPECFG)                       |     |

| 23.3.33               | 管道缓冲器指定寄存器 (PIPEBUF)                    |     |

| 23.3.34               | 管道 Max 包大小寄存器 (PIPEMAXP)                |     |

| 23.3.35               | 管道周期控制寄存器(PIPEPERI)                     |     |

| 23.3.36               | 管道 n 控制寄存器 (PIPEnCTR) (n=1 ~ 7)         |     |

| 23.3.37               | USB AC 特性转换寄存器 (USBACSWR)               |     |

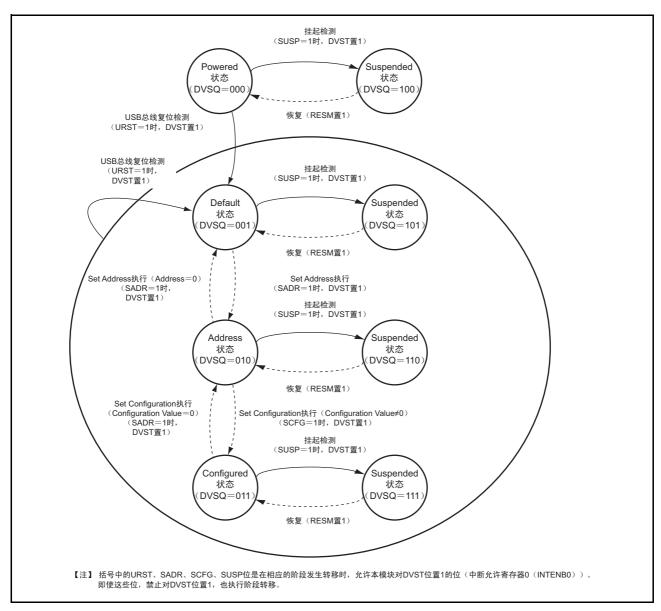

|                       | 了说明                                     |     |

| 23.4.1                | 系统控制                                    |     |

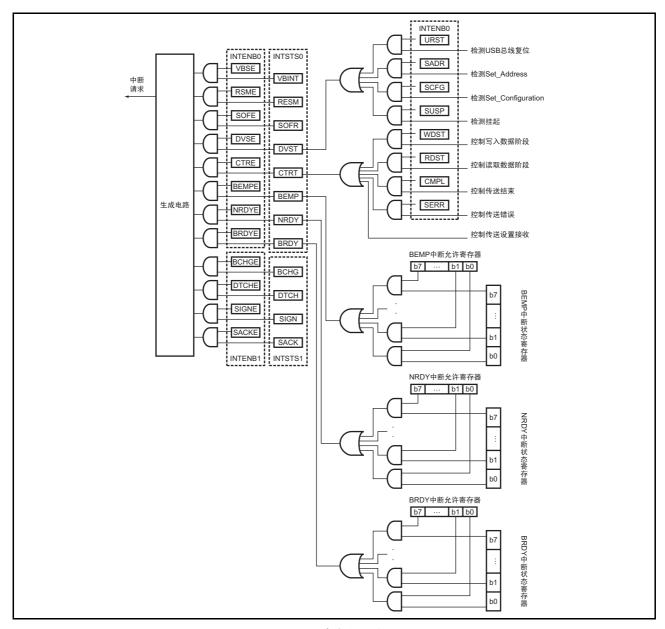

| 23.4.2                | 中断功能                                    |     |

| 23.4.3                | 章 章 · · · · · · · · · · · · · · · · · · |     |

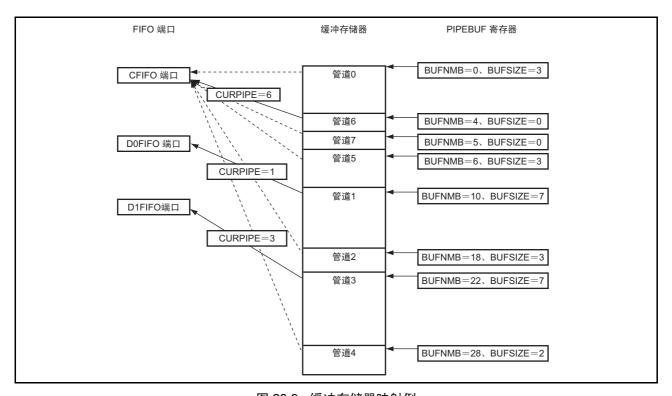

| 23.4.4                | 缓冲存储器                                   |     |

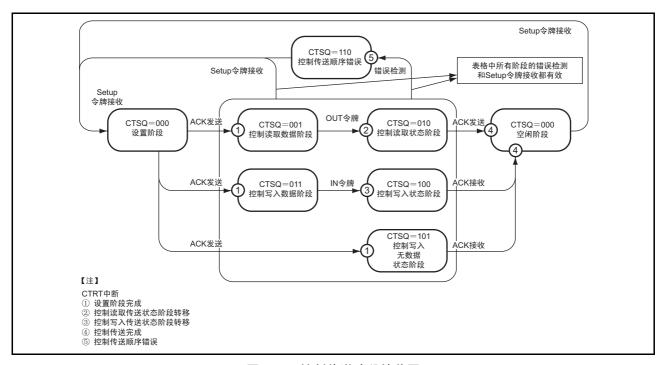

| 23.4.5                | 控制传送 (DCP)                              |     |

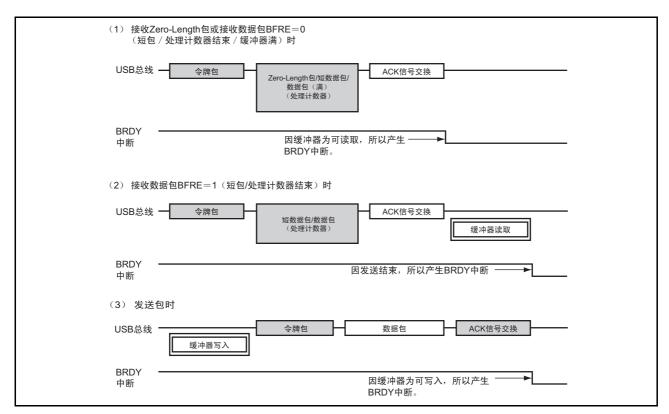

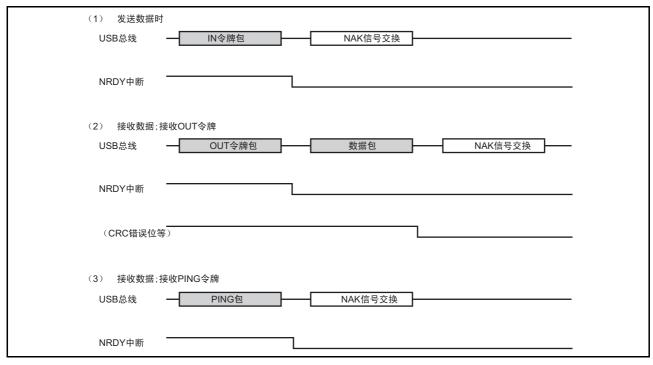

| 23.4.6                | 批量传送 (管道 1 ~ 5)                         |     |

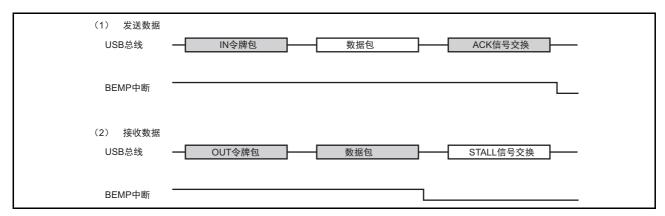

| 23.4.7                | 中断传送 (管道 6、7)                           |     |

| 23.4.8                | 同步传送 (管道 1、2)                           |     |

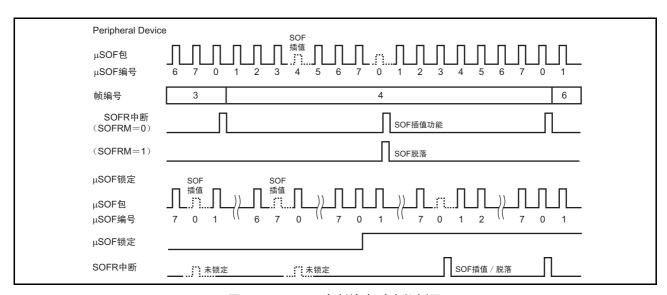

| 23.4.9                | SOF 插值功能                                |     |

| 23.4.10               | 管道安排                                    |     |

|                       | 目时的注意事项                                 |     |

| 23.5.1                | 使用同步 OUT 传送时的注意事项                       |     |

| 23.5.2                | USB 收发器的设定步骤                            |     |

| 23.5.3                | 中断源的清除时序                                |     |

| 23.3.3                | 1 PAINWH 11121/2/1/1                    |     |

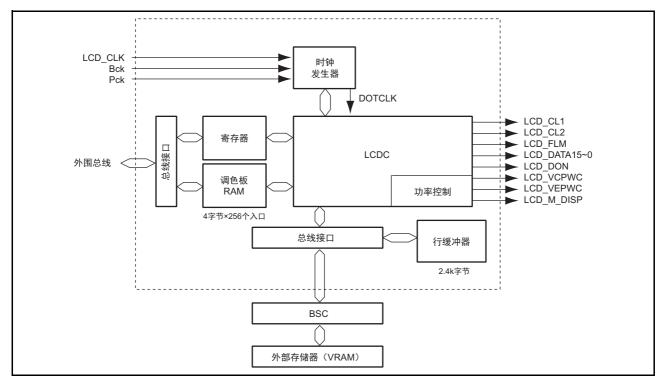

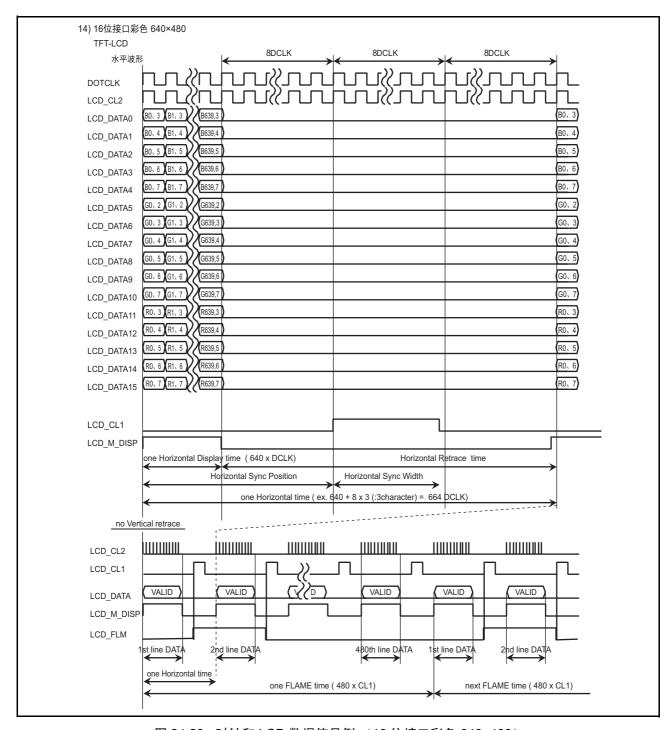

| 第 24 章                | LCD 控制器 (LCDC)                          | 799 |

| 24.1 特点               | Ţ                                       | 799 |

| 24.2 输入               | 、/ 输出引脚                                 | 800 |

|                       | <b>7器说明</b>                             |     |

| 24.3.1                | LCDC 输入时钟寄存器 (LDICKR)                   |     |

| 24.3.2                | LCDC 模块类型寄存器 (LDMTR)                    |     |

| 24.3.3                | LCDC 数据格式寄存器 (LDDFR)                    |     |

| 24.3.4                | LCDC 扫描模式寄存器 (LDSMR)                    | 806 |

| 24.3.5                | LCDC 上部显示面板用取数据起始地址寄存器(LDSARU)          |     |

| 24.3.6                | LCDC 下部显示用面板取数据起始地址寄存器(LDSARL)          |     |

| 24.3.7                | LCDC 显示面板取数据行地址偏移量寄存器(LDLAOR)           |     |

| 24.3.8                | LCDC 调色板控制寄存器 (LDPALCR)                 |     |

| 24.3.9                | 调色板数据寄存器 00 ~ FF (LDPR00 ~ LDPRFF)      |     |

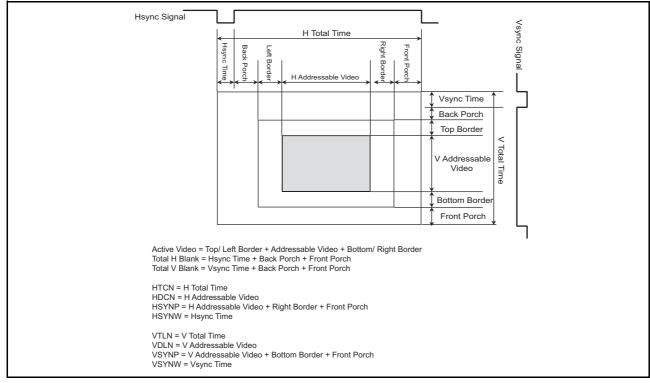

| 24.3.10               | LCDC 水平字符数寄存器 (LDHCNR)                  |     |

| 24.3.11               | LCDC 水平同步信号寄存器(LDHSYNR)                 |     |

| 24.3.11               | LCDC 垂直显示行数寄存器(LDVDLNR)                 |     |

| 24.3.12               | LCDC 垂直总行数寄存器(LDVTLNR)                  |     |

| 24.3.13               | LCDC 垂直同步信号寄存器(LDVSYNR)                 |     |

| 24.3.14               | LCDC AC 调制信号交替行数寄存器(LDACLNR)            |     |

| 24.3.16               | LCDC 中断控制寄存器 (LDINTR)                   |     |

| 24.3.10               | LCDC 电源管理模式寄存器(LDPMMR)                  |     |

| ∠ <del>+</del> .J.1 / | LCDC 心が日性状状則11 TIF (LDI MIMIK)          | 010 |

| 24.3.18   | LCDC 上电顺序期间寄存器 (LDPSPR)                                     | 817  |

|-----------|-------------------------------------------------------------|------|

| 24.3.19   | LCDC 控制寄存器 (LDCNTR)                                         | 818  |

| 24.3.20   | LCDC 用户指定中断控制寄存器(LDUINTR)                                   | 819  |

|           | LCDC 用户指定中断行数寄存器(LDUINTLNR)                                 |      |

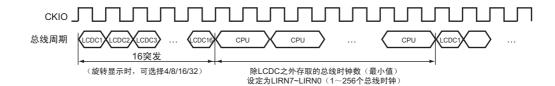

|           | LCDC 存储器存取间隔数寄存器(LDLIRNR)                                   |      |

|           | えり                                                          |      |

| 24.4.1    | 关于 LCDC 可显示的液晶模块尺寸                                          |      |

| 24.4.1    | 旋转显示的分辨率 / 突发长度及连接存储器 (SDRAM)的限制事项                          |      |

|           | 灰为亚小的分辨率/                                                   |      |

|           | - D - C - C - C - C - C - C - C - C - C                     |      |

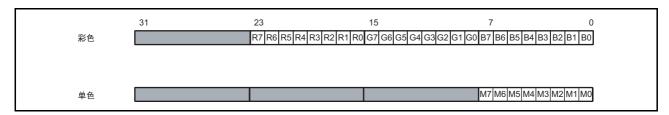

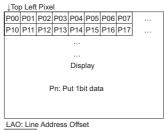

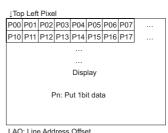

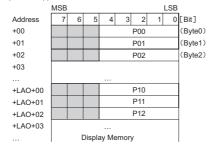

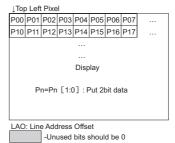

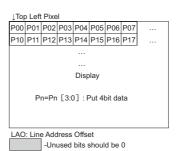

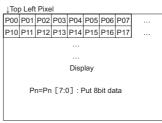

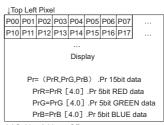

| 24.4.4    | 数据格式                                                        |      |

| 24.4.5    | 显示分辨率的设定                                                    |      |

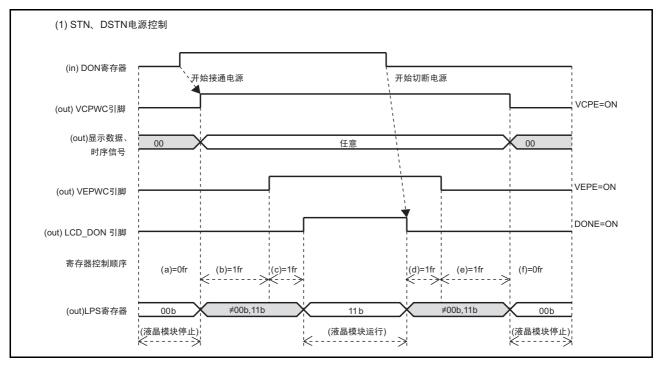

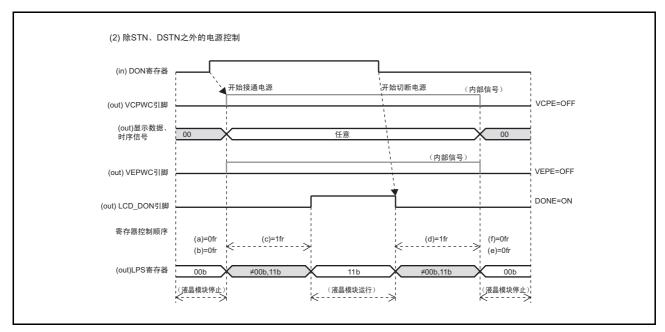

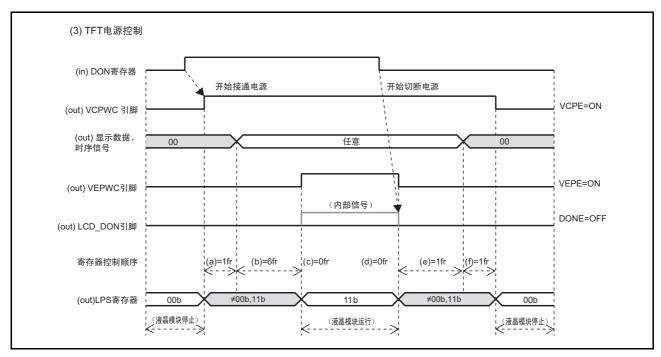

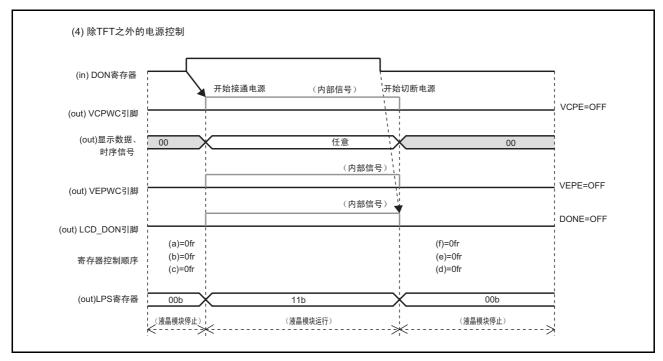

| 24.4.6    | 电源控制顺序处理                                                    |      |

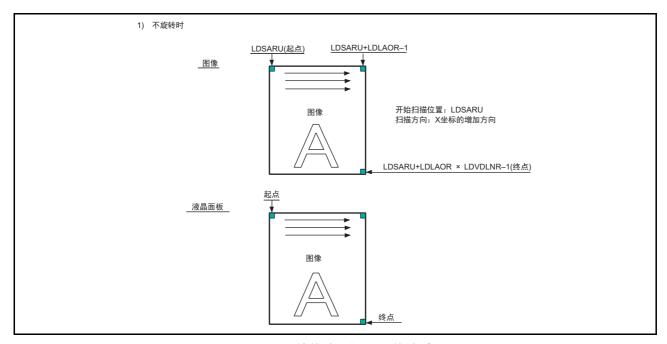

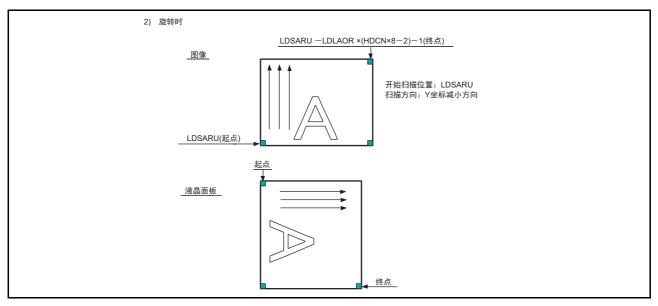

|           | 硬件旋转运行说明                                                    |      |

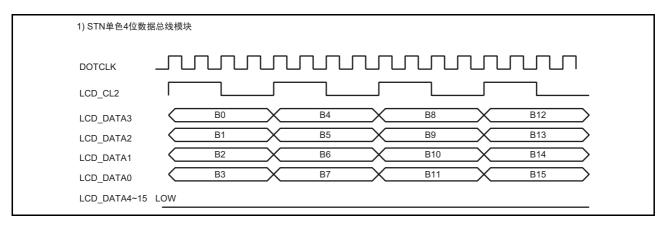

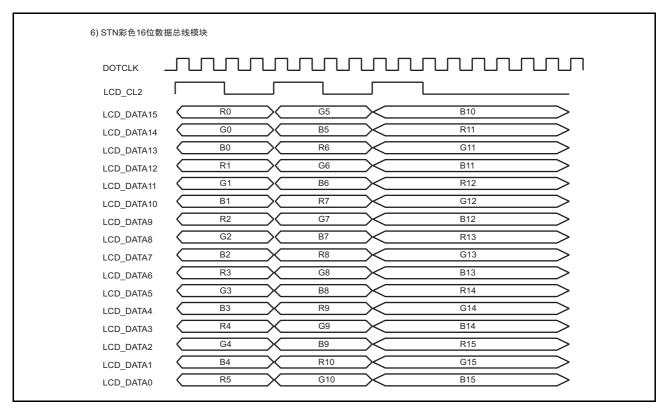

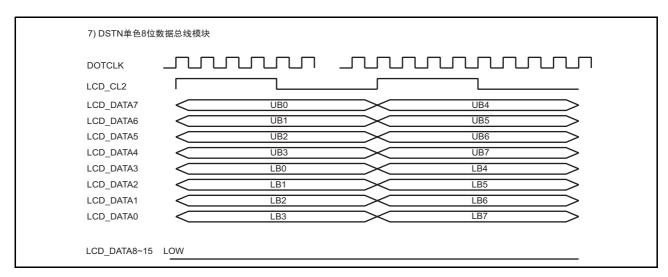

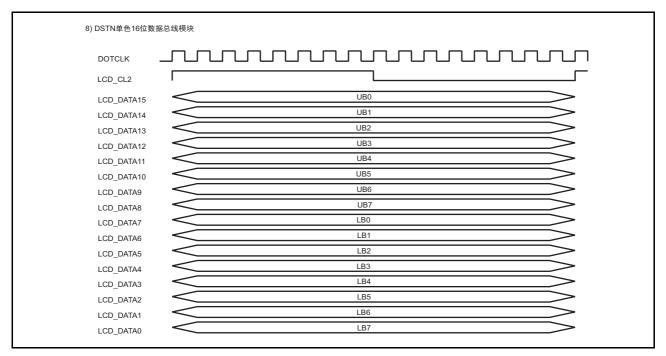

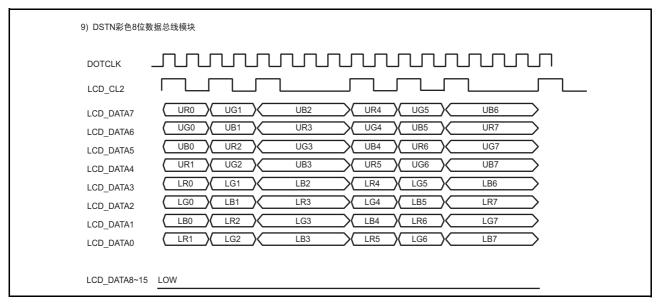

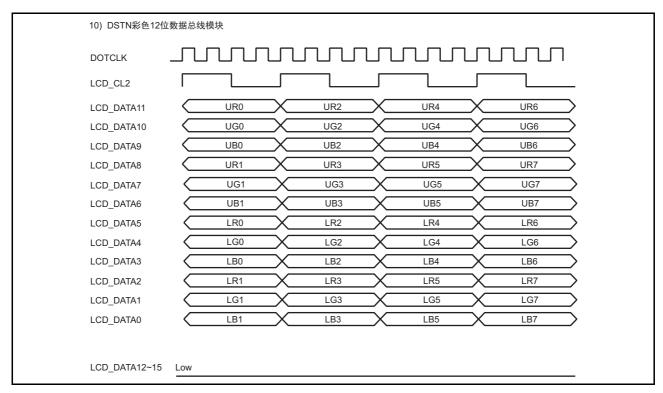

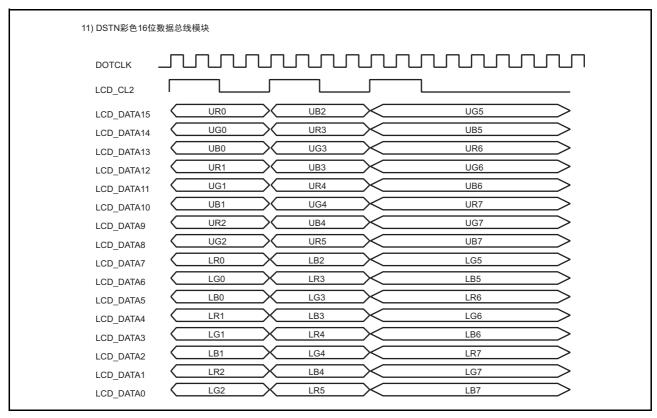

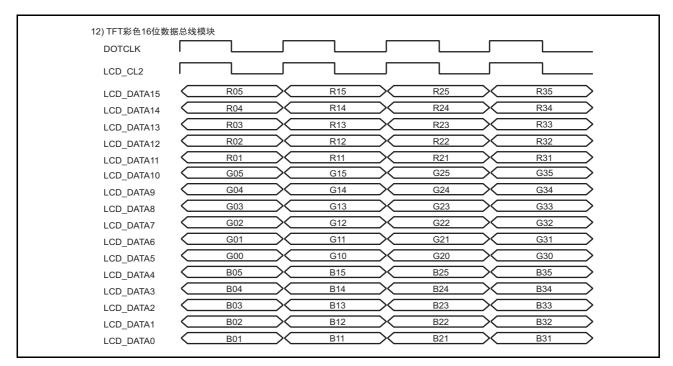

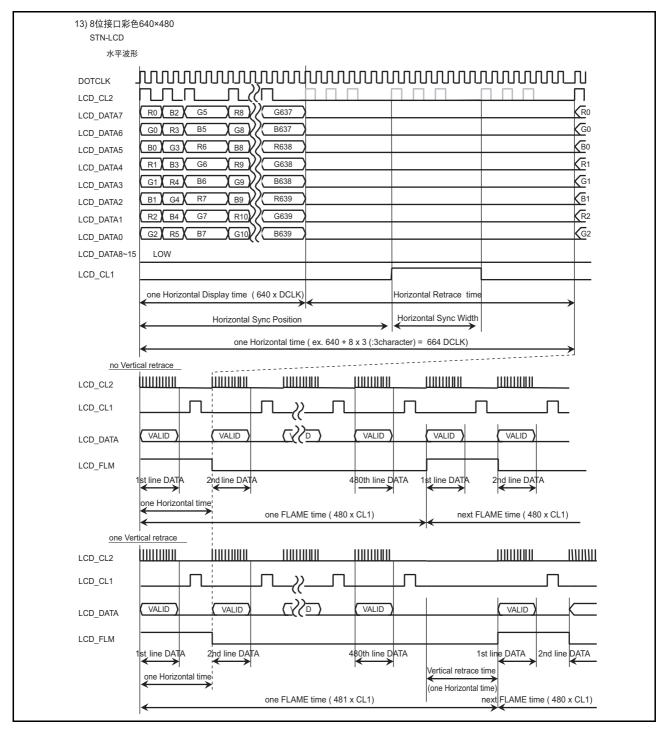

|           | 和 LCD 数据信号例                                                 |      |

|           | 时的注意事项                                                      |      |

| 24.6.1    | 存取保存显示数据的 VRAM (区域 3 的同步 DRAM)的停止步骤                         | 845  |

| ** o= ÷ = |                                                             | 0.40 |

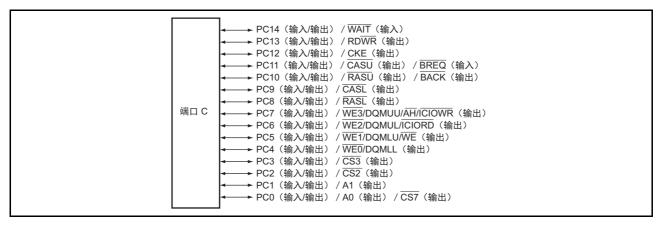

|           | 引脚功能控制器 (PFC)                                               |      |

|           |                                                             |      |

|           | 器的说明                                                        |      |

|           | 端口 B/IO 寄存器 L (PBIORL)                                      |      |

| 25.2.2    | 端口 B 控制寄存器 L1 ~ L4 (PBCRL1 ~ PBCRL4)                        | 852  |

| 25.2.3    | 端口 C/IO 寄存器 L (PCIORL)                                      | 856  |

| 25.2.4    | 端口 C 控制寄存器 L1 ~ L4 (PCCRL1 ~ PCCRL4)                        | 856  |

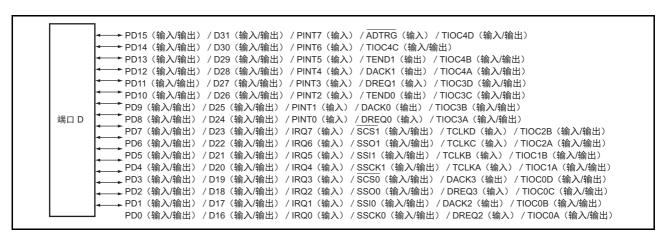

| 25.2.5    | 端口 D/IO 寄存器 L (PDIORL)                                      | 860  |

| 25.2.6    | 端口 D 控制寄存器 L1 ~ L4 (PDCRL1 ~ PDCRL4)                        | 860  |

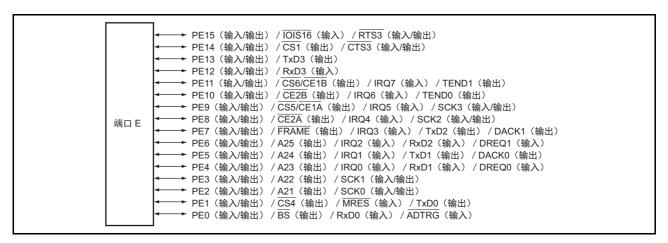

| 25.2.7    | 端口 E/IO 寄存器 L (PEIORL)                                      | 867  |

|           | 端口 E 控制寄存器 L1 ~ L4 (PECRL1 ~ PECRL4)                        |      |

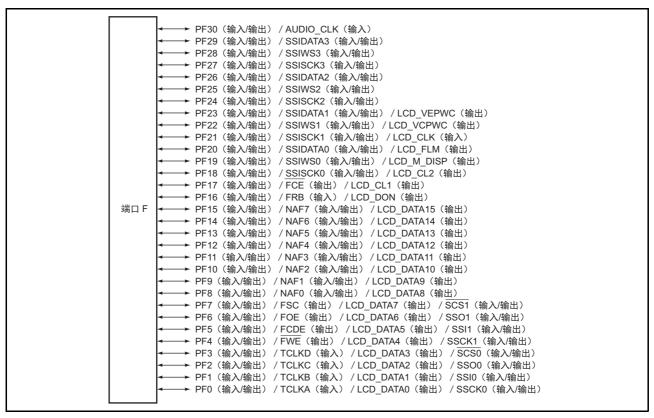

|           | 端口 F/IO 寄存器 H、L (PFIORH、PFIORL)                             |      |

|           | 端口 F 控制寄存器 H1 ~ H4、L1 ~ L4(PFCRH1 ~ PFCRH4、PFCRL1 ~ PFCRL4) |      |

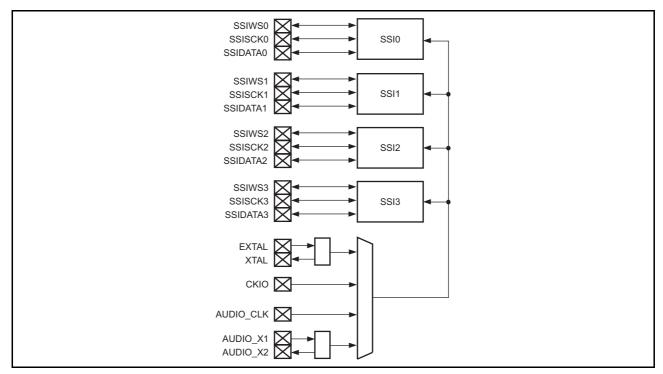

|           | IRQOUT 功能控制寄存器(IFCR)                                        |      |

|           | SSI 过采样时钟选择寄存器(SCSR)                                        |      |

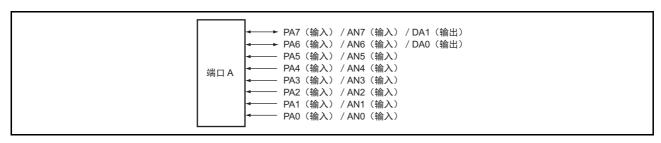

|           | #口 A 的功能转换                                                  |      |

|           | 时的注意事项                                                      |      |

| 23.4 区用中  | 门的任息事例                                                      | 002  |

| 第 26 章 l  | /O 端口                                                       | 883  |

|           |                                                             |      |

|           | A                                                           |      |

|           |                                                             |      |

|           | 寄存器说明端口 A 数据寄存器 L (PADRL)                                   |      |

|           |                                                             |      |

|           | B                                                           |      |

|           | 寄存器说明                                                       |      |

|           | 端口B数据寄存器L (PBDRL)                                           |      |

|           | 端口B端口寄存器L (PBPRL)                                           |      |

|           | C                                                           |      |

|           | 寄存器说明                                                       |      |

|           | 端口C数据寄存器L(PCDRL)                                            |      |

| 26.4.3    | 端口C端口寄存器L(PCPRL)                                            | 889  |

| 26.5 端口1  | D                                                           | 890  |

| 26.5.1    | 寄存器说明                                                       | 890  |

| 26.5.2    | 地口 D 数据字字照 I (DDDDI)                                        | 891  |

|           | 端口 D 数据寄存器 L (PDDRL)                                        | 071  |

|           | - 端口 D 数据奇存器 L (PDDRL)<br>- 端口 B 端口寄存器 L (PDPRL)            |      |

| 26.6.1                 | 寄存器说明                                         | 893 |

|------------------------|-----------------------------------------------|-----|

| 26.6.2                 | 端口 E 数据寄存器 L (PEDRL)                          | 894 |

| 26.6.3                 | 端口 E 端口寄存器 L (PEPRL)                          |     |

| 26.7 端口                | 7 F                                           | 896 |

| 26.7.1                 | 寄存器说明                                         | 896 |

| 26.7.2                 | 端口F数据寄存器H、L (PFDRH、PFDRL)                     | 897 |

| 26.7.3                 | 端口F端口寄存器H、L(PFPRH、PFPRL)                      | 899 |

| 26.8 使月                | 目时的注意事项                                       | 901 |

| 第 27 章                 | 内部 RAM                                        | 902 |

| 27.1 特点                | <u> </u>                                      | 902 |

| 27.2 使月                | 月时的注意事项                                       | 903 |

| 27.2.1                 | 页竞争                                           | 903 |

| 27.2.2                 | 关于 RAME 位、 RAMWE 位                            | 903 |

| 27.2.3                 | 指令配置禁止区域                                      | 903 |

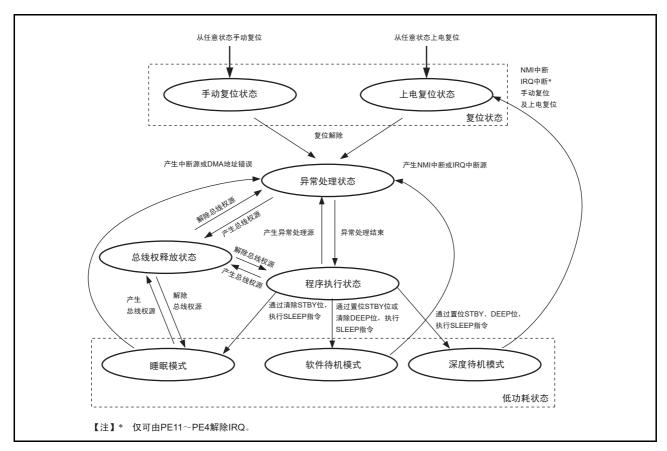

| 第 28 章                 | 低功耗模式                                         | 904 |

|                        | <u> </u>                                      |     |

| 28.1.1                 | 低功耗模式的种类                                      |     |

|                        | 字器说明                                          |     |

| 28.2.1                 | 待机控制寄存器 (STBCR)                               |     |

| 28.2.2                 | 待机控制寄存器 2 (STBCR2)                            |     |

| 28.2.3                 | 待机控制寄存器 3 (STBCR3)                            |     |

| 28.2.4                 | 待机控制寄存器 4 (STBCR4)                            |     |

| 28.2.5                 | 待机控制寄存器 5 (STBCR5)                            |     |

| 28.2.6                 | 待机控制寄存器 6 (STBCR6)                            |     |

| 28.2.7                 | 系统控制寄存器 1 (SYSCR1)                            |     |

| 28.2.8                 | 系统控制寄存器 2 (SYSCR2)                            |     |

| 28.2.9                 | 系统控制寄存器 3 (SYSCR3)                            |     |

| 28.2.10                | 深度待机控制寄存器 (DSCTR)                             |     |

| 28.2.11                | 深度待机控制寄存器 2 (DSCTR2)                          |     |

| 28.2.12                | 深度待机解除源选择寄存器 (DSSSR)                          |     |

| 28.2.13                | 深度待机解除源标志寄存器 (DSFR)                           |     |

| 28.2.14                | 保持用内部 RAM 调整寄存器 (DSRTR)                       |     |

| 28.3 运行                | • • - • •                                     |     |

| 28.3.1                 | 睡眠模式                                          |     |

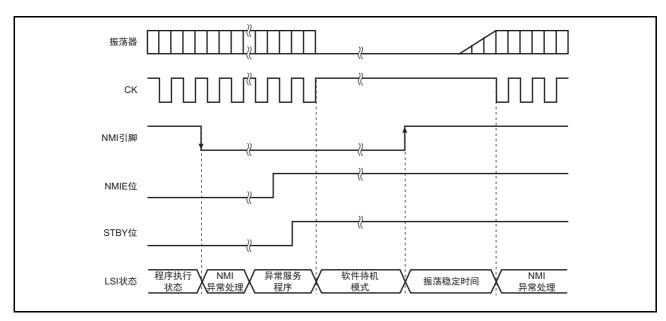

| 28.3.2                 | 软件待机模式                                        |     |

| 28.3.3                 | 软件待机模式的应用例                                    |     |

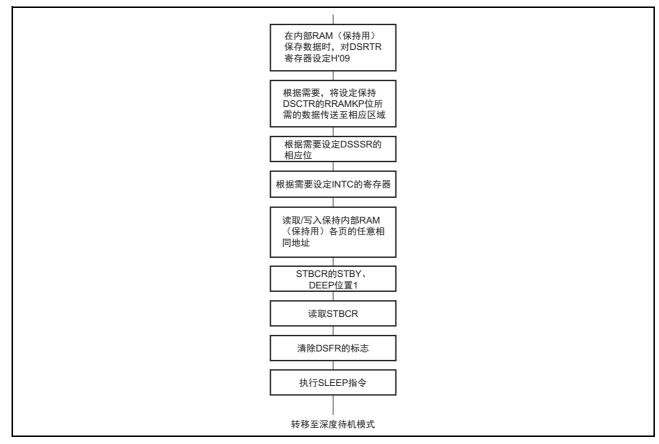

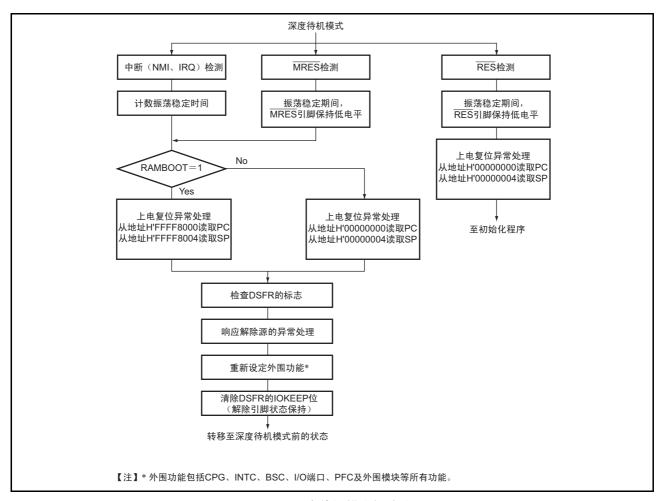

| 28.3.4                 | 深度待机模式                                        |     |

| 28.3.5                 | 模块待机功能                                        |     |

|                        | 目时的注意事项                                       |     |

| 28.4.1                 | 写入寄存器时的注意事项                                   |     |

| 28.4.2<br>28.4.3       | 有关深度待机控制寄存器 2 (DSCTR2)的注意事项<br>上电复位异常处理相关注意事项 |     |

|                        |                                               |     |

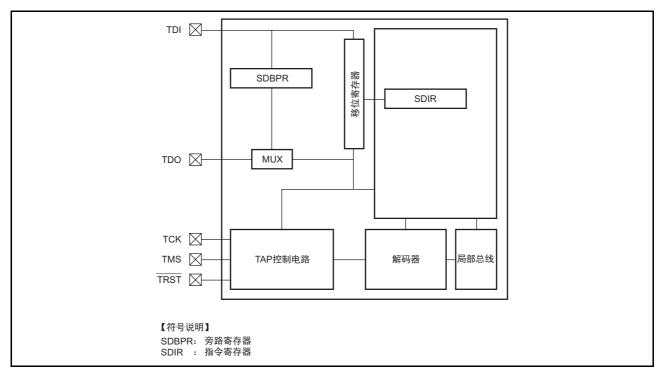

| 第 29 章<br>- 20 1 - 蛙 년 | 用户调试接口 (H-UDI)<br>5                           |     |

|                        | ュ<br>ヘ/ 输出引脚                                  |     |

|                        | ▽ N                                           |     |

| 29.3 可生<br>29.3.1      | テロス                                           |     |

| 29.3.1                 |                                               |     |

|                        | - 14マ司行称 (SDIK)                               |     |

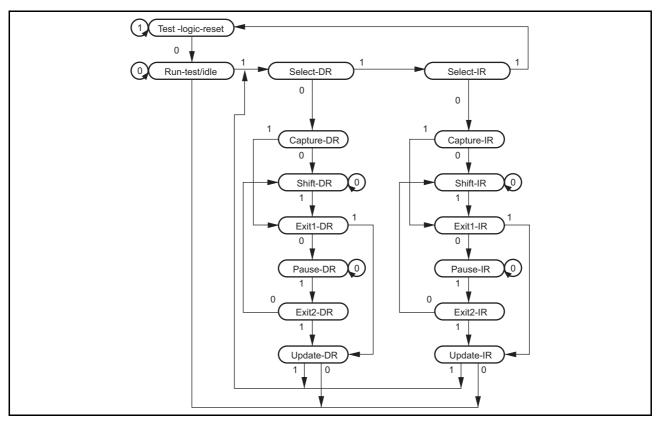

|                        | TΔP 挖制器                                       | 930 |

| 29.4.2 复位结构                     | 931  |

|---------------------------------|------|

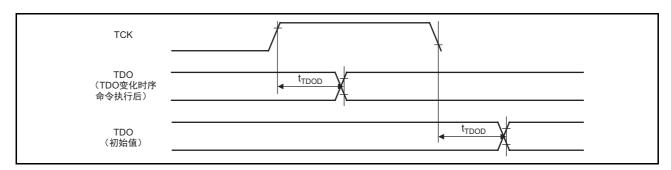

| 29.4.3 TDO 输出时序                 | 931  |

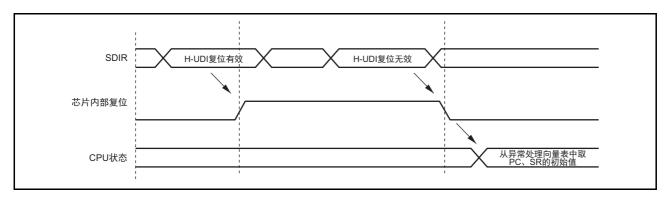

| 29.4.4 H-UDI 复位                 | 932  |

| 29.4.5 H-UDI 中断                 | 932  |

| 29.5 使用时的注意事项                   |      |

| 第 30 章  寄存器一览表                  | 933  |

| 30.1 寄存器地址一览表 (按各功能模块、手册章节编号顺序) | 934  |

| 30.2 寄存器位一览表                    | 953  |

| 30.3 各运行模式的寄存器状态一览表             |      |

| 第 31 章  电特性                     | 995  |

| 31.1 绝对最大额定值                    | 995  |

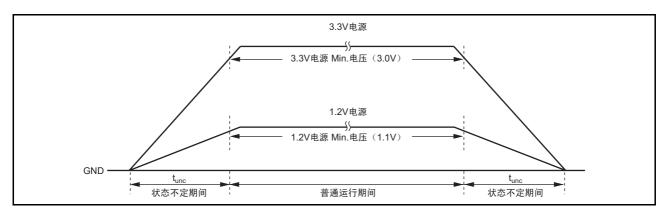

| 31.2 上电、断电顺序                    | 996  |

| 31.3 DC 特性                      | 997  |

| 31.4 AC 特性                      | 1002 |

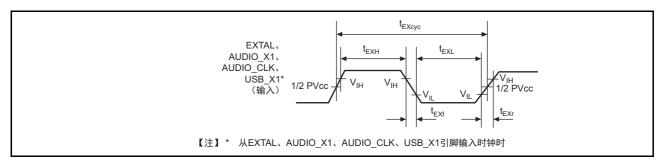

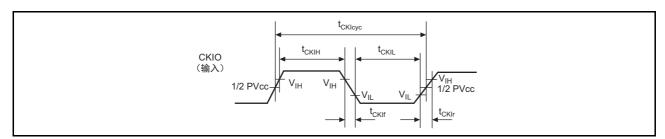

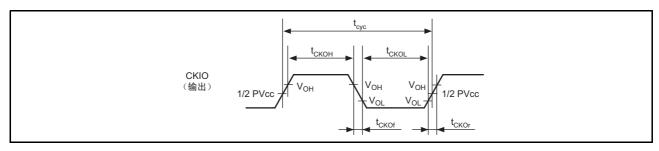

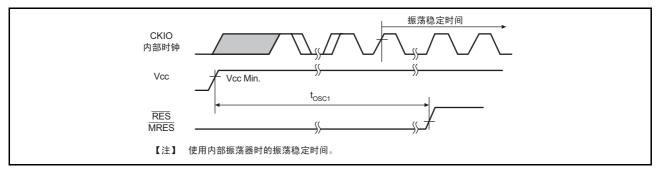

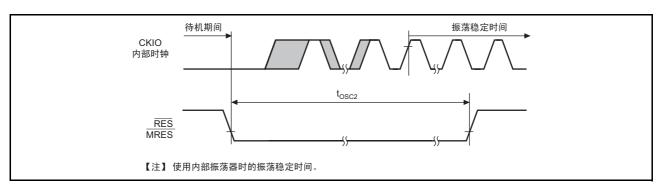

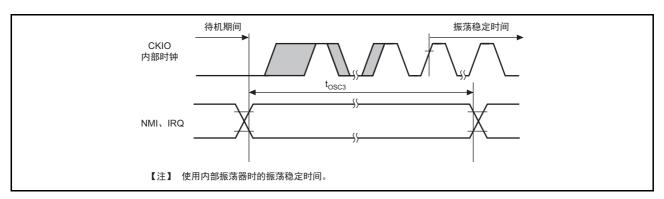

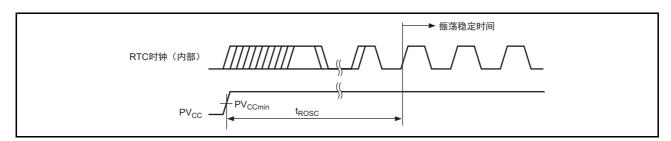

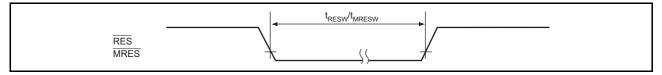

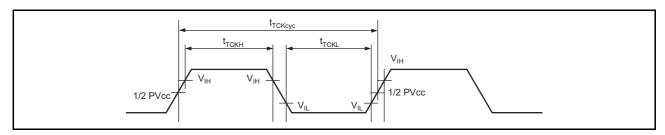

| 31.4.1 时钟时序                     | 1002 |

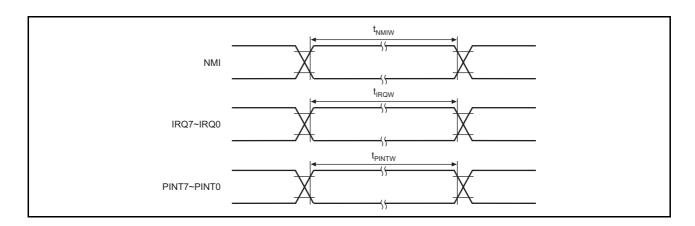

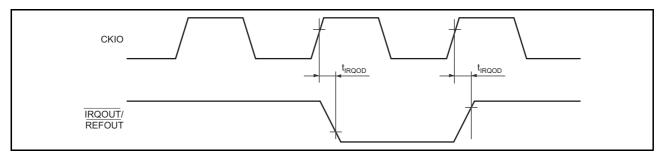

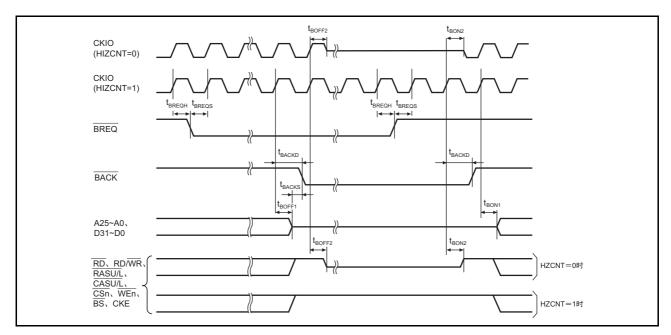

| 31.4.2 控制信号时序                   | 1005 |

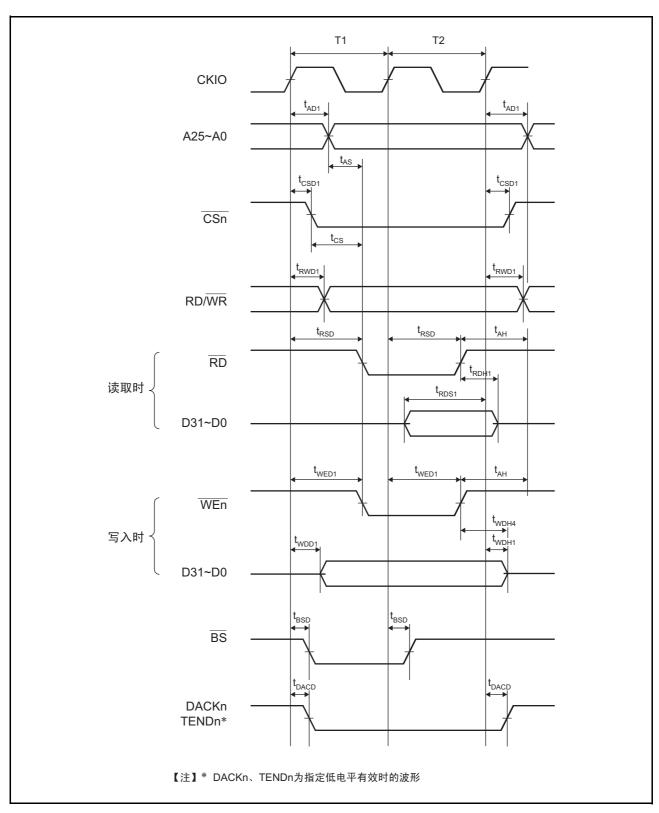

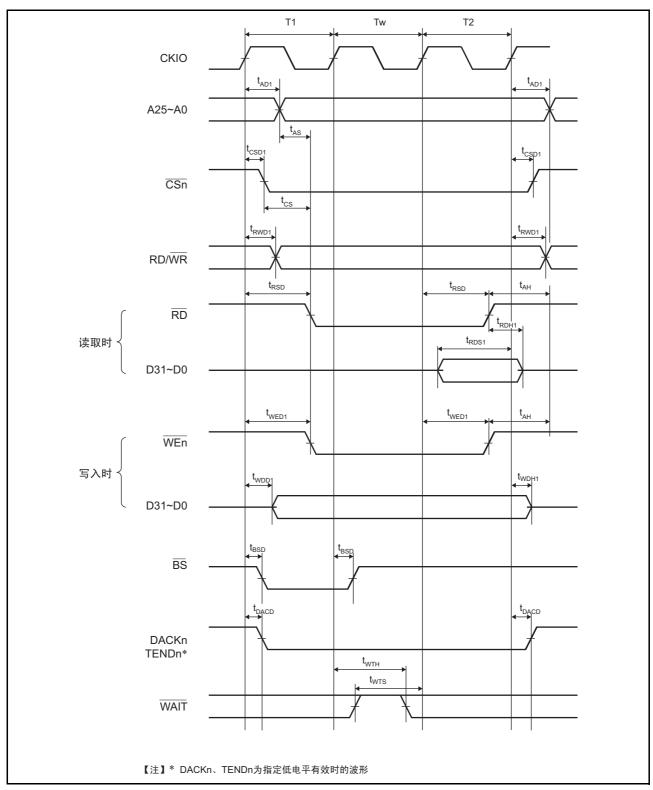

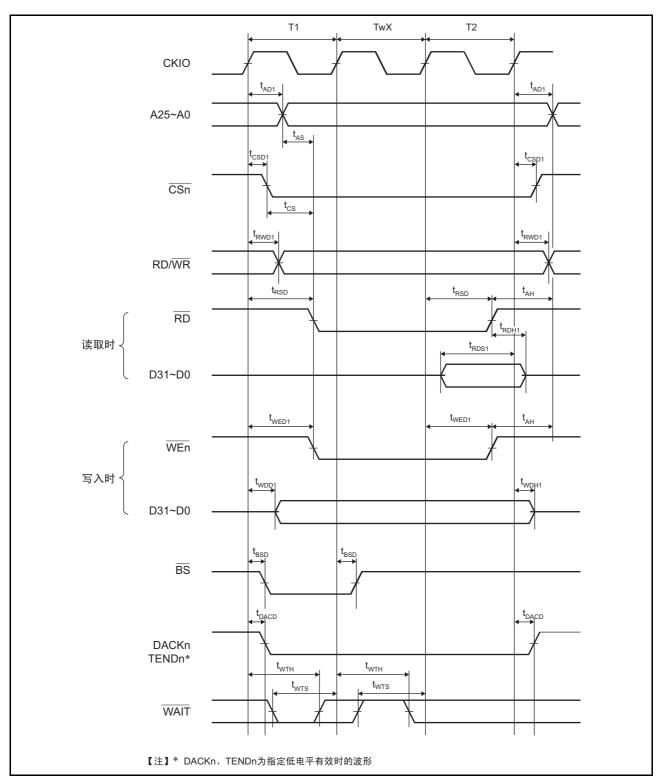

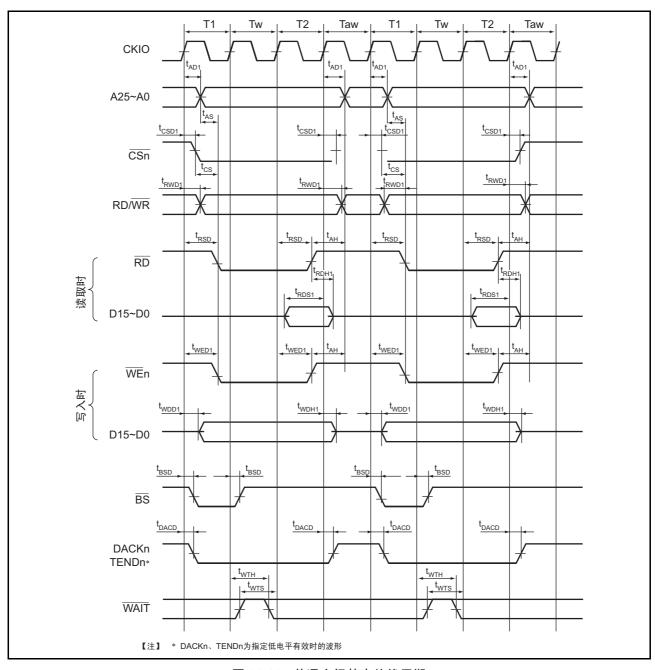

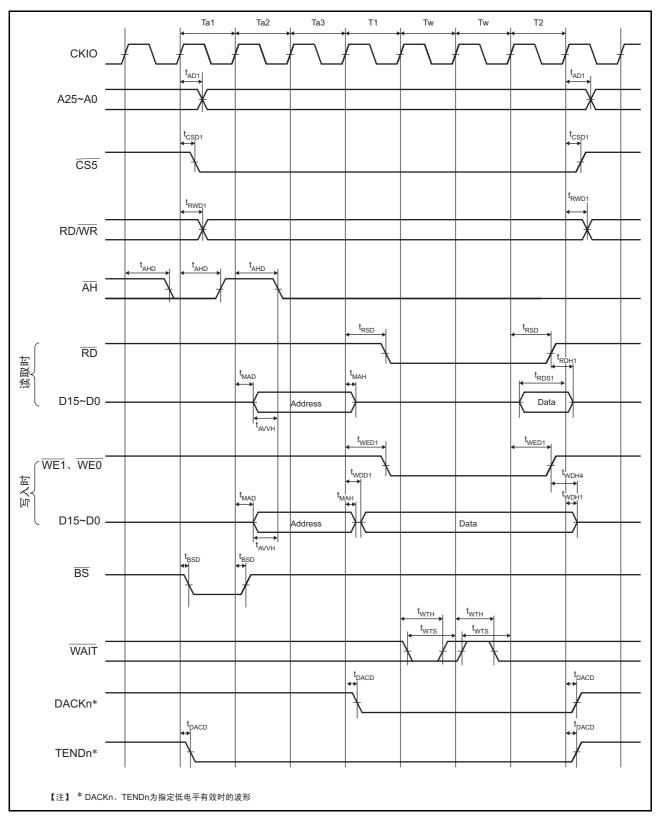

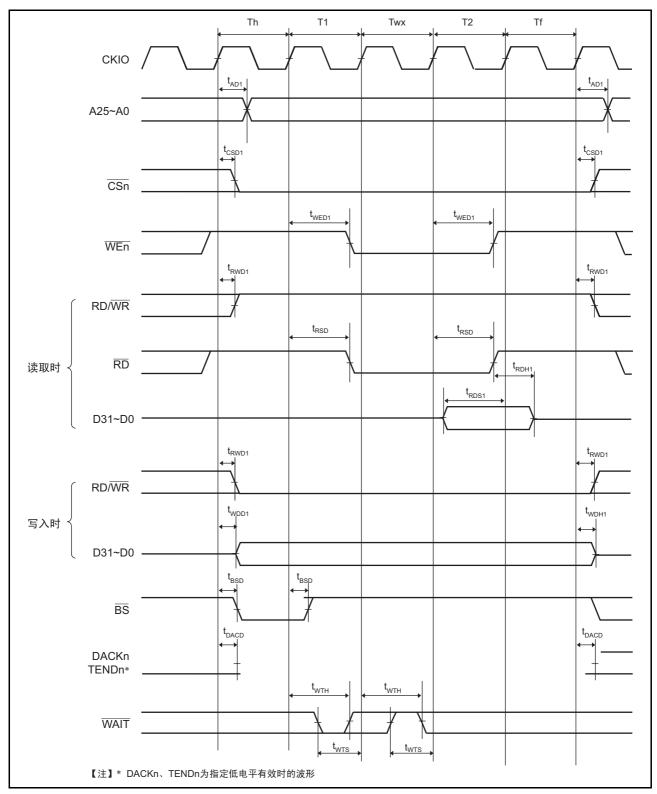

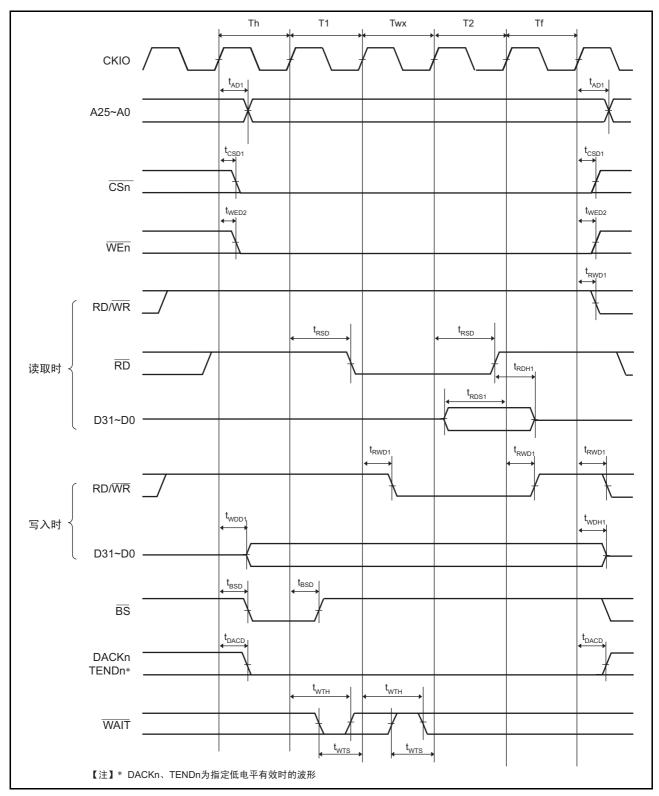

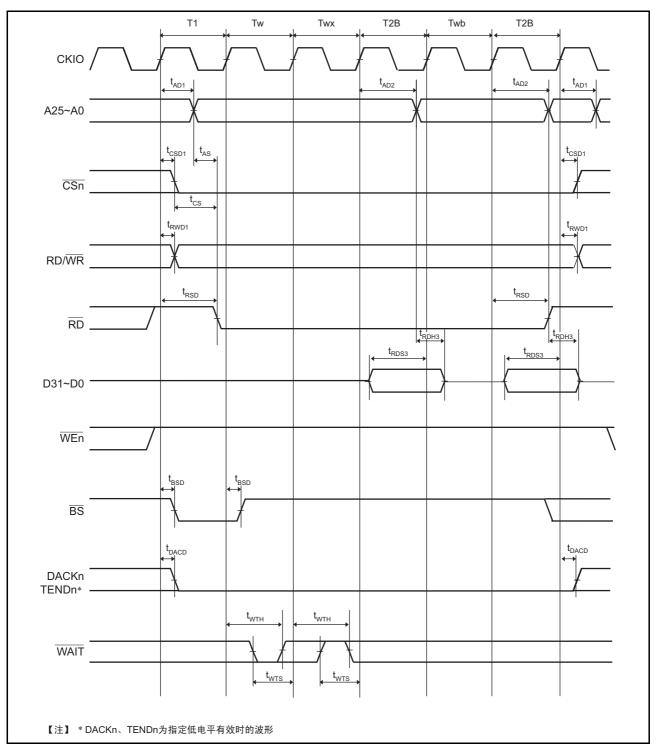

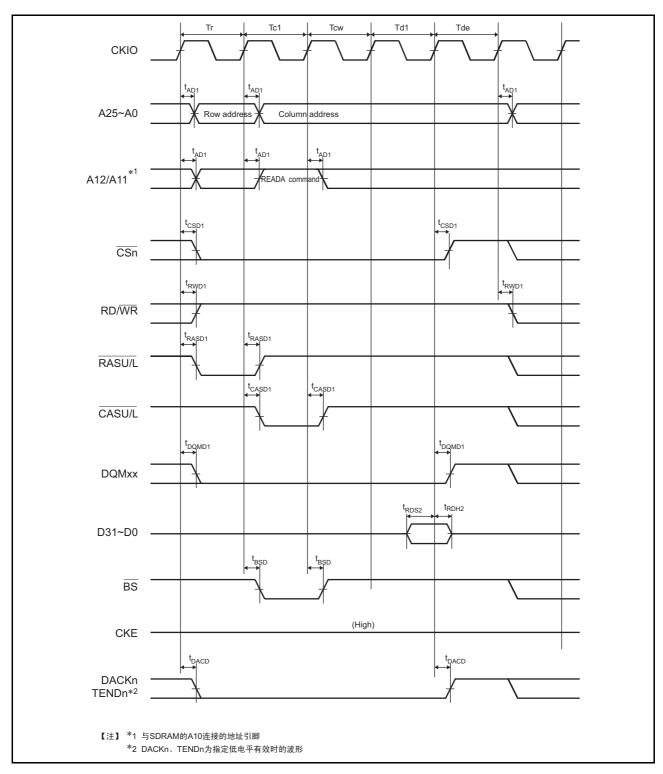

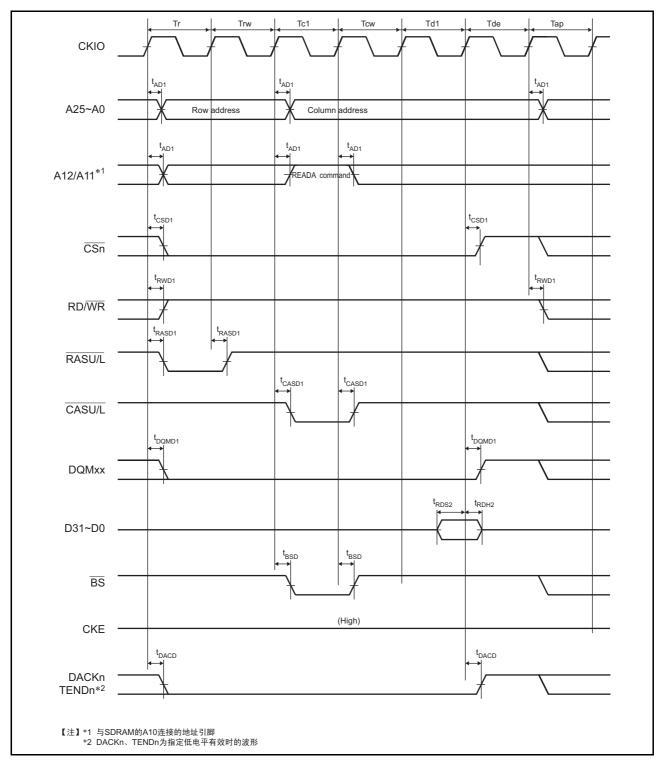

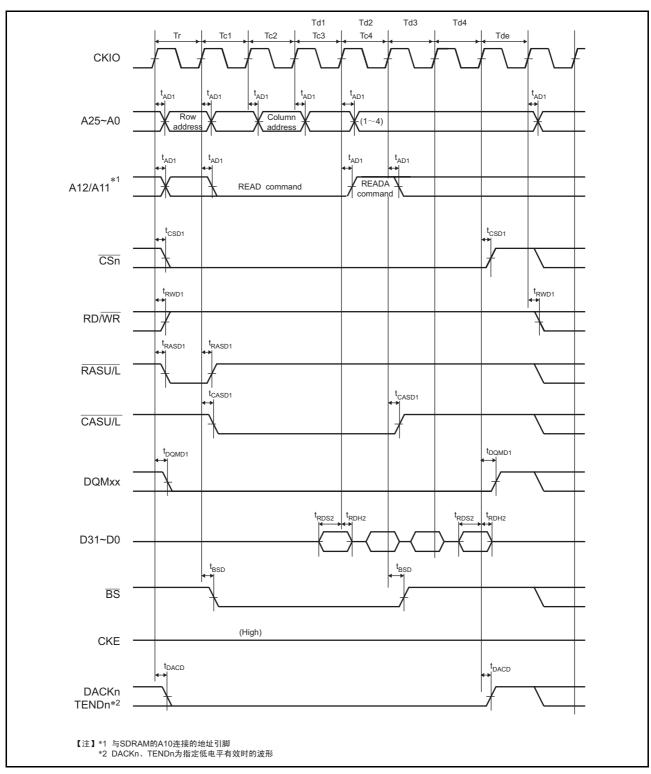

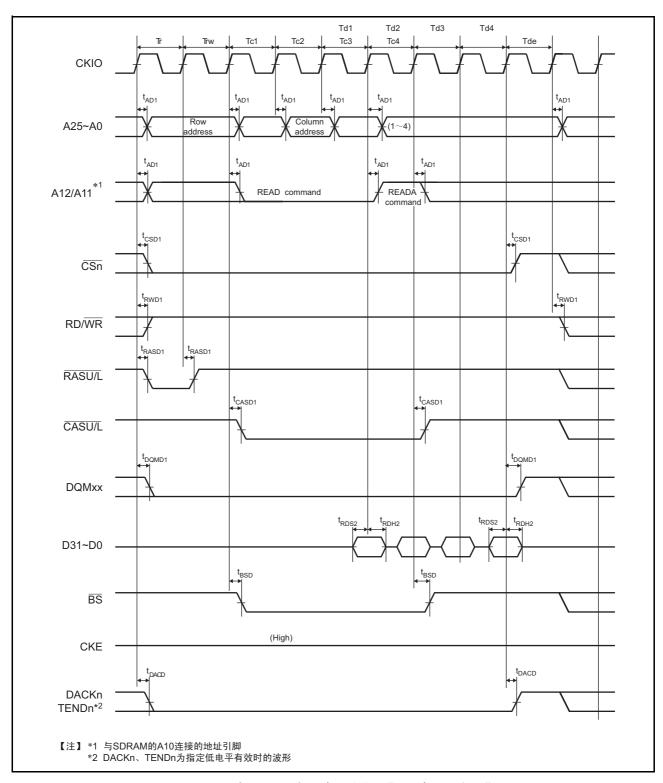

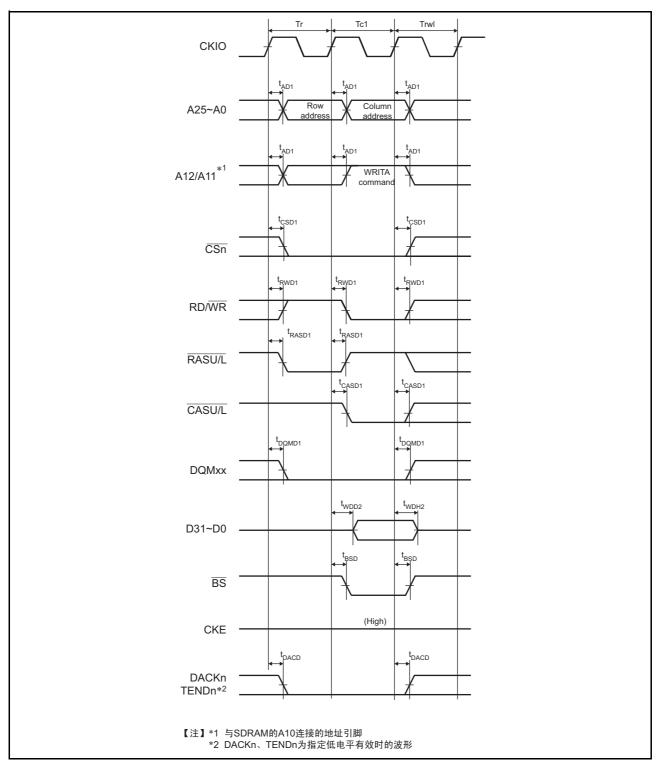

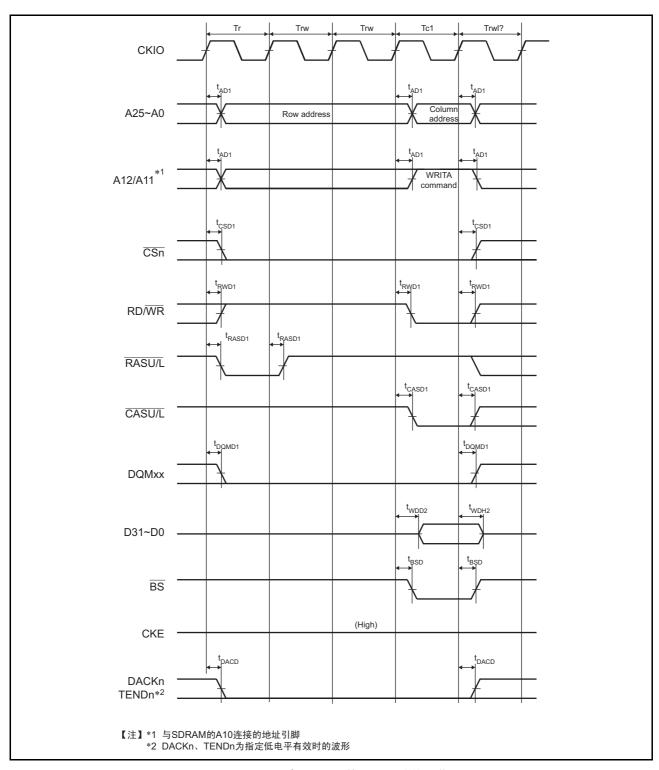

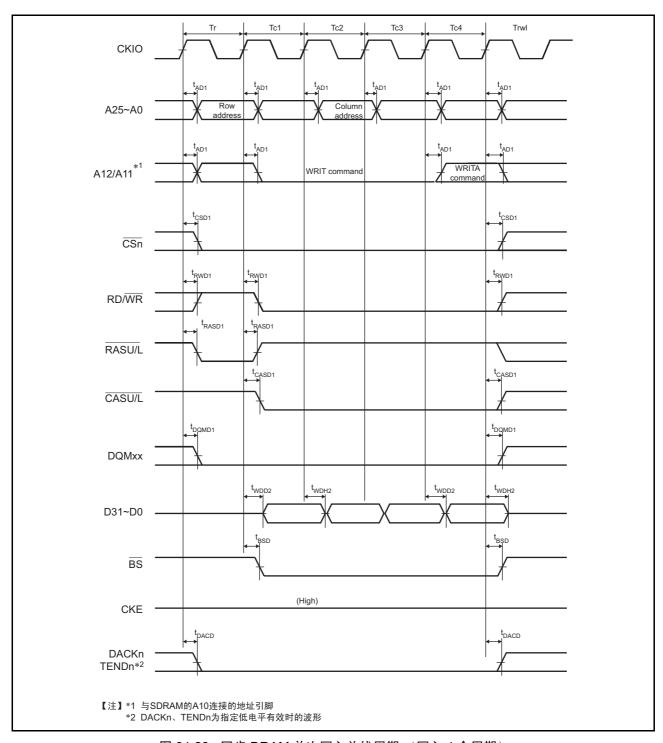

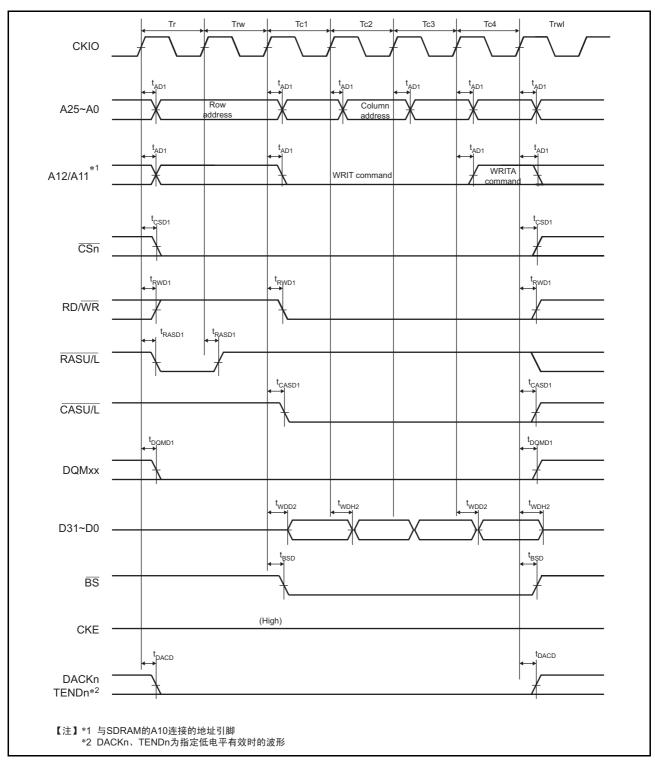

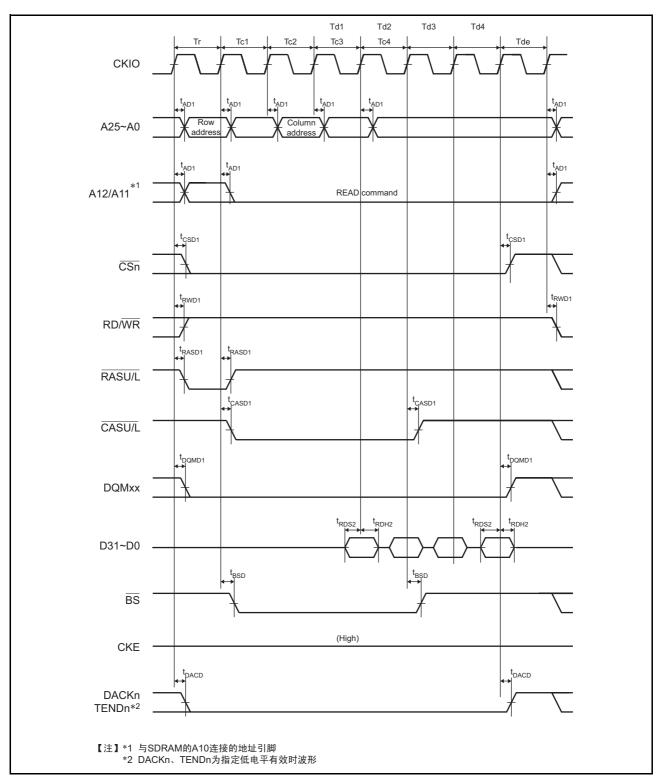

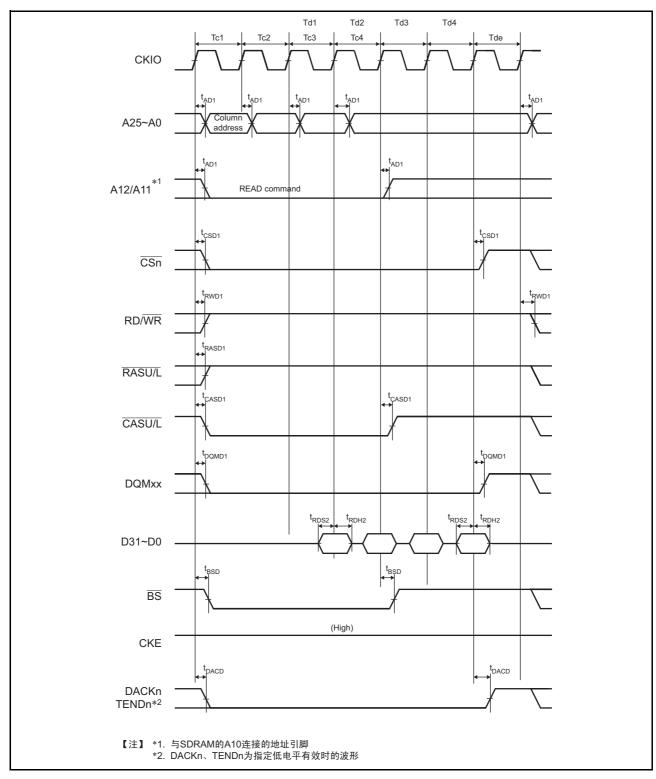

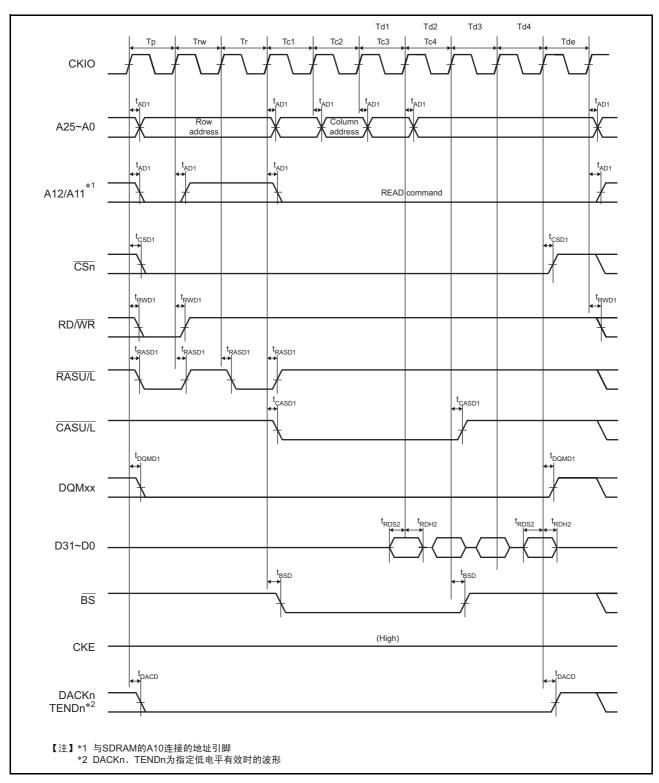

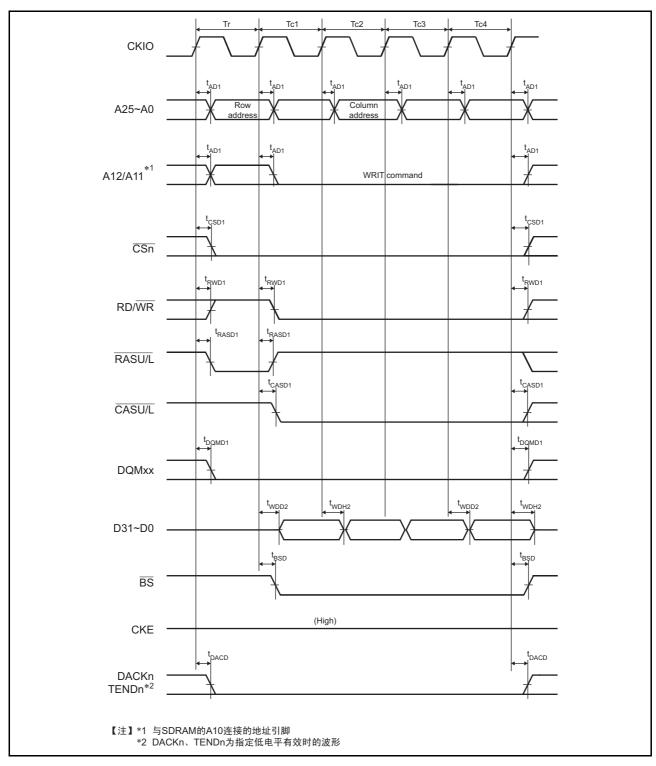

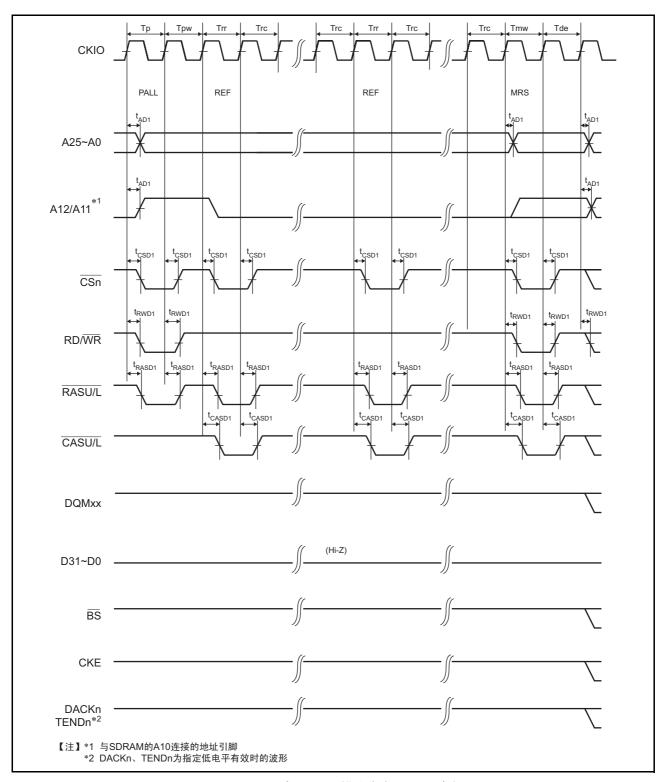

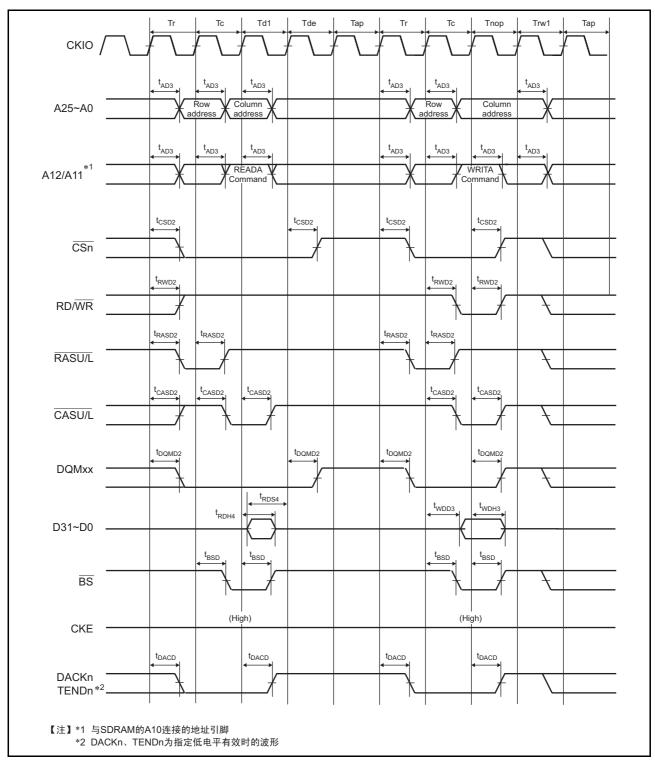

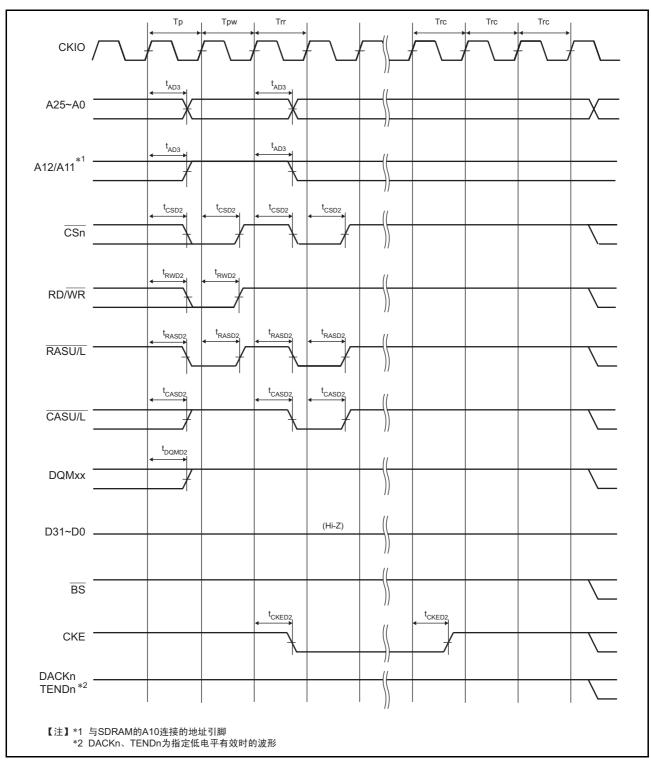

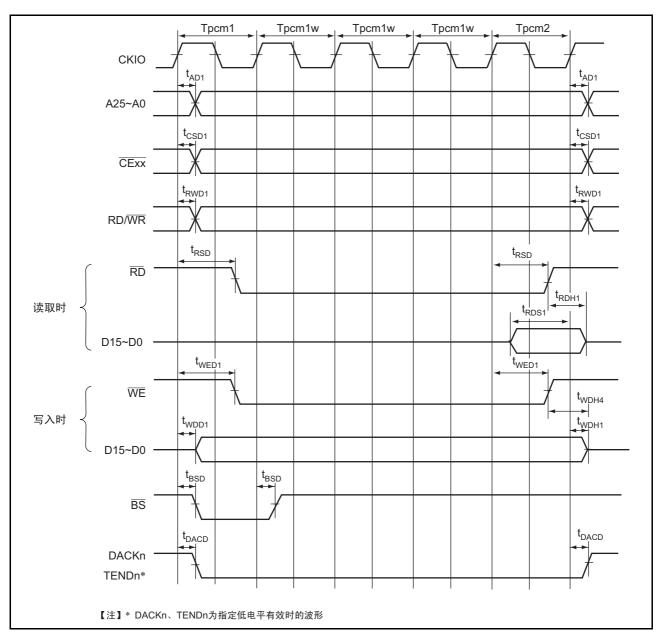

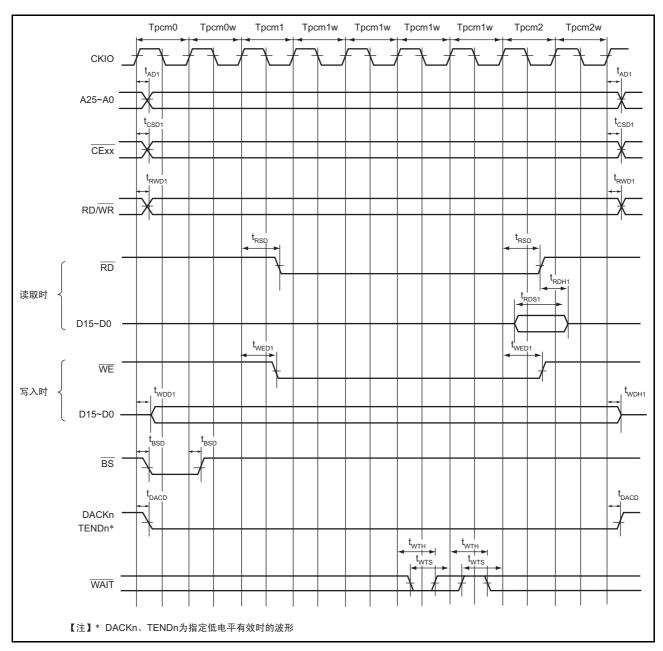

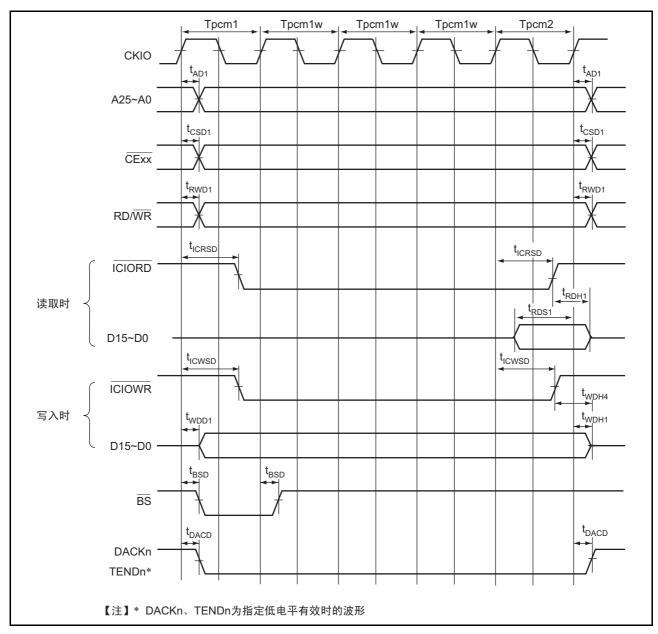

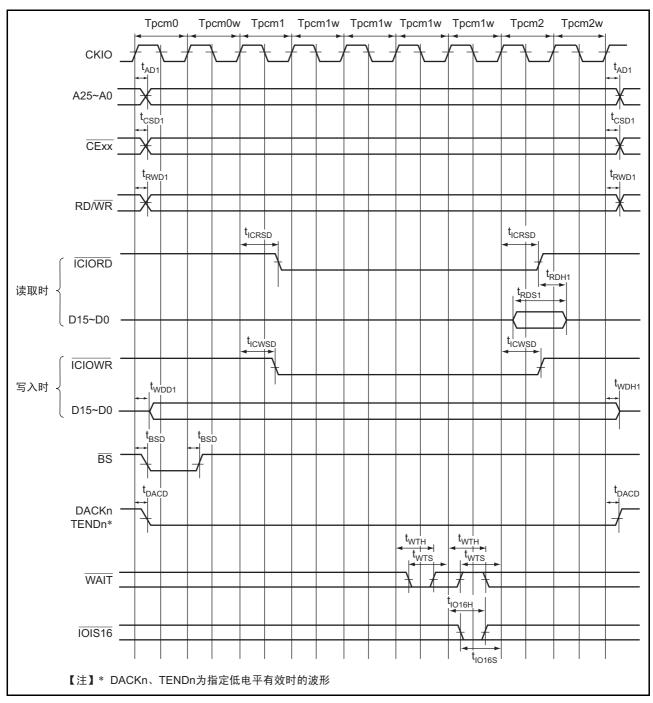

| 31.4.3 总线时序                     | 1007 |

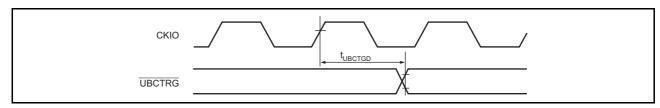

| 31.4.4 UBC 时序                   | 1041 |

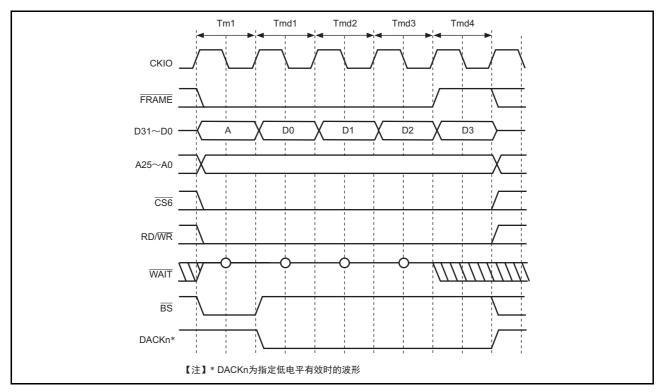

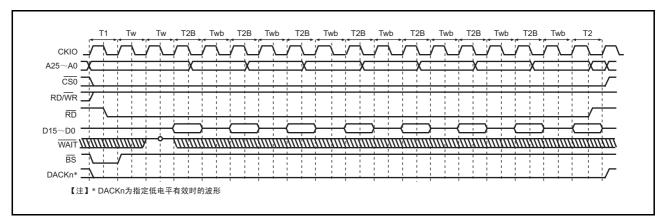

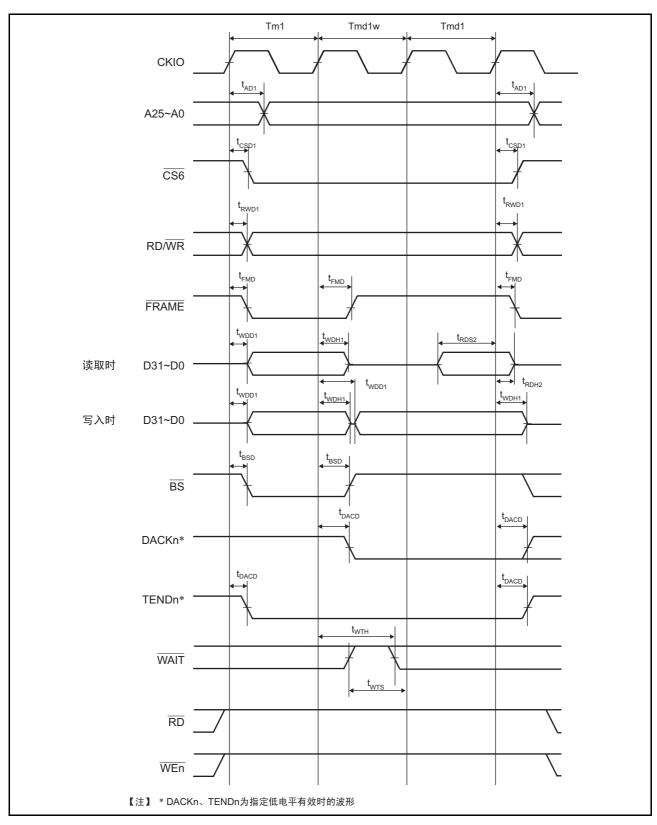

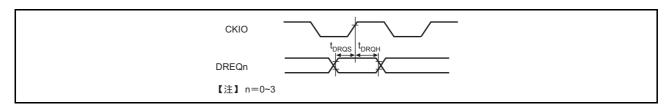

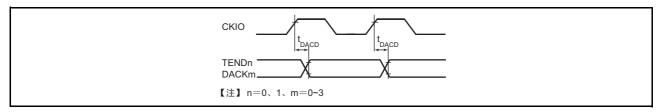

| 31.4.5 DMAC 时序                  | 1041 |

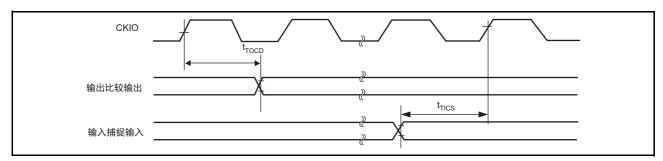

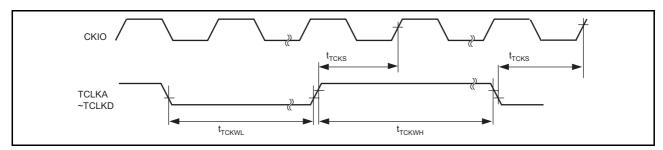

| 31.4.6 MTU2 时序                  | 1042 |

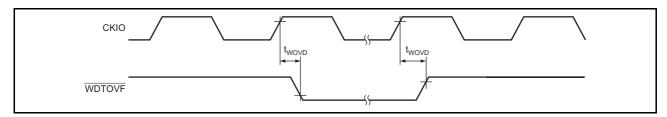

| 31.4.7 WDT 时序                   | 1043 |

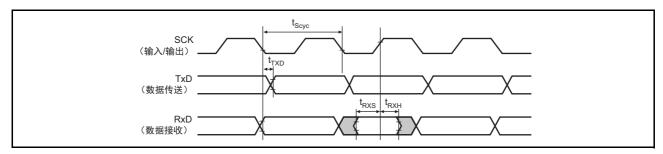

| 31.4.8 SCIF 时序                  | 1043 |

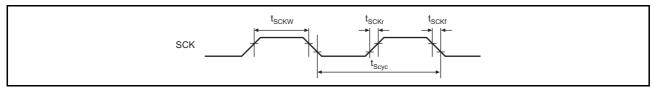

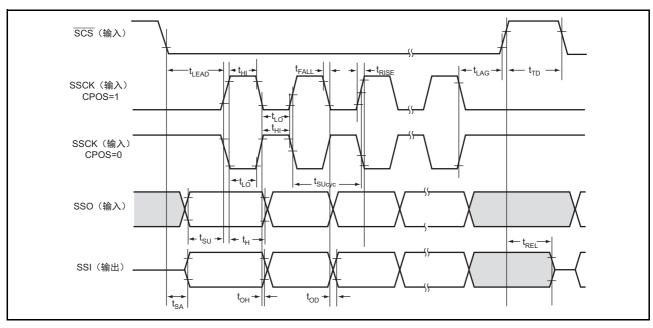

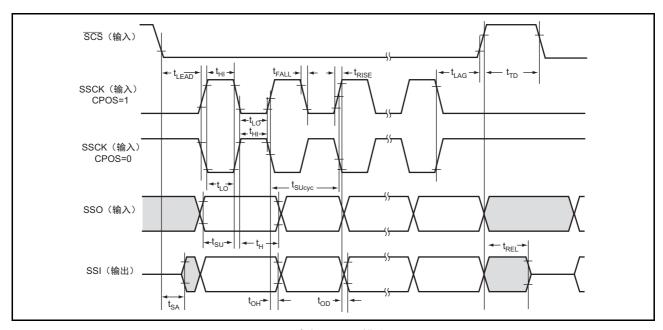

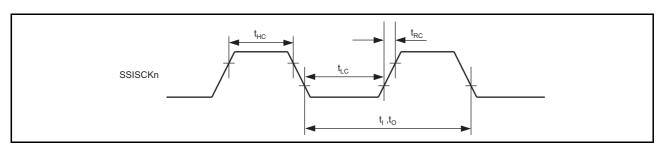

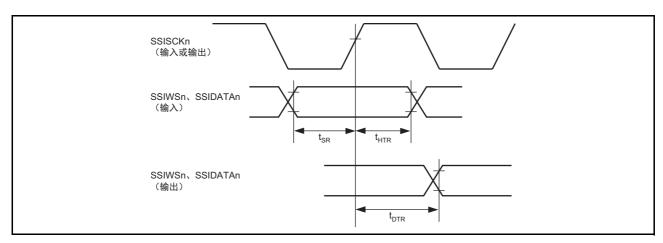

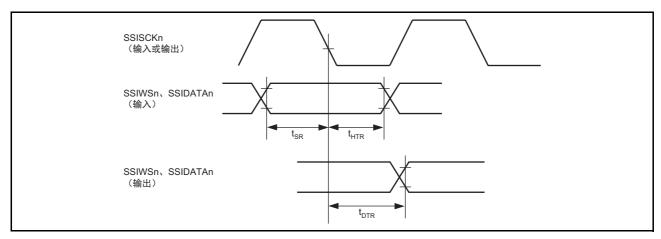

| 31.4.9 SSU 时序                   | 1044 |

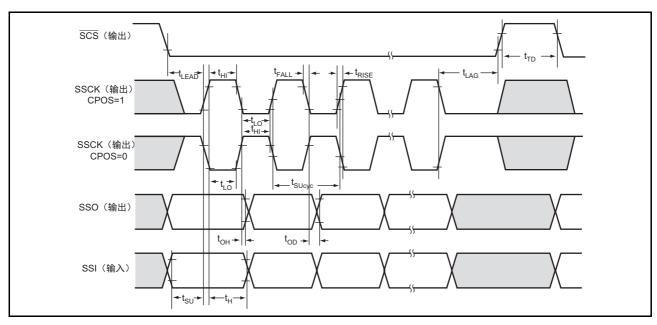

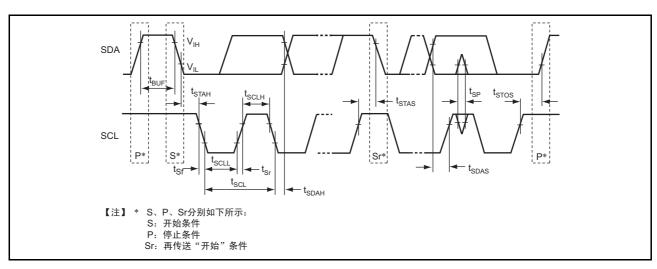

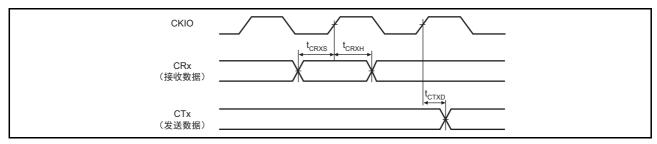

| 31.4.10 IIC3 时序                 |      |

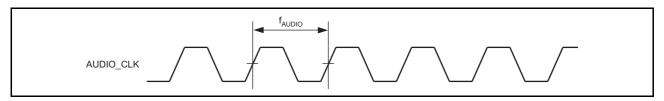

| 31.4.11 SSI 时序                  | 1048 |

| 31.4.12 RCAN-TL1 时序             |      |

| 31.4.13 ADC 时序                  |      |

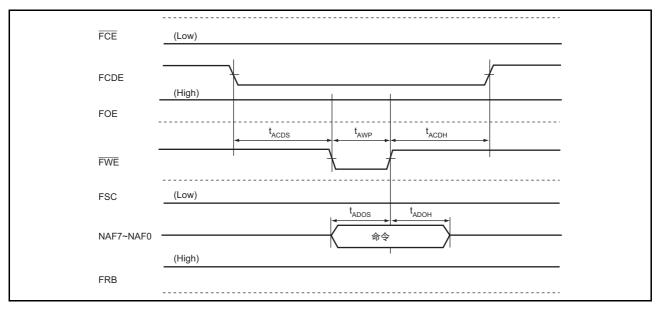

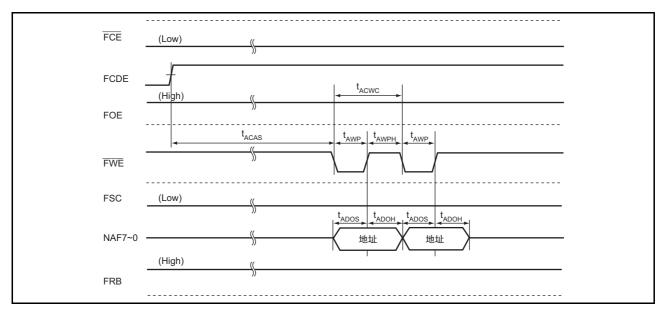

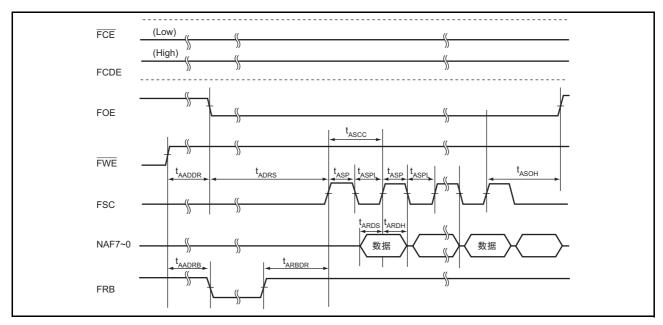

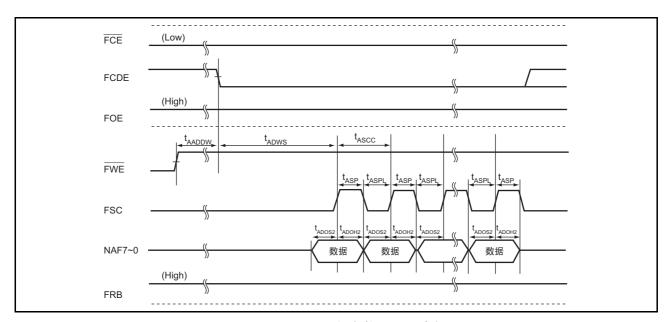

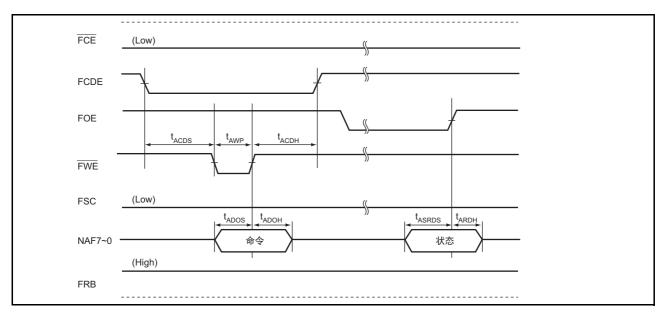

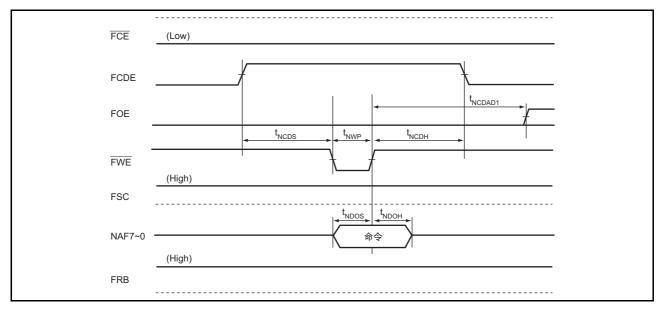

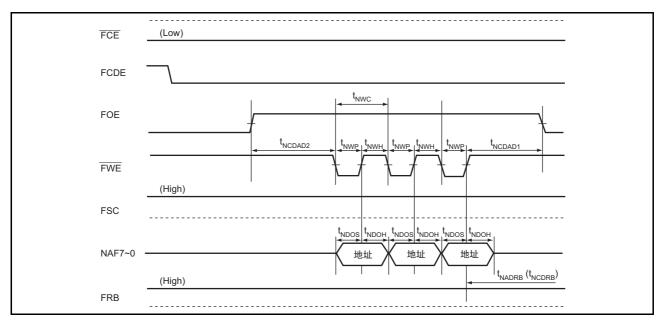

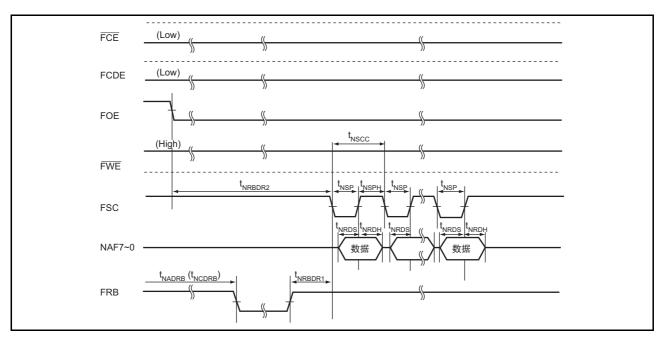

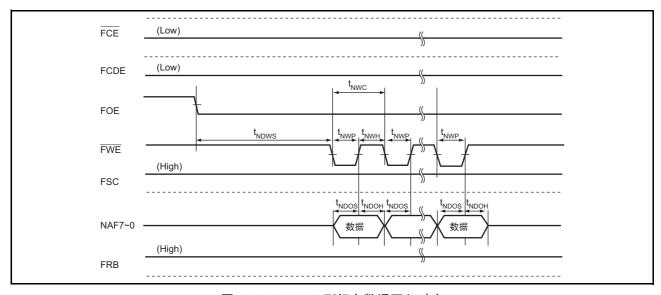

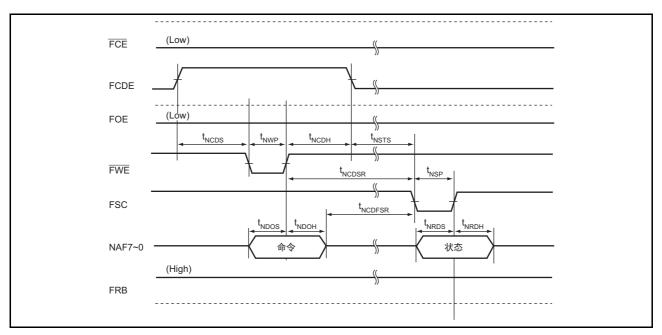

| 31.4.14 FLCTL 时序                |      |

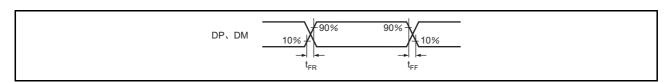

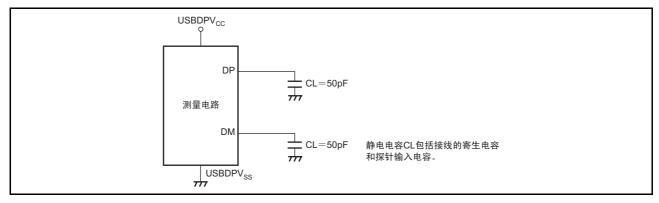

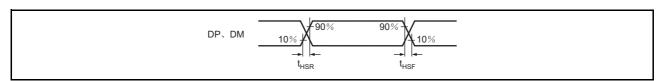

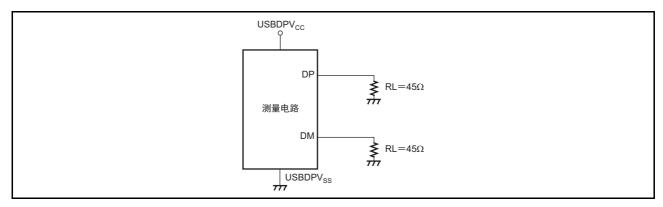

| 31.4.15 USB 时序                  |      |

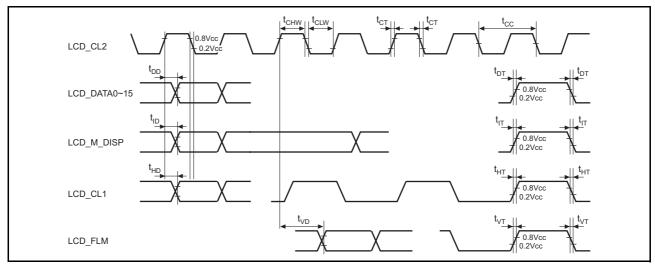

| 31.4.16 LCDC 时序                 |      |

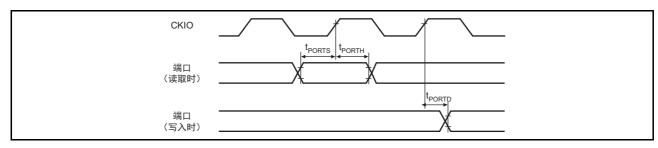

| 31.4.17 I/O 端口时序                |      |

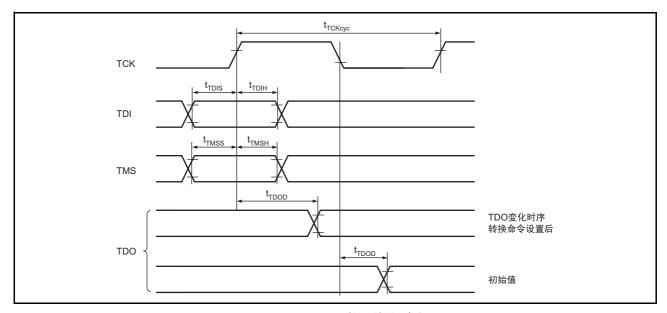

| 31.4.18 H-UDI 时序                | 1061 |

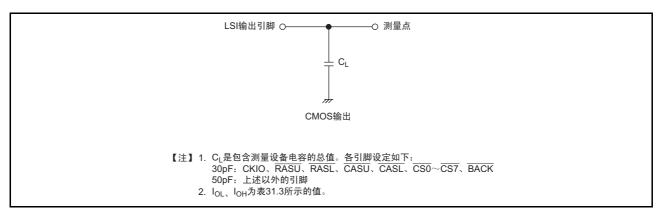

| 31.4.19 AC 特性测量条件               | 1062 |

| 31.5 A/D 转换器特性                  |      |

| 31.6 D/A 转换器特性                  |      |

| 31.7 使用时的注意事项                   | 1064 |

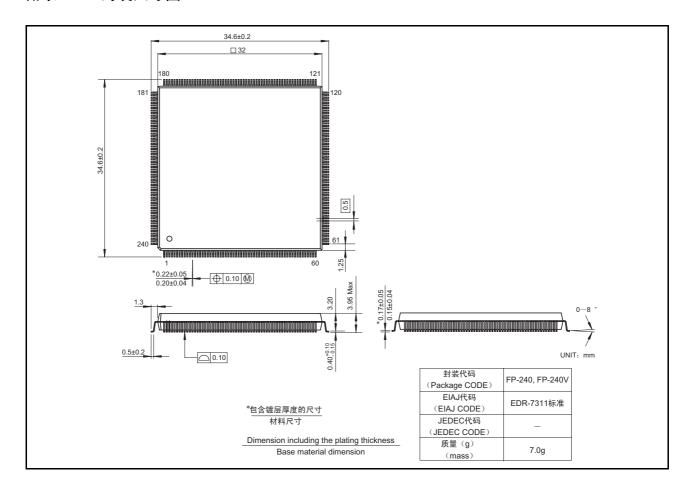

| 附录                              | 1065 |

| 附录 A. 引脚状态                      | 1065 |

| 附录 B. 封装尺寸图                     | 1070 |

| ± ¬1                            | 4074 |

SH7203 群 第 1 章 概要

# 第1章 概要

# 1.1 SH7203 的特点

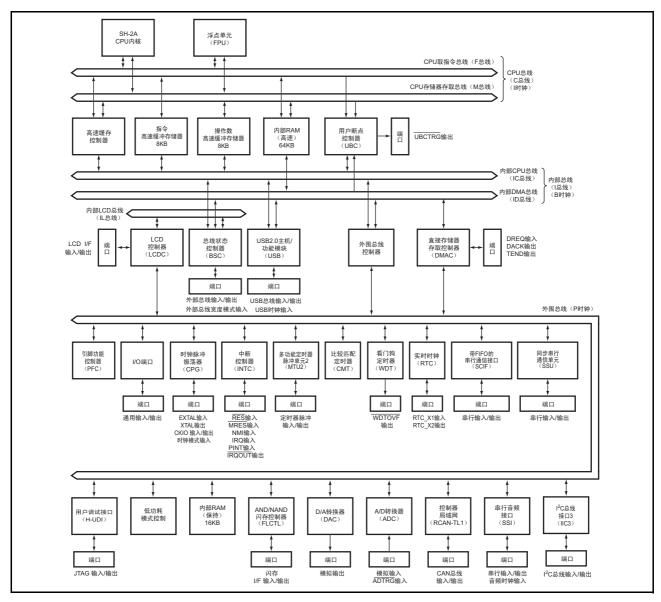

本 LSI 以瑞萨科技独创的 RISC (精简指令系统计算机)结构 CPU 为内核,是集成了系统构成所需外围功能的 RISC 单片机。

本 LSI 采用与 SH-1、 SH-2、 SH-2E 单片机在目标代码级高位兼容的 SH-2A CPU,由于具备 RISC 结构的指令系统,并采用超标量 / 哈佛体系结构,所以指令执行速度得以飞速提升。另外,采用与直接存储器存取控制器(DMAC)独立的内部 32 位总线结构,强化了数据处理能力。本 LSI 的 CPU 可构成以往单片机不可能实现的、需高速实时控制的应用程序等低成本、高性能 / 高功能的系统。

本LSI 内置浮点单元(FPU)与高速缓存。此外,还内置 64KB 高速内部 RAM、用于保存 16KB 数据的 RAM、多功能定时器脉冲单元 2(MTU2)、比较匹配定时器(CMT)、实时时钟(RTC)、带 FIFO 的串行通信接口(SCIF)、同步串行通信单元(SSU)、I<sup>2</sup>C 总线接口 3(IIC3)、串行音频接口(SSI)、控制器局域网(RCAN-TL1)、A/D 转换器、D/A 转换器、AND/NAND 闪存控制器(FLCTL)、USB2.0 主机 / 功能模块(USB)、中断控制器(INTC)及 I/O 端口等,作为系统构成所需的外围功能。

本 LSI 支持外部存储器存取功能,可与存储器或外围 LSI 直接连接。所以,可大幅降低系统成本。另外,本 LSI 的 I/O 引脚带有抑制引脚电位变为中间电位状态的弱保持电路,无需固定输入电平的外接电路,也可大幅度减少元器件个数。

本 LSI 的特点如表 1.1 所示。

# 表 1.1 SH7203 的特点

| 项目        | 特 点                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

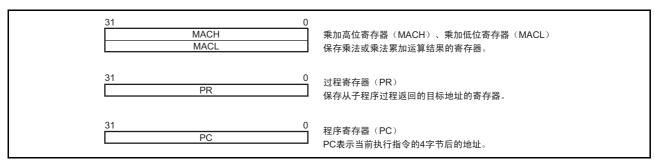

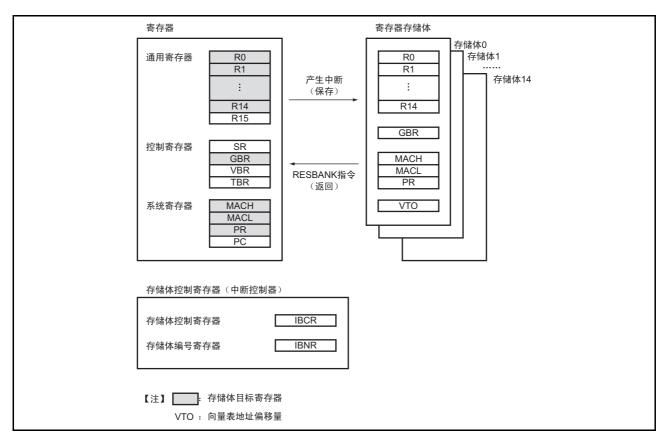

| CPU       | <ul> <li>瑞萨独创的 SuperH 体系结构</li> <li>与 SH-1、SH-2、SH-2E 在目标代码级高位兼容</li> <li>32 位内部数据总线</li> <li>通用寄存器体系结构</li> <li>16 个 32 位通用寄存器</li> <li>4 个 32 位控制寄存器</li> <li>4 个 32 位系统寄存器</li> <li>响应高速中断的寄存器存储体</li> <li>RISC 结构的指令系统 (与 SH 系列高位兼容)</li> <li>指令长度:提高编码效率的 16 位基本指令与提高性能 / 适用性的 32 位指令加载存储结构</li> <li>延迟转移指令</li> <li>基于 C 语言的指令系统</li> <li>包含 FPU 的 2 条指令同时执行型超标量</li> <li>指令执行时间:最多 2 条指令 / 周期</li> <li>地址空间:4G 字节</li> <li>内置乘法器</li> <li>5 段流水线</li> <li>哈佛体系结构</li> </ul>       |

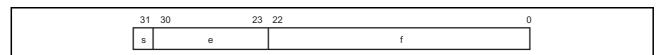

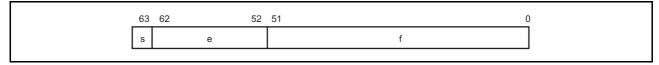

| 浮点单元(FPU) | <ul> <li>内置浮点协处理器</li> <li>支持单精度 (32位)及双精度 (64位)</li> <li>支持符合 IEEE754 标准的数据类型及异常</li> <li>舍入模式:就近舍入及向 0 舍入</li> <li>非规格化数的处理:舍入为 0</li> <li>浮点寄存器 <ul> <li>16个32位浮点寄存器(单精度×16字或双精度×8字)</li> <li>2个32位浮点系统寄存器</li> <li>支持 FMAC (乘法及累加)指令</li> <li>支持 FDIV (除法)/FSQRT (平方根)指令</li> <li>支持 FLDIO/FLDI1 (加载常数 0/1)指令</li> <li>指令执行时间</li> <li>等待时间(FMAC/FADD/FSUB/FMUL):3个周期(单精度)、8个周期(双精度)节距(FMAC/FADD/FSUB/FMUL):1个周期(单精度)、6个周期(双精度)【注】FMAC 仅支持单精度。</li> <li>5段流水线</li> </ul> </li> </ul> |

| 项目                   | 特 点                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

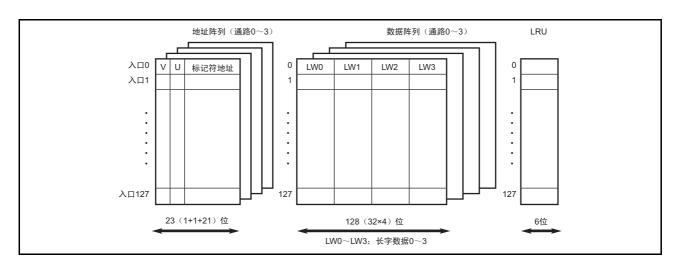

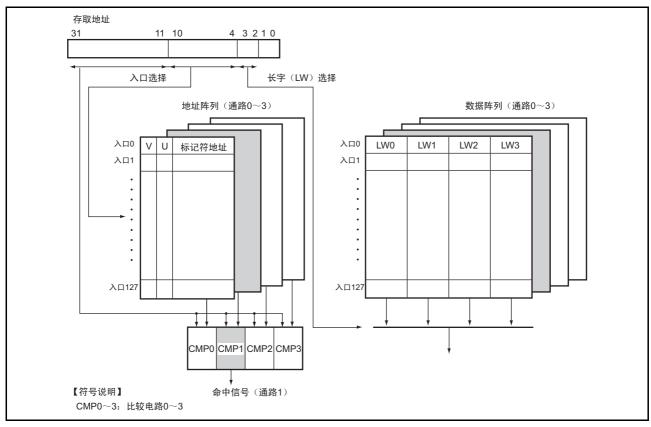

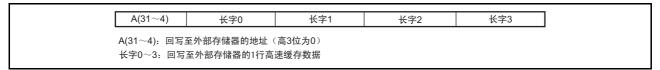

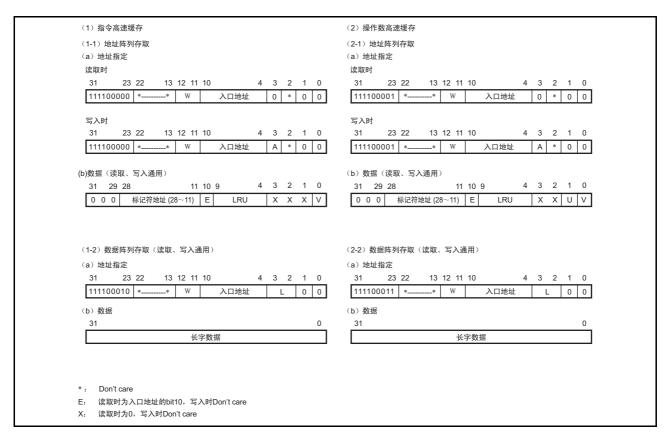

| 高速缓冲存储器              | <ul> <li>指令高速缓存: 8K 字节</li> <li>操作数高速缓存: 8K 字节</li> <li>各有 128 个入口 / 通路、4 路集联、16 字节的块长度</li> <li>回写、直写、LRU 置换算法</li> <li>具有通路锁定功能 (仅限操作数高速缓存): 可锁定通路 2、通路 3</li> </ul>                                                                                                                                                                                                                                              |

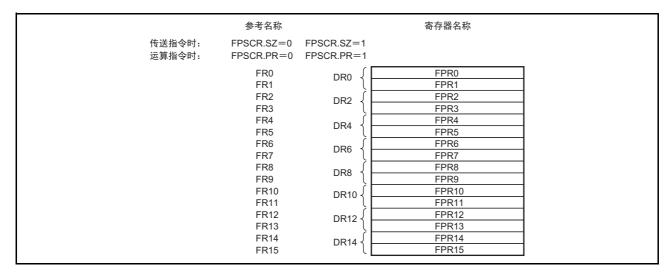

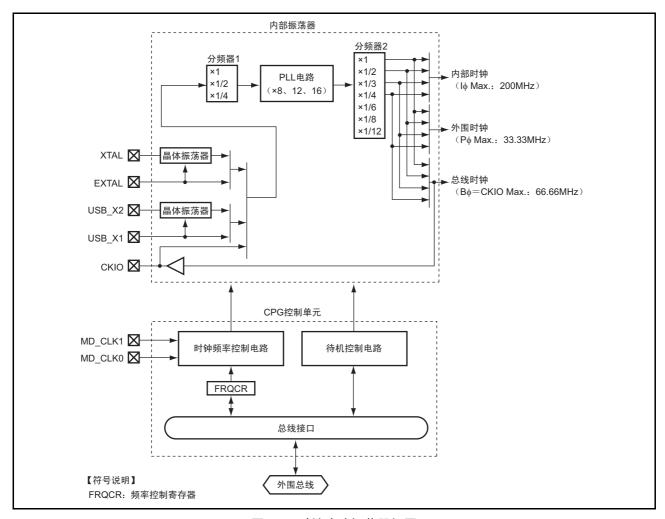

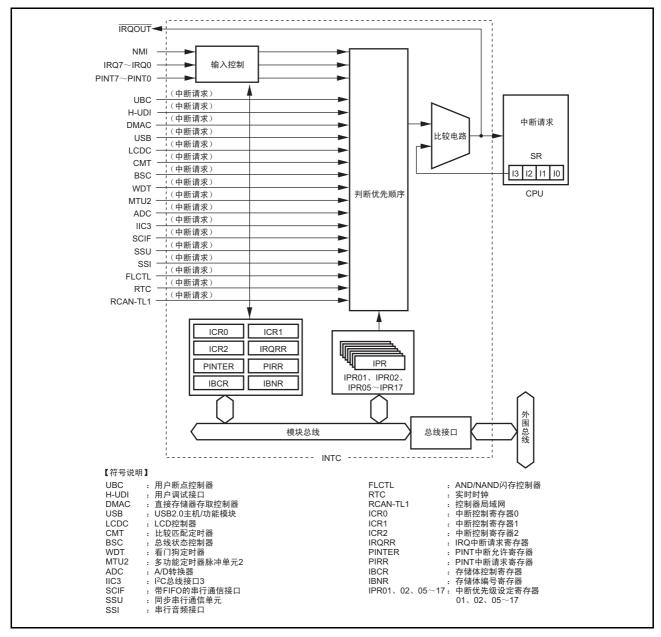

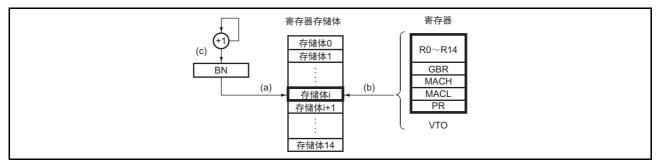

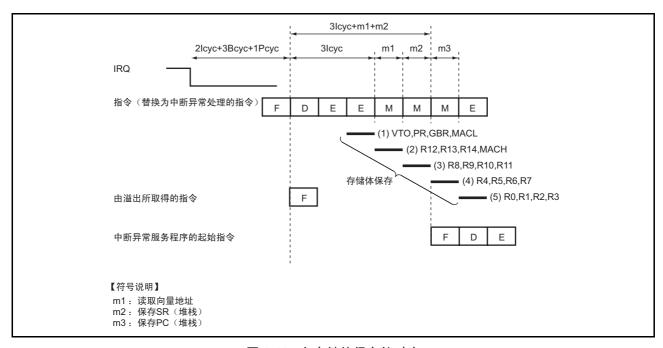

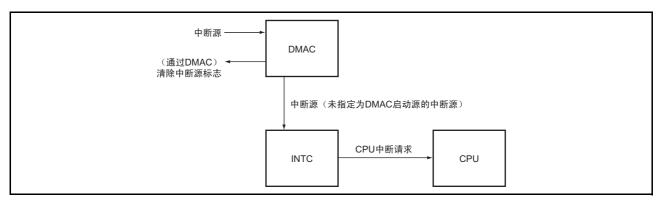

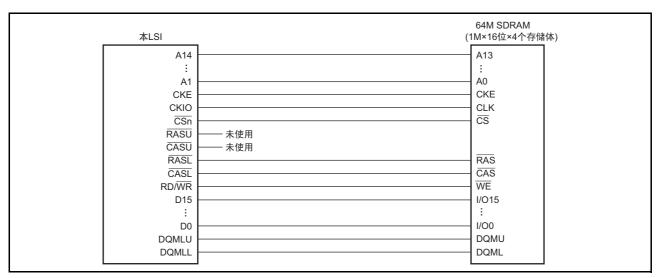

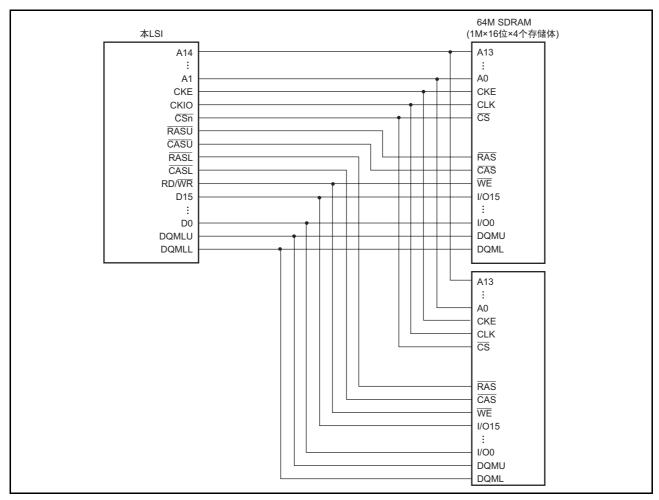

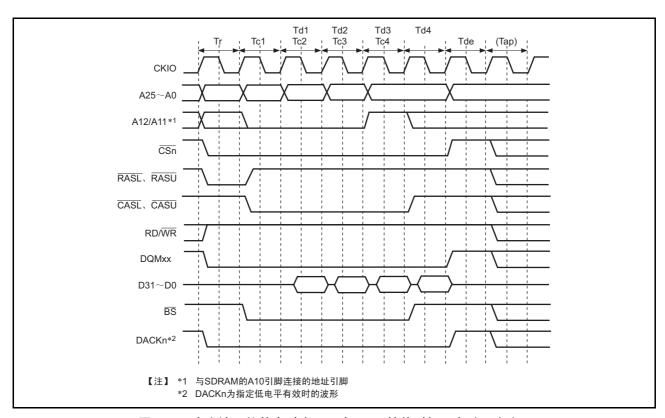

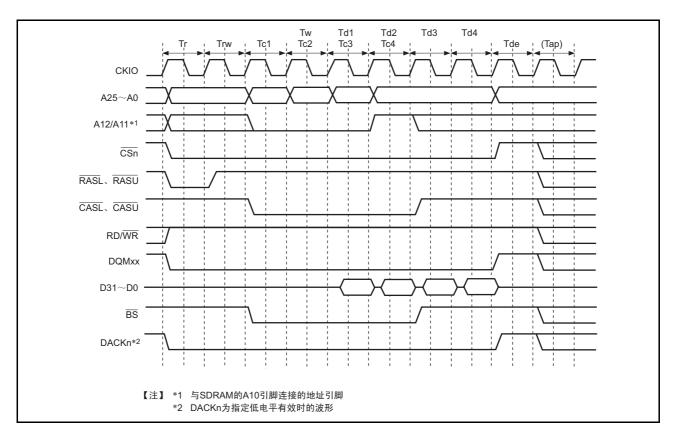

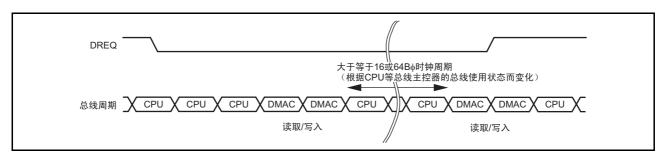

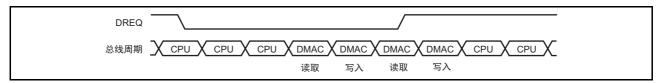

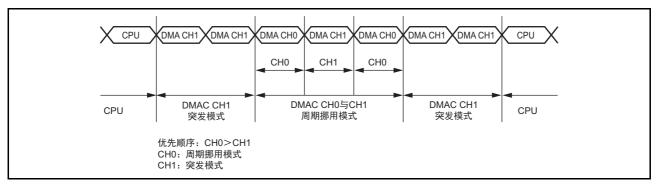

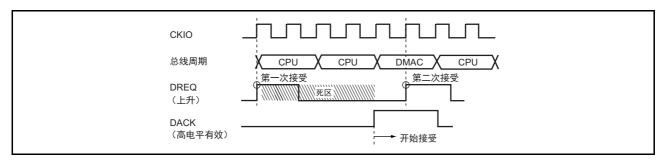

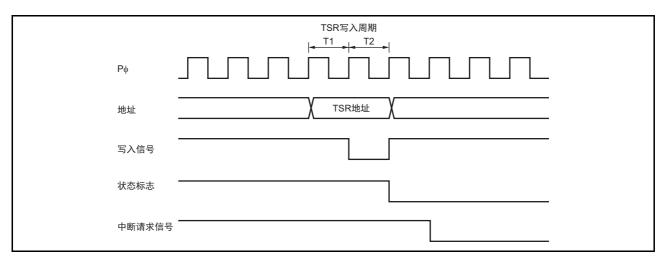

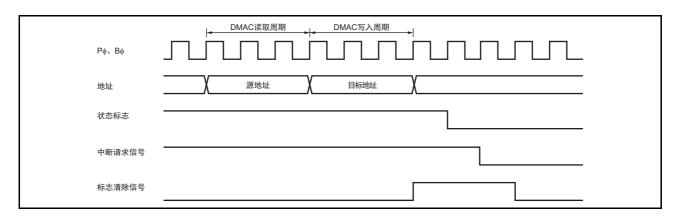

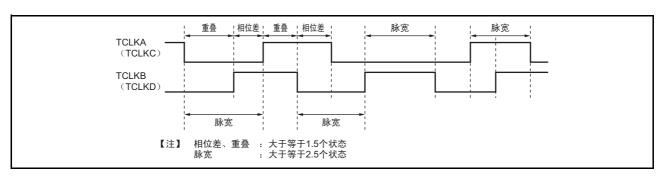

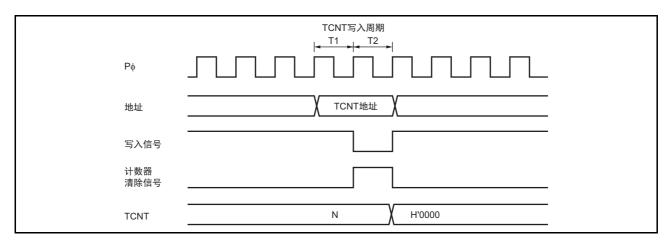

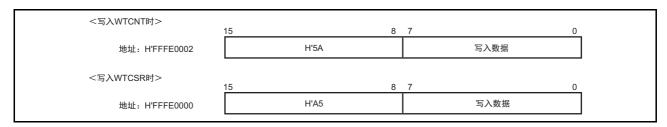

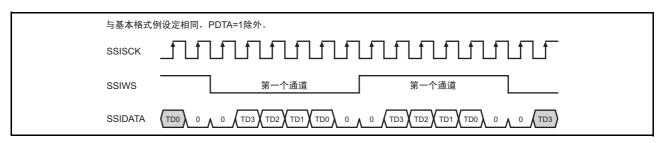

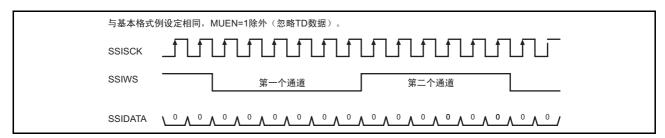

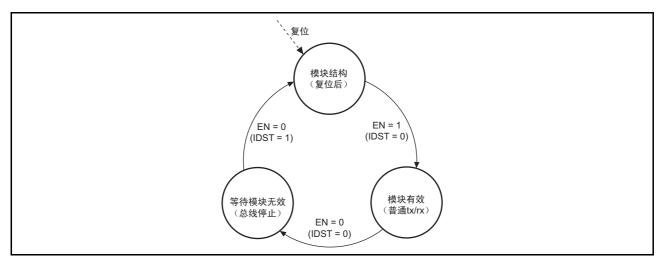

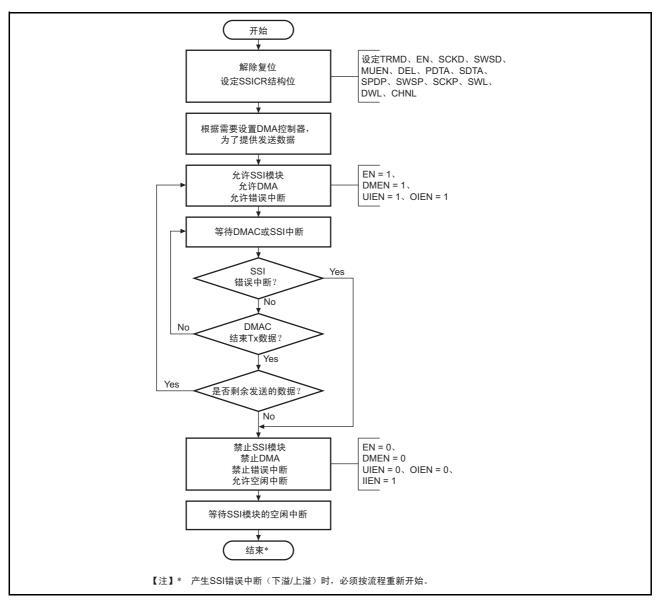

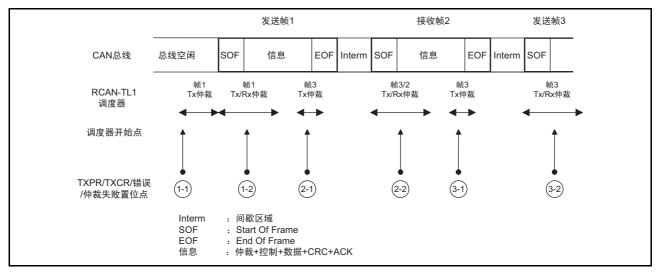

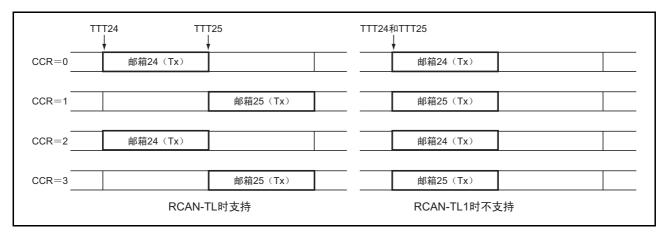

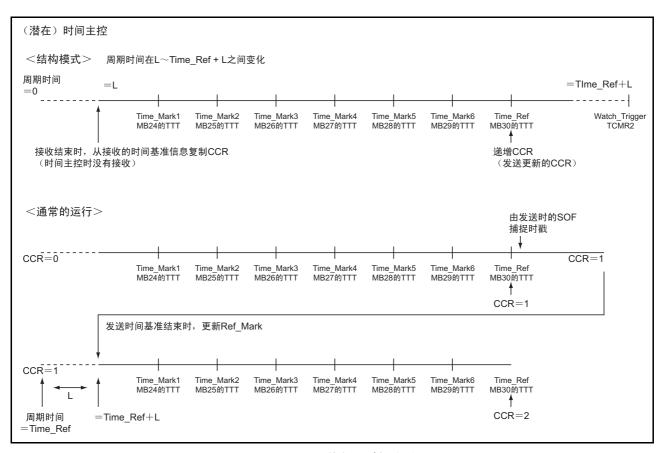

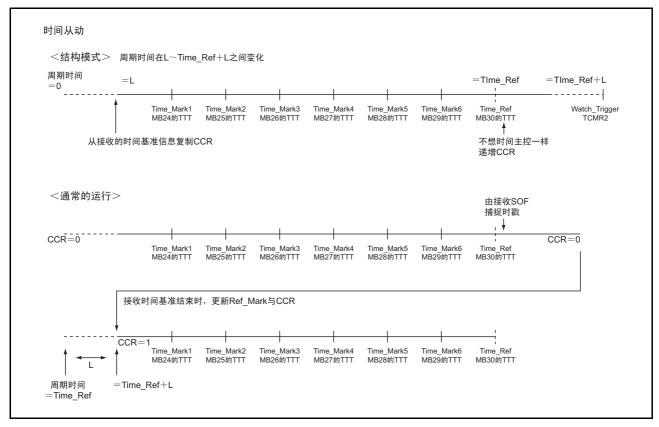

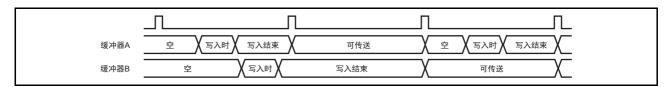

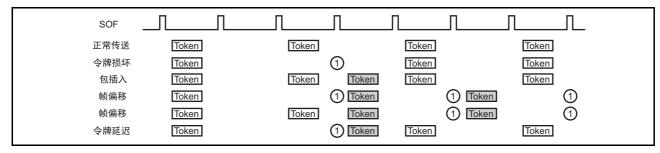

| 中断控制器 (INTC)         | <ul> <li>17 个外部中断引脚(NMI、IRQ7 <math>\sim</math> IRQ0、PINT7 <math>\sim</math> PINT0)</li> <li>内部外围中断:对各模块设定优先顺序</li> <li>可设定 16 级优先顺序</li> <li>通过寄存器存储体,可在中断处理的同时高速保存 / 返回寄存器</li> </ul>                                                                                                                                                                                                                              |