#### ISL73007SEHEV3Z

The ISL73007SEHEV3Z evaluation board (shown in Figure 3) features the ISL73007SEH buck regulator. This IC is a small foot print radiation hardened POL designed for critical low power applications.

The ISL73007SEH is operational over 3V to 18V integrating both high-side and low-side power FETs and switches at a default 500kHz frequency. The switching frequency can also be programmed from 300kHz up to 1MHz using an external resistor. The ISL73007SEH uses constant-frequency peak current mode control architecture for fast loop transient response and can use either its internal compensation at the 500kHz default switching frequency or an external Type II compensation at other frequencies to stabilize the loop as determined by specific design and performance requirements. When integrating both P-channel and N-channel power devices and with the option of internal compensation, a minimum of external components are required, thereby reducing the BOM count and complexity of the design.

The ISL73007SEHEV3Z evaluation board and this accompanying manual provide a quick and easy method to evaluate the ISL73007SEH part, see the ISL73007SEH datasheet for information about the device operation, function, and performance.

#### **Features**

- Optimized for 12V to 5V conversion and set up for a minimum 8V input with internal 500kHz switching frequency, slope and compensation configuration

- 3A output current

#### **Specifications**

The ISL73007SEHEV3Z evaluation board is by default internally configured for immediate evaluation with a minimum of components and connections.

The electrical ratings of the ISL73007SEHEV3Z evaluation board are shown in Table 1.

**Table 1. Electrical Ratings**

| Parameter           | Rating          |

|---------------------|-----------------|

| PVIN Supply Voltage | 8V - 18V        |

| DC Output Voltage   | 5V              |

| Operating Frequency | 500kHz          |

| Output Current      | 3A              |

| Temperature         | -55°C to +125°C |

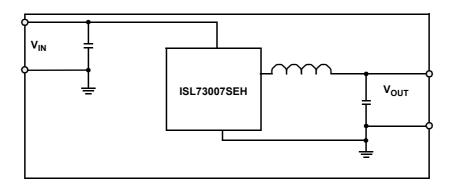

Figure 1. Block Diagram

### ISL73007SEHEV3Z Evaluation Board Manual

## **Contents**

| 1. | Fund | ctional Description         | 3 |

|----|------|-----------------------------|---|

|    |      | Operational Characteristics |   |

|    | 1.2  | Setup and Configuration     | 3 |

| 2. | Boar | rd Design                   | 4 |

|    | 2.1  | Basic Layout                | 5 |

|    | 2.2  | Layout Guidelines           | 5 |

|    |      | Schematic Diagram           |   |

|    | 2.4  | Bill of Materials           | 6 |

|    | 2.5  | Board Layout                | 6 |

| 3. | Турі | cal Performance Graphs      | 7 |

| 4. | Orde | ering Information           | 9 |

| 5. | Revi | sion History                | 9 |

## 1. Functional Description

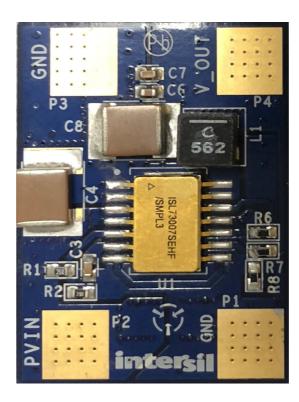

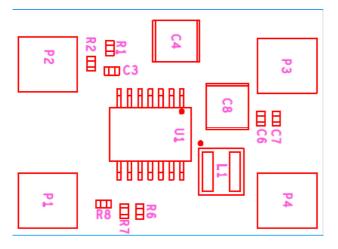

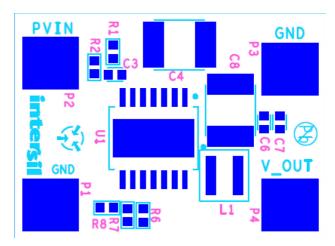

The ISL73007SEHEV3Z evaluation board has a default configuration of 8V -18V input to 5V output conversion with a 3A maximum output current and contains the ISL73007SEH voltage regulator IC in the internal configuration for the switching frequency, and for control loop and slope compensations. Figure 1 shows the ISL73007SEHEV3Z evaluation board block diagram. A photograph of the ISL73007SEHEV3Z is shown in Figure 3 and Figure 4.

The ISL73007SEHEV3Z evaluation board provides access to the pins of the IC device and convenient input and output points for connecting test equipment. For more information, see the Schematic Diagram, top layer silkscreen (Figure 11), and Bill of Materials. Performance data taken using the ISL73007SEHEV3Z and basic lab equipment is shown in Figure 12 through Figure 19.

### 1.1 Operational Characteristics

The ISL73007SEHEV3Z only requires a single voltage supply > 7.8V connected to the PVIN pad to operate, outputting 5V on the VOUT pad with a 3A output current capability. Configured for a nominal PVIN voltage of 12V, the input operating voltage at which the IC turns on is set by the resistor divider (R1 and R2) on the ENABLE pin. **Important:** Do not exceed 5V on the ENABLE pin.

### 1.2 Setup and Configuration

The following equipment is recommended for testing the board:

- Voltage power supply

- 100MHz oscilloscope

Complete the following steps to configure and use the board:

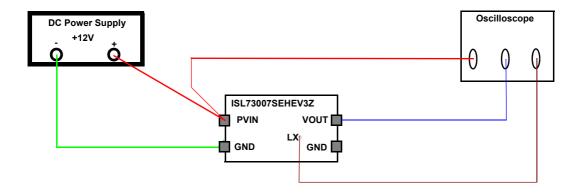

- 1. Configure the board as shown in Figure 2.

- 2. Connect and turn on an 8V to 16V power supply to the PVIN pad.

- Using the oscilloscope to look at VIN and VOUT waveforms and to also observe the behavior of the LX phase node located on pins 13 and 14 of the IC package. Proper probe grounding must be practiced when observing clean waveforms.

- 4. Output current loading can be externally added at the VOUT and GND pads for loaded output evaluations. A DVM(s) can be employed to monitor the input and output voltages and currents.

Figure 2. ISL73007SEH Basic Evaluation Test Setup Block Diagram

## 2. Board Design

Figure 3. ISL73007SEHEV3Z Evaluation Board (Top)

Figure 4. ISL73007SEHEV3Z Evaluation Board (Bottom)

## 2.1 Basic Layout

The ISL73007SEH is located in the upper center of the board and is labeled U1.

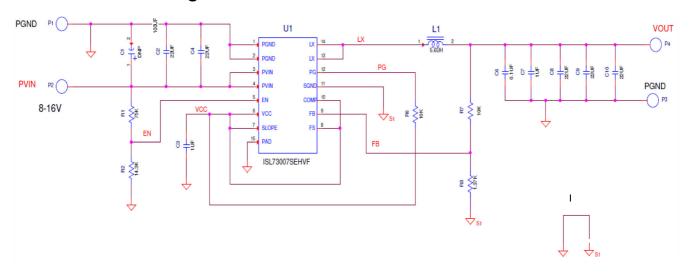

Connect the input power across the yellow Tantalum capacitor, the bulk input capacitance ( $C_{IN}$ ) at the PVIN and GND pads. The output voltage then appears on the V\_OUT and GND pads near the output inductor ( $L_{OUT}$ ) and the output capacitance ( $C_{OUT}$ ), respectively. Additional  $C_{IN}$  is provided by C2 (flip side) and C4. The other passive components near the PVIN pad are for setting the EN POR, slope compensation and VCC decoupling. The passive components between the GND and V\_OUT pads are for output voltage setting and PGOOD pull-up. Consult the schematic (Figure 5) for details.

### 2.2 Layout Guidelines

PCB design is critical to reduce parasitic inductances with critical components being closely placed to the IC. The critical components being the low ESR ceramic input capacitors for first placement. Avoid placing any traces or components under the LX shapes to avoid noise coupling from the switching node.

### 2.3 Schematic Diagram

Figure 5. ISL73007SEHEV3Z Schematic

## 2.4 Bill of Materials

| Qty | Reference<br>Designator | Description                                      | Manufacturer | Manufacturer Part  |

|-----|-------------------------|--------------------------------------------------|--------------|--------------------|

| 1   | U1                      | ISL73007SEH - 18V, 3A Rad Hard<br>Buck Regulator | Renesas      | ISL73007SEH/PROTO  |

| 5   | C2, C4, C8-C10          | 22μF, 2220 MLCC                                  | TDK          | C5750X7R1E226M     |

| 2   | C3, C7                  | 1μF, 0603 MLCC                                   | Various      | GCM188R71E105KA64D |

| 1   | C6                      | 0.1μF, 0603 MLCC                                 | Various      | Generic            |

| 2   | R6, R7                  | 10k, 0603 Metal Film Chip Resistor               | Various      | Generic            |

| 1   | R2                      | 14.3k, 0603 Metal Film Chip Resistor             | Various      | Generic            |

| 1   | R8                      | 1.371k, 0603 Metal Film Chip<br>Resistor         | Various      | Generic            |

| 1   | R1                      | 75k, 0603 Metal Film Chip Resistor               | Various      | Generic            |

| 1   | C1                      | 100μF, ESR 10mΩ POLYMER<br>CAPACITOR             | KEMET        | T541X107M020AH6510 |

| 1   | L1                      | 5.6μH, IND_XEL5050, Shielded<br>Power Inductor   | CoilCraft    | XEL5050-562ME      |

# 2.5 Board Layout

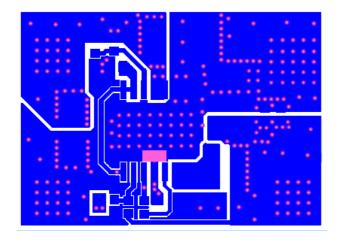

Figure 6. Top Layer

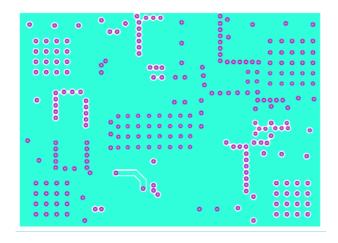

Figure 7. Layer 2

Figure 8. Layer 3

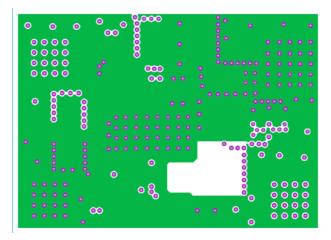

Figure 9. Bottom Layer

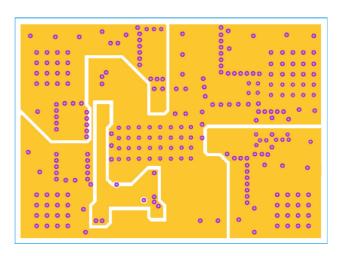

Figure 10. Top Assembly Layer

Figure 11. Top Silk Layer

# 3. Typical Performance Graphs

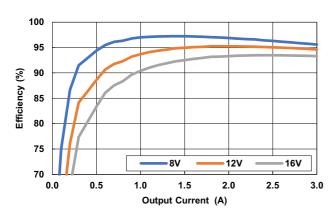

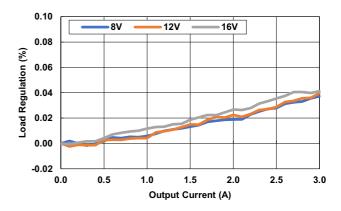

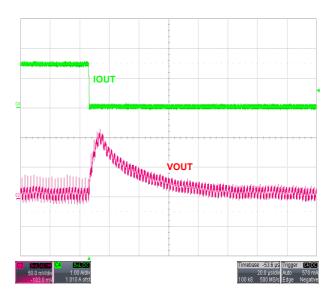

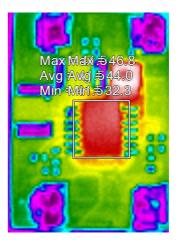

Unless otherwise noted, PVIN = 12V;  $V_{OUT}$  = 5V,  $f_{SW}$  = 500kHz,  $T_{A}$  = Room Ambient

Figure 12. Efficiency

Figure 13. Load Regulation

Unless otherwise noted, PVIN = 12V;  $V_{OUT}$  = 5V,  $f_{SW}$  = 500kHz,  $T_A$  = Room Ambient (Cont.)

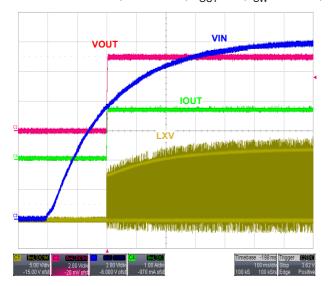

Figure 14. Turn-on, 3Ω load

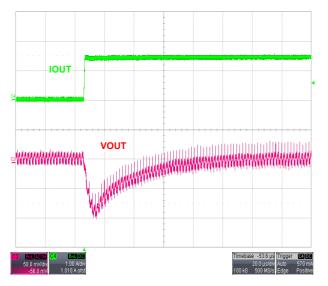

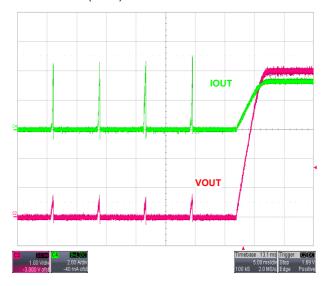

Figure 16. +1.5A Output Current Transient

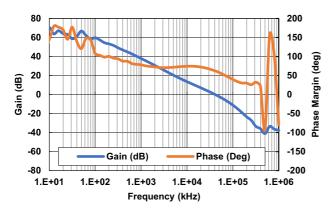

Figure 18. Gain/Phase Bode Plot, I<sub>OUT</sub> = 2.5A

Figure 15. Shorted Output into Restart after Hiccup

Figure 17. -1.5A Output Current Transient

Figure 19. Package Temperature at I<sub>OUT</sub> = 3A

# 4. Ordering Information

| Part Number     | Description                                                    |

|-----------------|----------------------------------------------------------------|

| ISL73007SEHEV3Z | Radiation Hardened ISL73007SEH buck regulator evaluation board |

# 5. Revision History

| Revision | Date         | Description     |

|----------|--------------|-----------------|

| 1.00     | Mar 23, 2022 | Initial release |

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit:

www.renesas.com/contact/