# 32-bit Single-Chip Microcontrollers

V850ES/Jx3-L

Power Supply Current

R01AN0473EJ0100 Rev.1.00 Mar. 28, 2011

## Introduction

This application note describes the functions that relate to lowering the power supply current of the V850ES/Jx3-L. Readers should use the information in this document to understand the features of this product's power supply current and the functions used to reduce it, and apply this knowledge to reduce the power supply current of their application system.

| Target Devices                                                                                                                                         | Contents                                                                                                                                                                                                                                                                                                                                                                                |                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| V850ES/JC3-L<br>• μPD70F3797<br>• μPD70F3798<br>• μPD70F3799                                                                                           | CHAPTER 1 OVERVIEW<br>1.1 Introduction<br>1.2 Power Supply Current Data                                                                                                                                                                                                                                                                                                                 | 3                   |

| <ul> <li>μPD70F3800</li> <li>μPD70F3801</li> <li>μPD70F3802</li> <li>μPD70F3803</li> <li>μPD70F3804</li> <li>μPD70F3838</li> <li>μPD70F3838</li> </ul> | <ul> <li>CHAPTER 2 FEATURES OF V850ES/Jx3-L POWER SUPPLY CURRENT</li> <li>2.1 Processing Performance and Power Consumption</li> <li>2.2 Operating Frequency and Power Supply Current</li> <li>2.3 Operating Ambient Temperature and Power Supply Current</li> <li>2.4 Power Supply Voltage and Power Supply Current</li> <li>CHAPTER 3 FUNCTIONS USED TO REDUCE POWER SUPPLY</li> </ul> | 4<br>5<br>6         |

| V850ES/JE3-L<br>• µPD70F3805<br>• µPD70F3806<br>• µPD70F3807<br>• µPD70F3808<br>• µPD70F3840                                                           | CHAPTER 3       FUNCTIONS USED TO REDUCE POWER SUPPLY         CURRENT                                                                                                                                                                                                                                                                                                                   | 8<br>10<br>12<br>15 |

| V850ES/JF3-L<br>• μPD70F3735<br>• μPD70F3736                                                                                                           | <ul> <li>3.2 Standby Function</li></ul>                                                                                                                                                                                                                                                                                                                                                 | 18<br>18<br>20      |

| V850ES/JG3-L<br>• µPD70F3737<br>• µPD70F3738<br>• µPD70F3792<br>• µPD70F3793<br>• µPD70F3841<br>• µPD70F3842                                           | <ul> <li>APPENDIX A Power Supply Current Characteristics</li></ul>                                                                                                                                                                                                                                                                                                                      | 23<br>23<br>27      |

# INTRODUCTION

| Target readers               | This Application Note is intended for users who understand the functions of the V850ES/Jx3-L and who will use this product to design application systems.                                                                                                                                                                                            |  |  |  |  |  |  |  |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Purpose                      | The purpose of this application note is to help users understand how to reduce the power supply current of the V850ES/Jx3-L.                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| Organization                 | <ul> <li>This document consists of the following main sections.</li> <li>Overview</li> <li>Features of V850ES/Jx3-L power supply current</li> <li>Functions used to reduce power supply current</li> </ul>                                                                                                                                           |  |  |  |  |  |  |  |

| How to read<br>this document | It is assumed that the reader of this document has general knowledge in the fields of electrical engineering, logic circuits, and microcontrollers.                                                                                                                                                                                                  |  |  |  |  |  |  |  |

|                              | To obtain an overview of the functions of the V850ES/Jx3-L: $\rightarrow$ Read this manual in the order of the Contents.                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

|                              | To understand the features of the power supply current in the V850ES/Jx3-L:<br>$\rightarrow$ See CHAPTER 2 FEATURES OF V850ES/Jx3-L POWER SUPPLY CURRENT.                                                                                                                                                                                            |  |  |  |  |  |  |  |

|                              | To understand the functions used to reduce the power supply current:<br>$\rightarrow$ See CHAPTER 3 FUNCTIONS USED TO REDUCE POWER SUPPLY CURRENT.                                                                                                                                                                                                   |  |  |  |  |  |  |  |

|                              | To learn more about the V850ES/Jx3-L's hardware functions:<br>$\rightarrow$ See the hardware user's manual of each V850ES/Jx3-L product.                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| Conventions                  | Data significance:Higher digits on the left and lower digits on the rightActive low representation:xxx (overscore over pin or signal name)Note:Footnote for item marked with Note in the textCaution:Information requiring particular attentionRemark:Supplementary informationNumeral representation:Binaryxxxx or xxxxBDecimalxxxxHexadecimalxxxxH |  |  |  |  |  |  |  |

| Related<br>documents         | The related documents indicated in this publication may include preliminary versions.<br>However, preliminary versions are not marked as such.                                                                                                                                                                                                       |  |  |  |  |  |  |  |

#### Documents related to V850ES/Jx3-L

| Document Name                                     | Document Number |

|---------------------------------------------------|-----------------|

| V850ES Architecture Hardware User's Manual        | U15943EJ        |

| V850ES/JC3-L, V850ES/JE3-L Hardware User's Manual | R01UH0018EJ     |

| V850ES/JG3-L Hardware User's Manual               | R01UH0165EJ     |

| V850ES/JF3-L Hardware User's Manual               | R01UH0017EJ     |

# CHAPTER 1 OVERVIEW

# 1.1 Introduction

This application note describes the functions that relate to lowering the power supply current of the V850ES/Jx3-L. The features of the power supply current are explained in chapter 2, and the functions used to reduce the power supply current are described in chapter 3.

It is hoped that by understanding the features of the V850ES/Jx3-L's power supply current and the functions used to reduce it, the reader will be able to apply this knowledge to reduce the power supply current of their own application systems.

# 1.2 Power Supply Current Data

The graphs and values used to express the power supply current in this document are actual values measured using specific samples. These values are not guaranteed. Also, be aware that power supply current characteristics may differ due to product variations. For guaranteed power supply current values, see the electrical specifications section of the hardware user's manual of each V850ES/Jx3-L product.

#### Remark

| V850ES/JC3-L, V850ES/JE3-L Hardware User's Manual | R01UH0018EJ |

|---------------------------------------------------|-------------|

| V850ES/JF3-L Hardware User's Manual               | R01UH0017EJ |

| V850ES/JG3-L Hardware User's Manual               | R01UH0165EJ |

# CHAPTER 2 FEATURES OF V850ES/Jx3-L POWER SUPPLY CURRENT

This chapter explains the features of the power supply current in the V850ES/Jx3-L.

# 2.1 Processing Performance and Power Consumption

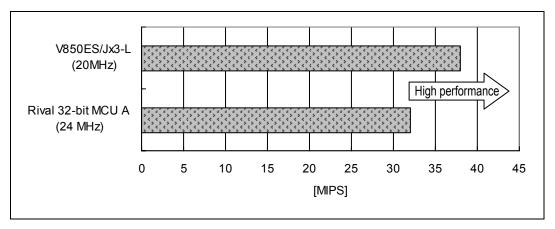

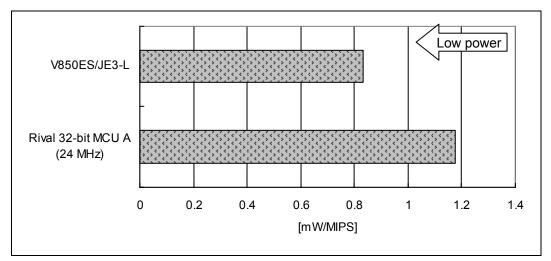

The V850ES/Jx3-L has the processing performance of a 32-bit microcontroller, but with the power efficiency of a 16-bit microcontroller. The V850ES/Jx3-L realizes a performance of 38MIPS at 20 MHz operation in the Dhrystone 2.1 benchmark program. This is about 1.4 times or more the level of rival 32-bit microcontrollers that operate with the same frequency (see *Figure 2-1*).

The V850ES/Jx3-L consumes less than about 70% of the power consumed by the rival 32-bit microcontrollers per MIPS (see *Figure 2-2*).

Figure 2-2. Power Consumption per MIPS [Dhrystone 2.1]

Remarks 1. Power supply voltage: 3.3 V

- 2. Power supply current: Value in the Dhrystone 2.1 program

- **3.** MIPS: Million instructions per second

- **4.** A 64-pin product with 256 KB flash memory was used for comparison.

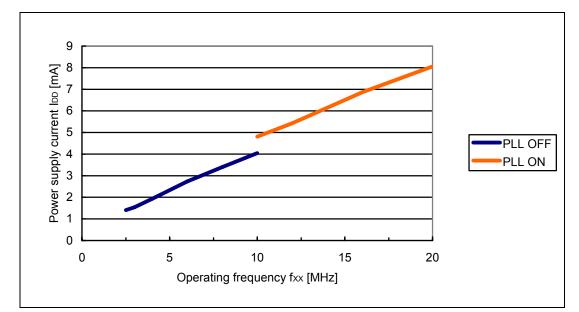

# 2.2 Operating Frequency and Power Supply Current

When comparing the power of microcontrollers, it is insufficient to simply compare operating frequency vs. current value. This is because the operating frequency used by the microcontroller is determined based on the processing execution time. For example, in the case of a certain microcontroller that must execute processing at 20 MHz in order to satisfy the allowable execution time, it may be possible to satisfy the allowable execution time with a microcontroller operating at 10 MHz if that microcontroller has double the processing performance of the original microcontroller.

The general rule in microcontrollers is that the power supply current increases in proportion to the operating frequency. Therefore, if the operating frequency can be lowered, and the same operations can be executed using a low frequency, the power consumption will also be reduced proportionately. For example, the V850ES/Jx3-L has a processing performance of 30MIPS (Dhrystone 2.1) even when operating at 16 MHz. This is the same performance as rival 32-bit microcontrollers operating at 24 MHz. The power supply current in this case is about 6.9 mA.

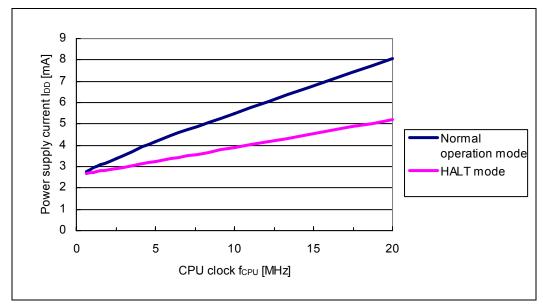

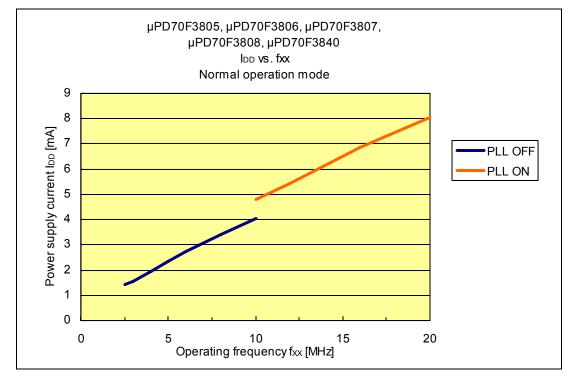

Figure 2-3 shows the relationship between the operating frequency and the power supply current of the V850ES/Jx3-L.

Figure 2-3. Relationship Between Operating Frequency and Power Supply Current

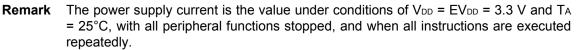

**Remark** The power supply current is the value under conditions of V<sub>DD</sub> = EV<sub>DD</sub> = 3.3 V and T<sub>A</sub> = 25°C, with all peripheral functions stopped, and when all instructions are executed repeatedly.

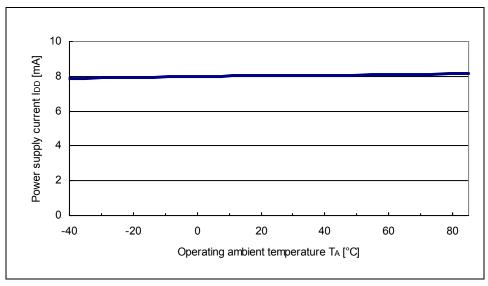

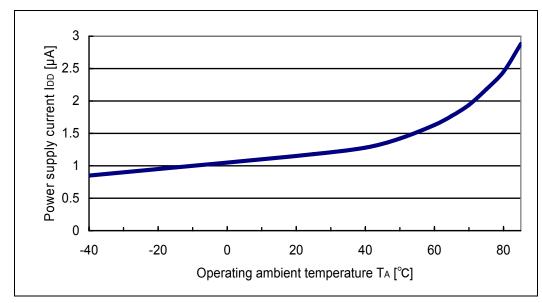

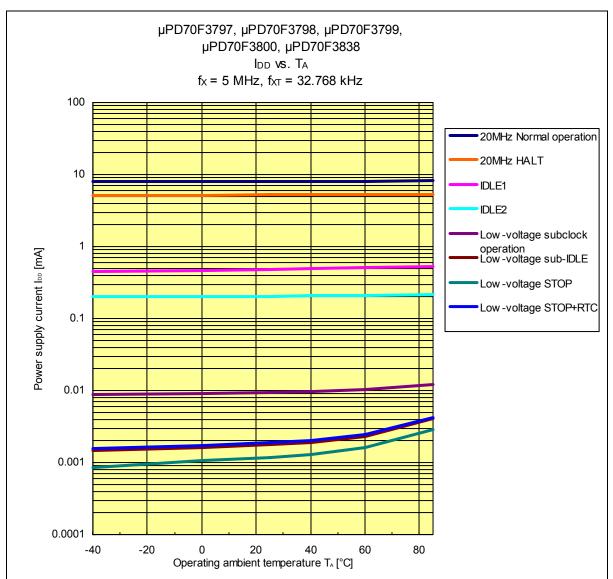

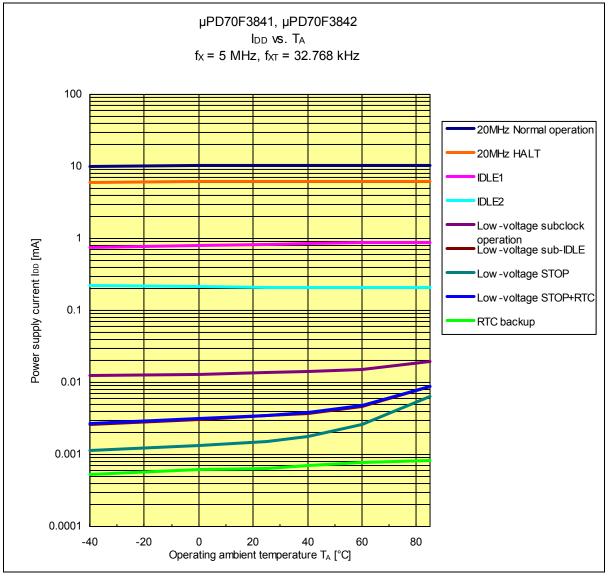

#### 2.3 Operating Ambient Temperature and Power Supply Current

The typical (TYP) power supply current value in the electrical specifications is the value when the operating ambient temperature (TA) is 25°C. The power supply current will change in accordance with the operating ambient temperature (TA). In modes such as STOP mode especially, the power supply current increases in greater proportion as the operating ambient temperature reaches the high-temperature zone. One effective way to reduce power supply current, therefore, is to restrict the temperature range in which the application system is used.

Figures 2-4 and 2-5 show the relationship between the operating ambient temperature and power supply current in normal operation mode and low-voltage STOP mode, respectively.

# Figure 2-4. Relationship Between Operating Ambient Temperature and Power Supply Current (V850ES/JE3-L in Normal Operation Mode)

**Remark** The power supply current is the value under conditions of V<sub>DD</sub> = EV<sub>DD</sub> = 3.3 V and T<sub>A</sub> = 25°C, with all peripheral functions stopped, and when all instructions are executed repeatedly.

# Figure 2-5. Relationship Between Operating Ambient Temperature and Power Supply Current (V850ES/JE3-L in Low-Voltage STOP Mode)

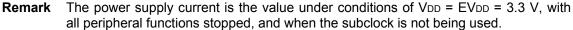

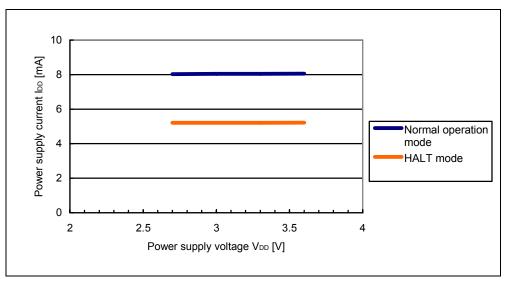

#### 2.4 Power Supply Voltage and Power Supply Current

The V850ES/Jx3-L has an on-chip regulator that operates the internal circuits on a constant voltage. This regulator supplies a stepped down voltage (about 2.5 V; stepped down from the VDD power supply voltage) to the oscillator block and internal logic circuits (except for the A/D converter, D/A converter, and output buffers).

Because the regulator is incorporated on the chip, its current consumption has almost no effect on the VDD power supply voltage.

Figures 2-6 and 2-7 show the relationship between the power supply voltage and power supply current at 20 MHz operation and in low-voltage mode, respectively.

#### Figure 2-6. Relationship Between Power Supply Voltage and Power Supply Current at 20 MHz Operation (V850ES/JE3-L)

**Remark** The power supply current is the value under conditions of T<sub>A</sub> = 25°C, with all peripheral functions stopped, and when all instructions are executed repeatedly in normal operation mode.

Figure 2-7. Relationship Between Power Supply Voltage and Power Supply Current in Low-Voltage Mode (V850ES/JE3-L)

**Remark** The power supply current is the value under conditions of T<sub>A</sub> = 25°C, with all peripheral functions stopped. In low-voltage STOP mode, this is the value when the subclock is not being used.

# CHAPTER 3 FUNCTIONS USED TO REDUCE POWER SUPPLY CURRENT

This chapter describes the functions used in the V850ES/Jx3-L to reduce power supply current.

# 3.1 Clock Control

The power supply current can be reduced by selecting the ideal clock and stopping unnecessary clocks and functions. The clock generator used in the V850ES/Jx3-L is shown below.

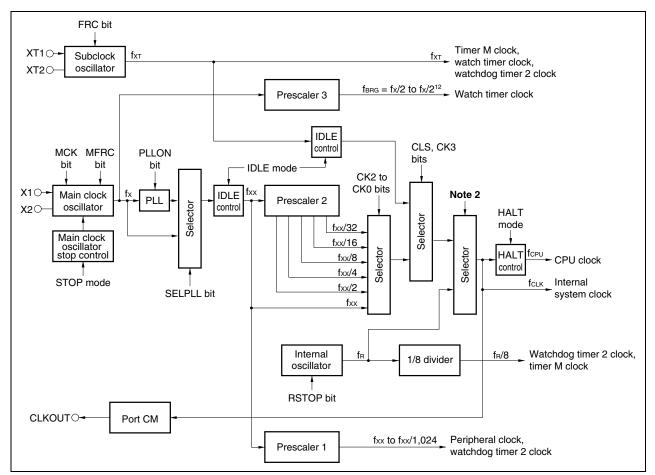

Figure 3-1. Clock Generator (1/2)<sup>Note 1</sup>

- **Notes 1.** This is the circuit used in the μPD70F3735, μPD70F3736, μPD70F3737, μPD70F3738, μPD70F3797, μPD70F3798, μPD70F3799, μPD70F3800, μPD70F3801, μPD70F3802, μPD70F3803, μPD70F3804, μPD70F3838, μPD70F3839, μPD70F3805, μPD70F3806, μPD70F3807, μPD70F3808, and μPD70F3840

- **2.** If watchdog timer 2 overflows during the oscillation stabilization period, the internal oscillation clock is selected.

- **Remark** fx: Main clock oscillation frequency

- fxx: Main clock frequency

- fclk: Internal system clock frequency

- fxT: Subclock frequency

- fcpu: CPU clock frequency

- fR: Internal oscillation clock frequency

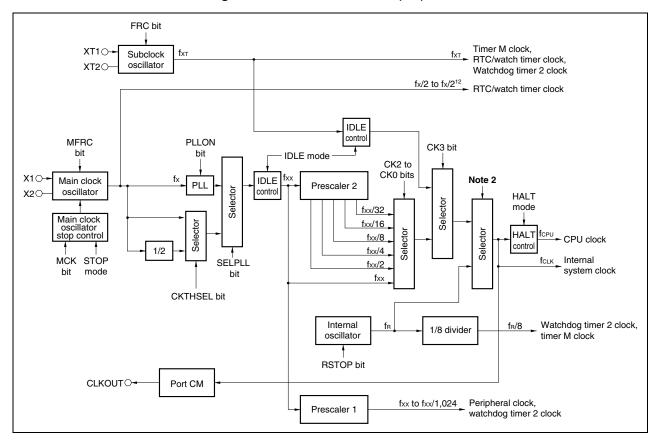

## Figure 3-1. Clock Generator (2/2)<sup>Note 1</sup>

- Notes 1. This is the circuit used in the μPD70F3792, μPD70F3793, μPD70F3841, and μPD70F3842.

2. If watchdog timer 2 overflows during the oscillation stabilization period, the internal oscillation clock is selected.

- **Remark** fx: Main clock oscillation frequency

- fxx: Main clock frequency

- fclk: Internal system clock frequency

- fxT: Subclock frequency

- fcpu: CPU clock frequency

- fR: Internal oscillation clock frequency

#### 3.1.1 CPU clock selection

A clock with a selectable divided main clock frequency (fxx) can be used as the CPU clock (fCPU) without changing the frequency of the on-chip peripheral function clock. Selecting a divided clock is effective in reducing the power supply current.

#### (1) Function details

A clock with a divided main clock frequency (fxx) can be used as the CPU clock (fCPU) and internal system clock (fCLK) by setting the CK3 to CK0 bits of the PCC register. The clock at this time has no effect on the peripheral clock supplied via prescaler 1, enabling the power supply current to be reduced without re-setting the on-chip peripheral functions.

This can be an effective way to reduce power supply current in cases such as the following:

- When a high-speed clock is required for the on-chip peripheral functions, but the CPU processing performance can be lowered.

- When a high CPU processing performance is required only for a specific period; otherwise low-speed processing is OK.

- As a substitute for HALT mode (when it is OK to take some time to recover from HALT)

Figure 3-2 shows the relationship between the frequency and power supply current when the CPU clock (fCPU) selection is changed by setting the CK3 to CK0 bits of the PCC register when fxx is 20 MHz.

**Remark** The power supply current is the value under conditions of V<sub>DD</sub> = EV<sub>DD</sub> = 3.3 V and T<sub>A</sub> = 25°C, with all peripheral functions stopped, and when all instructions are executed repeatedly in normal operation mode.

# (2) Processor clock control register (PCC)

This register is used to select the CPU clock ( $f_{CPU}$ ) and internal system clock ( $f_{CLK}$ ). The power supply current can be reduced by selecting a low-speed CPU clock.

For details about the PCC register, see the user's manual of the V850ES/Jx3-L product used.

0

0

1

1

0

0

1

0

The PCC register is a special register. Data can be written to this register only in a combination of specific sequences.

Reset sets this register to 03H.

|     | 7   | 6     | 5    | 4       | 3             | 2        | 1   | 0   |

|-----|-----|-------|------|---------|---------------|----------|-----|-----|

| PCC | FRC | MCK   | MFRC | CLS     | CK3           | CK2      | CK1 | CK0 |

|     |     |       |      |         |               |          |     |     |

|     | C   | 2 CK1 | CK0  | Clock S | election (fci | _κ/fcpu) |     |     |

0

1

0

1

0

1

Х

0

fxx

fxx/2

fxx/4 fxx/8

fxx/16 fxx/32

Subclock

(initial value)

Setting prohibited

Table 3-1.

PCC Register Format

**Remark** The CPU clock (fcPu) is used as the CPU operating clock.

0

0

0

0

1

1

1

0

0

0

0

0

0

0

0

1

The internal system clock ( $fcL\kappa$ ) is used as the operating clock of the interrupt controller, internal ROM, internal RAM, DMA function, and bus control function.

#### 3.1.2 PLL function

Two clock modes can be selected in the V850ES/Jx3-L: clock-through mode, in which the main clock oscillation frequency (fx) is used unchanged as the main clock frequency (fxx); and PLL mode, in which the PLL function is used to multiply the main clock oscillation frequency (fx) by 4. The power supply current can be reduced by stopping the PLL and operating the system in clock-through mode. The main clock oscillation frequency (fx) and main clock frequency (fxx) that can be used are as follows.

#### Table 3-2. Relationship Between Usable Main Clock Oscillation Frequency (fx) and Main Clock Frequency (fxx)

μPD70F3735, μPD70F3736, μPD70F3737, μPD70F3738, μPD70F3797, μPD70F3798, μPD70F3799, μPD70F3800, μPD70F3801, μPD70F3802, μPD70F3803, μPD70F3804, μPD70F3838, μPD70F3839, μPD70F3805, μPD70F3806, μPD70F3807, μPD70F3808, μPD70F3840

| Clock Mode         | Main Clock Oscillation Frequency (fx) | Main Clock Frequency (fxx) |

|--------------------|---------------------------------------|----------------------------|

| Clock-through mode | 2.5 to 10 MHz                         | 2.5 to 10 MHz              |

| PLL mode           | 2.5 to 5 MHz                          | 10 to 20 MHz               |

μPD70F3792, μPD70F3793, μPD70F3841, μPD70F3842

| Clock Mode         | Main Clock Oscillation Frequency (fx) | Main Clock Frequency (fxx) |

|--------------------|---------------------------------------|----------------------------|

| Clock-through mode | 2.5 to 10 MHz                         | 1.25 to 10 MHz             |

| PLL mode           | 2.5 to 5 MHz                          | 10 to 20 MHz               |

#### (1) Function details

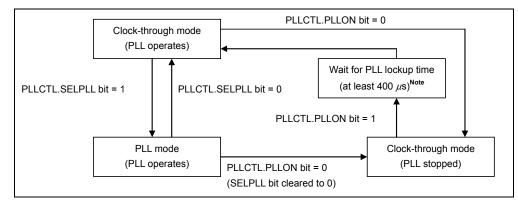

The PLLCTL register can be used to select whether the PLL operates or is stopped, and whether the clock mode is clock-through mode or PLL mode. A PLL lockup time (set by the PLLS register) is required when shifting from the PLL stopped state to the PLL operating state.

After reset is released, the PLL is in the operating state and the clock mode is clock-though mode. To operate the system in the PLL mode, therefore, the PLL mode must be set (PLLCTL.SELPLL bit = 1). When not using the PLL, the power supply current can be reduced by stopping the PLL (PLLCTL.PLLON bit = 0).

Operating in clock-through mode can be an effective way to reduce power supply current in cases such as the following:

- When the system, including the peripheral functions, can always operate at 10 MHz or lower.

- When a high CPU processing performance is required only for a specific period; otherwise low-speed processing is OK. Also, if the peripheral functions can be stopped/re-set when the clock mode switches between PLL mode and clock-through mode.

There are two ways to switch from PLL mode to clock-through mode: switching to clock-through mode (PLLCTL.SELPLL bit = 0) with the PLL operating (PLLCTL.PLLON bit = 1), and switching with it stopped (PLLCTL.PLLON = 0). Once the PLL is stopped, a PLL lockup time (400  $\mu$ s or longer) is required when shifting to the PLL operating state. However, by leaving the PLL stopped when it is not being used, the power supply current can be reduced by about 1 mA. Figure 3-3 shows a diagram of the status transitions between the clock-though mode and the PLL mode.

#### Figure 3-3. Diagram of Status Transitions Between Clock-Through Mode and PLL Mode

**Note** Set the PLLS register in accordance with the main clock oscillation frequency so that the PLL lockup time is 400  $\mu$ s or longer.

#### (2) PLL control register (PLLCTL)

This register is used to select the PLL operation and PLL mode. The power supply current can be reduced by stopping the PLL and operating in clock-through mode.

For details about the PLLCTL register, see the user's manual of the V850ES/Jx3-L product used.

Reset sets this register to 01H.

#### Table 3-3. PLLCTL Register Format

|        | 7 | 6 | 5 | 4 | 3 | 2 | 1      | 0     |

|--------|---|---|---|---|---|---|--------|-------|

| PLLCTL | 0 | 0 | 0 | 0 | 0 | 0 | SELPLL | PLLON |

| SELPLL | Operating clock selection          |

|--------|------------------------------------|

| 0      | Clock-through mode (initial value) |

| 1      | PLL mode                           |

| PLLON | PLL operation stop                       |

|-------|------------------------------------------|

| 0     | PLL stopped                              |

| 1     | PLL operating (PLL lockup time required) |

# (3) PLL lockup time specification register (PLLS)

This register is used to select the PLL lockup time required after the PLLCTL.PLLON bit is set to 1.

For details about the PLLS register, see the user's manual of the V850ES/Jx3-L product used.

Reset sets this register to 03H.

|      |   |       |       | –                   |                |             |   |       |       |

|------|---|-------|-------|---------------------|----------------|-------------|---|-------|-------|

|      | 7 |       | 6     | 5                   | 4              | 3           | 2 | 1     | 0     |

| PLLS | 0 |       | 0     | 0                   | 0              | 0           | 0 | PLLS1 | PLLS0 |

|      |   |       |       |                     |                |             |   |       |       |

|      |   | PLLS1 | PLLS0 | PL                  | L lockup ti    | me selectio | n |       |       |

|      |   | 0     | 0     | 2 <sup>10</sup> /fx |                |             |   |       |       |

|      | ĺ | 0     | 1     | 2 <sup>11</sup> /fx |                |             |   |       |       |

|      |   | 1     | 0     | 2 <sup>12</sup> /fx |                |             |   |       |       |

|      |   | 1     | 1     | 2 <sup>13</sup> /fx | (initial value | e)          |   |       |       |

Table 3-4. PLLS Register Format

**Remarks 1.** Set this register so that the lockup time is 400  $\mu$ s or longer.

2. Do not change the setting of the PLLS register during the lockup period.

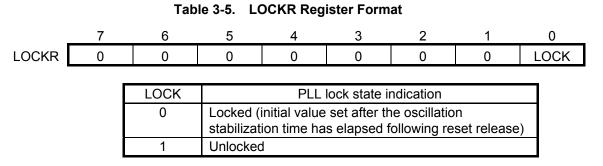

#### (4) Lock register (LOCKR)

This register indicates the stabilization state of the PLL frequency. When setting the system to PLL mode (PLLCTL.SELPLL bit = 1), the LOCKR.LOCK bit must first be cleared to 0.

For details about the LOCKR register, see the user's manual of the V850ES/Jx3-L product used.

Reset sets this register to 01H. After the oscillation stabilization time has elapsed following reset release, LOCKR is cleared to 00H.

Set conditions:

- Upon system reset (set to 01H by reset and cleared to 00H after oscillation stabilization time elapses following reset release)

- In IDLE2 or STOP mode

- Upon setting of PLL stop (clearing the PLLCTL.PLLON bit to 0)

- When the CPU operates on subclock and main clock is stopped (when the PCC.CK3 bit is set to 1 and then the PCC.MCK bit is set to 1)

Clear conditions:

- When the oscillation stabilization time (specified by the option byte) elapses following reset release

- When the oscillation stabilization time (specified by the OSTS register) elapses after exiting IDLE2 or STOP mode (or when IDLE2 or STOP mode is entered while the PLL is operating)

- After the PLL lockup time (specified by PLLS) elapses when the PLLCTL.PLLON bit is set to 1

#### 3.1.3 Internal oscillator

In the V850ES/Jx3-L, the clock of the internal oscillator can be selected as the clock for watchdog timer 2, timer M, and the clock monitor.

When not using these functions, or when not using the internal oscillator's clock for watchdog timer 2 and timer M, the power consumption can be reduced by stopping the internal oscillator.

#### (1) Function details

The internal oscillator starts operating after reset release. At this time, watchdog timer 2 starts operating on the internal oscillation clock (fR). When not using watchdog timer 2, stop both the internal oscillator and watchdog timer 2. Also, when operating watchdog timer 2 on another clock (main clock/subclock), stop the internal oscillator after switching the clock. By stopping the internal oscillator, the power supply current can be reduced by about 2 to 5  $\mu$ A.

The power supply current can be reduced by stopping the internal oscillator in cases such as the following:

- When not using watchdog timer 2 and the clock monitor

- When operating watchdog timer 2 on the main clock or subclock and at the same time not using the clock monitor

#### (2) Internal oscillation mode register (RCM)

This register is used to oscillate and stop the internal oscillator.

1

For details about the RCM register, see the user's manual of the V850ES/Jx3-L product used.

Reset sets this register to 00H.

|     | 7 | 6     | 5           | 4                             | 3             | 2          | 1 | 0     |  |  |

|-----|---|-------|-------------|-------------------------------|---------------|------------|---|-------|--|--|

| RCM | 0 | 0     | 0           | 0                             | 0             | 0          | 0 | RSTOP |  |  |

|     |   | RSTOP | 0.00        | illetien/eter                 | a of intornal | oocillator |   |       |  |  |

|     |   | RSIUP | USC         | mation/stop                   | p of internal | oscillator |   |       |  |  |

|     |   | 0     | Oscillate i | Oscillate internal oscillator |               |            |   |       |  |  |

#### Table 3-6. RCM Register Format

Stop internal oscillator

## 3.1.4 Function to supply/stop clock to peripheral functions

In the V850ES/Jx3-L, the peripheral functions can be operated and stopped by software. The power supply current can be reduced by stopping the operation of peripheral functions not being used.

#### (1) Function details

The following peripheral functions of the V850ES/Jx3-L can be operated and stopped by using software. After reset is released, the peripheral functions are in the stopped state.

- Timer P (TMP)

- Timer Q (TMQ)

- Timer M (TMM)

- Watch timer

- Real-time counter (RTC)<sup>Note 1</sup>

- Real-time output function (RTO)

- A/D converter (A/D)

- D/A converter (D/A)

- Asynchronous serial interface A (UARTA)

- Asynchronous serial interface C (UARTC)<sup>Note 2</sup>

- 3-wire variable length serial I/O (CSIB)

- $I^2C$  bus (I2C)

- DMA controller (DMA)

- Clock monitor (CLM)

- Low voltage detector (LVI)

- **Notes 1.** Provided in products other than the  $\mu$ PD70F3735,  $\mu$ PD70F3736,  $\mu$ PD70F3737, and  $\mu$ PD70F3738.

- **2.** Only provided in the μPD70F3792, μPD70F3793, μPD70F3841, and μPD70F3842.

#### (2) Registers enabling/stopping peripheral function operation

The operation of the peripheral functions can be enabled and stopped by using the following registers and bits.

| Peripheral<br>Function  | Operation<br>Enable/Stop<br>Control Register | Operation<br>Enable/Stop<br>Control Bit | Stop Setting |

|-------------------------|----------------------------------------------|-----------------------------------------|--------------|

| TMP                     | TPnCTL0                                      | TPnCE                                   | 0            |

| TMQ                     | TQ0CTL0                                      | TQ0CE                                   | 0            |

| ТММ                     | TM0CTL0                                      | TM0CE                                   | 0            |

| Watch timer             | WTM                                          | WTM0                                    | 0            |

| RTC <sup>Note 1</sup>   | RC1CC1                                       | RTCE                                    | 0            |

| RTO                     | RTPC0                                        | RTPOE0                                  | 0            |

| A/D                     | ADA0M0                                       | ADA0CE                                  | 0            |

| D/A                     | DA0M                                         | DA0CEn                                  | 0            |

| UARTA                   | UAnCTL0                                      | UAnPWR                                  | 0            |

| UARTC <sup>Note 2</sup> | UC0CTL0                                      | UC0PWR                                  | 0            |

| CSIB                    | CBnCTL0                                      | CBnPWR                                  | 0            |

| I <sup>2</sup> C        | IICCn                                        | IICEn                                   | 0            |

| DMA                     | DCHCn                                        | Enn                                     | 0            |

| CLM                     | CLM                                          | CLME                                    | 0            |

| LVI                     | LVIM                                         | LVION                                   | 0            |

Table 3-7.

Control Registers and Bits Corresponding to Peripheral Functions

**Notes 1.** Provided in products other than the  $\mu$ PD70F3735,  $\mu$ PD70F3736,  $\mu$ PD70F3737, and  $\mu$ PD70F3738.

**2.** Only provided in the μPD70F3792, μPD70F3793, μPD70F3841, and μPD70F3842.

# 3.2 Standby Function

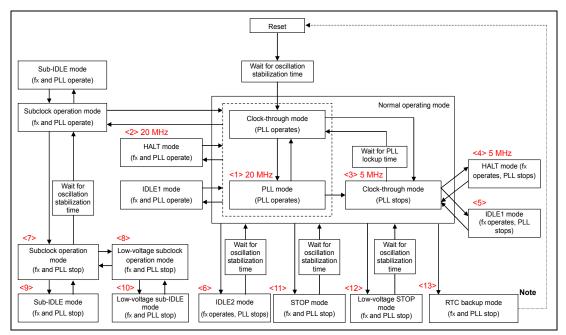

The V850ES/Jx3-L has three operating modes and seven standby modes<sup>Note</sup>. The power consumption can be effectively reduced by using the modes in combination and selecting the appropriate mode for the application.

**Note** The  $\mu$ PD70F3792,  $\mu$ PD70F3793,  $\mu$ PD70F3841, and  $\mu$ PD70F3842 have eight standby modes.

#### 3.2.1 Types of operating and standby modes

The types of operating and standby modes available are shown below.

| Mode                                | Function                                                                                                                                                                                                                                                      |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Normal operation mode               | Mode in which the CPU operates on the main clock.                                                                                                                                                                                                             |

| HALT mode                           | Mode in which only the CPU operating clock is stopped.                                                                                                                                                                                                        |

| IDLE1 mode                          | Mode in which the operations of all internal circuits except the oscillator, PLL <sup>Note 1</sup> and flash memory are stopped.                                                                                                                              |

| IDLE2 mode                          | Mode in which the operations of all internal circuits except the oscillator<br>are stopped. When returning to normal operation mode from IDLE2 mode,<br>regulator, flash memory and PLL setup time (specified by the OSTS<br>register) is required.           |

| Subclock operation mode             | Mode in which the subclock is used as the internal system clock. If the main clock is stopped, oscillation stabilization time set by the program must be secured when returning to normal operation mode.                                                     |

| Low-voltage subclock operation mode | Mode in which the subclock is used as the internal system clock, and the regulator voltage is lowered. The main clock is stopped.                                                                                                                             |

| Sub-IDLE mode                       | Mode in which the operations of all internal circuits except the oscillator, PLL <sup>Note 1</sup> and flash memory are stopped in subclock operation mode.                                                                                                   |

| Low-voltage sub-IDLE mode           | Mode in which the operations of all internal circuits except the flash memory are stopped in low-voltage subclock operation mode.                                                                                                                             |

| STOP mode                           | Mode in which the operations of all internal circuits except the subclock oscillator are stopped. When returning to normal operation mode, oscillation stabilization time (specified by the OSTS register) is required.                                       |

| Low-voltage STOP mode               | Mode in which the operations of all internal circuits except the subclock oscillator are stopped, and the regulator voltage is lowered. When returning to normal operation mode, oscillation stabilization time (specified by the OSTS register) is required. |

| RTC backup mode <sup>Note 2</sup>   | Mode in which all power supplies except for the RTC backup power<br>supply (RVDD) are stopped. This mode is entered from the pre-RTC<br>backup state.                                                                                                         |

Table 3-8.

V850ES/Jx3-L Operating Modes and Standby Modes

**Notes 1.** In IDLE1 mode and sub-IDLE mode, the PLL retains the state it was in immediately before the mode was shifted. If PLL operations are not required, the PLL should be stopped to save power. Note that shifting to IDLE2 mode automatically stops the PLL.

**2.** μPD70F3792, μPD70F3793, μPD70F3841, and μPD70F3842 only

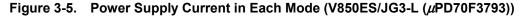

Figure 3-4 shows a mode status transition diagram and Figure 3-5 shows the power supply current in each mode.

Figure 3-4. Status Transition Diagram

**Note** μPD70F3792, μPD70F3793, μPD70F3841, and μPD70F3842 only

**Note** μPD70F3792, μPD70F3793, μPD70F3841, μPD70F3842 only

**Remark** See *Figure 3-4 Status Transition Diagram* for the definitions of modes <1> to <13> above.

## 3.3 A/D Converter

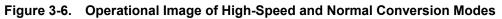

The A/D converter has two main conversion modes: normal conversion mode and high-speed conversion mode, and several sub-modes, such as continuous select mode and continuous scan mode. In these latter modes, A/D conversion continues repeatedly until the conversion operation is stopped by a software setting (ADA0M0.ADA0CE bit = 0). When executing A/D conversion continuously like this, setting the normal conversion mode enables a reduction in the average current.

#### (1) Function details

In normal conversion mode, once A/D conversion has been enabled (ADA0M0.ADA0CE bit = 1) and after the stabilization time has elapsed, A/D conversion starts and continues for the specified conversion time. After conversion is complete, the A/D converter stops operating and the A/D conversion end interrupt request signal (INTAD) is generated after the specified wait time has elapsed. Because conversion operations are stopped during the wait period, the average current can be reduced. Figure 3-6 shows an operational image of high-speed conversion mode.

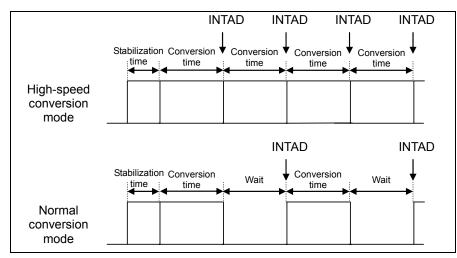

#### (2) A/D converter mode register 1 (ADA0M1)

This register is used to specify the conversion time.

For details about the ADA0M1 register, see the user's manual of the V850ES/Jx3-L product used.

Reset sets this register to 00H.

# 3.4 Watch Timer Function and Timer M

The watch timer generates an interrupt request signal (INTWT) at 0.25-second or 0.5-second intervals. By using the watch timer together with timer M (TMM), the frequency of time counting can be significantly reduced, lowering the power supply current. By using this combination, the  $\mu$ PD70F3735,  $\mu$ PD70F3736,  $\mu$ PD70F3737, and  $\mu$ PD70F3738, which do not incorporate an RTC, can reduce the frequency of time counting in the same way as products with an RTC.

#### (1) Function details

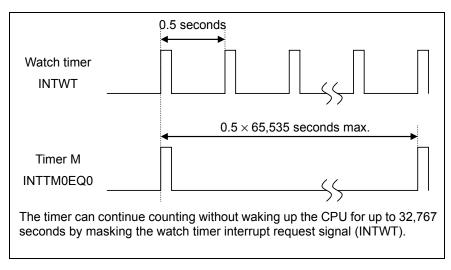

When using the watch timer, the time count must be processed by using an interrupt request signal (INTWT). However, by selecting INTWT as the count clock of timer M (TMM) and processing the time count using timer M's compare match interrupt request signal (INTTM0EQ0), the frequency of processing the time count can be significantly reduced, lowering the power supply current. This is especially effective when the mode is continually switched between sub-IDLE mode and subclock operation mode because only watch-based count operations are executed. Figure 3-7 shows the timing at which the watch timer interrupt request signal (INTTM0EQ0) are generated.

Figure 3-7. Timing of Watch Timer Interrupt and Timer M Interrupt

#### (2) TMM0 control register 0 (TM0CTL0)

This register is used to control the TMM0 operations and select the count clock.

For details about the TM0CTL0 register, see the user's manual of the V850ES/Jx3-L product used.

Reset sets this register to 00H.

|         | 7       | 6       | 5 4     | 3           | 2              | 1       | 0       |

|---------|---------|---------|---------|-------------|----------------|---------|---------|

| TM0CTL0 | TMOCE   | 0       | 0 0     | 0           | TM0CKS2        | TM0CKS1 | TM0CKS0 |

|         |         |         |         |             |                |         |         |

|         | TM0CKS2 | TM0CKS1 | TM0CKS0 | Coun        | t clock select | ion     |         |

|         | 0       | 0       | 0       | fxx (initia | l value)       |         |         |

|         | 0       | 0       | 1       | fxx/2       |                |         |         |

|         | 0       | 1       | 0       | fxx/4       |                |         |         |

|         | 0       | 1       | 1       | fxx/64      |                |         |         |

|         | 1       | 0       | 0       | fxx/512     |                |         |         |

|         | 1       | 0       | 1       | INTWT (     | Set value)     |         |         |

|         | 1       | 1       | 0       | fr/8        |                |         |         |

|         | 1       | 1       | 1       | fхт         |                |         |         |

| -       |         |         |         |             |                |         |         |

#### Table 3-10. TM0CTL0 Register Format

# **APPENDIX A** Power Supply Current Characteristics

Caution The data shown in this chapter indicates the results measured under the conditions specified for individual sample devices. These values are for reference only and do not constitute guaranteed values.

When designing your device, be sure to observe the ratings specified in the user's manual.

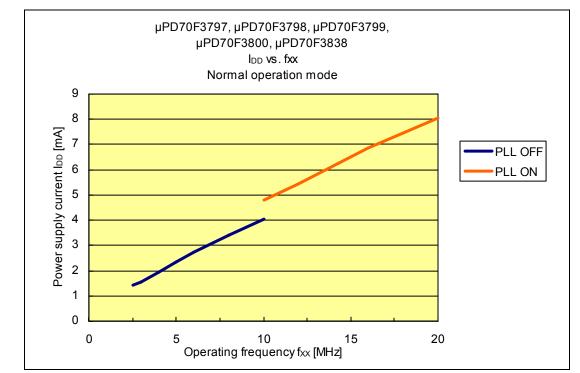

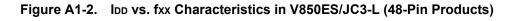

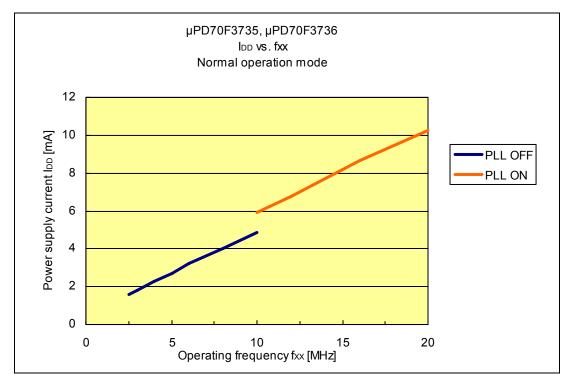

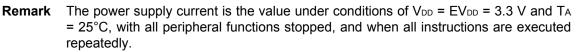

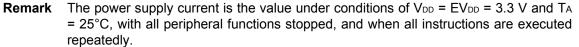

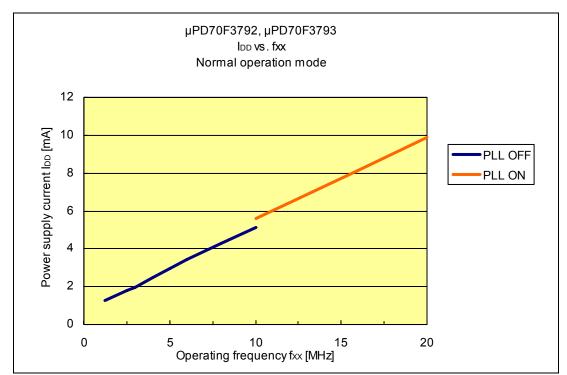

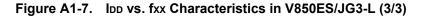

# A.1 Operating Frequency vs. Power Supply Current Characteristics (in Normal Operation Mode)

The following figures show how the power supply current changes according to the operating clock frequency variation.

Figure A1-1. IDD vs. fxx Characteristics in V850ES/JC3-L (40-Pin Products)

**Remark** The power supply current is the value under conditions of V<sub>DD</sub> = EV<sub>DD</sub> = 3.3 V and T<sub>A</sub> = 25°C, with all peripheral functions stopped, and when all instructions are executed repeatedly.

**Remark** The power supply current is the value under conditions of  $V_{DD} = EV_{DD} = 3.3$  V and T<sub>A</sub> = 25°C, with all peripheral functions stopped, and when all instructions are executed repeatedly.

**Remark** The power supply current is the value under conditions of  $V_{DD} = EV_{DD} = RV_{DD} = 3.3 V$ and  $T_A = 25^{\circ}C$ , with all peripheral functions stopped, and when all instructions are executed repeatedly.

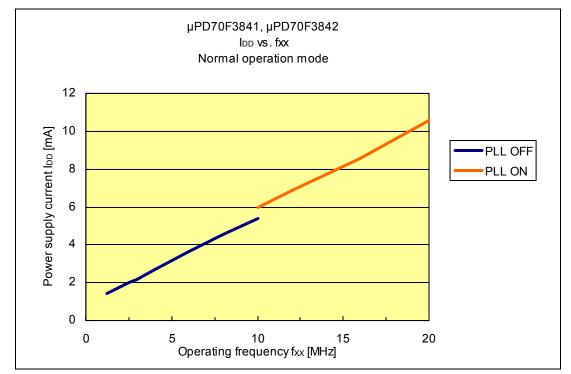

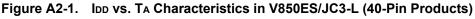

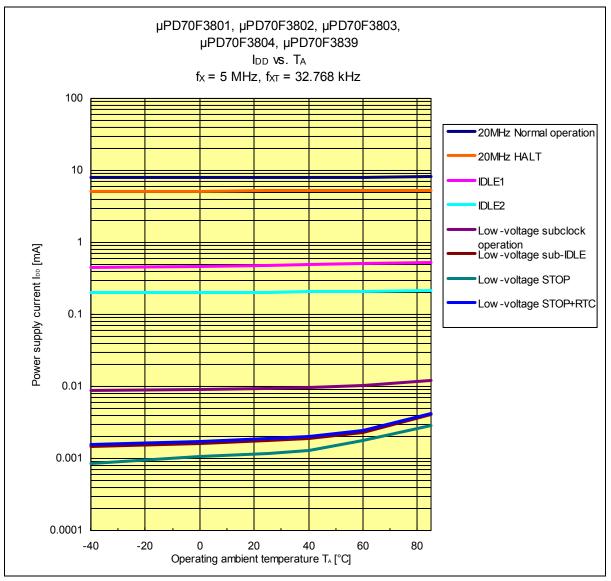

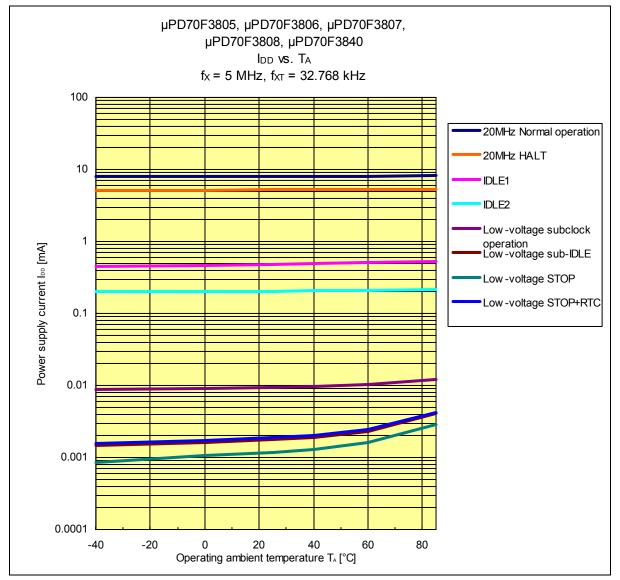

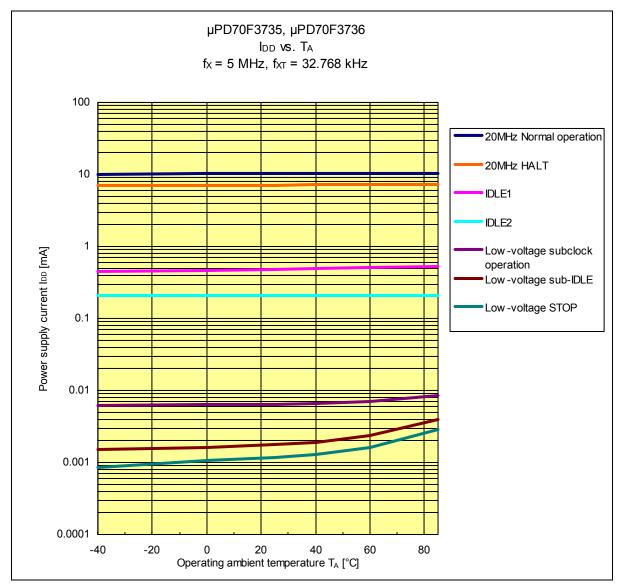

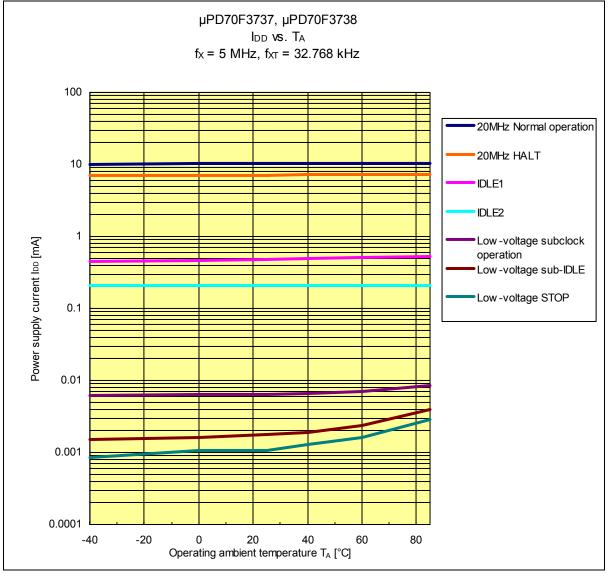

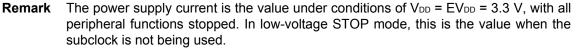

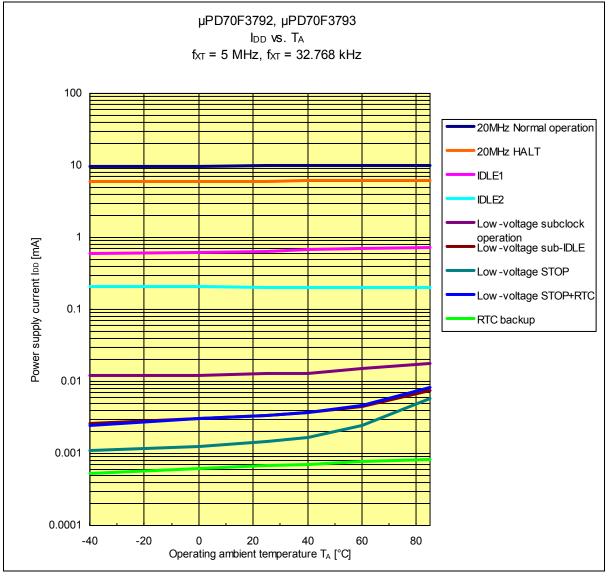

# A.2 Operating Ambient Temperature vs. Power Supply Current Characteristics

The following figures show how the power supply current changes according to the operating ambient temperature variation.

**Remark** The power supply current is the value under conditions of  $V_{DD} = EV_{DD} = 3.3$  V, with all peripheral functions stopped. In low-voltage STOP mode, this is the value when the subclock is not being used.

#### Figure A2-2. IDD vs. TA Characteristics in V850ES/JC3-L (48-Pin Products)

#### Figure A2-3. IDD vs. TA Characteristics in V850ES/JE3-L

Figure A2-5. IDD vs. TA Characteristics in V850ES/JG3-L (1/3)

Figure A2-6. IDD vs. TA Characteristics in V850ES/JG3-L (2/3)

Figure A2-7. IDD vs. TA Characteristics in V850ES/JG3-L (3/3)

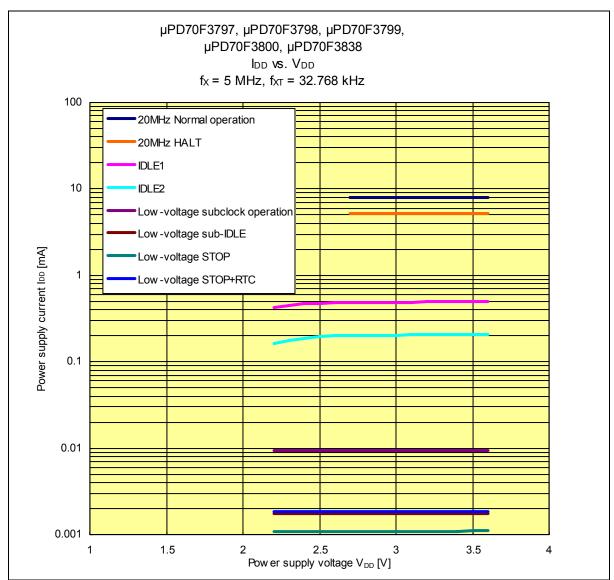

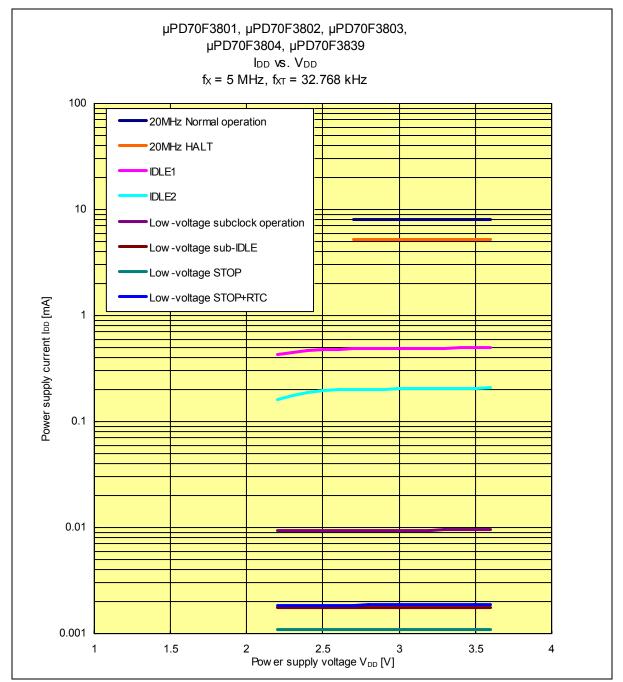

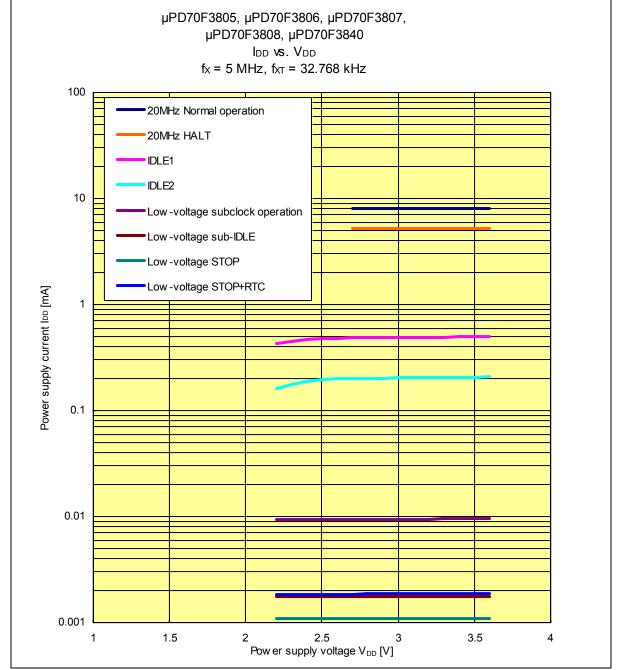

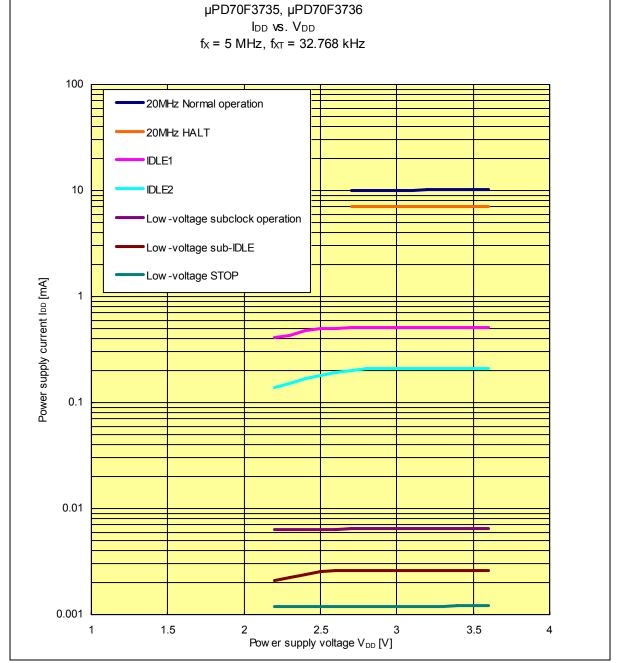

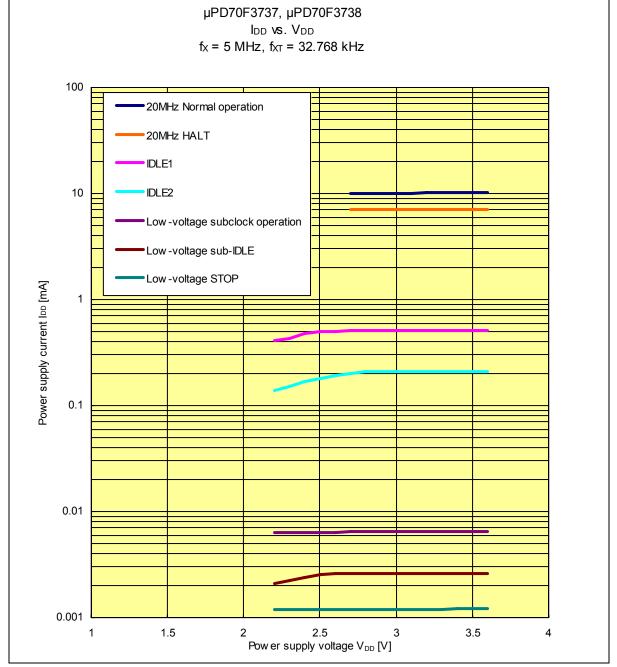

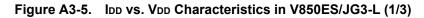

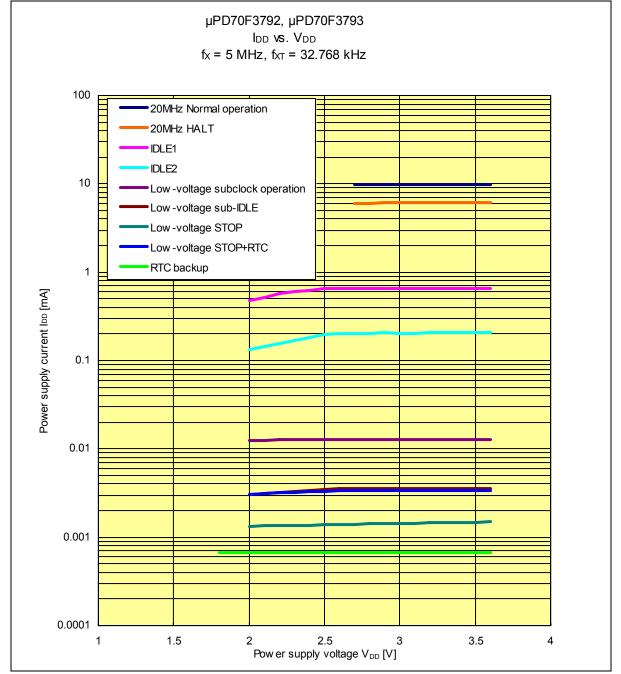

## A.3 Power Supply Voltage vs. Power Supply Current Characteristics

The following figures show how the power supply current changes according to the power supply voltage variation.

Figure A3-1. Ibd vs. Vbb Characteristics in V850ES/JC3-L (40-Pin Products)

Figure A3-2. IDD vs. VDD Characteristics in V850ES/JC3-L (48-Pin Products)

Figure A3-3. IDD vs. VDD Characteristics in V850ES/JE3-L

Figure A3-4. IDD vs. VDD Characteristics in V850ES/JF3-L

**Remark** The power supply current is the value under conditions of  $V_{DD} = EV_{DD}$  and  $T_A = 25^{\circ}C$ , with all peripheral functions stopped. In low-voltage STOP mode, this is the value when the subclock is not being used.

Figure A3-6. IDD vs. VDD Characteristics in V850ES/JG3-L (2/3)

**Remark** The power supply current is the value under conditions of V<sub>DD</sub> = EV<sub>DD</sub> = RV<sub>DD</sub> and T<sub>A</sub> = 25°C, with all peripheral functions stopped. In low-voltage STOP mode, this is the value when the subclock is not being used.

Figure A3-7. IDD vs. VDD Characteristics in V850ES/JG3-L (3/3)

**Remark** The power supply current is the value under conditions of V<sub>DD</sub> = EV<sub>DD</sub> = RV<sub>DD</sub> and T<sub>A</sub> = 25°C, with all peripheral functions stopped. In low-voltage STOP mode, this is the value when the subclock is not being used.

# Website and Support

- Renesas Electronics Website <u>http://www.renesas.com/</u>

- Inquiries <u>http://www.renesas.com/inquiry</u>

| V850ES/Jx3-L                        |               |      | Power Supply Current |        |  |

|-------------------------------------|---------------|------|----------------------|--------|--|

| 32-bit Single-Chip Microcontrollers |               |      |                      |        |  |

| Revis                               | sion Record   |      |                      |        |  |

|                                     |               |      | Descriptio           | on     |  |

| Rev.                                | Date          | Page | Su                   | ummary |  |

| 1.00                                | Mar. 28, 2011 | —    | First edition issued |        |  |

|                                     |               |      |                      |        |  |

|                                     |               |      |                      |        |  |

|                                     |               |      |                      |        |  |

|                                     |               |      |                      |        |  |

|                                     |               |      |                      |        |  |

|                                     |               |      |                      |        |  |

|                                     |               |      |                      |        |  |

All trademarks and registered trademarks are the property of their respective owners.

#### NOTES FOR CMOS DEVICES

- (1) VOLTAGE APPLICATION WAVEFORM AT INPUT PIN: Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between VIL (MAX) and VIH (MIN) due to noise, etc., the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between VIL (MAX) and VIH (MIN).

- (2) HANDLING OF UNUSED INPUT PINS: Unconnected CMOS device inputs can be cause of malfunction. If an input pin is unconnected, it is possible that an internal input level may be generated due to noise, etc., causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND via a resistor if there is a possibility that it will be an output pin. All handling related to unused pins must be judged separately for each device and according to related specifications governing the device.

- (3) PRECAUTION AGAINST ESD: A strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it when it has occurred. Environmental control must be adequate. When it is dry, a humidifier should be used. It is recommended to avoid using insulators that easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors should be grounded. The operator should be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with mounted semiconductor devices.

- (4) STATUS BEFORE INITIALIZATION: Power-on does not necessarily define the initial status of a MOS device. Immediately after the power source is turned ON, devices with reset functions have not yet been initialized. Hence, power-on does not guarantee output pin levels, I/O settings or contents of registers. A device is not initialized until the reset signal is received. A reset operation must be executed immediately after power-on for devices with reset functions.

- (5) POWER ON/OFF SEQUENCE: In the case of a device that uses different power supplies for the internal operation and external interface, as a rule, switch on the external power supply after switching on the internal power supply. When switching the power supply off, as a rule, switch off the external power supply and then the internal power supply. Use of the reverse power on/off sequences may result in the application of an overvoltage to the internal elements of the device, causing malfunction and degradation of internal elements due to the passage of an abnormal current. The correct power on/off sequence must be judged separately for each device and according to related specifications governing the device.

- (6) INPUT OF SIGNAL DURING POWER OFF STATE : Do not input signals or an I/O pull-up power supply while the device is not powered. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Input of signals during the power off state must be judged separately for each device and according to related specifications governing the device.

#### Notice

- All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application categorized as "Specific" written consent of Renesas Electronics should be for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The recommended where you have failed to obtain the prior written consent of Renesas Electronics and the prior written consent of Renesas Electronics as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product for any application application as exploration categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product for which there are supported as the specific as the specific and there are supported as the specific and the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product for any specific and there are present as the specific as the specific

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools

- personal electronic equipment; and industrial robots.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically

designed for life support.

- \*Specific\*: Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and mafunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and mafunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

Refer to "http://www.renesas.com/" for the latest and detailed information

#### SALES OFFICES

#### **Renesas Electronics Corporation**

http://www.renesas.com

Renesas Electronics America Inc. 2880 Scott Boulevard Santa Clara, CA 95050-2554, U.S.A. Tel: +1-408-588-4000, Fax: +1-408-588-6130 Renesas Electronics Canada Limited 1011 Nicholson Road, Newmarket, Ontario L3Y 9C3, Canada Tel: +1-905-898-5441, Fax: +1-905-898-3220 Renesas Electronics Europe Limited Dukes Meadow, Millboard Road, Boume End, Buckinghamshire, SL8 5FH, U.K Tel: +44-1628-585-100, Fax: +44-1628-585-900 Renesas Electronics Europe GmbH Arcadiastrasse 10, 40472 Düsseldorf, Germany Tel: +49-211-65030, Fax: +44-1628-585-900 Renesas Electronics Compe GmbH Arcadiastrasse 10, 40472 Düsseldorf, Germany Tel: +49-211-65030, Fax: +44-1628-585-900 Renesas Electronics (Shanghai) Co., Ltd. 7th Floor, Quantum Plaza, No.27 ZhiChunLu Haidian District, Beijing 100083, P.R.China Tel: +480-12453-1155, Fax: +480-21638-7659 Renesas Electronics (Shanghai) Co., Ltd. Unit 204, 205, A221 Center, No.1233 Lujiazul Ring Rd., Pudong District, Shanghai 200120, China Tel: +482-13477-1818, Fax: +480-21687-7858 Renesas Electronics Hong Kong Limited Unit 1001.161, 16/F., Tower 2, Grand Century Place, 193 Prince Edward Road West, Mongkok, Kowloon, Hong Kong Tel: +482-286-9318, Fax: +4852-2886-9022/9044 Renesas Electronics Taiwan Co., Ltd. 7F, No. 363 Fu Shing North Road Taipel, Taiwan Tel: +486-2-4175-9900, Fax: +4882-24175-9670 Renesas Electronics Taiwan Co., Ltd. 1 harbourFront Avenue, #06-10, keppel Bay Tower, Singapore 098632 Tel: +656-2175-9900, Fax: +4882-24075-9670 Renesas Electronics Kong Acnog Amorop Trade Centre, No. 18, Jin Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: +60-37755-9300, Fax: +405-2755-9510 Renesas Electronics Korea Co., Ltd. 11F, Samik Lavied or Bildy, 720-2 Veoksam-Dong, Kangnam-Ku, Seoul 135-080, Korea Tel: +60-57755-930, Fax: +40-2-7555-9510