# **RL78/F14 Application Note**

Porting guide from 78K0R/Fx3 to RL78/F14

### Abstract

This application note explains the differences between the functions of the RL78/F14 and the 78K0R/Fx3 (x = B, C, E, F, G) and provides examples when porting.

Under certain use conditions, the operations of the microcontroller might be different from the examples shown in this document. So please evaluate sufficiently the products or systems manufactured by you after porting and check the details of each function in the user's manuals.

### **Target Device**

| RL78/F14 (30 pins) :           | R5F10PAD,    | R5F10PAE     |              |              |

|--------------------------------|--------------|--------------|--------------|--------------|

| RL78/F14 (32 pins) :           | R5F10PBD,    | R5F10PBE     |              |              |

| RL78/F14 (48 pins) :           | R5F10PGD,    | R5F10PGE,    | R5F10PGF,    | R5F10PGG,    |

|                                | R5F10PGH,    | R5F10PGJ     |              |              |

| RL78/F14 (64 pins) :           | R5F10PLE,    | R5F10PLF,    | R5F10PLG,    | R5F10PLH,    |

|                                | R5F10PLJ     |              |              |              |

| RL78/F14 (80 pins) :           | R5F10PME,    | R5F10PMF,    | R5F10PMG,    | R5F10PMH,    |

|                                | R5F10PMJ     |              |              |              |

| RL78/F14 (100 pins) :          | R5F10PPE,    | R5F10PPF,    | R5F10PPG,    | R5F10PPH,    |

|                                | R5F10PPJ     |              |              |              |

| 78K0R/FB3 (30 pins, 32 pins) : | μ PD78F1804, | μ PD78F1805, | μ PD78F1806, | μ PD78F1807  |

| 78K0R/FC3 (40 pins) :          | μ PD78F1808, | μ PD78F1809, | μ PD78F1810, | μ PD78F1811  |

| 78K0R/FC3 (48 pins) :          | μ PD78F1812, | μ PD78F1813, | μ PD78F1814, | μ PD78F1815, |

|                                | μ PD78F1816, | μ PD78F1817, | μ PD78F1826, | μ PD78F1827, |

|                                | μ PD78F1828, | μ PD78F1829, | μ PD78F1830  |              |

| 78K0R/FE3 (64 pins) :          | μ PD78F1818, | μ PD78F1819, | μ PD78F1820, | μ PD78F1821, |

|                                | μ PD78F1822, | μ PD78F1831, | μ PD78F1832, | μ PD78F1833, |

|                                | μ PD78F1834, | μ PD78F1835  |              |              |

| 78K0R/FF3 (80 pins) :          | μ PD78F1823, | μ PD78F1824, | μ PD78F1825, | μ PD78F1836, |

|                                | μ PD78F1837, | μ PD78F1838, | μ PD78F1839, | μ PD78F1840  |

| 78K0R/FG3 (100 pins) :         | μ PD78F1841, | μ PD78F1842, | μ PD78F1843, | μ PD78F1844, |

|                                | μ PD78F1845  |              |              |              |

|                                |              |              |              |              |

R01AN2639EJ0200 Rev. 2.00 Oct. 31, 2017

#### Contents Comparison of functions (General).....4 1. 1.1 80-pin Products ......8 1.2 1.3 1.4 1.5 1.6 1.7 2. 3. 3.1 3.2.1 3.2.2 3.2.3 3.2.4 3.2.5 3.2.6 3.2.7 4. 4.1 4.2 5. 5.1 Power supply......46 6. 6.1 6.2 7. 7.1 7.2 7.3 8. Option byte ......54 9.

| 11.3 Connection of unused pins6                                                                                                            | 1 |

|--------------------------------------------------------------------------------------------------------------------------------------------|---|

| 12. Interrupts                                                                                                                             | 3 |

| 13. Watchdog timer                                                                                                                         | 5 |

| 14. DTC                                                                                                                                    | 7 |

| 15. Timer                                                                                                                                  | 3 |

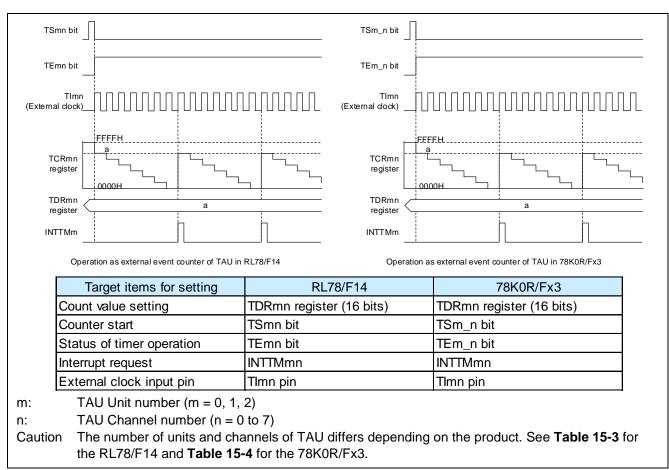

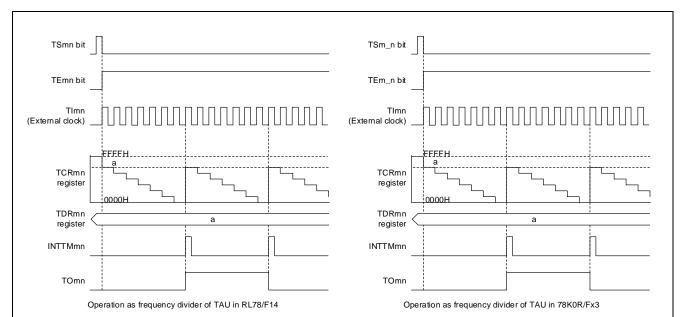

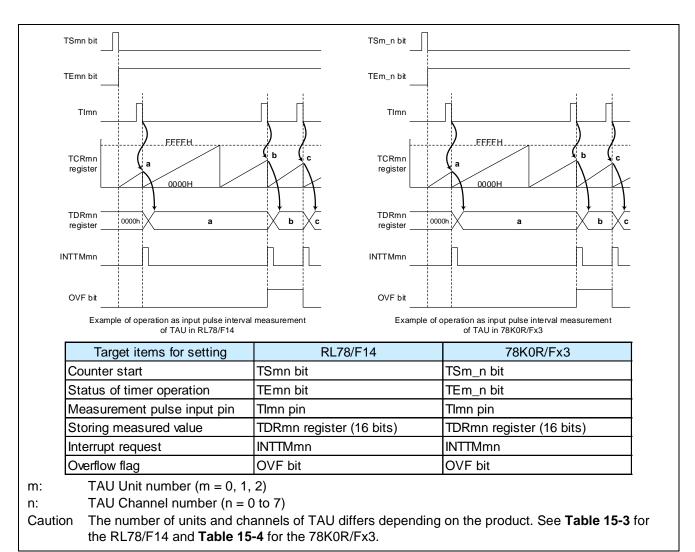

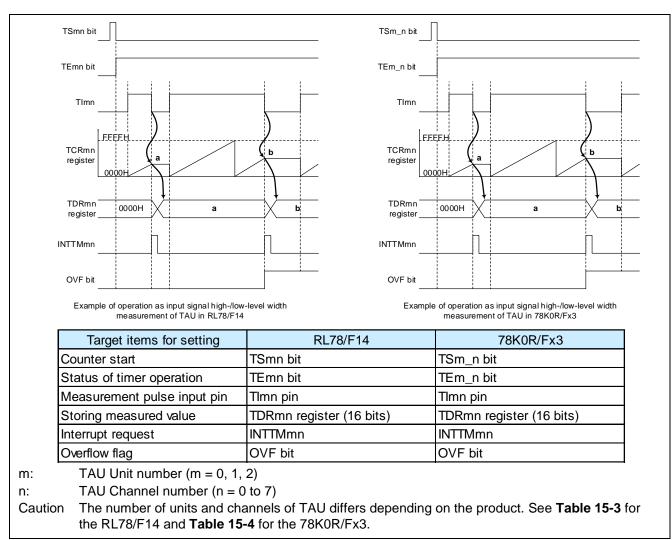

| 15.1 Porting code for TAU in 78K0R/Fx3 over to that in RL78/F14                                                                            |   |

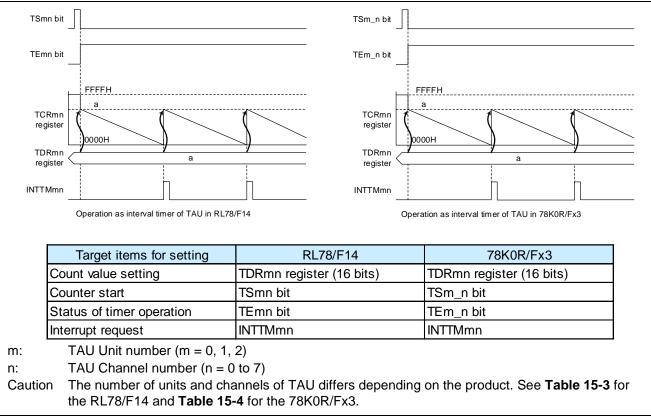

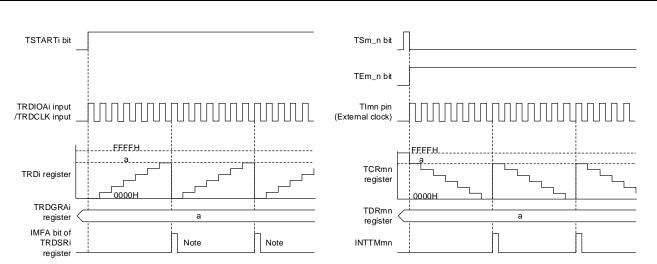

| 15.1.1 Porting code for interval timer of TAU79                                                                                            | 9 |

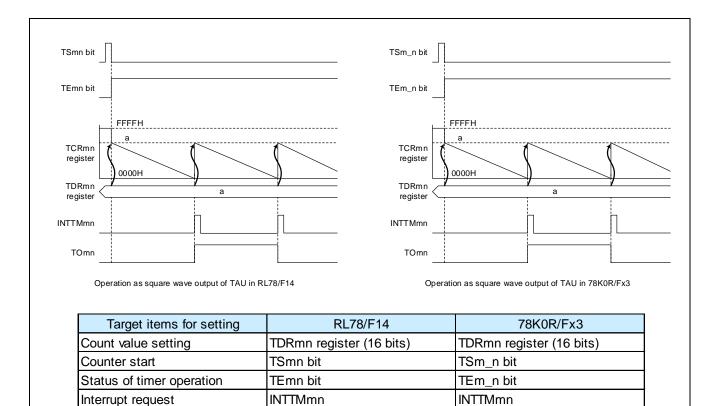

| 15.1.2 Porting code for square wave output function of TAU                                                                                 | D |

| 15.1.3 Porting code for external event counter of TAU8                                                                                     | 1 |

| 15.1.4 Porting code for divider function of TAU8                                                                                           | 2 |

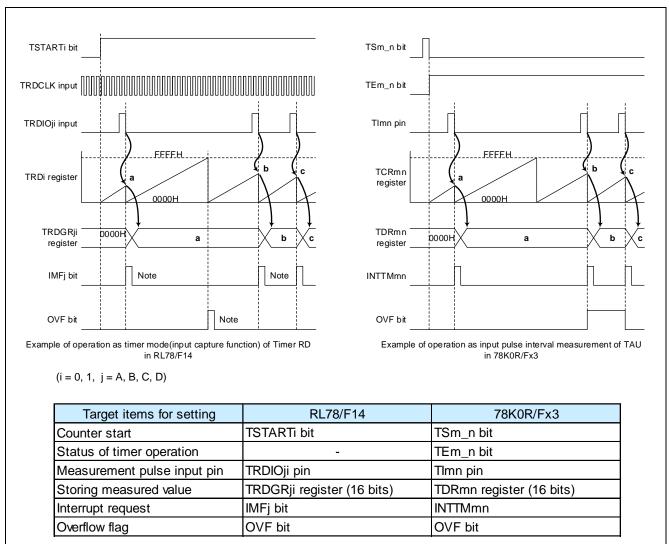

| 15.1.5 Porting code for input pulse interval measurement function of TAU8                                                                  | 3 |

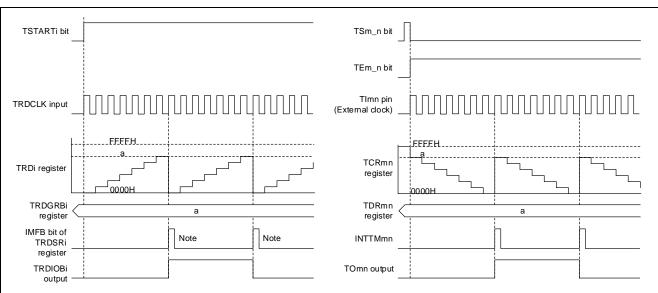

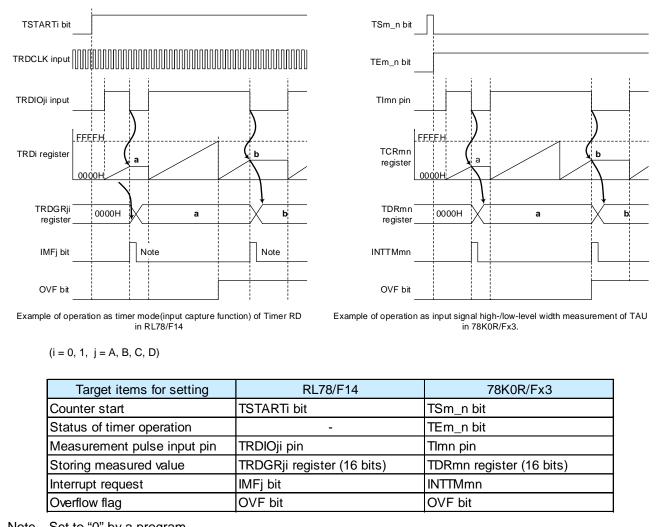

| 15.1.6 Porting code for input signal high-/low-level width measurement function84                                                          | 4 |

| 15.1.7 Porting code for one-shot pulse output function of TAU                                                                              |   |

| 15.1.8 Porting code for PWM function of TAU8                                                                                               |   |

| 15.1.9 Porting code for multiple PWM output function8                                                                                      |   |

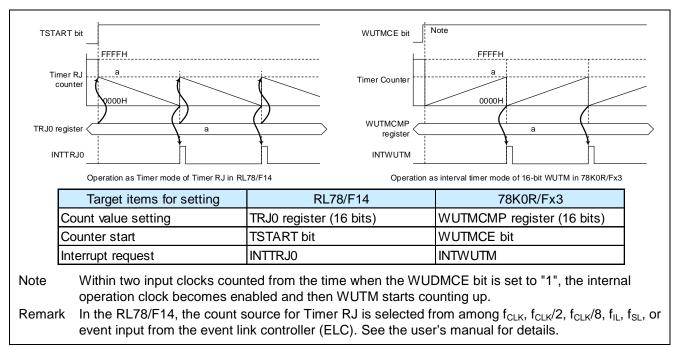

| 15.2 Porting code for functions of 16-bit wakeup timer over to that for Timer RJ8                                                          |   |

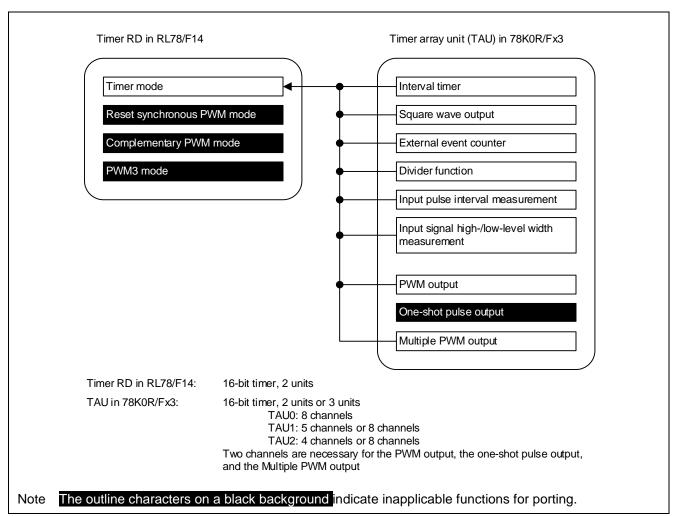

| 15.3 Porting code for TAU functions over to that for Timer RD functions                                                                    | 1 |

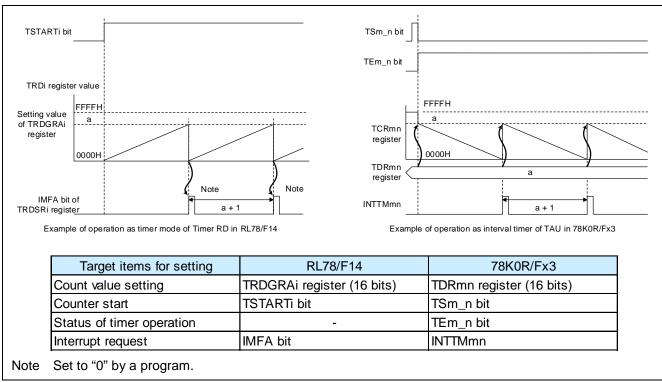

| 15.3.1 Porting code for TAU (interval timer) over to that for Timer RD (timer mode)                                                        | 5 |

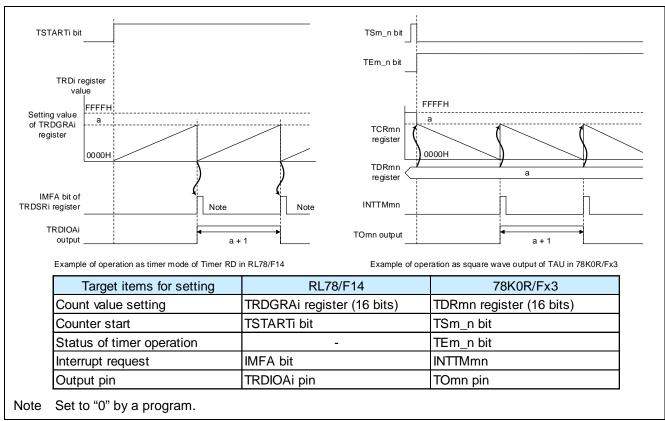

| 15.3.2 Porting code for TAU (square wave output function) over to that for Timer RD (timer mode)                                           | 6 |

| 15.3.3 Porting code for TAU (external event counter) over to that for Timer RD (input capture function)                                    |   |

| 15.3.4 Porting code for TAU (divider function) over to that for Timer RD (output compare function)                                         | 8 |

| 15.3.5 Porting code for TAU (input pulse interval measurement function) over to that for<br>Timer RD (input capture function)              | 9 |

| 15.3.6 Porting code for TAU (input signal high-/low-level width measurement function) over to that for Timer RD (input capture function)10 |   |

| 15.3.7 Porting code for TAU (PWM output) over to that for Timer RD (PWM function) 10                                                       | 1 |

| 15.3.8 Porting code for TAU (multiple PWM output) over to that for Timer RD (PWM function                                                  | ) |

| 16. Serial interface                                                                                                                       | 5 |

| 16.1 100-pin products                                                                                                                      |   |

| 16.2 80-pin products                                                                                                                       |   |

| 16.3 64-pin products                                                                                                                       |   |

| 16.4 48-pin products                                                                                                                       |   |

| 16.5 40-pin products                                                                                                                       |   |

| 16.6 32-pin products                                                                                                                       |   |

| 16.7 30-pin products                                                                                                                       |   |

| 17. A/D converter                                                                                                                          |   |

| 18. References                                                                                                                             |   |

| Website and Support <website and="" support,ws="">11</website>                                                                             |   |

### 1. Comparison of functions (General)

This application note explains the differences between the functions of the RL78/F14 and the 78K0R/Fx3 (x = B, C, E, F, G) and provides examples when porting.

Under certain use conditions, the operations of the microcontroller might be different from the examples shown in this document. So please evaluate sufficiently the products or systems manufactured by you after porting and check the details of each function in the user's manuals.

The overview of the comparison of functions between the RL78/F14 and the 78K0R/Fx3 is shown in Table 1-1, and the overview is broken down into Table 1-2 to Table 1-8 by the number of pins for each product.

#### Table 1-1 Major functions of RL78/F14 which are portable from 78K0R/Fx3 (1/2)

| Fur        | nctions (Note 1)                                 | RL78/F14                                                                                                                    |                                             | 78K0R/Fx3                                                                                                                                      |                                   | Page<br>(Note 2) |

|------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------|

| CPU        |                                                  | RL78 CPU core                                                                                                               |                                             | 78K0R CPU core                                                                                                                                 |                                   | 20               |

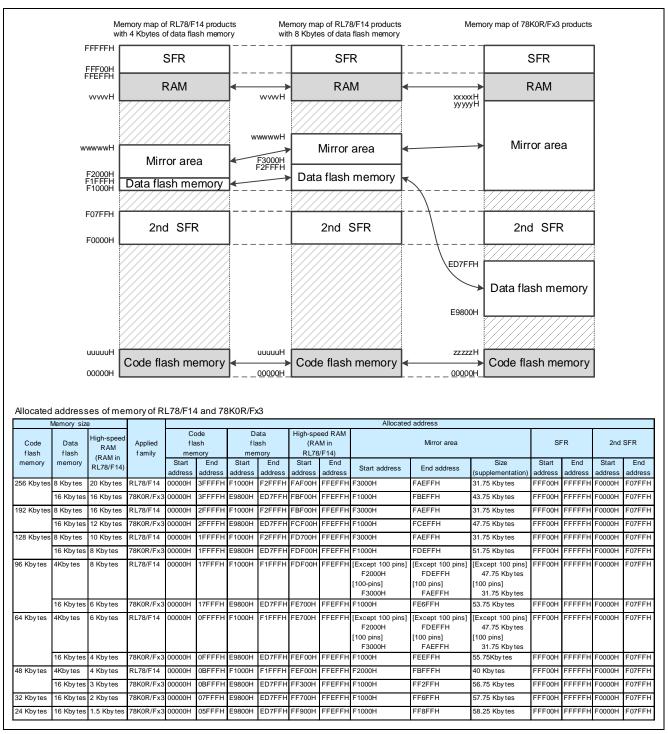

| Memory     | Code flash memory                                | 48, 64, 96, 128, 192, 256 Kbytes                                                                                            | 48, 64, 96, 128, 192, 256 Kbytes            |                                                                                                                                                | Kbytes                            | 39               |

|            | Data flash memory                                | 4, 8 Kbytes                                                                                                                 |                                             | 16 Kbytes                                                                                                                                      |                                   |                  |

|            | RAM                                              | 4, 6, 8, 10, 16, 20 Kbytes                                                                                                  |                                             | 1.5, 2, 3, 4, 6, 8, 12, 16 Kbytes                                                                                                              |                                   |                  |

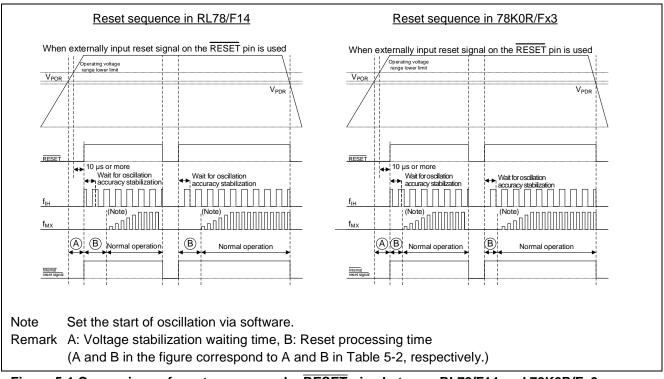

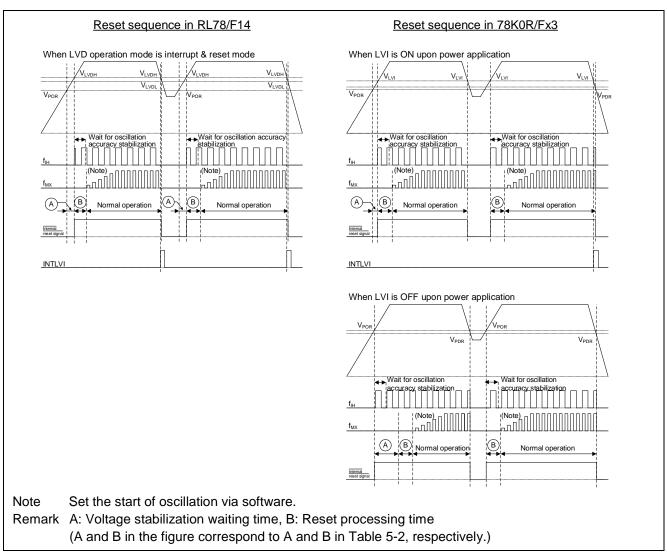

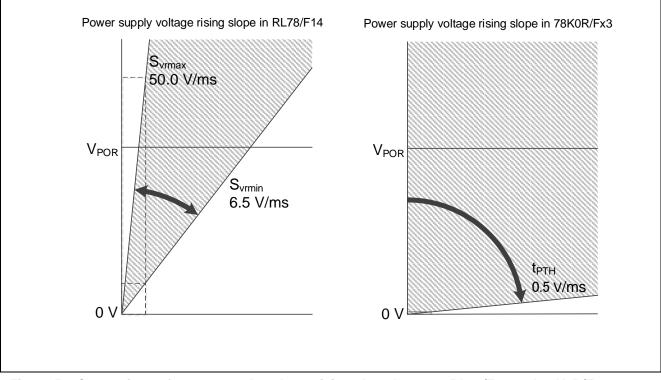

| Reset      | Number of reset sources                          | 7                                                                                                                           |                                             | 7                                                                                                                                              |                                   | 42               |

|            | Power-on-clear                                   | When power supply is rising:<br>When power supply is falling:                                                               | 1.56 V (TYP.)<br>1.55 V (TYP.)              | When power supply is rising:<br>When power supply is falling:                                                                                  | 1.61 V (TYP.)<br>1.59 V (TYP.)    |                  |

| Voltage de | tection function                                 | Voltage is detected:<br>·Interrupt & reset mode:<br>·Reset mode:<br>·Interrupt mode:                                        | 1 point<br>4 levels<br>6 levels<br>6 levels | Voltage is detected:<br>·Reset mode<br>·Interrupt mode                                                                                         | 1 point<br>10 levels<br>10 levels | 48               |

| Clock      | Main system clock                                | 1 MHz to 20 MHz                                                                                                             |                                             | 2 MHz to 20 MHz                                                                                                                                |                                   | 49               |

|            | Subsystem clock                                  | 32.768 kHz<br>(Provided for products with 48, 6-<br>pins)                                                                   | 4, 80, and 100                              | -                                                                                                                                              |                                   |                  |

|            | On-chip oscillator                               | Low-speed (f <sub>IL</sub> ): 15 kHz (TYP.)<br>High-speed (f <sub>IH</sub> ): 1, 4, 8, 12, 16, 24, 32, 48, 64 MHz<br>(TYP.) |                                             | Low-speed (f <sub>IL</sub> ): 30 kHz (TYP.)<br>High-speed (f <sub>IH</sub> ): 4, 8 MHz (TYP.)                                                  |                                   |                  |

|            | PLL                                              | PLL multiplication factor: x3, x4, x6, x8                                                                                   |                                             | PLL multiplication factor: ×1, ×6, ×8                                                                                                          |                                   |                  |

|            | WDT-dedicated<br>low-speed on-chip<br>oscillator | 15 kHz (TYP.)                                                                                                               |                                             | -                                                                                                                                              |                                   |                  |

|            | Clock monitor<br>function                        | Provided                                                                                                                    |                                             | Provided                                                                                                                                       |                                   |                  |

| I/O port   | ·                                                | I/O: 23, 25, 38, 52, 68, 86<br>(CMOS/N-ch I/O: 9, 13, 16 (N<br>Input-only: 3, 5 (Shared with osci<br>Output-only: 0, 1      |                                             | I/O: 19, 21, 27, 32, 46, 62, 80<br>(CMOS/N-ch I/O: 0, 1, 5 (Note<br>Input-only: 2, 4<br>Output-only: 0, 1<br>N-ch open-drain I/O (6 V toleranc | ,,                                | 57               |

| Interrupts | External                                         | 9, 13, 14, 15, 16 sources                                                                                                   |                                             | 8, 9, 10, 11, 12 sources                                                                                                                       |                                   | 63               |

| •          | Internal                                         | 40, 41, 48 sources                                                                                                          |                                             | 30, 31, 34, 36, 40, 41, 43, 47, 49                                                                                                             | sources                           | 1                |

|            | Key input                                        | 6, 8 channels                                                                                                               |                                             | 0, 4, 8 channels                                                                                                                               |                                   | 1                |

|            | Number of interrupt sources                      | 49, 50, 54, 55, 62, 63, 64 source                                                                                           | S                                           | 38, 39, 43, 46, 50, 51, 54, 55, 58,                                                                                                            | 59, 61 sources                    |                  |

| Watchdog   | timer                                            | Provided                                                                                                                    |                                             | Provided                                                                                                                                       |                                   | 65               |

Notes 1. This table does not show all the functions provided for the RL78/F14.

2. The details about porting each function are described on the pages shown.

- 3. N-ch open-drain output can be selected by writing "1" to the target bit of the port output mode register (POM1, POM6, POM7, POM12). For details, see **CHAPTER 3 PIN assignment** and the user's manual.

- 4. N-ch open-drain output can be selected by writing "1" to the target bit of the port output mode register (POM4, POM7). For details, see **CHAPTER 3 PIN assignment** and the user's manual.

### Table 1-1 Major functions of RL78/F14 which are portable from 78K0R/Fx3 (2/2)

| Fur        | nction (Note 1)     | RL                                                      | .78/F14                | 78                                                      | K0R/Fx3                                         | Page<br>(Note 2) |

|------------|---------------------|---------------------------------------------------------|------------------------|---------------------------------------------------------|-------------------------------------------------|------------------|

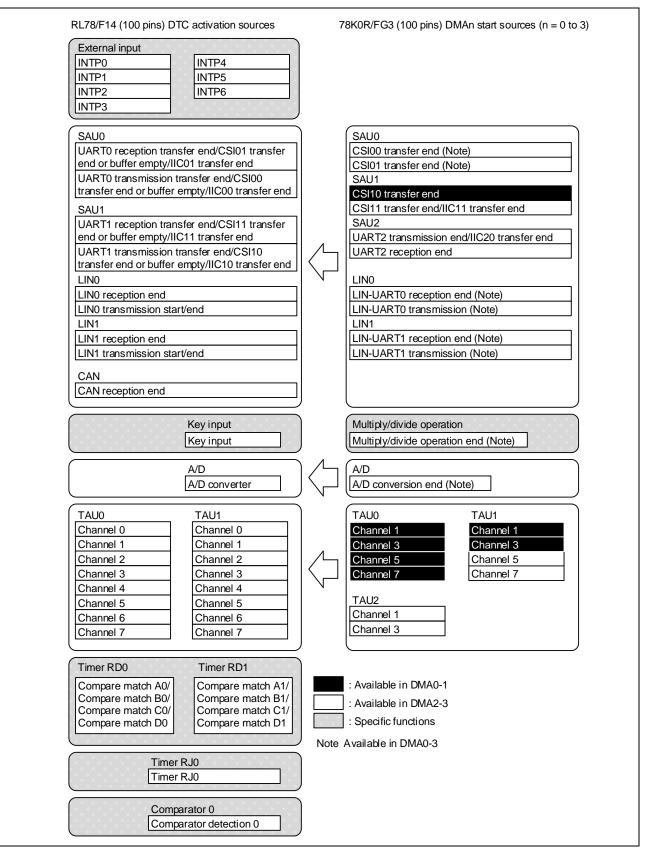

| DMA        |                     | DTC: 1 circuit (37, 38, 4                               | 4 sources)             | DMA: 2, 4 channels                                      |                                                 | 67               |

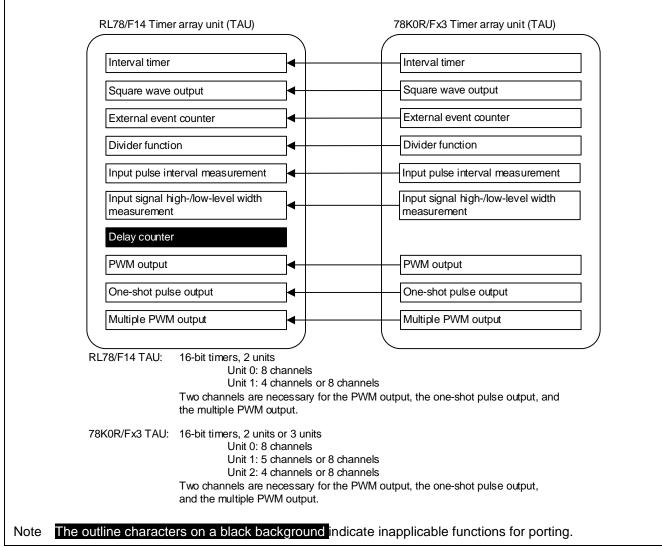

| Timer      |                     | TAU0: 8 channels, TAU1: 4, 8 channels                   |                        | TAU0: 8 channels, TAU                                   | J1: 5, 8 channels,                              | 73               |

|            |                     |                                                         |                        | TAU2: 0, 4, 8 channels                                  | i                                               |                  |

|            |                     | Timer RD:                                               | 2 channels             |                                                         | -                                               |                  |

|            |                     | Timer RJ:                                               | 1 channel              |                                                         | -                                               |                  |

|            |                     |                                                         | -                      | 16-bit wakeup timer:                                    | 1 channel                                       |                  |

|            |                     | Real-time clock: Provided -                             |                        | -                                                       |                                                 |                  |

| Serial     | SAU                 | SAU0/SAU1                                               |                        | SAU0/SAU1/SAU2                                          |                                                 | 105              |

| interface  |                     | ·CSI: 3, 4 channels                                     |                        | ·CSI: 2, 3, 4 channels                                  |                                                 |                  |

|            |                     | <ul> <li>Simplified I<sup>2</sup>C (Note 3):</li> </ul> | 3, 4 channels          | <ul> <li>Simplified I<sup>2</sup>C (Note 3):</li> </ul> | 0, 1, 2 channels                                |                  |

|            |                     | <ul> <li>UART: 2 channels</li> </ul>                    |                        | <ul> <li>UART: 0, 1 channel</li> </ul>                  |                                                 |                  |

|            | I <sup>2</sup> C    | IICA:                                                   | 0, 1 channel           |                                                         | -                                               |                  |

|            | LIN-UART            | RLIN3:                                                  | 1, 2 channels          | UARTF:                                                  | 2 channels (Note 4)                             |                  |

|            | CAN                 | RS-CAN lite:                                            | 1 channel              | 0, 1 channel                                            |                                                 |                  |

| A/D conve  | rter                | 10-bit resolution:                                      |                        | 10-bit resolution:                                      |                                                 | 112              |

|            |                     | 10, 12, 15, 18, 19, 20                                  | , 25, 31 channels      | 6, 8, 11, 15, 16, 24 cł                                 | nannels                                         |                  |

| D/A conve  | rter                | 8-bit resolution:                                       | 1 channel              |                                                         | -                                               | -                |

| Flash merr | nory                | Library is necessary for                                | rewriting flash memory | Library is necessary for                                | Library is necessary for rewriting flash memory |                  |

| Operation  | frequency           | Grade L:                                                | 32 MHz (MAX.)          | (A) grade products:                                     | 24 MHz (MAX.)                                   | -                |

|            |                     | Grade K:                                                | 24 MHz (MAX.)          | (A2) grade products:                                    | 24 MHz (MAX.)                                   |                  |

|            |                     | Grade Y:                                                | 24 MHz (MAX.)          |                                                         |                                                 |                  |

| Operating  | ambient temperature | Grade L:                                                | -40 to +105°C          | (A) grade products:                                     | -40 to +85°C                                    | -                |

|            |                     | Grade K:                                                | -40 to +125°C          | (A2) grade products:                                    | -40 to +125°C                                   |                  |

|            |                     | Grade Y:                                                | -40 to +150°C          |                                                         |                                                 |                  |

Notes 1. This table does not show all the functions provided for the RL78/F14.

2. The details about porting each function are described on the pages shown.

3. The simplified I<sup>2</sup>C (SAU) can perform only master transmission and master reception.

4. LIN reception can be performed by using TAU in combination.

### 1.1 100-pin Products

| Fur        | nctions (Note 1)                                 | RL78/F14 (100 p                                                                                  | ins)          | 78K0R/FG3 (100 p                                                                                               | pins)         | Page<br>(Note 2) |

|------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------|---------------|----------------------------------------------------------------------------------------------------------------|---------------|------------------|

| CPU        |                                                  | RL78 CPU core                                                                                    |               | 78K0R CPU core                                                                                                 |               | 20               |

| Memory     | Code flash memory                                | 64, 96, 128, 192, 256 Kbytes                                                                     |               | 64, 96, 128, 192, 256 Kbytes                                                                                   |               | 39               |

|            | Data flash memory                                | 4, 8 Kbytes                                                                                      |               | 16 Kbytes                                                                                                      |               |                  |

|            | RAM                                              | 6, 8, 10, 16, 20 Kbytes                                                                          |               | 4, 6, 8, 12, 16 Kbytes                                                                                         |               |                  |

| Reset      | Number of reset                                  | 7                                                                                                |               | 7                                                                                                              |               | 42               |

|            | sources                                          |                                                                                                  |               |                                                                                                                |               |                  |

|            | Power-on-clear                                   | When power supply is rising:                                                                     | 1.56 V (TYP.) | When power supply is rising:                                                                                   | 1.61 V (TYP.) |                  |

|            |                                                  | When power supply is falling:                                                                    | 1.55 V (TYP.) | When power supply is falling:                                                                                  | 1.59 V (TYP.) |                  |

| Voltage de | tection function                                 | Voltage is detected:                                                                             | 1 point       | Voltage is detected:                                                                                           | 1 point       | 48               |

|            |                                                  | <ul> <li>Interrupt &amp; reset mode:</li> </ul>                                                  | 4 levels      | Reset mode                                                                                                     | 10 levels     |                  |

|            |                                                  | <ul> <li>Reset mode:</li> </ul>                                                                  | 6 levels      | <ul> <li>Interrupt mode</li> </ul>                                                                             | 10 levels     |                  |

|            |                                                  | <ul> <li>Interrupt mode:</li> </ul>                                                              | 6 levels      |                                                                                                                |               |                  |

| Clock      | Main system clock                                |                                                                                                  |               | 2 MHz to 20 MHz                                                                                                |               | 49               |

|            | Subsystem clock                                  | 32.768 kHz                                                                                       |               | -                                                                                                              |               |                  |

|            | On-chip oscillator                               | Low-speed (f <sub>IL</sub> ): 15 kHz (TYP.)                                                      |               | Low-speed (fill): 30 kHz (TYP.)                                                                                |               |                  |

|            |                                                  | High-speed (f <sub>iH</sub> ): 1, 4, 8, 12, 16, 24, 32, 48, 64 MHz<br>(TYP.)                     |               | z High-speed (f <sub>IH</sub> ): 4, 8 MHz (TYP.)                                                               |               |                  |

|            | PLL                                              | PLL multiplication factor: x3, x4, x6, x8                                                        |               | PLL multiplication factor: ×1, ×6,                                                                             | <b>x</b> 8    |                  |

|            | WDT-dedicated<br>low-speed on-chip<br>oscillator | 15 kHz (TYP.)                                                                                    |               | -                                                                                                              |               |                  |

|            | Clock monitor<br>function                        | Provided                                                                                         |               | Provided                                                                                                       |               |                  |

| I/O port   |                                                  | I/O: 86<br>(CMOS/N-ch I/O: 16 (Note 3))<br>Input-only: 5 (Shared with oscillat<br>Output-only: 1 |               | I/O: 80<br>(CMOS/N-ch I/O: 5 (Note 4))<br>Input-only: 4<br>Output-only: 1<br>N-ch open-drain I/O (6 V tolerand | e): 4         | 57               |

| Interrupts | External                                         | 16 sources                                                                                       |               | 12 sources                                                                                                     |               | 63               |

|            | Internal                                         | 48 sources                                                                                       |               | 49 sources                                                                                                     |               |                  |

|            | Key input                                        | 8 channels                                                                                       |               | 8 channels                                                                                                     |               |                  |

|            | Number of interrupt sources                      | 64 sources                                                                                       |               | 61 sources                                                                                                     |               |                  |

| Watchdog   | timer                                            | Provided                                                                                         |               | Provided                                                                                                       |               | 65               |

Notes 1. This table does not show all the functions provided for the RL78/F14.

2. The details about porting each function are described on the pages shown.

3. N-ch open-drain output can be selected by writing "1" to the target bit of the port output mode register (POM1, POM6, POM7, POM12). For details, see **CHAPTER 3 PIN assignment** and the user's manual.

4. N-ch open-drain output can be selected by writing "1" to the target bit of the port output mode register (POM4, POM7). For details, see **CHAPTER 3 PIN assignment** and the user's manual.

### Table 1-2 Major functions of RL78/F14 (100 pins) which are portable from 78K0R/FG3 (2/2)

| Fur       | nction (Note 1)     | RL78/F14                                                  | l (100 pins)          | 78K0R/                                                 | FG3 (100 pins)                  | Page<br>(Note 2) |

|-----------|---------------------|-----------------------------------------------------------|-----------------------|--------------------------------------------------------|---------------------------------|------------------|

| DMA       |                     | DTC: 1 circuit (44 sources                                | 5)                    | DMA: 4 channels                                        |                                 | 67               |

| Timer     |                     | TAU0: 8 channels, TAU1: 8 channels                        |                       | TAU0: 8 channels, TAU1                                 | I: 8 channels, TAU2: 8 channels | 73               |

|           |                     | Timer RD:                                                 | 2 channels            |                                                        | -                               |                  |

|           |                     | Timer RJ:                                                 | 1 channel             |                                                        | -                               |                  |

|           |                     |                                                           | -                     | 16-bit wakeup timer:                                   | 1 channel                       |                  |

|           |                     | Real-time clock:                                          | Provided              |                                                        | -                               |                  |

| Serial    | SAU                 | SAU0/SAU1                                                 |                       | SAU0/SAU1/SAU2                                         |                                 | 105              |

| interface |                     | ·CSI: 4 channels                                          |                       | ·CSI: 4 channels                                       |                                 |                  |

|           |                     | <ul> <li>Simplified I<sup>2</sup>C (Note 3): 4</li> </ul> | channels              | <ul> <li>Simplified I<sup>2</sup>C (Note 3)</li> </ul> | : 2 channels                    |                  |

|           |                     | <ul> <li>UART: 2 channels</li> </ul>                      |                       | <ul> <li>UART: 1 channels</li> </ul>                   |                                 |                  |

|           | I <sup>2</sup> C    | IICA:                                                     | 1 channel             |                                                        | -                               |                  |

|           | LIN-UART            | RLIN3:                                                    | 2 channels            | UARTF:                                                 | 2 channels (Note 4)             |                  |

|           | CAN                 | RS-CAN lite:                                              | 1 channel             | 1 channel                                              |                                 |                  |

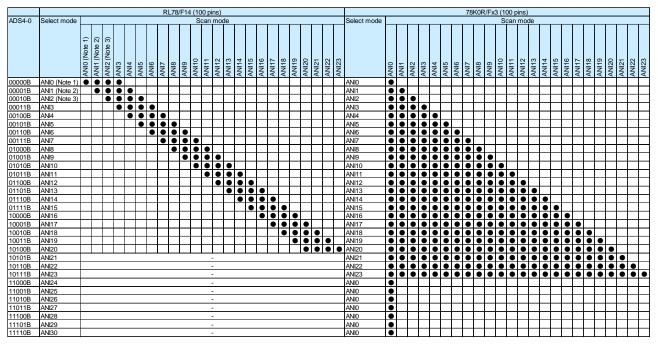

| A/D conve | rter                | 10-bit resolution:                                        | 31 channels           | 10-bit resolution:                                     | 24 channels                     | 112              |

| D/A conve | rter                | 8-bit resolution:                                         | 1 channel             |                                                        | -                               | -                |

| Flash men | nory                | Library is necessary for re                               | ewriting flash memory | Library is necessary for                               | rewriting flash memory          | -                |

| Operation | frequency           | Grade L:                                                  | 32 MHz (MAX.)         | (A) grade products:                                    | 24 MHz (MAX.)                   | -                |

|           |                     | Grade K:                                                  | 24 MHz (MAX.)         | (A2) grade products:                                   | 24 MHz (MAX.)                   |                  |

|           |                     | Grade Y:                                                  | 24 MHz (MAX.)         |                                                        |                                 |                  |

| Operating | ambient temperature | Grade L:                                                  | -40 to +105°C         | (A) grade products:                                    | -40 to +85°C                    | -                |

|           |                     | Grade K:                                                  | -40 to +125°C         | (A2) grade products:                                   | -40 to +125°C                   |                  |

|           |                     | Grade Y:                                                  | -40 to +150°C         |                                                        |                                 |                  |

Notes 1. This table does not show all the functions provided for the RL78/F14.

2. The details about porting each function are described on the pages shown.

3. The simplified I<sup>2</sup>C (SAU) can perform only master transmission and master reception.

4. LIN reception can be performed by using TAU in combination.

### 1.2 80-pin Products

| Table 1-3 Major functions of RL78/F14 (80 pins) | which are portable from 78K0R/FF3 (1/2) |

|-------------------------------------------------|-----------------------------------------|

|-------------------------------------------------|-----------------------------------------|

|            | nctions (Note 1)                                 | RL78/F14 (80 pi                                                                                   | ns)                                         | 78K0R/FF3 (80 p                                                                                                | ins)                              | Page<br>(Note 2 |

|------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------|

| CPU        |                                                  | RL78 CPU core                                                                                     |                                             | 78K0R CPU core                                                                                                 |                                   | 20              |

| Memory     | Code flash memory                                | 64, 96, 128, 192, 256 Kbytes                                                                      |                                             | 64, 96, 128, 192, 256 Kbytes                                                                                   |                                   | 39              |

|            | Data flash memory                                | 4, 8 Kbytes                                                                                       |                                             | 16 Kbytes                                                                                                      |                                   |                 |

|            | RAM                                              | 6, 8, 10, 16, 20 Kbytes                                                                           |                                             | 4, 6, 8, 12, 16 Kbytes                                                                                         |                                   | 1               |

| Reset      | Number of reset                                  | 7                                                                                                 |                                             | 7                                                                                                              |                                   | 42              |

|            | sources                                          |                                                                                                   |                                             |                                                                                                                |                                   |                 |

|            | Power-on-clear                                   | When power supply is rising:<br>When power supply is falling:                                     | 1.56 V (TYP.)<br>1.55 V (TYP.)              | When power supply is rising:<br>When power supply is falling:                                                  | 1.61 V (TYP.)<br>1.59 V (TYP.)    |                 |

| Voltage de | tection function                                 | Voltage is detected:<br>·Interrupt & reset mode:<br>·Reset mode:<br>·Interrupt mode:              | 1 point<br>4 levels<br>6 levels<br>6 levels | Voltage is detected:<br>·Reset mode<br>·Interrupt mode                                                         | 1 point<br>10 levels<br>10 levels | 48              |

| Clock      | Main system clock                                | 1 MHz to 20 MHz                                                                                   |                                             | 2 MHz to 20 MHz                                                                                                |                                   | 49              |

|            | Subsystem clock                                  | 32.768 kHz                                                                                        |                                             | -                                                                                                              |                                   |                 |

|            | On-chip oscillator                               | Low-speed (fiL): 15 kHz (TYP.)<br>High-speed (fiH): 1, 4, 8, 12, 16, 24, 32, 48, 64 MHz<br>(TYP.) |                                             | Low-speed (f <sub>IL</sub> ): 30 kHz (TYP.)<br>High-speed (f <sub>IH</sub> ): 4, 8 MHz (TYP.)                  |                                   |                 |

|            | PLL                                              | PLL multiplication factor: x3, x4, x6, x8                                                         |                                             | PLL multiplication factor: x1, x6, x8                                                                          |                                   |                 |

|            | WDT-dedicated<br>low-speed on-chip<br>oscillator | 15 kHz (TYP.)                                                                                     |                                             | -                                                                                                              |                                   |                 |

|            | Clock monitor<br>function                        | Provided                                                                                          |                                             | Provided                                                                                                       |                                   |                 |

| I/O port   |                                                  | I/O: 68<br>(CMOS/N-ch I/O: 16 (Note 3))<br>Input-only: 5 (Shared with oscilla<br>Output-only: 1   |                                             | I/O: 62<br>(CMOS/N-ch I/O: 5 (Note 4))<br>Input-only: 4<br>Output-only: 1<br>N-ch open-drain I/O (6 V tolerand | ce): 4                            | 57              |

| Interrupts | External                                         | 14 (Note 6), 16 (Note 5) sources                                                                  |                                             | 12 sources                                                                                                     |                                   | 63              |

|            | Internal                                         | 41 (Note 6), 48 (Note 5) sources                                                                  |                                             | 43 (Note 8), 47 (Note 7) sources                                                                               |                                   | 1               |

|            | Key input                                        | 8 channels                                                                                        |                                             | 8 channels                                                                                                     |                                   | 1               |

|            | Number of interrupt sources                      | 55 (Note 6), 64 (Note 5) sources                                                                  |                                             | 55 (Note 8), 59 (Note 7) sources                                                                               |                                   |                 |

| Watchdog   | timer                                            | Provided                                                                                          |                                             | Provided                                                                                                       |                                   | 65              |

Notes 1. This table does not show all the functions provided for the RL78/F14.

2. The details about porting each function are described on the pages shown.

3. N-ch open-drain output can be selected by writing "1" to the target bit of the port output mode register (POM1, POM6, POM7, POM12). For details, see **CHAPTER 3 PIN assignment** and the user's manual.

4. N-ch open-drain output can be selected by writing "1" to the target bit of the port output mode register (POM4, POM7). For details, see **CHAPTER 3 PIN assignment** and the user's manual.

- 5. R5F10PMx (x = G, H, J) products

- 6. R5F10PMx (x = E, F) products

- 7. µPD78F18yy (yy = 36, 37, 38, 39, 40) products

- 8. µPD78F18yy (yy = 23, 24, 25) products

### Table 1-3 Major functions of RL78/F14 (80 pins) which are portable from 78K0R/FF3 (2/2)

| Fun         | ction (Note 1)      | RL78/F                                                  | -14 (80 pins)                   | 78K0R/F                                | FF3 (80 pins)                | Page<br>(Note 2) |

|-------------|---------------------|---------------------------------------------------------|---------------------------------|----------------------------------------|------------------------------|------------------|

| DMA         |                     | DTC: 1 circuit (38 (Note                                | e 4), 44 (Note 3) sources)      | DMA: 4 channels                        |                              | 67               |

| Timer       |                     | TAU0: 8 channels, TAU1:                                 | 4 (Note 4), 8(Note 3), channels | TAU0: 8 channels, TAU1:                | 8 channels, TAU2: 4 channels | 73               |

|             |                     | Timer RD:                                               | 2 channels                      |                                        | -                            |                  |

|             |                     | Timer RJ:                                               | 1 channel                       |                                        | -                            |                  |

|             |                     |                                                         | -                               | 16-bit wakeup timer:                   | 1 channel                    |                  |

|             |                     | Real-time clock:                                        | Provided                        |                                        | -                            |                  |

| Serial      | SAU                 | SAU0/SAU1                                               |                                 | SAU0/SAU1/SAU2                         |                              | 105              |

| interface   |                     | ·CSI: 4 channels                                        |                                 | <ul> <li>CSI: 3 channels</li> </ul>    |                              |                  |

|             |                     | <ul> <li>Simplified I<sup>2</sup>C (Note 5):</li> </ul> | 4 channels                      | •Simplified I <sup>2</sup> C (Note 5): | 2 channels                   |                  |

|             |                     | UART: 2 channels                                        |                                 | ·UART: 1 channels                      |                              |                  |

|             | l <sup>2</sup> C    | IICA:                                                   | 1 channels                      |                                        | -                            |                  |

|             | LIN-UART            | RLIN3:1 (Note 4), 2 (No                                 | ote 3) channels                 | UARTF: 2 channels (No                  | te 6)                        |                  |

|             | CAN                 | RS-CAN lite:                                            | 1 channel                       | 0 (Note 8), 1 (Note 7) ch              | nannel                       |                  |

| A/D conver  | rter                | 10-bit resolution: 20 (No                               | ote 4), 25 (Note 3) channels    | 10-bit resolution: 16 cha              | innels                       | 112              |

| D/A conver  | rter                | 8-bit resolution:                                       | 1 channel                       |                                        | -                            | -                |

| Flash mem   | ory                 | Library is necessary for                                | rewriting flash memory          | Library is necessary for               | rewriting flash memory       | -                |

| Operation   | frequency           | Grade L:                                                | 32 MHz (MAX.)                   | (A) grade products:                    | 24 MHz (MAX.)                | -                |

|             |                     | Grade K:                                                | 24 MHz (MAX.)                   | (A2) grade products:                   | 24 MHz (MAX.)                |                  |

|             |                     | Grade Y:                                                | 24 MHz (MAX.)                   |                                        |                              |                  |

| Operating a | ambient temperature | Grade L:                                                | -40 to +105°C                   | (A) grade products:                    | -40 to +85°C                 | -                |

|             | -                   | Grade K:                                                | -40 to +125°C                   | (A2) grade products:                   | -40 to +125°C                |                  |

|             |                     | Grade Y:                                                | -40 to +150°C                   |                                        |                              |                  |

Notes 1. This table does not show all the functions provided for the RL78/F14.

- 2. The details about porting each function are described on the pages shown.

- 3. R5F10PMx (x = G, H, J) products

- 4. R5F10PMx (x = E, F) products

- 5. The simplified I<sup>2</sup>C (SAU) can perform only master transmission and master reception.

- 6. LIN reception can be performed by using TAU in combination.

- 7. µPD78F18yy (yy = 36, 37, 38, 39, 40) products

- 8. µPD78F18yy (yy = 23, 24, 25) products

### 1.3 64-pin Products

| Table 1-4 Major functions of RL78/F14 | (64 pins) which are portable from | 78K0R/FE3 (1/2) |

|---------------------------------------|-----------------------------------|-----------------|

|---------------------------------------|-----------------------------------|-----------------|

|            | nctions (Note 1)                                 | RL78/F14 (64 pi                                                                                                            | ns)                                         | 78K0R/FE3 (64 p                                                                                                | vins)                             | Page<br>(Note 2 |  |

|------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------|--|

| CPU        |                                                  | RL78 CPU core                                                                                                              |                                             | 78K0R CPU core                                                                                                 |                                   | 20              |  |

| Memory     | Code flash memory                                | 64, 96, 128, 192, 256 Kbytes                                                                                               |                                             | 32, 48, 64, 96, 128, 192, 256 Kby                                                                              | /tes                              | 39              |  |

|            | Data flash memory                                | 4, 8 Kbytes                                                                                                                |                                             | 16 Kbytes                                                                                                      |                                   |                 |  |

|            | RAM                                              | 6, 8, 10, 16, 20 Kbytes                                                                                                    |                                             | 2, 3, 4, 6, 8, 12, 16 Kbytes                                                                                   |                                   | 1               |  |

| Reset      | Number of reset                                  | 7                                                                                                                          |                                             | 7                                                                                                              |                                   | 42              |  |

|            | sources                                          |                                                                                                                            |                                             |                                                                                                                |                                   |                 |  |

|            | Power-on-clear                                   | When power supply is rising:<br>When power supply is falling:                                                              | 1.56 V (TYP.)<br>1.55 V (TYP.)              | When power supply is rising:<br>When power supply is falling:                                                  | 1.61 V (TYP.)<br>1.59 V (TYP.)    |                 |  |

| Voltage de | tection function                                 | Voltage is detected:<br>·Interrupt & reset mode:<br>·Reset mode:<br>·Interrupt mode:                                       | 1 point<br>4 levels<br>6 levels<br>6 levels | Voltage is detected:<br>·Reset mode<br>·Interrupt mode                                                         | 1 point<br>10 levels<br>10 levels | 48              |  |

| Clock      | Main system clock                                | 1 MHz to 20 MHz                                                                                                            |                                             | 2 MHz to 20 MHz                                                                                                |                                   | 49              |  |

|            | Subsystem clock                                  | 32.768 kHz                                                                                                                 |                                             | -                                                                                                              |                                   |                 |  |

|            | On-chip oscillator                               | Low-speed (f <sub>IL</sub> ): 15 kHz (TYP.)<br>High-speed (f <sub>H</sub> ): 1, 4, 8, 12, 16, 24, 32, 48, 64 MHz<br>(TYP.) |                                             | Low-speed (f <sub>IL</sub> ): 30 kHz (TYP.)<br>High-speed (f <sub>IH</sub> ): 4, 8 MHz (TYP.)                  |                                   |                 |  |

|            | PLL                                              | PLL multiplication factor: x3, x4, x6, x8                                                                                  |                                             | PLL multiplication factor: x1, x6, x8                                                                          |                                   |                 |  |

|            | WDT-dedicated<br>low-speed on-chip<br>oscillator | 15 kHz (TYP.)                                                                                                              |                                             | -                                                                                                              |                                   |                 |  |

|            | Clock monitor<br>function                        | Provided                                                                                                                   |                                             | Provided                                                                                                       |                                   |                 |  |

| I/O port   |                                                  | I/O: 52<br>(CMOS/N-ch I/O: 16 (Note 3))<br>Input-only: 5 (Shared with oscillar<br>Output-only: 1                           |                                             | I/O: 46<br>(CMOS/N-ch I/O: 5 (Note 4))<br>Input-only: 4<br>Output-only: 1<br>N-ch open-drain I/O (6 V tolerand | ce): 4                            | 57              |  |

| Interrupts | External                                         | 14 (Note 6), 15 (Note 5) sources                                                                                           |                                             | 10 (Note 8), 11 (Note 7) sources                                                                               |                                   | 63              |  |

|            | Internal                                         | 41 (Note 6), 48 (Note 5) sources                                                                                           |                                             | 41 (Note 8), 43 (Note 10), 47 (Note 9) sources                                                                 |                                   |                 |  |

|            | Key input                                        | 8 channels                                                                                                                 |                                             | 8 channels                                                                                                     |                                   | 1               |  |

|            | Number of interrupt sources                      | 55 (Note 6), 63 (Note 5) sources                                                                                           |                                             | 51 (Note 8), 54 (Note 10), 58 (Note                                                                            | e 9) sources                      |                 |  |

| Watchdog   | timer                                            | Provided                                                                                                                   |                                             | Provided                                                                                                       |                                   | 65              |  |

Notes 1. This table does not show all the functions provided for the RL78/F14.

2. The details about porting each function are described on the pages shown.

3. N-ch open-drain output can be selected by writing "1" to the target bit of the port output mode register (POM1, POM6, POM7, POM12). For details, see **CHAPTER 3 PIN assignment** and the user's manual.

4. N-ch open-drain output can be selected by writing "1" to the target bit of the port output mode register (POM4, POM7). For details, see **CHAPTER 3 PIN assignment** and the user's manual.

- 5. R5F10PLx (x = G, H, J) products

- 6. R5F10PLx (x = E, F) products

- 7. µPD78F18yy (yy = 21, 22, 31, 32, 33, 34, 35) products

- 8. µPD78F18yy (yy = 18, 19, 20) products

- 9. µPD78F18yy (yy = 31, 32, 33, 34, 35) products

- 10.µPD78F18yy (yy = 21, 22) products

#### Table 1-4 Major functions of RL78/F14 (64 pins) which are portable from 78K0R/FE3 (2/2)

| Fun                 | action (Note 1)     | RL                                                                                       | 78/F14 (64 pins)                    | 78K0R/I                                                                                                             | FE3 (64 pins)                | Page<br>(Note 2) |

|---------------------|---------------------|------------------------------------------------------------------------------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------|------------------------------|------------------|

| DMA                 |                     | DTC: 1 circuit (38 (N                                                                    | lote 4), 44 (Note 3) sources)       | DMA: 4 channels                                                                                                     |                              | 67               |

| Timer               |                     | TAU0: 8 channels, TA                                                                     | U1: 4 (Note 4), 8 (Note 3) channels | TAU0: 8 channels, TAU1:                                                                                             | 8 channels, TAU2: 4 channels | 73               |

|                     |                     | Timer RD:                                                                                | 2 channels                          |                                                                                                                     | -                            |                  |

|                     |                     | Timer RJ:                                                                                | 1 channel                           |                                                                                                                     | -                            |                  |

|                     |                     |                                                                                          | -                                   | 16-bit wakeup timer:                                                                                                | 1 channel                    |                  |

|                     |                     | Real-time clock:                                                                         | Provided                            |                                                                                                                     | -                            |                  |

| Serial<br>interface | SAU                 | SAU0/SAU1<br>•CSI: 4 channels<br>•Simplified I <sup>2</sup> C (Note<br>•UART: 2 channels | e 5): 4 channels                    | SAU0/SAU1/SAU2<br>·CSI: 3 channels<br>·Simplified I <sup>2</sup> C (Note 5):<br>channels<br>·UART: 0 (Note 8), 1 (N |                              | 105              |

|                     | I <sup>2</sup> C    | IICA:                                                                                    | 1 channel                           | , <i>, , , , , , , , , , , , , , , , , , </i>                                                                       | -                            |                  |

|                     | LIN-UART            | RLIN3: 1 (Note 4), 2                                                                     | (Note 3) channels                   | UARTF: 2 channels (No                                                                                               | ote 6)                       |                  |

|                     | CAN                 | RS-CAN lite:                                                                             | 1 channel                           | 0 (Note 10), 1 (Note 9) 0                                                                                           | channel                      |                  |

| A/D conver          | rter                | 10-bit resolution: 19                                                                    | (Note 4), 20 (Note 3) channels      | 10-bit resolution: 15 cha                                                                                           | annels                       | 112              |

| D/A conver          | rter                | 8-bit resolution:                                                                        | 1 channel                           |                                                                                                                     | -                            | -                |

| Flash mem           | nory                | Library is necessary                                                                     | for rewriting flash memory          | Library is necessary for                                                                                            | rewriting flash memory       | -                |

| Operation t         | frequency           | Grade L:                                                                                 | 32 MHz (MAX.)                       | (A) grade products:                                                                                                 | 24 MHz (MAX.)                | -                |

|                     |                     | Grade K:                                                                                 | 24 MHz (MAX.)                       | (A2) grade products:                                                                                                | 24 MHz (MAX.)                |                  |

|                     |                     | Grade Y:                                                                                 | 24 MHz (MAX.)                       |                                                                                                                     |                              |                  |

| Operating           | ambient temperature | Grade L:                                                                                 | -40 to +105°C                       | (A) grade products:                                                                                                 | -40 to +85°C                 | -                |

|                     |                     | Grade K:<br>Grade Y:                                                                     | -40 to +125°C<br>-40 to +150°C      | (A2) grade products:                                                                                                | -40 to +125°C                |                  |

Notes 1. This table does not show all the functions provided for the RL78/F14.

- 2. The details about porting each function are described on the pages shown.

- 3. R5F10PLx (x = G, H, J) products

- 4. R5F10PLx (x = E, F) products

- 5. The simplified I<sup>2</sup>C (SAU) can perform only master transmission and master reception.

- 6. LIN reception can be performed by using TAU in combination.

- 7. μPD78F18yy (yy = 21, 22, 31, 32, 33, 34, 35) products

- 8. µPD78F18yy (yy = 18, 19, 20) products

- 9.  $\mu$ PD78F18yy (yy = 31, 32, 33, 34, 35) products

- 10.µPD78F18yy (yy = 18, 19, 20, 21, 22) products

### 1.4 48-pin Products

| Fur        | nctions (Note 1)    | RL78/F14 (48 pi                                                    | ns)                    | 78K0R/FC3 (48                               | pins)         | Page<br>(Note 2) |

|------------|---------------------|--------------------------------------------------------------------|------------------------|---------------------------------------------|---------------|------------------|

| CPU        |                     | RL78 CPU core                                                      |                        | 78K0R CPU core                              |               | 20               |

| Memory     | Code flash memory   | 48, 64, 96, 128, 192, 256 Kbytes                                   |                        | 24, 32, 48, 64, 96, 128, 192, 256           | Kbytes        | 39               |

| ,          | Data flash memory   | 4, 8 Kbytes                                                        |                        | 16 Kbytes                                   | ,             |                  |

|            | RAM                 | 4, 6, 8, 10, 16, 20 Kbytes                                         |                        | 1.5, 2, 3, 4, 6, 8, 12, 16 Kbytes           |               |                  |

| Reset      | Number of reset     | 7                                                                  |                        | 7                                           |               | 42               |

|            | sources             |                                                                    |                        |                                             |               |                  |

|            | Power-on-clear      | When power supply is rising:                                       | 1.56 V (TYP.)          | When power supply is rising:                | 1.61 V (TYP.) |                  |

|            |                     | When power supply is falling:                                      | 1.55 V (TYP.)          | When power supply is falling:               | 1.59 V (TYP.) |                  |

| Voltage de | etection function   | Voltage is detected:                                               | 1 point                | Voltage is detected:                        | 1 point       | 48               |

|            |                     | ·Interrupt & reset mode:                                           | 4 levels               | ·Reset mode                                 | 10 levels     |                  |

|            |                     | ·Reset mode:                                                       | 6 levels               | Interrupt mode                              | 10 levels     |                  |

|            |                     | <ul> <li>Interrupt mode:</li> </ul>                                | 6 levels               |                                             |               |                  |

| Clock      | Main system clock   | 1 MHz to 20 MHz                                                    |                        | 2 MHz to 20 MHz                             |               | 49               |

|            | Subsystem clock     | 32.768 kHz                                                         |                        | -                                           |               |                  |

| F          | On-chip oscillator  | Low-speed (f <sub>II</sub> ): 15 kHz (TYP.)                        |                        | Low-speed (f <sub>IL</sub> ): 30 kHz (TYP.) |               |                  |

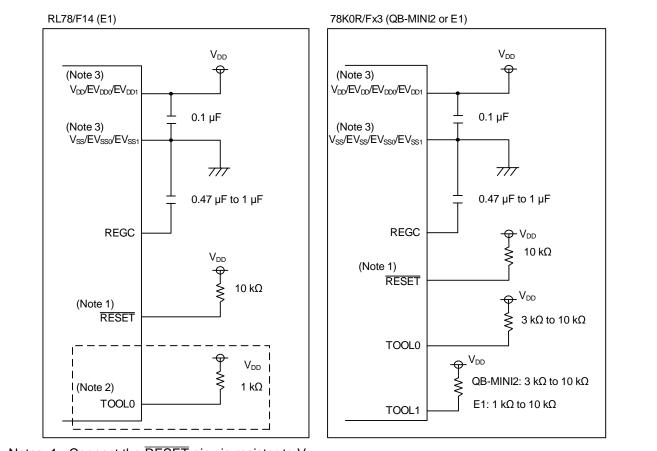

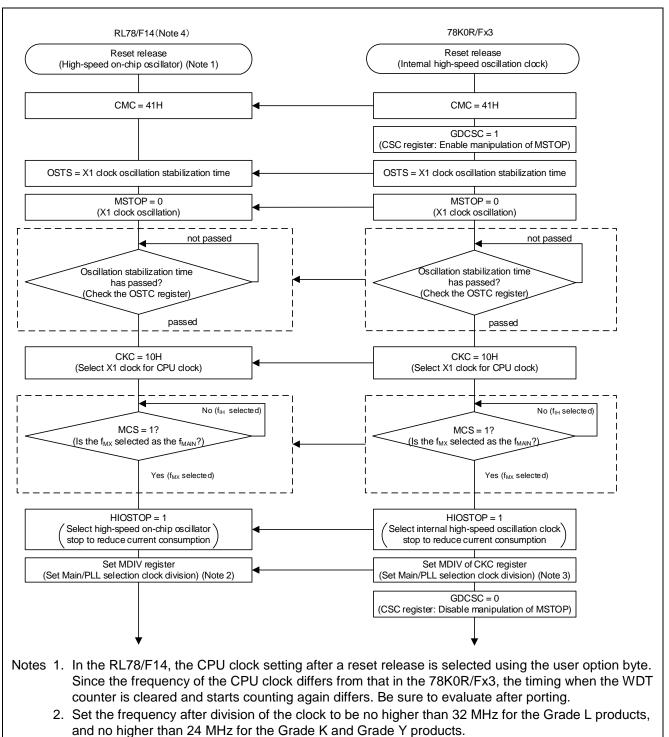

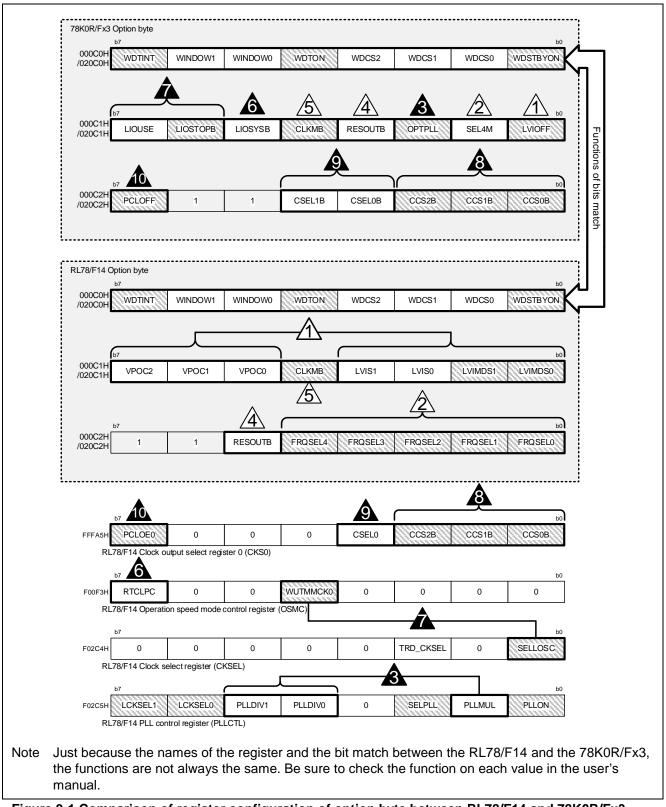

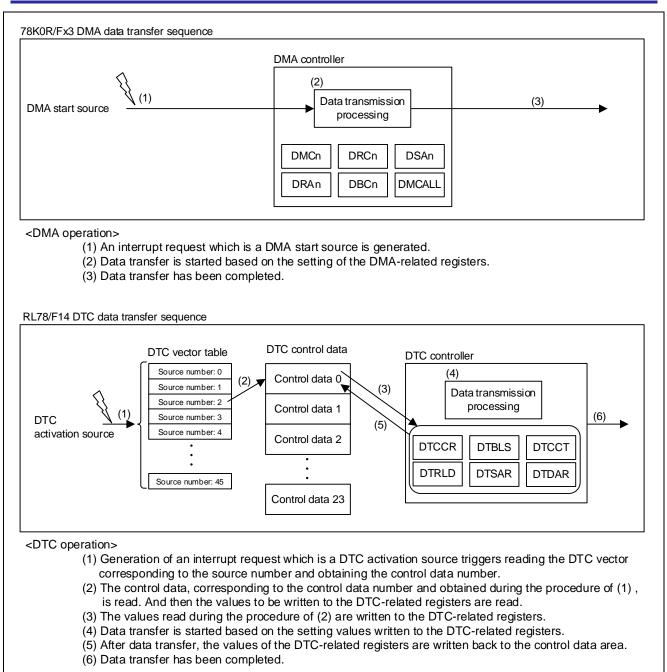

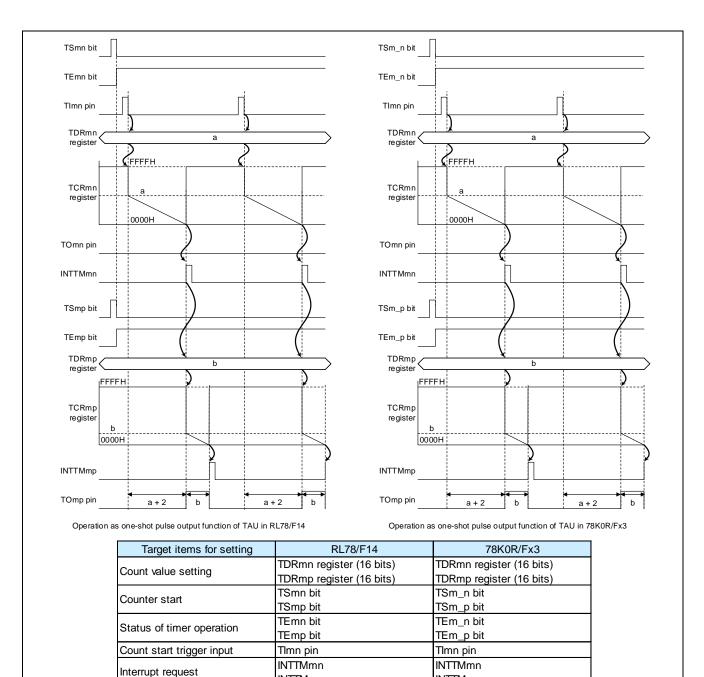

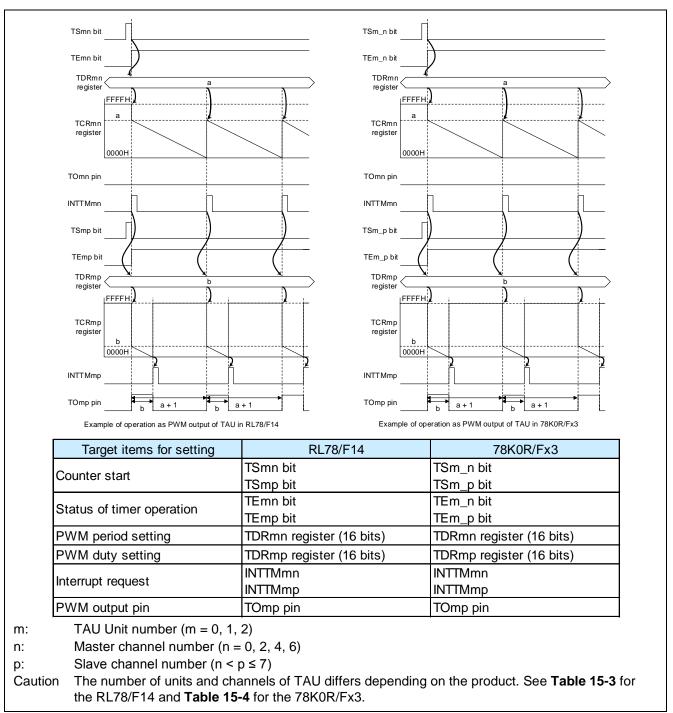

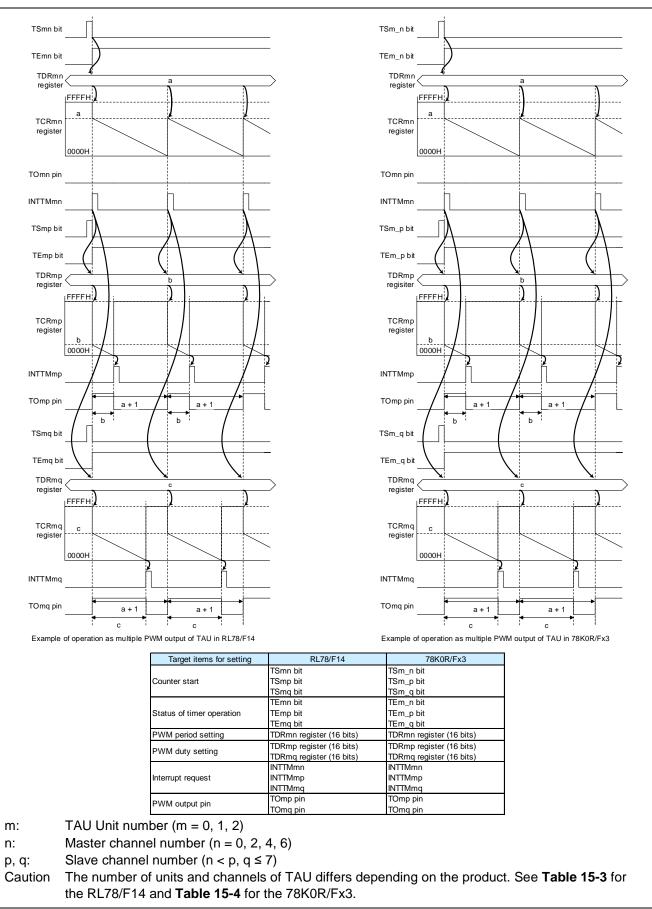

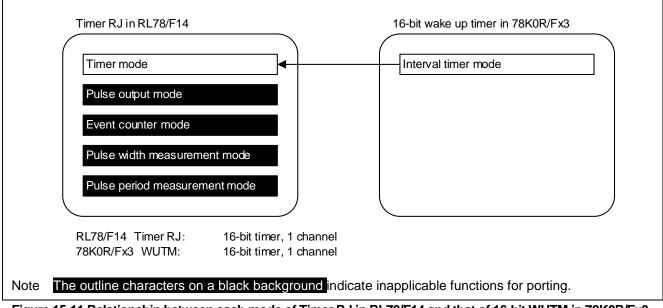

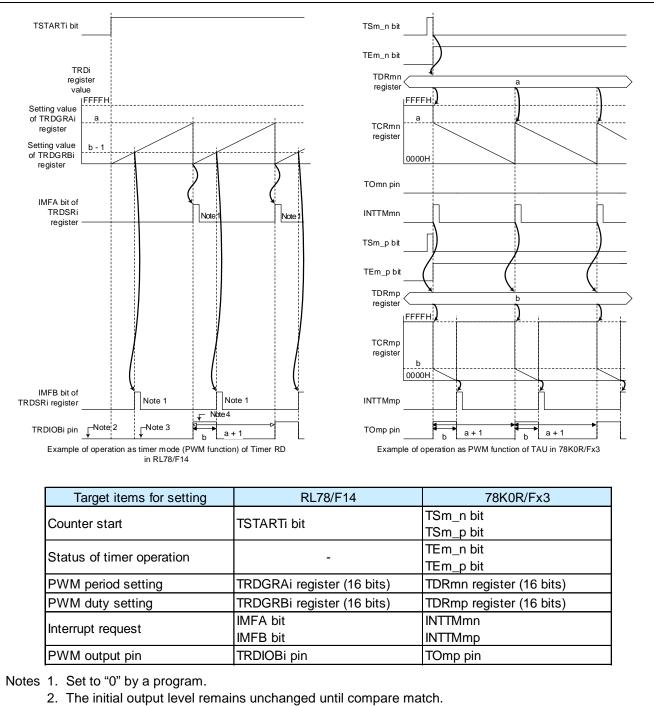

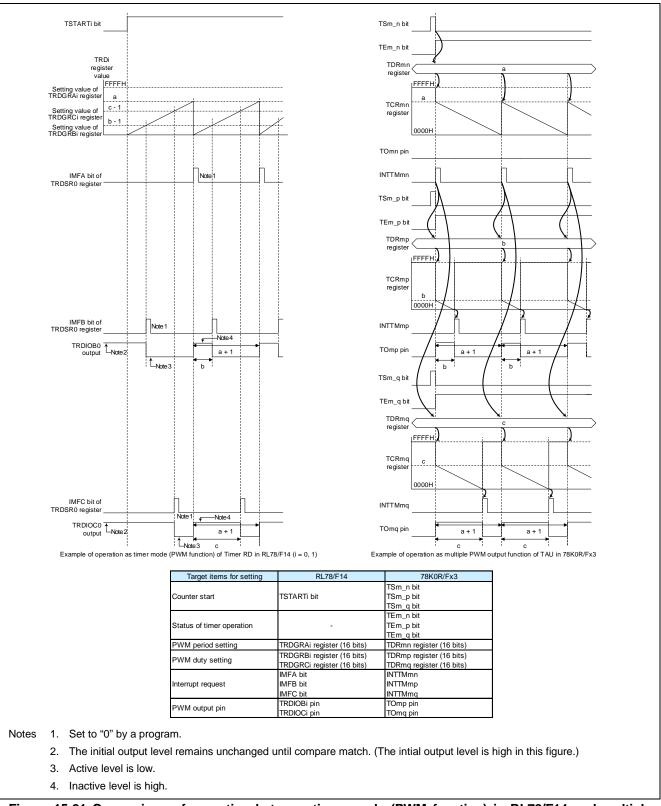

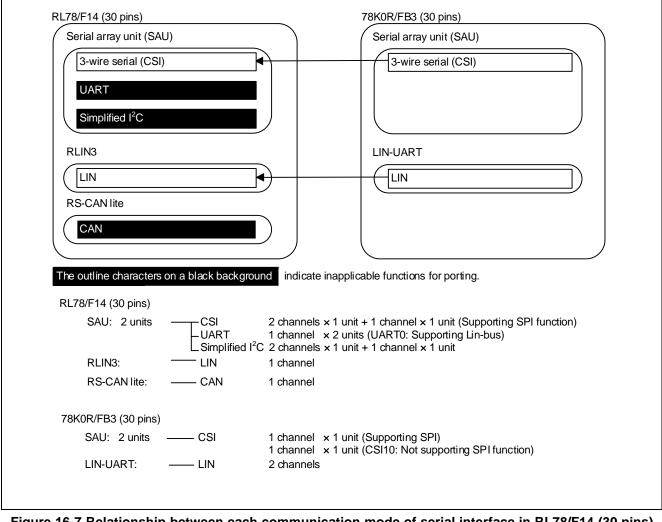

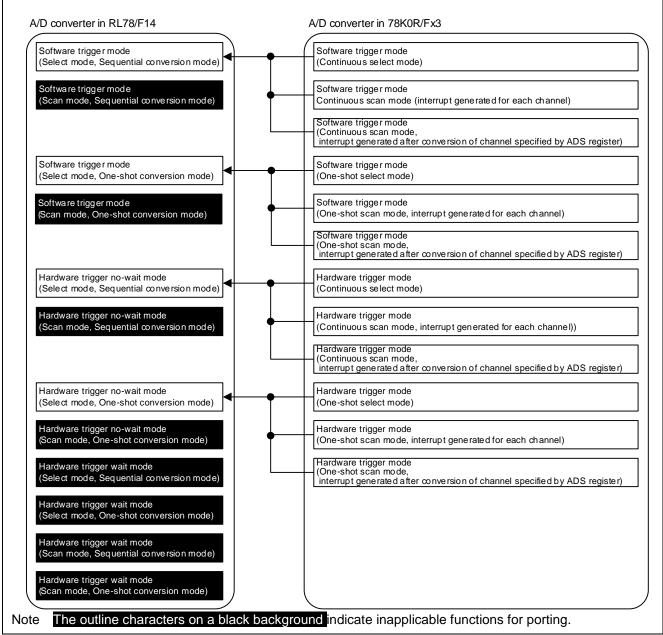

|            | en en p econator    | High-speed (f <sub>II</sub> ): 1, 4, 8, 12, 16, 24, 32, 48, 64 MHz |                        | High-speed ( $f_{H}$ ): 4, 8 MHz (TYP.)     |               |                  |