# **RH850/F1x Series**

Hardware Design Guide

### Introduction

This application note is intended to provide RH850/F1x series specific information and recommendations on the device usage. It should be used in conjunction with the corresponding RH850/F1x series user manuals and data sheets.

#### **Target Device**

#### RH850/F1L Group

RH850/F1L (176 pin)

RH850/F1L (144 pin)

RH850/F1L (100 pin)

RH850/F1L (80 pin)

RH850/F1L (64 pin)

RH850/F1L (48 pin)

#### RH850/F1M Group

RH850/F1M (233 pin) RH850/F1M (176 pin) RH850/F1M (144 pin)

#### RH850/F1H Group

RH850/F1H (272 pin) RH850/F1H (233 pin) RH850/F1H (176 pin)

R01AN1410EJ0420 Rev. 4.20 January 26, 2016

### **Table of Contents**

| 1.1       User Manual       6         1.2       Data Sheet       6         1.3       Operating Precaution       7         2.       Power Supply Overview of RH850/F1L Group       8         2.1.1       Power Supply Pin Overview of RH850/F1L Group       8         2.1.2       Power Supply Pin Configuration of RH850/F1L Group       8         2.1.3       Power Supply Pin Architecture of RH850/F1L Group       8         2.1.4       Power Supply Overview of RH850/F1L Group       12         2.2       Power Supply Pin Overview of RH850/F1M Group       13         2.2.1       Power Supply Pin Overview of RH850/F1M Group       13         2.2.1       Power Supply Pin Configuration of RH850/F1M Group       13         2.2.2       Power Supply Pin Configuration of RH850/F1M Group       13         2.2.3       Power Supply Pin Configuration of RH850/F1M Group       13         2.3.4       Power Supply Pin Overview of RH850/F1H Group       18         2.3.1       Power Supply Pin Configuration of RH850/F1H Group       18         2.3.2       Power Supply Pin Configuration of RH850/F1H Group       18         2.3.3       Power Supply Pin Configuration of RH850/F1H Group       23         2.4       Power Supply Pin Configuration of RH850/F1H Group       23<                                                                                                               | 1. Reference Documents                                          | 6  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|----|

| 1.3         Operating Precaution         7           2.         Power Supply Overview of RH850/F1L Group         8           2.1         Power Supply Overview of RH850/F1L Group         8           2.1.1         Power Supply Pin Overview of RH850/F1L Group         8           2.1.2         Power Supply Pin Configuration of RH850/F1L Group         8           2.1.3         Power Supply Pin Architecture of RH850/F1L Group         8           2.1.4         Power Supply Overview of RH850/F1M Group         12           2.2         Power Supply Pin Overview of RH850/F1M Group         13           2.2.1         Power Supply Pin Overview of RH850/F1M Group         13           2.2.2         Power Supply Pin Configuration of RH850/F1M Group         13           2.2.3         Power Supply Pin Configuration of RH850/F1M Group         13           2.2.4         Power Supply Pin Configuration of RH850/F1H Group         18           2.3.1         Power Supply Pin Configuration of RH850/F1H Group         18           2.3.2         Power Supply Pin Configuration of RH850/F1H Group         18           2.3.3         Power Supply Pin Configuration of RH850/F1H Group         18           2.3.4         Power Supply Pin Configuration of RH850/F1H Group         18           2.3.3         Power Supply Pin Archit                                                  | 1.1 User Manual                                                 | 6  |

| 2. Power Supply       8         2.1 Power Supply Overview of RH850/F1L Group       8         2.1.1 Power Supply Pin Overview of RH850/F1L Group       8         2.1.2 Power Supply Pin Configuration of RH850/F1L Group       8         2.1.3 Power Supply Pin Architecture of RH850/F1L Group       8         2.1.4 Power Supply Overview of RH850/F1L Group       12         2.2 Power Supply Overview of RH850/F1M Group       13         2.2.1 Power Supply Pin Overview of RH850/F1M Group       13         2.2.2 Power Supply Pin Overview of RH850/F1M Group       13         2.2.3 Power Supply Pin Architecture of RH850/F1M Group       13         2.2.4 Power Supply Pin Configuration of RH850/F1M Group       13         2.2.5 Power Supply Pin Architecture of RH850/F1M Group       18         2.3.1 Power Supply Pin Configuration of RH850/F1H Group       18         2.3.2 Power Supply Pin Configuration of RH850/F1H Group       18         2.3.3 Power Supply Pin Configuration of RH850/F1H Group       18         2.3.4 Power Supply Pin Configuration of RH850/F1H Group       18         2.3.5 Power Supply Pin Configuration of RH850/F1H Group       19         2.3.5 Power Supply Pin Configuration of RH850/F1H Group       23         2.4 Principle Capacitor Placement at REGVCC of RH850/F1X Series       24         3. Minimum External Components of RH850/F1L Group          |                                                                 | -  |

| 2.1       Power Supply Overview of RH850/F1L Group       8         2.1.1       Power Supply Pin Overview of RH850/F1L Group       8         2.1.2       Power Supply Pin Configuration of RH850/F1L Group       8         2.1.3       Power Supply Pin Architecture of RH850/F1L Group       8         2.1.4       Power Supply Overview of RH850/F1L Group       12         2.2       Power Supply Overview of RH850/F1M Group       13         2.2.1       Power Supply Pin Overview of RH850/F1M Group       13         2.2.2       Power Supply Pin Overview of RH850/F1M Group       13         2.2.3       Power Supply Pin Configuration of RH850/F1M Group       13         2.2.4       Power Supply Dim Overview of RH850/F1M Group       13         2.2.4       Power Supply Pin Configuration of RH850/F1H Group       18         2.3.1       Power Supply Pin Overview of RH850/F1H Group       18         2.3.1       Power Supply Pin Configuration of RH850/F1H Group       18         2.3.4       Power Supply Pin Architecture of RH850/F1H Group       18         2.3.5       Power Supply Pin Architecture of RH850/F1H Group       23         2.4       Power Supply Pin Architecture of RH850/F1H Group       23         2.4       Power Supply Pin Architecture of RH850/F1H Group       23                                                                                               | 1.3 Operating Precaution                                        | 7  |

| 2.1.1       Power Supply Pin Overview of RH850/F1L Group       8         2.1.2       Power Supply Pin Configuration of RH850/F1L Group       8         2.1.3       Power Supply Pin Architecture of RH850/F1L Group       8         2.1.4       Power Supply Overview of RH850/F1L Group       12         2.2       Power Supply Overview of RH850/F1M Group       13         2.2.1       Power Supply Pin Overview of RH850/F1M Group       13         2.2.2       Power Supply Pin Configuration of RH850/F1M Group       13         2.2.3       Power Supply Pin Configuration of RH850/F1M Group       13         2.2.4       Power Supply Pin Architecture of RH850/F1M Group       13         2.2.4       Power Supply Pin Configuration of RH850/F1H Group       18         2.3.1       Power Supply Pin Overview of RH850/F1H Group       18         2.3.1       Power Supply Pin Configuration of RH850/F1H Group       18         2.3.4       Power Supply Pin Architecture of RH850/F1H Group       18         2.3.5       Power Supply Pin Architecture of RH850/F1H Group       23         2.4       Principle Capacitor Placement at REGVCC of RH850/F1x Series       24         3.4       Principle Capacitor Placement at REGVCC of RH850/F1K Series       25         3.2       Minimum External Components of RH850/F1M Group                                                                  | 2. Power Supply                                                 | 8  |

| 2.1.2       Power Supply Pin Configuration of RH850/F1L Group.       8         2.1.3       Power Supply Pin Architecture of RH850/F1L Group.       8         2.1.4       Power Supply Overview of RH850/F1L Group.       12         2.2       Power Supply Overview of RH850/F1M Group.       13         2.2.1       Power Supply Din Overview of RH850/F1M Group.       13         2.2.2       Power Supply Pin Configuration of RH850/F1M Group.       13         2.2.3       Power Supply Pin Architecture of RH850/F1M Group.       13         2.2.4       Power Supply Din Architecture of RH850/F1M Group.       13         2.2.5       Power Supply Din Overview of RH850/F1H Group.       18         2.3.1       Power Supply Pin Configuration of RH850/F1H Group.       18         2.3.1       Power Supply Pin Configuration of RH850/F1H Group.       18         2.3.2       Power Supply Pin Configuration of RH850/F1H Group.       18         2.3.3       Power Supply Pin Architecture of RH850/F1H Group.       18         2.3.4       Power Supply Pin Architecture of RH850/F1H Group.       19         2.3.5       Power Supply Pin Architecture of RH850/F1H Group.       23         2.4       Principle Capacitor Placement at REGVCC of RH850/F1x Series.       24         3.1       Minimum External Components of RH850/F1M G                                                          | 2.1 Power Supply Overview of RH850/F1L Group                    |    |

| 2.1.3       Power Supply Pin Architecture of RH850/F1L Group       8         2.1.4       Power Supply Overview of RH850/F1L Group       12         2.2       Power Supply Overview of RH850/F1M Group       13         2.2.1       Power Supply Pin Overview of RH850/F1M Group       13         2.2.2       Power Supply Pin Configuration of RH850/F1M Group       13         2.2.3       Power Supply Pin Architecture of RH850/F1M Group       13         2.2.4       Power Supply Overview of RH850/F1M Group       13         2.2.5       Power Supply Dim Configuration of RH850/F1H Group       18         2.3.1       Power Supply Pin Overview of RH850/F1H Group       18         2.3.2       Power Supply Pin Overview of RH850/F1H Group       18         2.3.4       Power Supply Pin Configuration of RH850/F1H Group       18         2.3.3       Power Supply Pin Architecture of RH850/F1H Group       18         2.3.4       Power Supply Timing of RH850/F1H Group       23         2.4       Principle Capacitor Placement at REGVCC of RH850/F1x Series       24         3.       Minimum External Components of RH850/F1M Group       25         3.1       Minimum External Components of RH850/F1H Group       28         3.3       Minimum External Components of RH850/F1H Group       28                                                                                             | 2.1.1 Power Supply Pin Overview of RH850/F1L Group              |    |

| 2.1.4       Power Supply Timing of RH850/F1L Group       12         2.2       Power Supply Overview of RH850/F1M Group       13         2.2.1       Power Supply Pin Overview of RH850/F1M Group       13         2.2.2       Power Supply Pin Configuration of RH850/F1M Group       13         2.2.3       Power Supply Pin Architecture of RH850/F1M Group       13         2.2.4       Power Supply Dia Architecture of RH850/F1M Group       13         2.2.4       Power Supply Dia Architecture of RH850/F1H Group       18         2.3.1       Power Supply Pin Overview of RH850/F1H Group       18         2.3.1       Power Supply Pin Overview of RH850/F1H Group       18         2.3.2       Power Supply Pin Configuration of RH850/F1H Group       18         2.3.3       Power Supply Pin Configuration of RH850/F1H Group       18         2.3.3       Power Supply Pin Architecture of RH850/F1H Group       19         2.3.5       Power Supply Timing of RH850/F1H Group       19         2.3.5       Power Supply Timing of RH850/F1H Group       23         2.4       Principle Capacitor Placement at REGVCC of RH850/F1x Series       24         3.       Minimum External Components of RH850/F1H Group       28         3.3       Minimum External Components of RH850/F1H Group       28                                                                                            | 2.1.2 Power Supply Pin Configuration of RH850/F1L Group         |    |

| 2.2       Power Supply Overview of RH850/F1M Group.       13         2.2.1       Power Supply Pin Overview of RH850/F1M Group.       13         2.2.2       Power Supply Pin Configuration of RH850/F1M Group.       13         2.2.3       Power Supply Pin Architecture of RH850/F1M Group.       13         2.2.4       Power Supply Dim Architecture of RH850/F1M Group.       13         2.2.4       Power Supply Overview of RH850/F1H Group.       17         2.3       Power Supply Overview of RH850/F1H Group.       18         2.3.1       Power Supply Pin Configuration of RH850/F1H Group.       18         2.3.2       Power Supply Pin Configuration of RH850/F1H Group.       18         2.3.3       Power Supply Pin Configuration of RH850/F1H Group.       18         2.3.4       Power Supply Pin Architecture of RH850/F1H Group.       19         2.3.5       Power Supply Timing of RH850/F1H Group.       23         2.4       Principle Capacitor Placement at REGVCC of RH850/F1x Series.       24         3.       Minimum External Components of RH850/F1H Group.       25         3.1       Minimum External Components of RH850/F1H Group.       26         3.3       Minimum External Components of RH850/F1H Group.       33         4.1       Recommended Oscillator Circuit       33 <t< th=""><th>2.1.3 Power Supply Pin Architecture of RH850/F1L Group</th><th></th></t<> | 2.1.3 Power Supply Pin Architecture of RH850/F1L Group          |    |

| 2.2.1       Power Supply Pin Overview of RH850/F1M Group       13         2.2.2       Power Supply Pin Configuration of RH850/F1M Group       13         2.2.3       Power Supply Pin Architecture of RH850/F1M Group       13         2.2.4       Power Supply Overview of RH850/F1M Group       13         2.2.4       Power Supply Overview of RH850/F1H Group       17         2.3       Power Supply Overview of RH850/F1H Group       18         2.3.1       Power Supply Pin Overview of RH850/F1H Group       18         2.3.2       Power Supply Pin Configuration of RH850/F1H Group       18         2.3.3       Power Supply Pin Architecture of RH850/F1H Group       18         2.3.4       Power Supply Di Architecture of RH850/F1H Group       19         2.3.5       Power Supply Timing of RH850/F1H Group       23         2.4       Principle Capacitor Placement at REGVCC of RH850/F1K Series       24         3.       Minimum External Components       25         3.1       Minimum External Components of RH850/F1H Group       25         3.2       Minimum External Components of RH850/F1H Group       28         3.3       Minimum External Components of RH850/F1H Group       30         4.       Oscillator       33         4.1       Main Oscilllator       3                                                                                                               | 2.1.4 Power Supply Timing of RH850/F1L Group                    |    |

| 2.2.2       Power Supply Pin Configuration of RH850/F1M Group       13         2.2.3       Power Supply Pin Architecture of RH850/F1M Group       13         2.2.4       Power Supply Timing of RH850/F1M Group       17         2.3       Power Supply Overview of RH850/F1H Group       18         2.3.1       Power Supply Pin Overview of RH850/F1H Group       18         2.3.2       Power Supply Pin Configuration of RH850/F1H Group       18         2.3.3       Power Supply Handling at RH850/F1H Group       18         2.3.4       Power Supply Pin Architecture of RH850/F1H Group       19         2.3.5       Power Supply Timing of RH850/F1H Group       23         2.4       Principle Capacitor Placement at REGVCC of RH850/F1x Series       24         3.       Minimum External Components       25         3.1       Minimum External Components of RH850/F1H Group       25         3.2       Minimum External Components of RH850/F1H Group       26         3.3       Minimum External Components of RH850/F1H Group       30         4.       Oscillator       33         4.1       Main Oscillator Circuit       33         4.1       Nain Oscillator       34         4.2       Recommended Oscillator Layout       34         5.                                                                                                                                                 | 2.2 Power Supply Overview of RH850/F1M Group                    |    |

| 2.2.3       Power Supply Pin Architecture of RH850/F1M Group       13         2.2.4       Power Supply Timing of RH850/F1M Group       17         2.3       Power Supply Overview of RH850/F1H Group       18         2.3.1       Power Supply Pin Overview of RH850/F1H Group       18         2.3.2       Power Supply Pin Overview of RH850/F1H Group       18         2.3.3       Power Supply Pin Configuration of RH850/F1H Group       18         2.3.4       Power Supply Handling at RH850/F1H-272pin       18         2.3.5       Power Supply Timing of RH850/F1H Group       19         2.3.5       Power Supply Timing of RH850/F1H Group       23         2.4       Principle Capacitor Placement at REGVCC of RH850/F1x Series       24         3.       Minimum External Components       25         3.1       Minimum External Components of RH850/F1L Group       28         3.3       Minimum External Components of RH850/F1M Group       28         3.3       Minimum External Components of RH850/F1H Group       30         4.       Oscillator       33         4.1       Recommended Oscillator Circuit       33         4.1.1       Main Oscillator       34         4.2       Recommended Oscillator Layout       34         5.       <                                                                                                                                              | 2.2.1 Power Supply Pin Overview of RH850/F1M Group              |    |

| 2.2.4       Power Supply Timing of RH850/F1M Group       17         2.3       Power Supply Overview of RH850/F1H Group       18         2.3.1       Power Supply Pin Overview of RH850/F1H Group       18         2.3.2       Power Supply Pin Configuration of RH850/F1H Group       18         2.3.3       Power Supply Pin Configuration of RH850/F1H Group       18         2.3.4       Power Supply Handling at RH850/F1H-272pin       18         2.3.5       Power Supply Timing of RH850/F1H Group       19         2.3.5       Power Supply Timing of RH850/F1H Group       23         2.4       Principle Capacitor Placement at REGVCC of RH850/F1x Series       24         3.       Minimum External Components       25         3.1       Minimum External Components of RH850/F1L Group       28         3.3       Minimum External Components of RH850/F1M Group       28         3.3       Minimum External Components of RH850/F1M Group       30         4.       Oscillator       33         4.1       Recommended Oscillator Circuit       33         4.1.1       Main Oscillator       34         4.2       Recommended Oscillator Layout       34         5.       Device Pins       35         5.1.1       Minimum RESET Circuit                                                                                                                                                          | 2.2.2 Power Supply Pin Configuration of RH850/F1M Group         |    |

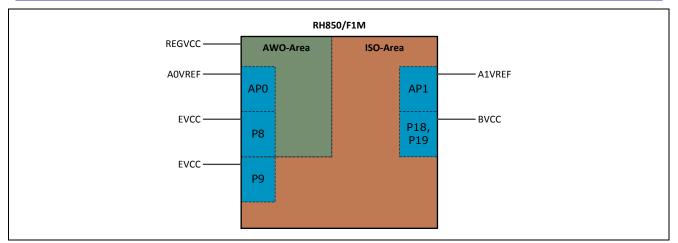

| 2.3       Power Supply Overview of RH850/F1H Group       18         2.3.1       Power Supply Pin Overview of RH850/F1H Group       18         2.3.2       Power Supply Pin Configuration of RH850/F1H Group       18         2.3.3       Power Supply Pin Configuration of RH850/F1H Group       18         2.3.4       Power Supply Handling at RH850/F1H Group       18         2.3.4       Power Supply Pin Architecture of RH850/F1H Group       19         2.3.5       Power Supply Timing of RH850/F1H Group       23         2.4       Principle Capacitor Placement at REGVCC of RH850/F1x Series       24         3.       Minimum External Components       25         3.1       Minimum External Components of RH850/F1M Group       25         3.2       Minimum External Components of RH850/F1M Group       28         3.3       Minimum External Components of RH850/F1H Group       30         4.       Oscillator       33         4.1       Main Oscillator Circuit       33         4.1.1       Main Oscillator       34         4.2       Recommended Oscillator Layout       34         5.       Device Pins       35         5.1.1       Minimum RESET Circuit       35         5.1.2       RESET Input Characteristic during Power-On </td <td>2.2.3 Power Supply Pin Architecture of RH850/F1M Group</td> <td></td>                                                                     | 2.2.3 Power Supply Pin Architecture of RH850/F1M Group          |    |

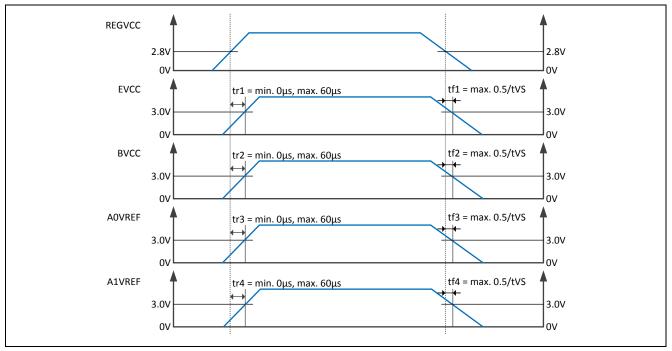

| 2.3.1       Power Supply Pin Overview of RH850/F1H Group       18         2.3.2       Power Supply Pin Configuration of RH850/F1H Group       18         2.3.3       Power Supply Handling at RH850/F1H-272pin       18         2.3.4       Power Supply Pin Architecture of RH850/F1H Group       19         2.3.5       Power Supply Timing of RH850/F1H Group       23         2.4       Principle Capacitor Placement at REGVCC of RH850/F1x Series       24         3.       Minimum External Components       25         3.1       Minimum External Components of RH850/F1L Group       25         3.2       Minimum External Components of RH850/F1M Group       28         3.3       Minimum External Components of RH850/F1H Group       28         3.3       Minimum External Components of RH850/F1H Group       30         4.       Oscillator       33         4.1       Recommended Oscillator Circuit       33         4.1.1       Main Oscillator       34         4.2       Recommended Oscillator Layout       34         5.       Device Pins       35         5.1.1       Minimum RESET Circuit       35         5.1.2       RESET Input Characteristics       35         5.1.3       RESET Pin Input Characteristic during Power-On                                                                                                                                                        | 2.2.4 Power Supply Timing of RH850/F1M Group                    |    |

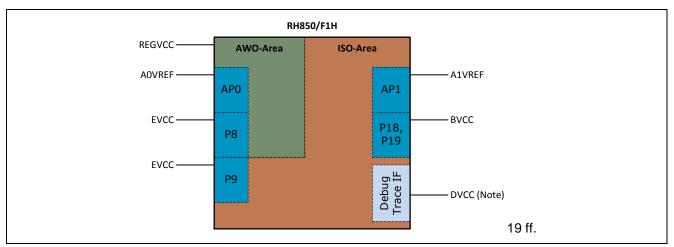

| 2.3.2Power Supply Pin Configuration of RH850/F1H Group182.3.3Power Supply Handling at RH850/F1H-272pin182.3.4Power Supply Pin Architecture of RH850/F1H Group192.3.5Power Supply Timing of RH850/F1H Group232.4Principle Capacitor Placement at REGVCC of RH850/F1x Series243.Minimum External Components253.1Minimum External Components of RH850/F1L Group253.2Minimum External Components of RH850/F1M Group283.3Minimum External Components of RH850/F1H Group304.Oscillator334.1Recommended Oscillator Circuit334.1.1Main Oscillator344.2Recommended Oscillator Layout345.Device Pins355.1.1Minimum RESET Circuit355.1.2RESET355.1.3RESET Tinput Characteristics355.1.3RESET Tinput Characteristic during Power-On36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2.3 Power Supply Overview of RH850/F1H Group                    |    |

| 2.3.3       Power Supply Handling at RH850/F1H-272pin       18         2.3.4       Power Supply Pin Architecture of RH850/F1H Group       19         2.3.5       Power Supply Timing of RH850/F1H Group       23         2.4       Principle Capacitor Placement at REGVCC of RH850/F1x Series       24         3.       Minimum External Components       25         3.1       Minimum External Components of RH850/F1L Group       25         3.2       Minimum External Components of RH850/F1L Group       28         3.3       Minimum External Components of RH850/F1H Group       28         3.3       Minimum External Components of RH850/F1H Group       30         4.       Oscillator       33         4.1       Recommended Oscillator Circuit       33         4.1.1       Main Oscillator       33         4.1.2       Sub Oscillator       34         4.2       Recommended Oscillator Layout       34         5.       Device Pins       35         5.1.1       Minimum RESET Circuit       35         5.1.2       RESET       35         5.1.3       RESET Pin Input Characteristic during Power-On       36                                                                                                                                                                                                                                                                                  | 2.3.1 Power Supply Pin Overview of RH850/F1H Group              |    |

| 2.3.4Power Supply Pin Architecture of RH850/F1H Group192.3.5Power Supply Timing of RH850/F1H Group232.4Principle Capacitor Placement at REGVCC of RH850/F1X Series243.Minimum External Components253.1Minimum External Components of RH850/F1L Group253.2Minimum External Components of RH850/F1M Group283.3Minimum External Components of RH850/F1H Group283.3Minimum External Components of RH850/F1H Group304.Oscillator334.1Recommended Oscillator Circuit334.1.1Main Oscillator344.2Recommended Oscillator Layout345.Device Pins355.1.1Minimum RESET Circuit355.1.2RESET355.1.3RESET Pin Input Characteristic during Power-On36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2.3.2 Power Supply Pin Configuration of RH850/F1H Group         |    |

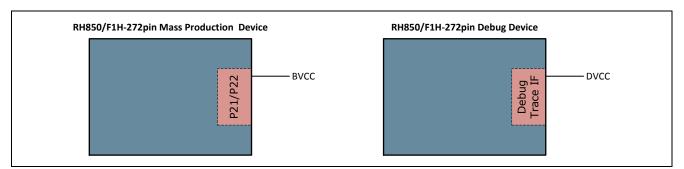

| 2.3.5Power Supply Timing of RH850/F1H Group232.4Principle Capacitor Placement at REGVCC of RH850/F1x Series243.Minimum External Components253.1Minimum External Components of RH850/F1L Group253.2Minimum External Components of RH850/F1M Group283.3Minimum External Components of RH850/F1H Group304.Oscillator334.1Recommended Oscillator Circuit334.1.1Main Oscillator334.1.2Sub Oscillator344.2Recommended Oscillator Layout345.Device Pins355.1.1Minimum RESET Circuit355.1.2RESET Input Characteristics355.1.3RESET Pin Input Characteristic during Power-On36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2.3.3 Power Supply Handling at RH850/F1H-272pin                 |    |

| 2.4       Principle Capacitor Placement at REGVCC of RH850/F1x Series       24         3.       Minimum External Components       25         3.1       Minimum External Components of RH850/F1L Group       25         3.2       Minimum External Components of RH850/F1M Group       28         3.3       Minimum External Components of RH850/F1H Group       28         3.3       Minimum External Components of RH850/F1H Group       30         4.       Oscillator       33         4.1       Recommended Oscillator Circuit       33         4.1.1       Main Oscillator       34         4.2       Recommended Oscillator Layout       34         5.       Device Pins       35         5.1.1       Minimum RESET Circuit       35         5.1.2       RESET Input Characteristics       35         5.1.3       RESET Pin Input Characteristic during Power-On       36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2.3.4 Power Supply Pin Architecture of RH850/F1H Group          |    |

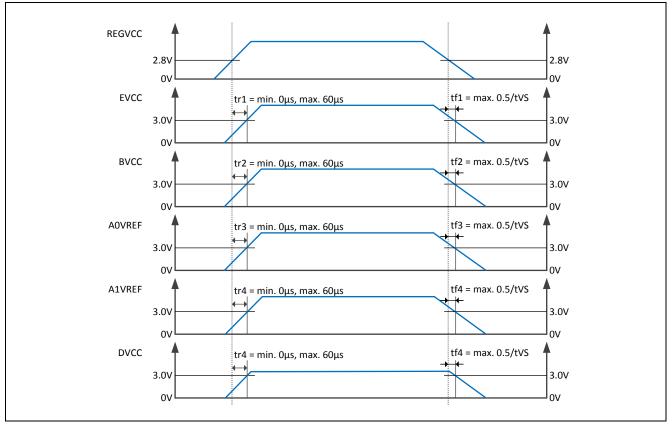

| 3. Minimum External Components       25         3.1 Minimum External Components of RH850/F1L Group       25         3.2 Minimum External Components of RH850/F1M Group       28         3.3 Minimum External Components of RH850/F1H Group       30         4. Oscillator.       33         4.1 Recommended Oscillator Circuit       33         4.1.1 Main Oscillator       33         4.1.2 Sub Oscillator       34         4.2 Recommended Oscillator Layout       34         5. Device Pins       35         5.1.1 Minimum RESET Circuit       35         5.1.2 RESET Input Characteristics       35         5.1.3 RESET Pin Input Characteristic during Power-On       36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2.3.5 Power Supply Timing of RH850/F1H Group                    |    |

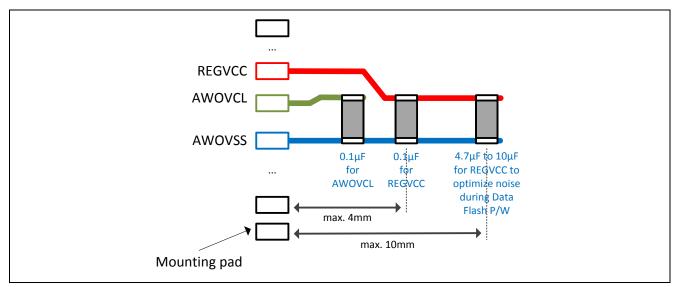

| 3.1       Minimum External Components of RH850/F1L Group       25         3.2       Minimum External Components of RH850/F1M Group       28         3.3       Minimum External Components of RH850/F1H Group       30         4.       Oscillator       33         4.1       Recommended Oscillator Circuit       33         4.1.1       Main Oscillator       33         4.1.2       Sub Oscillator       34         4.2       Recommended Oscillator Layout       34         5.       Device Pins       35         5.1.1       RESET       35         5.1.2       RESET Circuit       35         5.1.3       RESET Pin Input Characteristic during Power-On       36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2.4 Principle Capacitor Placement at REGVCC of RH850/F1x Series |    |

| 3.2       Minimum External Components of RH850/F1M Group       28         3.3       Minimum External Components of RH850/F1H Group       30         4.       Oscillator       33         4.1       Recommended Oscillator Circuit       33         4.1.1       Main Oscillator       33         4.1.2       Sub Oscillator       34         4.2       Recommended Oscillator Layout       34         5.       Device Pins       35         5.1       RESET       35         5.1.1       Minimum RESET Circuit       35         5.1.2       RESET Input Characteristics       35         5.1.3       RESET Pin Input Characteristic during Power-On       36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3. Minimum External Components                                  | 25 |

| 3.3 Minimum External Components of RH850/F1H Group       30         4. Oscillator       33         4.1 Recommended Oscillator Circuit       33         4.1.1 Main Oscillator       33         4.1.2 Sub Oscillator       34         4.2 Recommended Oscillator Layout       34         5. Device Pins       35         5.1 RESET       35         5.1.1 Minimum RESET Circuit       35         5.1.2 RESET Input Characteristics       35         5.1.3 RESET Pin Input Characteristic during Power-On       36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3.1 Minimum External Components of RH850/F1L Group              |    |

| 4. Oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3.2 Minimum External Components of RH850/F1M Group              |    |

| 4.1       Recommended Oscillator Circuit       33         4.1.1       Main Oscillator       33         4.1.2       Sub Oscillator       34         4.2       Recommended Oscillator Layout       34         5.       Device Pins       35         5.1       RESET       35         5.1.1       Minimum RESET Circuit       35         5.1.2       RESET Input Characteristics       35         5.1.3       RESET Pin Input Characteristic during Power-On       36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3.3 Minimum External Components of RH850/F1H Group              |    |

| 4.1       Recommended Oscillator Circuit       33         4.1.1       Main Oscillator       33         4.1.2       Sub Oscillator       34         4.2       Recommended Oscillator Layout       34         5.       Device Pins       35         5.1       RESET       35         5.1.1       Minimum RESET Circuit       35         5.1.2       RESET Input Characteristics       35         5.1.3       RESET Pin Input Characteristic during Power-On       36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4. Oscillator                                                   | 33 |

| 4.1.1       Main Oscillator       33         4.1.2       Sub Oscillator       34         4.2       Recommended Oscillator Layout       34         5.       Device Pins       35         5.1       RESET       35         5.1.1       Minimum RESET Circuit       35         5.1.2       RESET Input Characteristics       35         5.1.3       RESET Pin Input Characteristic during Power-On       36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                 |    |

| 4.1.2       Sub Oscillator       34         4.2       Recommended Oscillator Layout       34         5.       Device Pins       35         5.1       RESET       35         5.1.1       Minimum RESET Circuit       35         5.1.2       RESET Input Characteristics       35         5.1.3       RESET Pin Input Characteristic during Power-On       36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                 |    |

| 4.2 Recommended Oscillator Layout345. Device Pins355.1 RESET355.1.1 Minimum RESET Circuit355.1.2 RESET Input Characteristics355.1.3 RESET Pin Input Characteristic during Power-On36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                 |    |

| 5.1       RESET       35         5.1.1       Minimum RESET Circuit       35         5.1.2       RESET Input Characteristics       35         5.1.3       RESET Pin Input Characteristic during Power-On       36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                 |    |

| 5.1       RESET       35         5.1.1       Minimum RESET Circuit       35         5.1.2       RESET Input Characteristics       35         5.1.3       RESET Pin Input Characteristic during Power-On       36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5 Device Pins                                                   | 35 |

| 5.1.1Minimum RESET Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                 |    |

| 5.1.2RESET Input Characteristics355.1.3RESET Pin Input Characteristic during Power-On36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                 |    |

| 5.1.3 RESET Pin Input Characteristic during Power-On                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                 |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                 |    |

| 5.2 General Purpose I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                 |    |

| 5.2         | 2.1                          | RESET State of General Purpose I/O                                           | 37  |

|-------------|------------------------------|------------------------------------------------------------------------------|-----|

| 5.2         | 2.2                          | JP0_4/_DCUTRST                                                               | 37  |

| 5.2         | 2.3                          | P0_0/RESETOUT/CAN0TX/TAUD012/TAUD0O2/RLIN20RX/PWGA100/DPO                    | 37  |

| 5.2         | 5.2.4 Analog Filter Function |                                                                              | 38  |

| 5.2         | 2.5                          | Behaviour during Low Power Mode                                              | 39  |

| 5.3         | Re                           | commended Connection of unused Pins                                          | 40  |

| 5.3         | 3.1                          | Recommended Connection of unused Pins for RH850/F1L Group                    | 40  |

| 5.3         | 3.2                          | Recommended Connection of unused Pins for RH850/F1M Group                    | 42  |

| 5.3         | 3.3                          | Recommended Connection of unused Pins for RH850/F1H Group                    | 44  |

| 5.4         | Pir                          | Assignment Differences                                                       | 46  |

| 5.5         | Inje                         | ected Current                                                                | 47  |

| 6. A        |                              | Converter                                                                    | 10  |

| о. д<br>6.1 |                              | nversion Time                                                                |     |

| 6.2         |                              | ternal Multiplexer Wait Time                                                 |     |

|             |                              | uivalent Input Circuit                                                       |     |

| 6.3         | -                            | ternal Circuit on ADC Input                                                  |     |

| 6.4         | EX                           |                                                                              | 92  |

| 7. D        | )eve                         | lopment and Test Tool Interface                                              | .54 |

| 7.1         | De                           | velopment Tool Interface of RH850/F1L Group                                  | 55  |

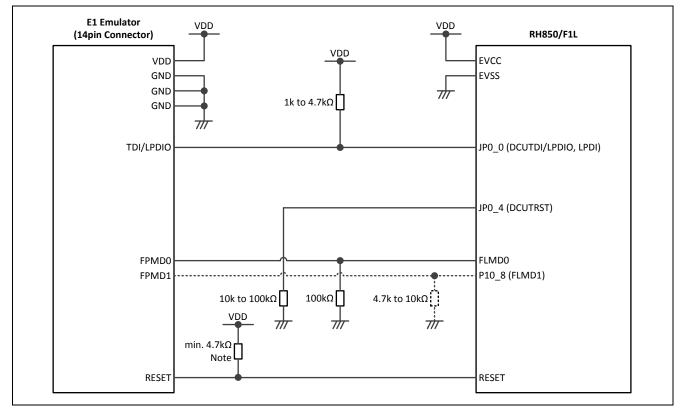

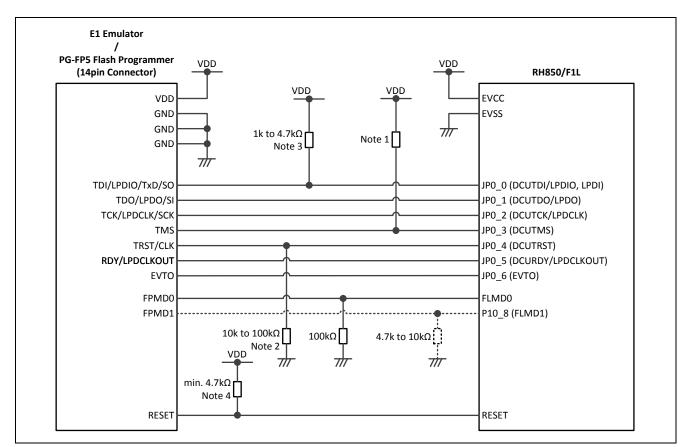

| 7.1         | 1.1                          | Debug Interface Connection of RH850/F1L Group                                | 55  |

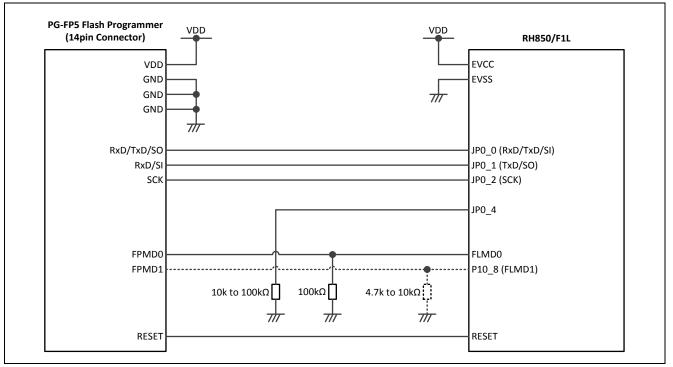

| 7.1         | 1.2                          | Flash Programming Interface Connection of RH850/F1L Group                    | 58  |

| 7.1         | 1.3                          | Combined Debug and Flash Programming Interface Connection of RH850/F1L Group | 60  |

| 7.2         | De                           | velopment Tool Interface of RH850/F1M Group                                  | 61  |

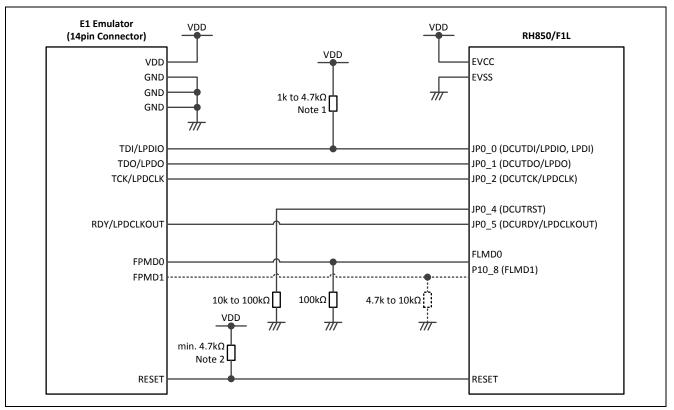

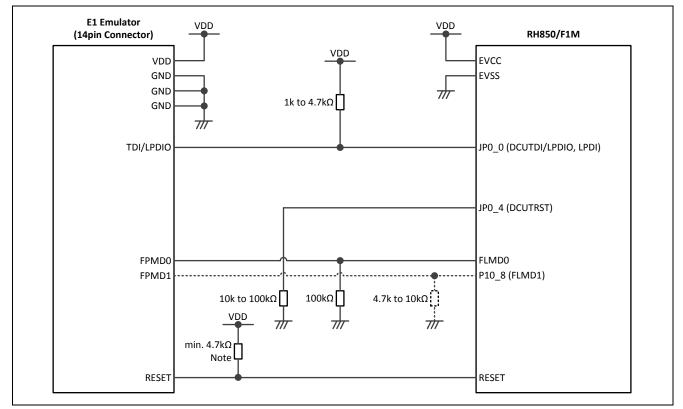

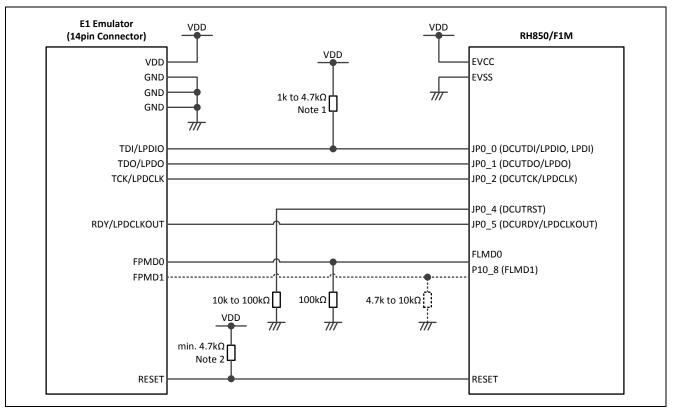

| 7.2         | 2.1                          | Debug Interface Connection of RH850/F1M Group                                | 61  |

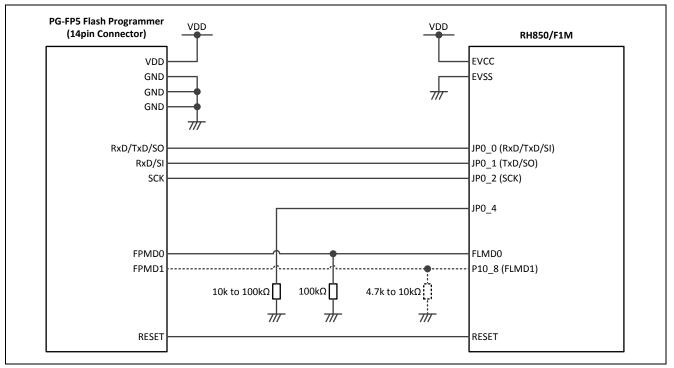

| 7.2         | 2.2                          | Flash Programming Interface Connection of RH850/F1M Group                    | 64  |

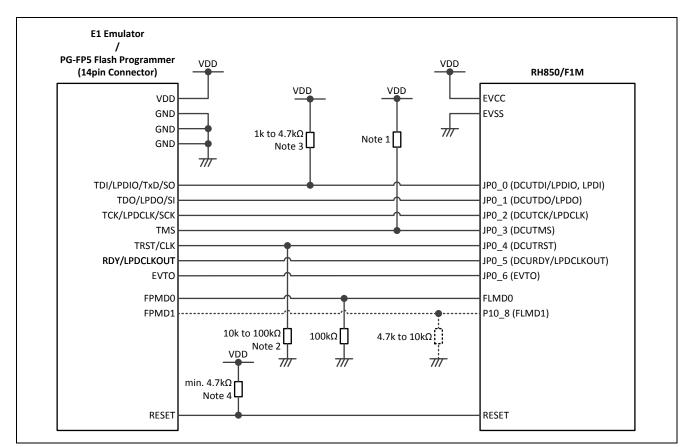

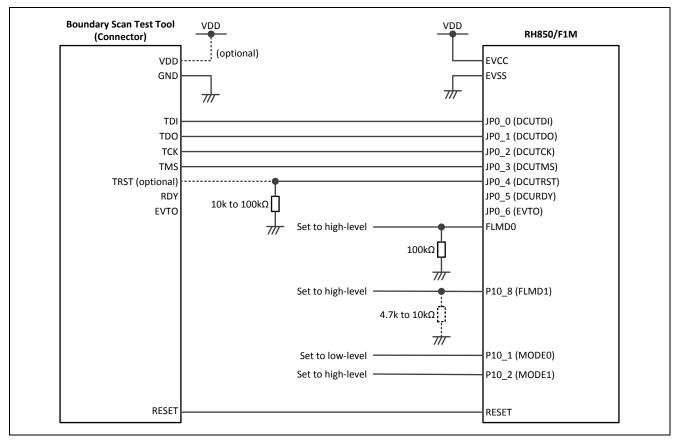

| 7.2         | 2.3                          | Combined Debug and Flash Programming Interface Connection of RH850/F1M Group | 66  |

| 7.3         | De                           | velopment Tool Interface of RH850/F1H Group                                  | 67  |

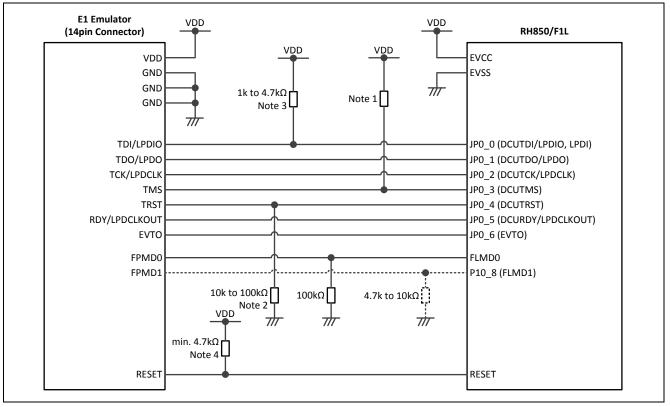

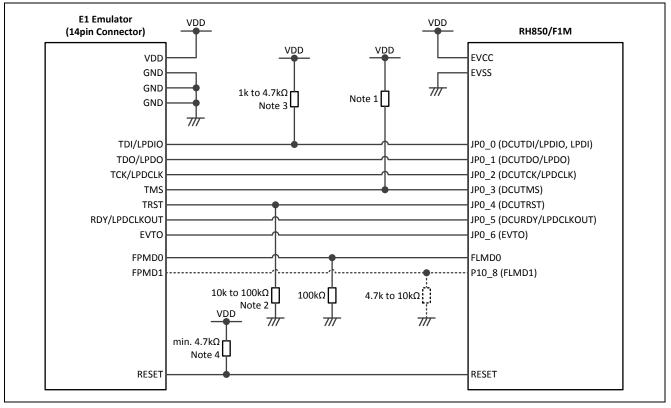

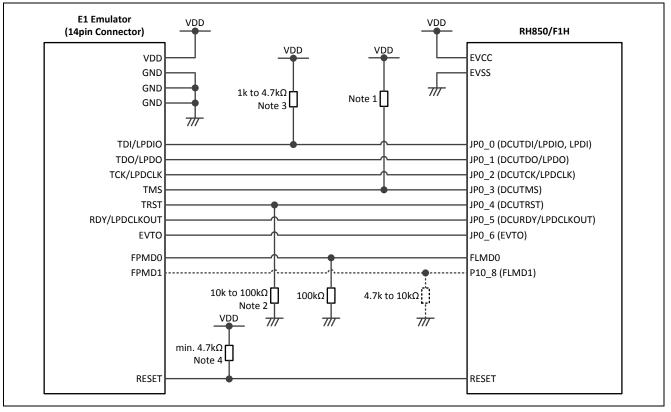

| 7.3         | 3.1                          | Debug Interface Connection of RH850/F1H Group                                | 67  |

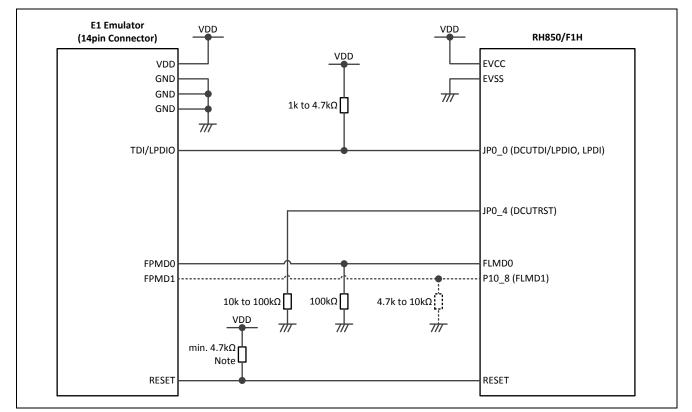

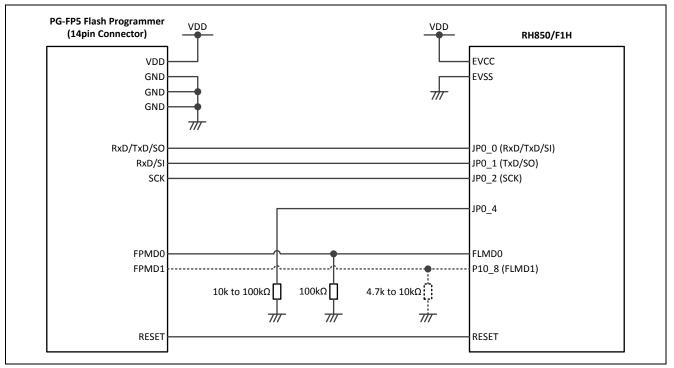

| 7.3         | 3.2                          | Flash Programming Interface Connection of RH850/F1H Group                    | 70  |

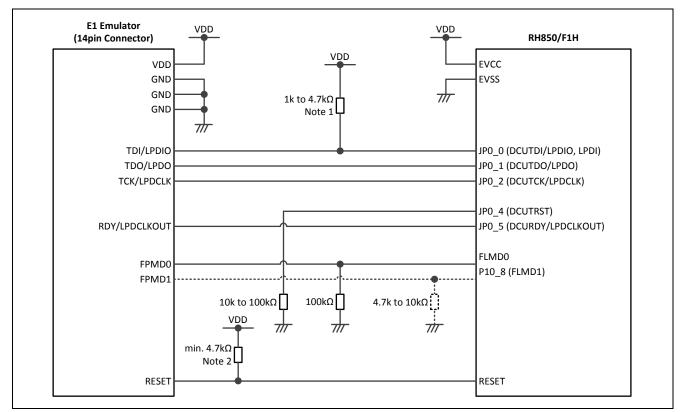

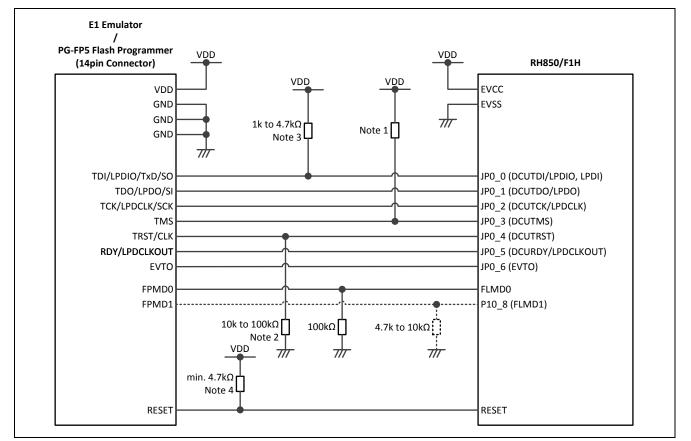

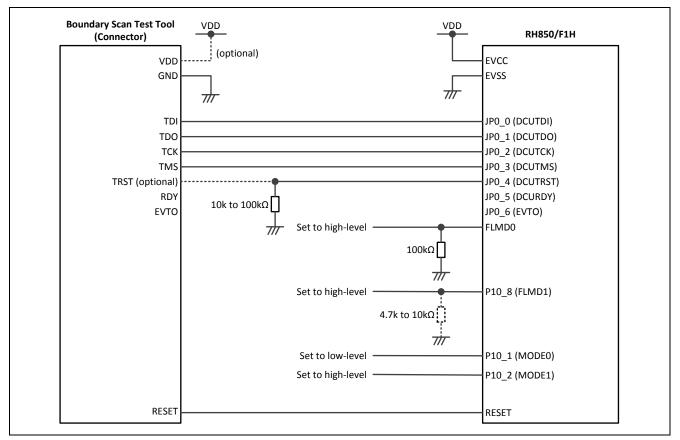

| 7.3         | 3.3                          | Combined Debug and Flash Programming Interface Connection of RH850/F1H Group | 72  |

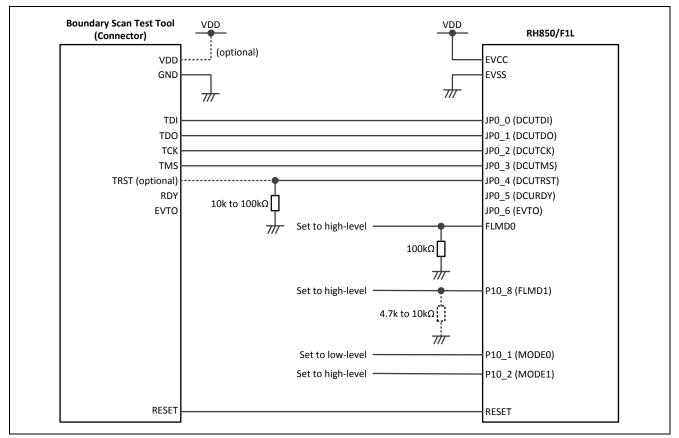

| 7.4         | Во                           | undary Scan Mode Interface of RH850/F1L Group                                | 73  |

| 7.5         | Во                           | undary Scan Mode Interface of RH850/F1M Group                                | 74  |

| 7.6         | Во                           | undary Scan Mode Interface of RH850/F1H Group                                | 75  |

| Wahe        | ite ·                        | and Support                                                                  | 76  |

| 11603       |                              |                                                                              |     |

| Revis       | ion                          | History                                                                      | 1   |

| Gene        | ral F                        | Precautions in the Handling of MPU/MCU Products                              | 6   |

## **Table of Figures**

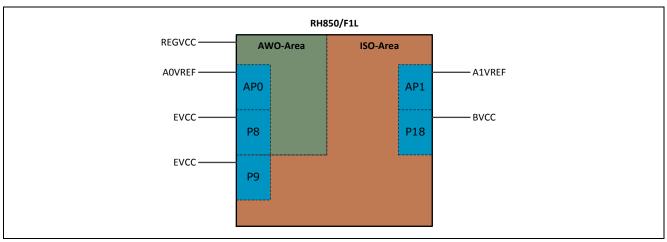

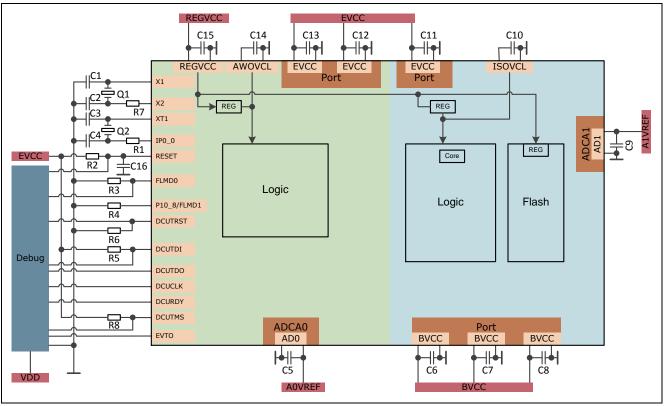

| Figure 1 RH850/F1L Power supply architecture                                                   | 9    |

|------------------------------------------------------------------------------------------------|------|

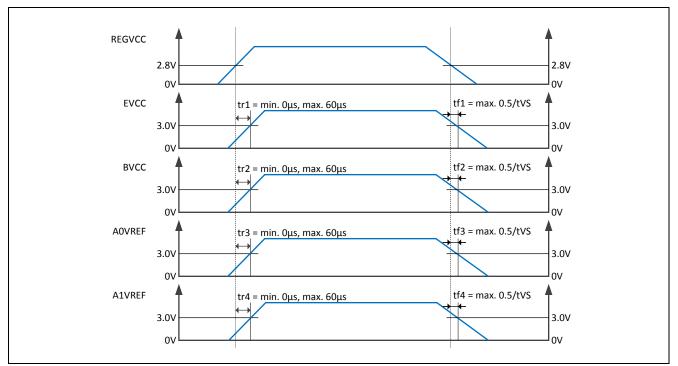

| Figure 2 RH850/F1L Power up/down timing                                                        | 12   |

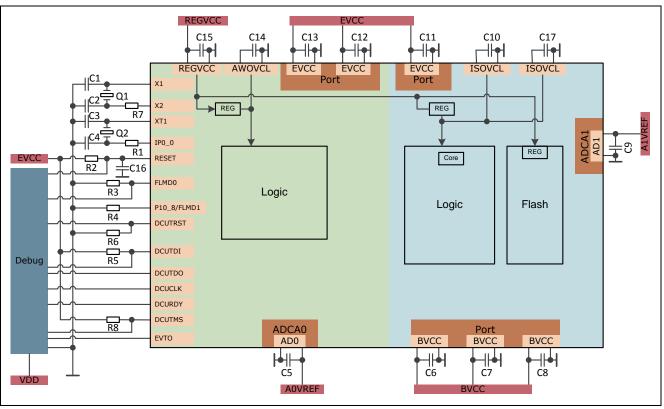

| Figure 3 RH850/F1M Power supply architecture                                                   | 14   |

| Figure 4 RH850/F1M Power up/down timing                                                        | 17   |

| Figure 5 RH950/F1H-272pin Power supply pin difference between mass production and debug device | 18   |

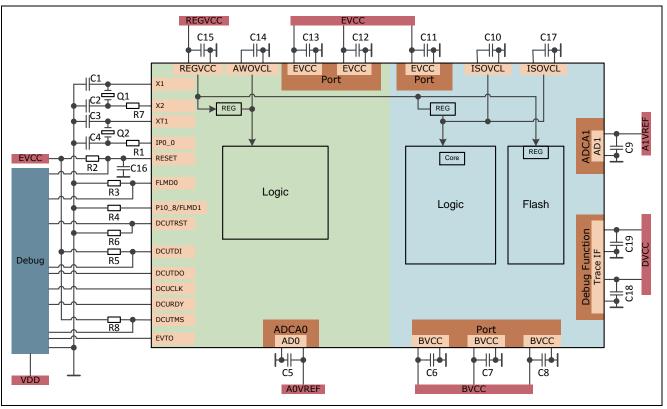

| Figure 6 RH850/F1H Power supply architecture                                                   | 19   |

| Figure 7 RH850/F1H Power up/down timing                                                        | 23   |

| Figure 8 Principle capacitor placement at REGVCC for EMI at data flash operation               | 24   |

| Figure 9 Minimum external components for RH850/F1L-176pin                                      | 25   |

| Figure 10 Minimum external components for RH850/F1M-233pin                                     | 28   |

| Figure 11 Minimum external components for RH850/F1H-272pin                                     | 30   |

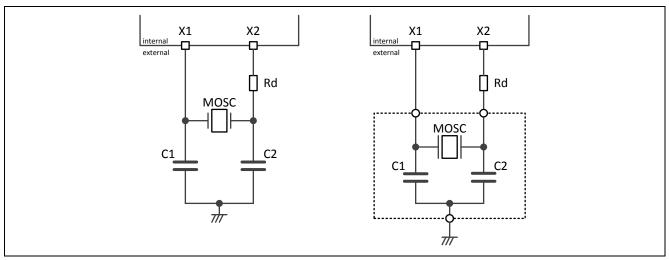

| Figure 12 Recommended main oscillator circuit                                                  | 33   |

| Figure 13 Recommended sub oscillator circuit                                                   | 34   |

| Figure 14 Minimum RESET circuit                                                                | 35   |

| Figure 15 External RESET timing                                                                | 36   |

| Figure 16 RESET Pin Input Behaviour at Power-on Clear                                          | 36   |

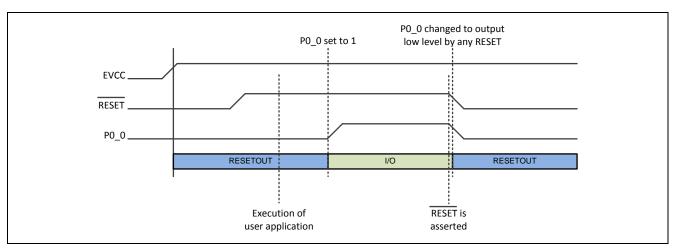

| Figure 17 RESETOUT pin behaviour                                                               | 37   |

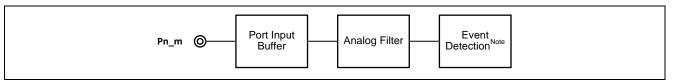

| Figure 18 Analog Filter Function                                                               | 38   |

| Figure 19 ADC conversion time                                                                  | 48   |

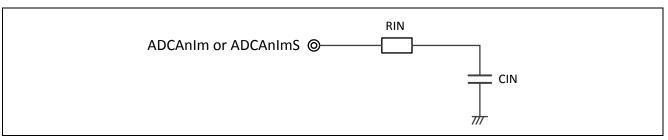

| Figure 20 ADC equivalent input circuit                                                         | 49   |

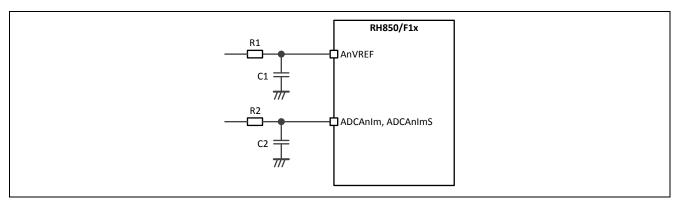

| Figure 21 ADC external circuit on analog input                                                 | . 52 |

| Figure 22 RH850/F1L 1pin Low-pin debug interface connection                                    | 55   |

| Figure 23 RH850/F1L 4pin Low-pin debug interface connection                                    | 56   |

| Figure 24 RH850/F1L Nexus, 4pin LPD and 1pin LPD debug interface connection                    | 57   |

| Figure 25 RH850/F1L PG-FP5 flash programming interface connection                              | . 59 |

| Figure 26 RH850/F1L Combined debug and flash programming interface connections                 | 60   |

| Figure 27 RH850/F1M 1pin Low-pin debug interface connection                                    | 61   |

| Figure 28 RH850/F1M 4pin Low-pin debug interface connection                                    | 62   |

| Figure 29 RH850/F1M Nexus, 4pin LPD and 1pin LPD debug interface connection                    | 63   |

| Figure 30 RH850/F1M PG-FP5 flash programming interface connection                              | 65   |

| Figure 31 RH850/F1M Combined debug and flash programming interface connections                 | 66   |

| Figure 32 RH850/F1H 1pin Low-pin debug interface connection                                    | 67   |

| Figure 33 RH850/F1H 4pin Low-pin debug interface connection                                    | 68   |

| Figure 34 RH850/F1H Nexus, 4pin LPD and 1pin LPD debug interface connection                    | 69   |

| Figure 35 RH850/F1H PG-FP5 flash programming interface connection                              | 71   |

| Figure 36 RH850/F1H Combined debug and flash programming interface connections                 | . 72 |

| Figure 37 Boundary scan connection of RH850/F1L Group                                          | 73   |

| Figure 38 Boundary scan connection of RH850/F1M Group                                          | 74   |

| RH850/F1x Series                                      | Hardware Design Guide |

|-------------------------------------------------------|-----------------------|

| Figure 39 Boundary scan connection of RH850/F1H Group |                       |

### 1. Reference Documents

This chapter contains information about the device reference documentation.

#### 1.1 User Manual

The user manual provides information about the functional behaviour of the device.

| RH850/F1L User's Manual: | R01UH0390EJxxxx |

|--------------------------|-----------------|

| RH850/F1M User's Manual: | R01UH0518EJxxxx |

| RH850/F1H User's Manual: | R01UH0445EJxxxx |

### 1.2 Data Sheet

The data sheet provides information about the electrical behaviour of the device.

| RH850/F1L (176 pin) Data Sheet: | R01DS0170EJxxxx |

|---------------------------------|-----------------|

| RH850/F1L (144 pin) Data Sheet: | R01DS0210EJxxxx |

| RH850/F1L (100 pin) Data Sheet: | R01DS0211EJxxxx |

| RH850/F1L (80 pin) Data Sheet:  | R01DS0212EJxxxx |

| RH850/F1L (64 pin) Data Sheet:  | R01DS0213EJxxxx |

| RH850/F1L (48 pin) Data Sheet:  | R01DS0214EJxxxx |

|                                 |                 |

| RH850/F1M Data Sheet :          | R01DS0250EJxxxx |

|                                 |                 |

| RH850/F1H Data Sheet:           | R01DS0234EJxxxx |

### 1.3 Operating Precaution

The operating precaution provides information about user's manual and data sheet differences and actual device implementations.

| RH850/F1L (176 pin) Operating Precaution: | R01TU0046EDxxxx |

|-------------------------------------------|-----------------|

| RH850/F1L (144 pin) Operating Precaution: | R01TU0051EDxxxx |

| RH850/F1L (100 pin) Operating Precaution: | R01TU0052EDxxxx |

| RH850/F1L (80 pin) Operating Precaution:  | R01TU0053EDxxxx |

| RH850/F1L (64 pin) Operating Precaution:  | R01TU0063EDxxxx |

| RH850/F1L (48 pin) Operating Precaution:  | R01TU0064EDxxxx |

|                                           |                 |

| RH850/F1M (233 pin) Operating Precaution: | R01TUxxxxEDxxxx |

| RH850/F1M (176 pin) Operating Precaution: | R01TU0077EDxxxx |

| RH850/F1M (144 pin) Operating Precaution: | R01TUxxxxEDxxxx |

|                                           |                 |

| RH850/F1H (272 pin) Operating Precaution  | R01TU0068EDxxxx |

| RH850/F1H (233 pin) Operating Precaution  | R01TU0076EDxxxx |

| RH850/F1H (176 pin) Operating Precaution  | R01TU0065EDxxxx |

|                                           |                 |

### 2. Power Supply

### 2.1 Power Supply Overview of RH850/F1L Group

### 2.1.1 Power Supply Pin Overview of RH850/F1L Group

The devices of the RH850/F1L group have the following power supply pins.

| Device           | Power Supply Pins          |

|------------------|----------------------------|

| RH850/F1L-176pin | REGVCC                     |

|                  | EVCC, EVSS                 |

|                  | BVCC, BVSS                 |

|                  | AnVREF, AnVSS $(n = 0, 1)$ |

| RH850/F1L-144pin | REGVCC                     |

|                  | EVCC, EVSS                 |

|                  | BVCC, BVSS                 |

|                  | AnVREF, AnVSS $(n = 0, 1)$ |

| RH850/F1L-100pin | REGVCC                     |

|                  | EVCC, EVSS                 |

|                  | A0VREF, A0VSS              |

| RH850/F1L-80pin  | REGVCC                     |

|                  | EVCC, EVSS                 |

|                  | A0VREF, A0VSS              |

| RH850/F1L-64pin  | REGVCC                     |

|                  | EVCC, EVSS                 |

|                  | A0VREF, A0VSS              |

| RH850/F1L-48pin  | REGVCC                     |

|                  | EVCC, EVSS                 |

|                  | A0VREF, A0VSS              |

The pins AWOVCL, AWOVSS and ISOVCL, ISOVSS are available on all devices to connect external capacitors.

### 2.1.2 Power Supply Pin Configuration of RH850/F1L Group

Depending on the device, the following power supply pin configuration applies:

The EVCC supply pins are internally connected.

The BVCC supply pins are internally connected.

### 2.1.3 Power Supply Pin Architecture of RH850/F1L Group

The RH850/F1L group supports different power supply architectures. The power supply architecture depends on the chosen RH850/F1L group device, application requirements and the use case.

Some common conditions apply to the supply of the RH850/F1L group:

- REGVCC = EVCC = VPOC to 5.5V

- BVCC = VPOC to REGVCC

- A0VREF = 3.0V to 5.5V

- A1VREF = 3.0V to 5.5V

- AWOVSS = ISOVSS = EVSS = BVSS = A0VSS = A1VSS = 0V

The following figure and the different cases describe the impact to the ADC ports and the ports with analog/digital function depending on the power supply architecture. In addition, it describes the limitations to these ports.

| Case 1 – Single Supply 5V |                                                   |  |

|---------------------------|---------------------------------------------------|--|

| Condition                 | REGVCC = 5V                                       |  |

|                           | EVCC = 5V                                         |  |

|                           | BVCC = 5V                                         |  |

|                           | A0VREF = 5V                                       |  |

|                           | A1VREF = 5V                                       |  |

| Port Function             | AP0 – Port usable with analog or digital function |  |

|                           | P8 – Port usable with analog or digital function  |  |

|                           | P9 – Port usable with analog or digital function  |  |

|                           | AP1 – Port usable with analog or digital function |  |

|                           | P18 – Port usable with analog or digital function |  |

| Limitation                | No limitation applies                             |  |

| →                         | Operation permitted                               |  |

#### Case 2 – Single Supply 3.3V Condition REGVCC = 3.3V EVCC = 3.3VBVCC = 3.3VA0VREF = 3.3VA1VREF = 3.3VPort Function AP0 - Port usable with analog or digital function P8 - Port usable with analog or digital function P9 - Port usable with analog or digital function - Port usable with analog or digital function AP1 P18 - Port usable with analog or digital function Limitation No limitation applies Operation permitted $\rightarrow$

| Case 3 – Mixed Supply 5V & 3.3V |                                                                         |  |

|---------------------------------|-------------------------------------------------------------------------|--|

| Condition                       | REGVCC = 5V                                                             |  |

|                                 | EVCC = 5V                                                               |  |

|                                 | BVCC = 3.3V                                                             |  |

|                                 | A0VREF = 5V                                                             |  |

|                                 | A1VREF = 5V                                                             |  |

| Port Function                   | AP0 – Port usable with analog or digital function                       |  |

|                                 | P8 – Port usable with analog or digital function                        |  |

|                                 | P9 – Port usable with analog or digital function                        |  |

|                                 | AP1 – Port usable with analog or digital function                       |  |

|                                 | P18 – Port usable with analog or digital function, analog input voltage |  |

|                                 | limited to max. 3.3V, reduced AD conversion range between 0V to 3.3V    |  |

| Limitation                      | Analog port function limitation applies to P18                          |  |

| $\rightarrow$                   | Operation permitted                                                     |  |

| Case 4 – Mixed Supply 5V & 3.3V |                                                   |  |

|---------------------------------|---------------------------------------------------|--|

| Condition                       | REGVCC = 5V                                       |  |

|                                 | EVCC = 3.3V                                       |  |

|                                 | BVCC = 3.3V                                       |  |

|                                 | A0VREF = 5V                                       |  |

|                                 | A1VREF = 5V                                       |  |

| Port Function                   | AP0 – Port usable with analog or digital function |  |

|                                 | P8 – Port usable with analog or digital function  |  |

|                                 | P9 – Port usable with analog or digital function  |  |

|                                 | AP1 – Port usable with analog or digital function |  |

|                                 | P18 – Port usable with analog or digital function |  |

| Limitation                      | Common condition REGVCC = EVCC not met            |  |

| →                               | Operation not permitted                           |  |

| Case 5 – Mixed Supply 5V & 3.3V |                                                                         |  |

|---------------------------------|-------------------------------------------------------------------------|--|

| Condition                       | REGVCC = 3.3V                                                           |  |

|                                 | EVCC = 3.3V                                                             |  |

|                                 | BVCC = 3.3V                                                             |  |

|                                 | A0VREF = 5V                                                             |  |

|                                 | A1VREF = 5V                                                             |  |

| Port Function                   | AP0 – Port usable with analog or digital function                       |  |

|                                 | P8 – Port usable with analog or digital function, analog input voltage  |  |

|                                 | limited to max. 3.3V, reduced AD conversion range between 0V to 3.3V    |  |

|                                 | P9 – Port usable with analog or digital function, analog input voltage  |  |

|                                 | limited to max. 3.3V, reduced AD conversion range between 0V to 3.3V    |  |

|                                 | AP1 – Port usable with analog or digital function                       |  |

|                                 | P18 – Port usable with analog or digital function, analog input voltage |  |

|                                 | limited to max. 3.3V, reduced AD conversion range between 0V to 3.3V    |  |

|                                 |                                                                         |  |

|                                 | Analog input channel on APO, Analog input channel on P8, P9,            |  |

|                                 | AP1 P18<br>→ Reduced AD conversion range                                |  |

|                                 | A A A A A A A A A A A A A A A A A A A                                   |  |

|                                 |                                                                         |  |

|                                 | 5V 3FFh 5V                                                              |  |

|                                 | 3.3V 3.3V 2A3h                                                          |  |

|                                 |                                                                         |  |

|                                 |                                                                         |  |

|                                 |                                                                         |  |

|                                 | Note: Conversion range example based on 10-bit ADC resolution           |  |

| Limitation                      | Analog port function limitation applies to P8, P9 and P18               |  |

| $\rightarrow$                   | Operation permitted                                                     |  |

| Case 6 – Mixed Supply 5V & 3.3V |                                                                      |  |

|---------------------------------|----------------------------------------------------------------------|--|

| Condition                       | REGVCC = 3.3V                                                        |  |

|                                 | EVCC = 3.3V                                                          |  |

|                                 | BVCC = 3.3V                                                          |  |

|                                 | A0VREF = 5V                                                          |  |

|                                 | A1VREF = 5V                                                          |  |

| Port Function                   | AP0 – Port usable with analog or digital function                    |  |

|                                 | P8 – Port usable with digital function only                          |  |

|                                 | P9 – Port usable with digital function only                          |  |

|                                 | AP1 – Port usable with analog or digital function                    |  |

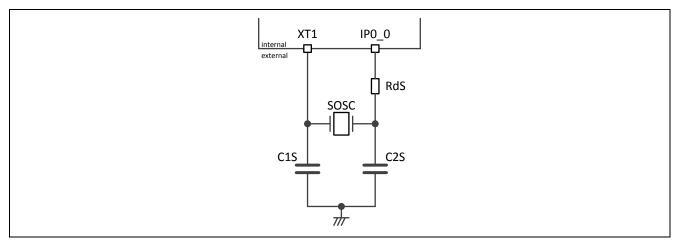

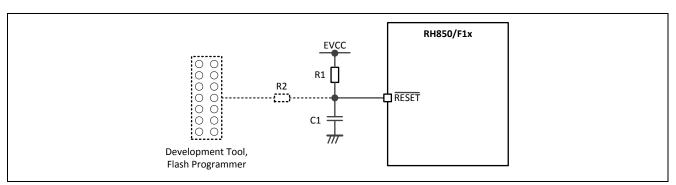

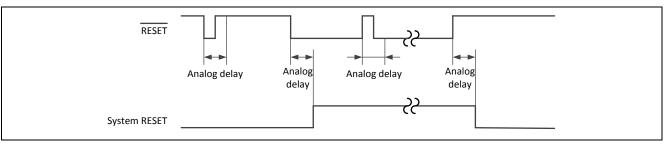

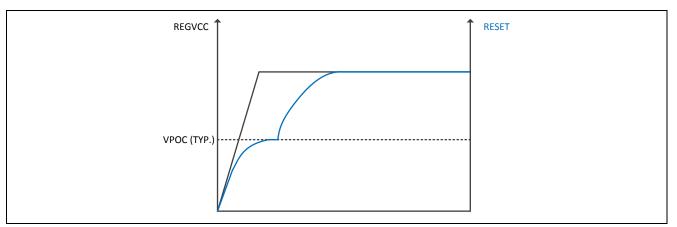

|                                 | P18 – Port usable with digital function only                         |  |