# APPLICATION NOTE

# RZ/T1 Group

Example of Downloading to Serial Flash Memory by Using "Semihosting" of ARM<sup>®</sup> Development Studio 5 (DS-5<sup>TM</sup>)

R01AN2951EJ0120 Rev.1.20 Sep. 15, 2017

# Summary

This application note presents a method for downloading programs to the serial flash memory allocated to the external address space (SPI multi-I/O bus space) of an RZ/T1 group microcontroller.

Note that the method of downloading described in this application note utilizes the "semihosting" (file operation) functionality of ARM<sup>®</sup> Development Studio 5 (DS-5<sup>TM</sup>, hereafter abbreviated as DS-5). You will need to obtain DS-5 separately. For details of the semihosting functionality of DS-5, refer to the documentation\*<sup>1</sup> provided by ARM<sup>®</sup>.

Note 1. Refer to "ARM® Compiler toolchain Developing Software for ARM® Processors, Semihosting" for details.

# **Applicable Devices**

RZ/T1 Group

When applying the program covered in this application note to another microcontroller, modify the program according to the specifications for the target microcontroller and conduct an extensive evaluation of the modified program.

# Table of Contents

| 1. | Speci  | fications                                                             | 4  |

|----|--------|-----------------------------------------------------------------------|----|

| 2. | Cond   | itions for Checking Operations                                        | 5  |

| 3. | Relate | ed Application Notes                                                  | 6  |

| 4. | Desci  | iption of Hardware                                                    | 7  |

|    | 4.1    | List of Pins                                                          | 7  |

|    | 4.2    | Reference Circuit                                                     |    |

| 5. | Outlin | e of Downloading to the Serial Flash Memory                           | 9  |

|    | 5.1    | Terms Related to Downloading to the Serial Flash Memory               | 9  |

|    | 5.2    | Schematic View of Flash Downloader Operation                          | 10 |

|    | 5.3    | Developing a Flash Downloader                                         | 11 |

|    | 5.3.1  | Memory Map                                                            | 12 |

|    | 5.4    | Customizing the Examples of Downloading to the Serial Flash Memory    | 13 |

| 6. | Exam   | ple of Downloading to the RZ/T1 Evaluation Board (RTK7910022C00000BR) | 14 |

|    | 6.1    | Settings for the RZ/T1 Evaluation Board (RTK7910022C00000BR)          | 15 |

|    | 6.2    | Copying DS-5 Scripts                                                  | 15 |

|    | 6.3    | Importing and Building Projects                                       | 16 |

|    | 6.4    | Generating Application Binary Files                                   | 17 |

|    | 6.5    | Copying the Flash Downloader Executable File                          | 18 |

|    | 6.6    | DS-5 Debug Configuration Settings                                     | 18 |

|    | 6.7    | Connecting the RZ/T1 Evaluation Board with an ARM® Emulator           | 19 |

|    | 6.8    | Running the Download Script                                           | 20 |

| 7. | Flash  | Memory Interface Functions                                            | 21 |

|    | 7.1    | Fixed-Width Integers                                                  | 21 |

|    | 7.2    | Structures and Unions                                                 | 21 |

|    | 7.3    | Constants                                                             |    |

|    | 7.4    | Variables                                                             | 31 |

|    | 7.5    | Flash Memory Interface Functions                                      | 31 |

|    | 7.6    | Details of the Flash Memory Interface Functions                       | 34 |

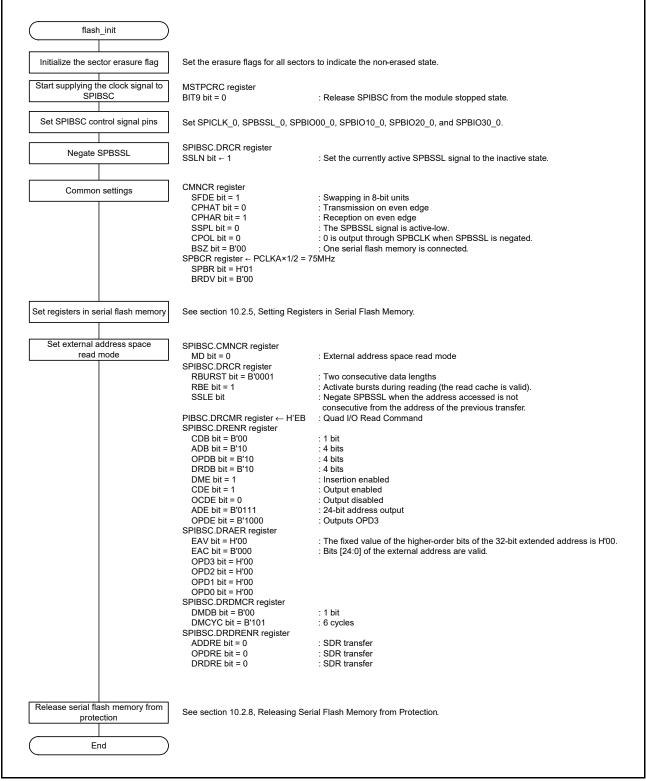

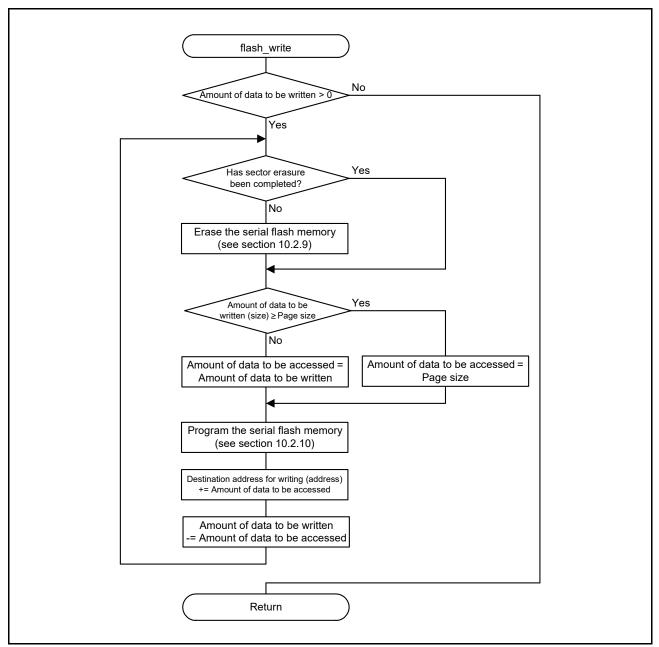

|    | 7.7    | Flowcharts of the Flash Memory Interface Functions                    | 42 |

|    | 7.7.1  | Flow of the Initialization Interface Function                         | 42 |

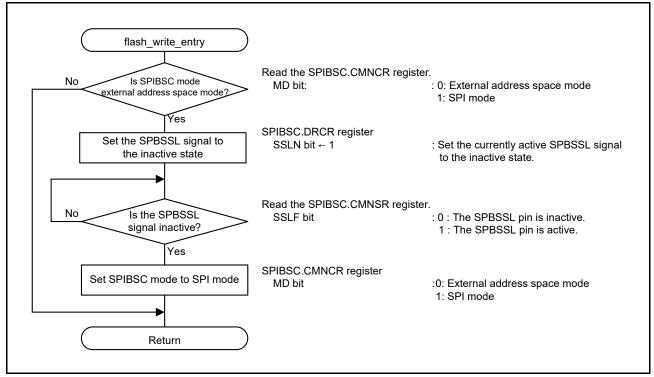

|    | 7.7.2  | Serial Flash Memory Write Mode Entry Function                         | 43 |

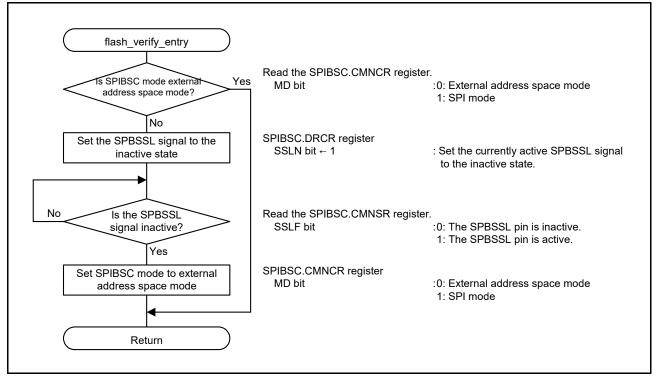

|    | 7.7.3  | Serial Flash Memory Read Mode Entry Function                          | 44 |

|    | 7.7.4  | Flow of the Write Interface Function                                  | 45 |

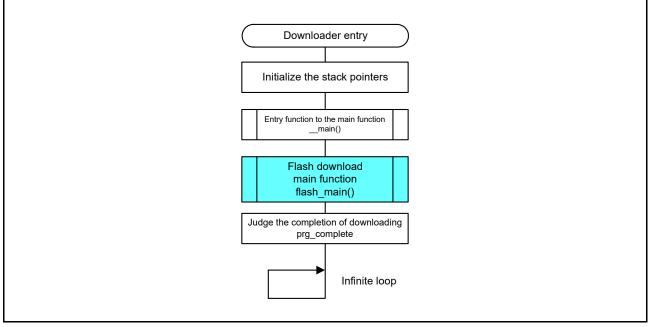

| 8. | Opera  | ation of the Flash Downloader                                         | 46 |

|    | 8.1    | Memory Allocation of the Application Program                          | 46 |

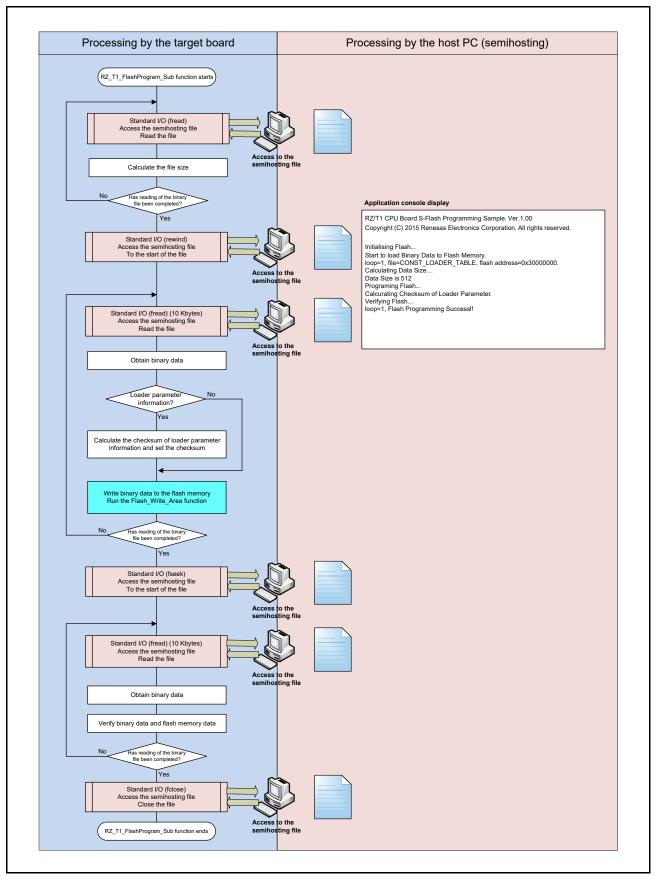

|    | 8.2    | Flow of Flash Downloader Processing                                   | 47 |

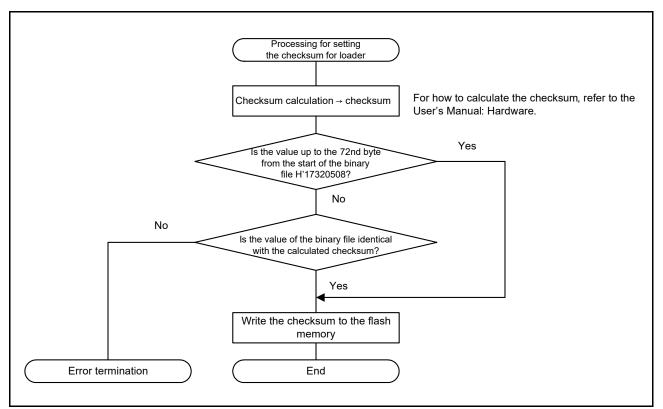

|    | 8.2.1  | Calculating the Checksum of the Loader Parameter Information          | 50 |

| 9. | Config | guration of the Flash Downloader                                      | 51 |

|    | 9.1    | Configuration of Projects                                             | 51 |

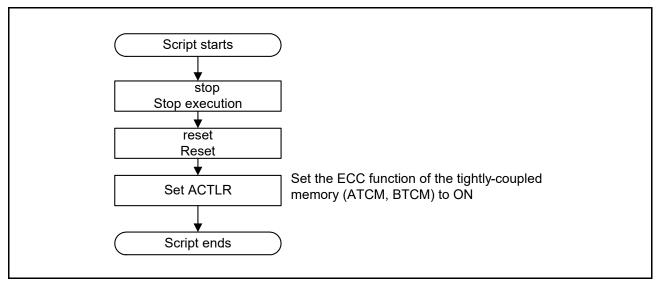

|     | 9.2    | RZ/T1 Evaluation Board Initialization Script                                                                           | 52 |

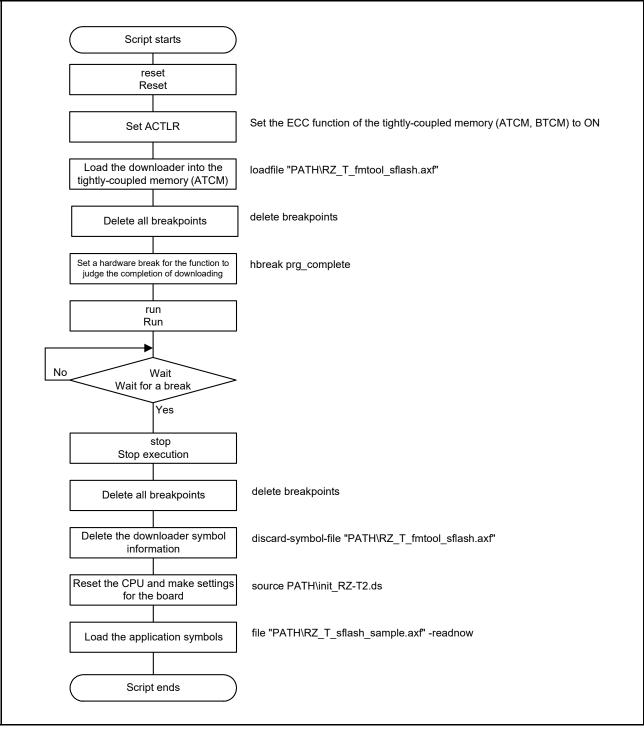

|-----|--------|------------------------------------------------------------------------------------------------------------------------|----|

|     | 9.3    | Application Downloading Script                                                                                         | 53 |

| 10. | Applic | ation Examples                                                                                                         | 54 |

|     | 10.1   | Changing the Binary File Names and Destination Addresses for Writing                                                   | 54 |

|     | 10.1.  | Changing the Binary File Names for Writing to the Flash Memory                                                         | 54 |

|     | 10.1.  | 2 Changing the Destination Addresses for Writing to the Flash Memory                                                   | 56 |

|     | 10.2   | Changing the Sample Program to Suit the Given Flash Memory                                                             | 58 |

|     | 10.2.  | Conditions for the Sample Program                                                                                      | 58 |

|     | 10.2.  | 2 Changing the Sample Program when Not Changing the Serial Flash Memory                                                | 58 |

|     | 10.2.  | Changing the Sample Program when Changing the Serial Flash Memory                                                      | 59 |

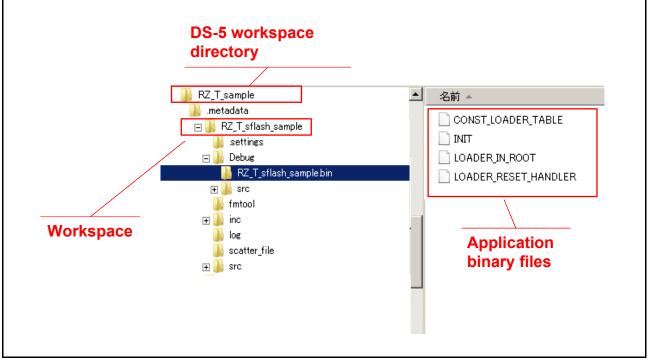

|     | 10.2.  | Changing the Read Command Waveforms                                                                                    | 59 |

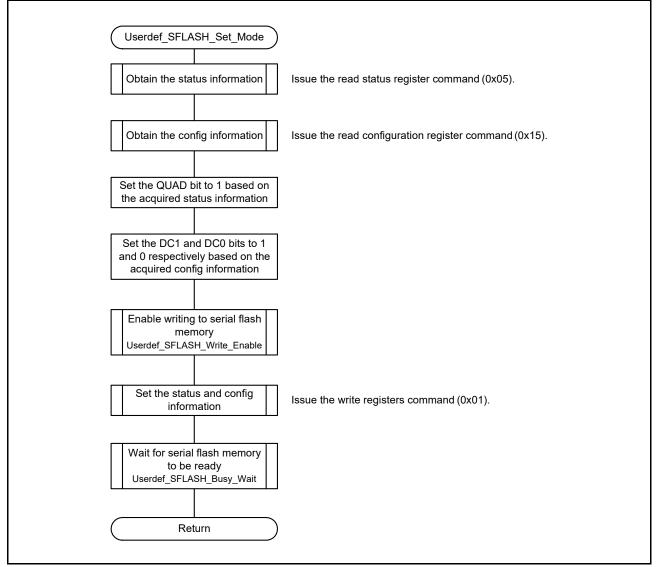

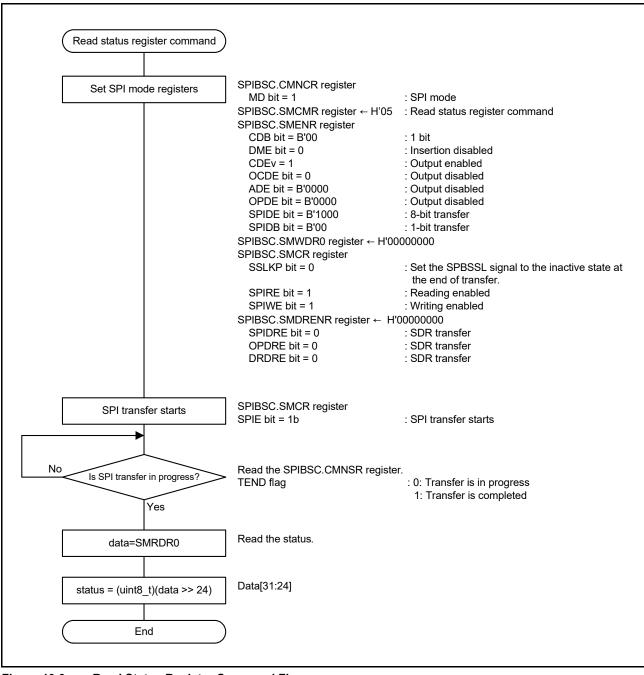

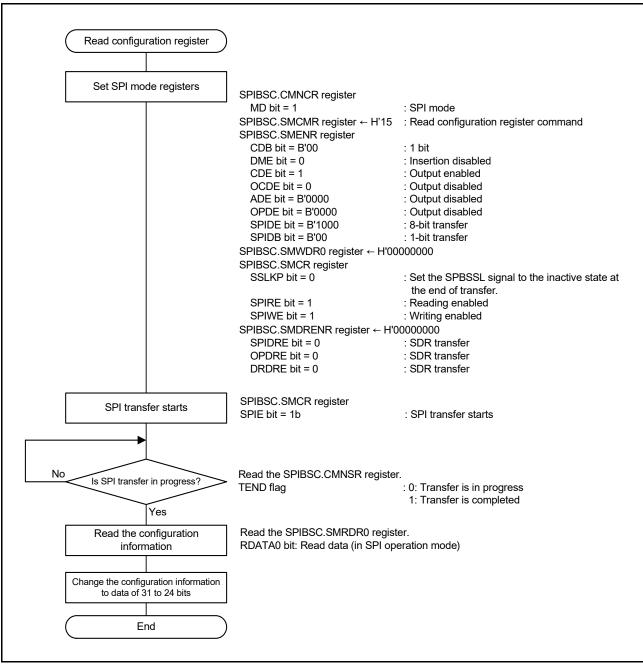

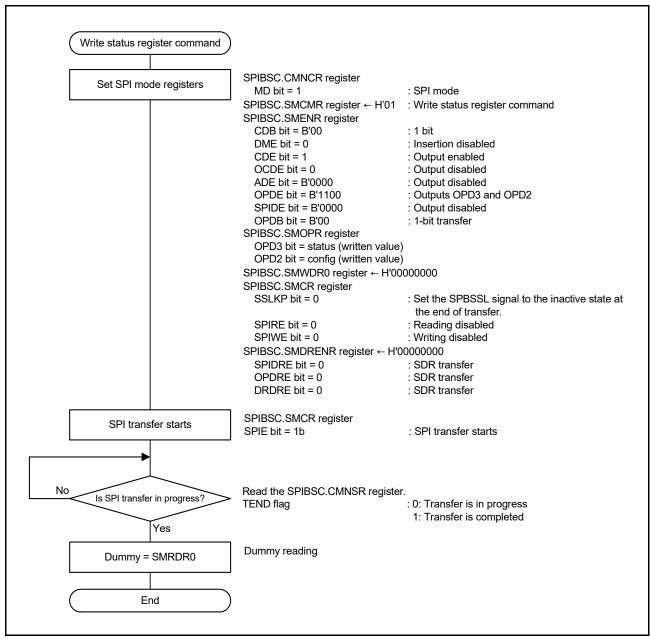

|     | 10.2.  | Setting Registers in the Serial Flash Memory                                                                           | 61 |

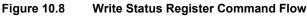

|     | 10.2.  | Enabling Writing to the Serial Flash Memory                                                                            | 65 |

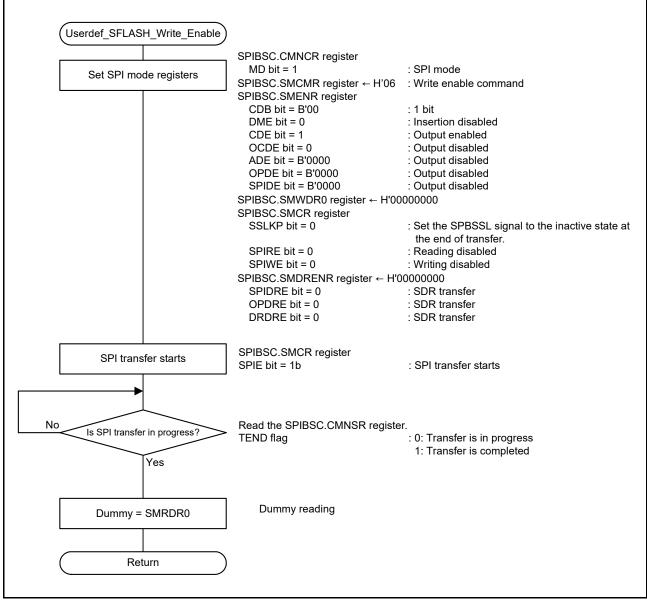

|     | 10.2.  | Waiting for the Serial Flash Memory to be Ready                                                                        | 66 |

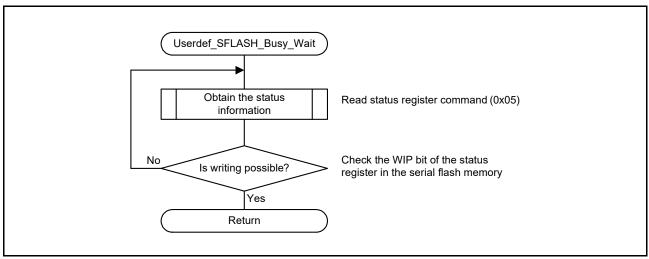

|     | 10.2.  | Releasing the Serial Flash Memory from Protection                                                                      | 67 |

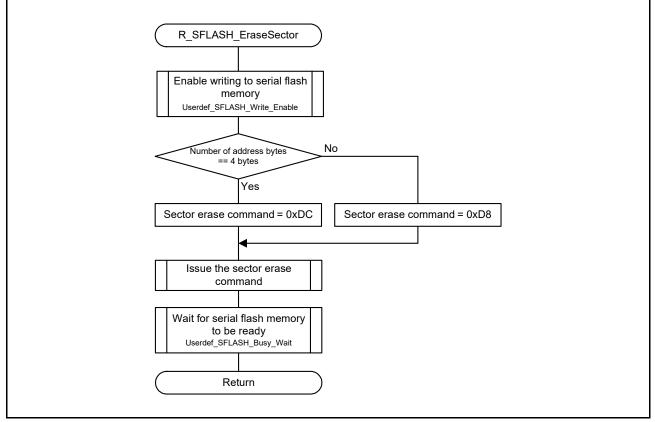

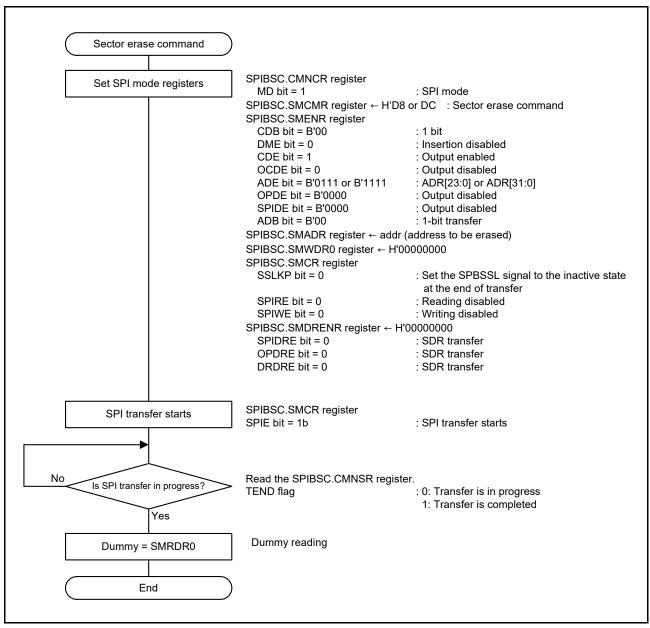

|     | 10.2.  | Erasing the Serial Flash Memory                                                                                        | 68 |

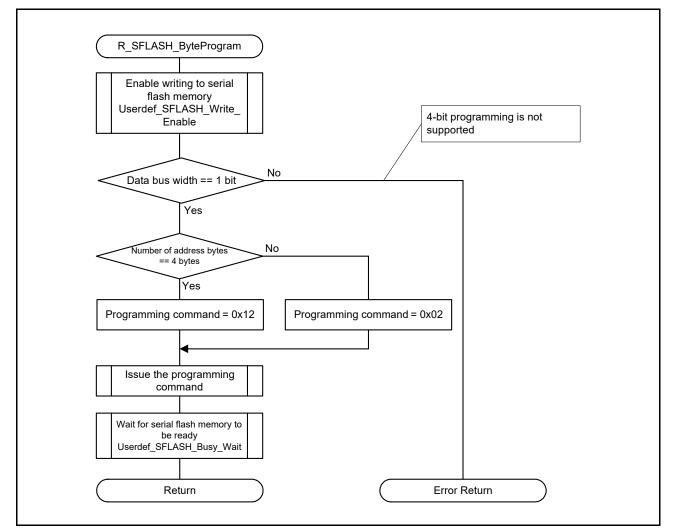

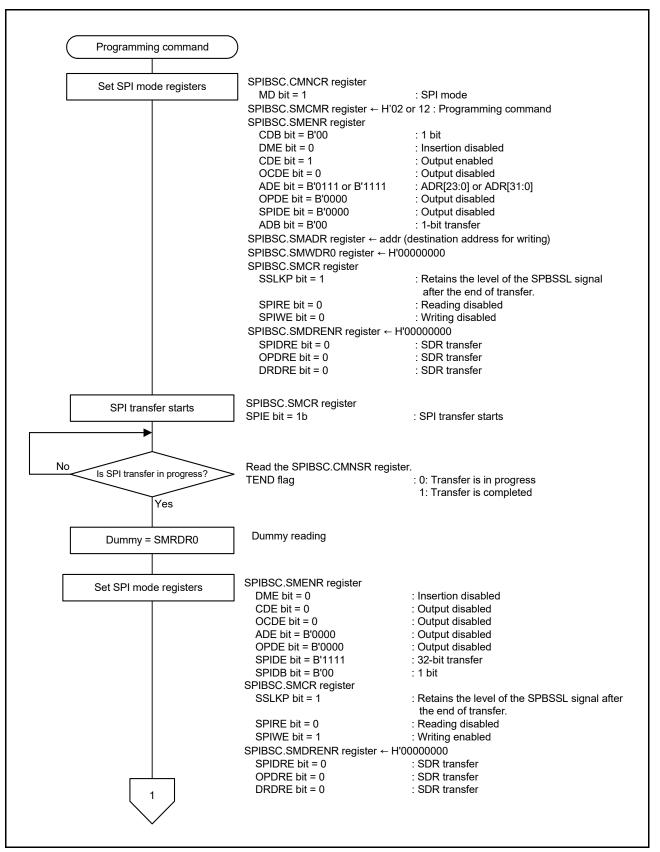

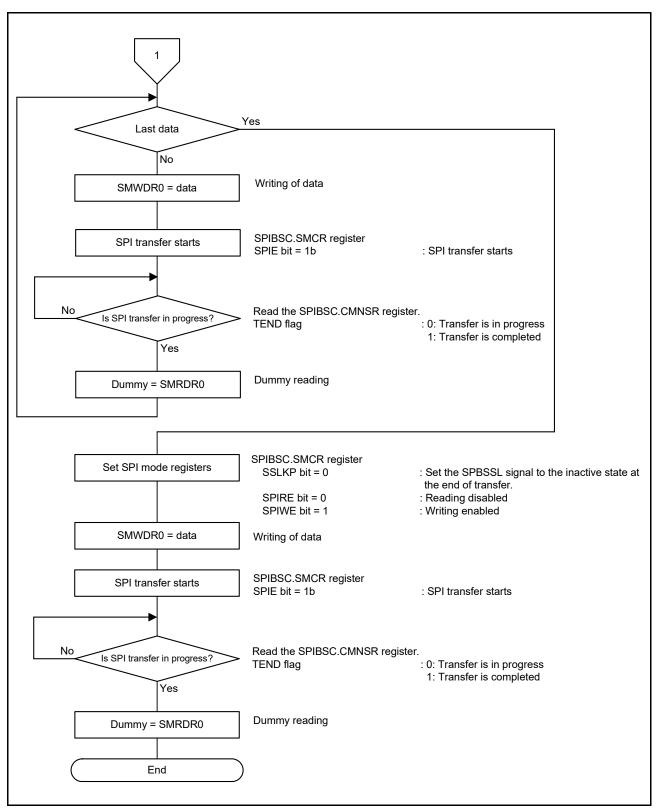

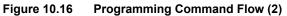

|     | 10.2.  | 0 Programming the Serial Flash Memory                                                                                  | 70 |

|     | 10.3   | Customizing the Sample Program for Initial Settings of the Microcomputers<br>Incorporating the R-IN Engine (Cortex-M3) | 73 |

| 11. | Samp   | e Program                                                                                                              | 75 |

| 12. | Docur  | nents for Reference                                                                                                    | 76 |

# 1. Specifications

The serial flash memory is a type of nonvolatile memory typically used to store program codes and data. Writing to the serial flash memory requires an appropriate algorithm for the serial flash memory in use. This application note presents such an algorithm as a C-language program that runs in the tightly-coupled memory (specifically, the ATCM) of an RZ/A1H group microcontroller. It also describes how to use the semihosting functionality of DS-5 to refer to binary files for SPIBSC initial settings and for applications<sup>\*1</sup> which are stored on the hard disk of the host computer on which DS-5 is running, and to write them to the serial flash memory.

Table 1.1 lists the peripheral modules used and their applications.

Note 1. See Table 5.1 for details of binary files for SPIBSC initial settings and for applications.

Table 1.1

Peripheral Modules and Their Applications

| Peripheral Module                                                                          | Application                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SPI multi-I/O bus controller (SPIBSC)                                                      | <ul> <li>This is used to generate signals for use in access to the serial flash memory<br/>connected to the external address space (SPI multi-I/O bus space).</li> </ul>                                                                                                                                                                                                                                                  |  |

| ARM <sup>®</sup> Development Studio 5 (DS-5 <sup>TM</sup> )<br>"semihosting" functionality | <ul> <li>Semihosting is used to have code running on the target (the program running on the board) handle transfer to and from the I/O functions of the host computer on which the debugger is running.</li> <li>This is used to refer to the terminal output from the target to the application console of DS-5 and to the handling of application binary files stored on the hard disk of the host computer.</li> </ul> |  |

# 2. Conditions for Checking Operations

Operation of the sample program covered in this application note has been confirmed under the conditions below.

| Table 2.1 | <b>Conditions for Checking Operations</b> |

|-----------|-------------------------------------------|

|-----------|-------------------------------------------|

| ltem                                                | Description                                                                                                                                                                                             |

|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MCU used                                            | RZ/T1 Group                                                                                                                                                                                             |

| Operating frequency                                 | CPUCLK = 450 MHz, PCLKA = 150 MHz                                                                                                                                                                       |

| Operating voltage                                   | 3.3 V                                                                                                                                                                                                   |

| Integrated development environment                  | DS-5 Version 5.25.0 from ARM®                                                                                                                                                                           |

| Operating mode                                      | SPI boot mode (serial flash memory)                                                                                                                                                                     |

| Board used                                          | RZ/T1 evaluation board (RTK7910022C00000BR)                                                                                                                                                             |

| Devices used<br>(functions to be used on the board) | Serial flash memory allocated to the SPI multi-I/O bus space (1- or 4-bit bus width) <ul> <li>Manufacturer: Macronix International Co., Ltd.</li> <li>Product type number: MX25L51245GMI-10G</li> </ul> |

# 3. Related Application Notes

The application notes related to the descriptions in this application note are listed below. Also consult the following documents along with this application note.

- RZ/T1 Group Initial Settings (R01AN2554EJ)

- RZ/T1 Group Initial Settings of the Microcomputers Incorporating the R-IN Engine (R01AN2989EJ)

# 4. Description of Hardware

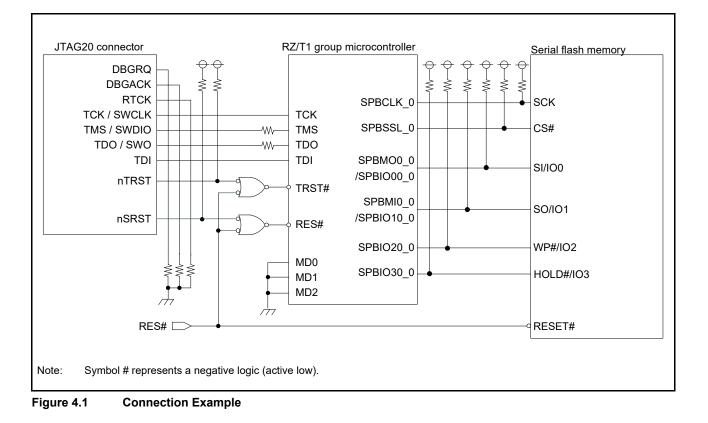

#### 4.1 List of Pins

Table 4.1 lists the pins used and their functions.

| Table 4.1 Pins Used and Their F | Functions |

|---------------------------------|-----------|

|---------------------------------|-----------|

| Pin Name            | I/O    | Description                                                                       |

|---------------------|--------|-----------------------------------------------------------------------------------|

| SPBCLK_0            | Output | Clock output                                                                      |

| SPBSSL_0            | Output | Slave select                                                                      |

| SPBMO0_0/SPBIO00_0  | I/O    | Master send data: data 0                                                          |

| SPBMI0_0/SPBIO10_0  | I/O    | Master input data: data 1                                                         |

| SPBIO20_0           | I/O    | Data 2                                                                            |

| SPBIO30_0           | I/O    | Data 3                                                                            |

| MD2,<br>MD1,<br>MD0 | Input  | Selection of boot mode (set to SPI boot mode)<br>MD2: "L"<br>MD1: "L"<br>MD0: "L" |

| ТСК                 | Input  | Clock input from the ARM <sup>®</sup> emulator                                    |

| TMS                 | Input  | Mode selection from the ARM <sup>®</sup> emulator                                 |

| TRST#               | Input  | Reset input from the ARM <sup>®</sup> emulator                                    |

| TDI                 | Input  | Data input from the ARM <sup>®</sup> emulator                                     |

| TDO                 | Output | Data output to the ARM <sup>®</sup> emulator                                      |

| RES#                | Input  | System reset signal                                                               |

Note: Symbol # represents a negative logic (or active low).

# 4.2 Reference Circuit

Figure 4.1 is a connection example.

# 5. Outline of Downloading to the Serial Flash Memory

This section gives an outline of downloading to the serial flash memory.

#### 5.1 Terms Related to Downloading to the Serial Flash Memory

Table 5.1 lists the terms related to downloading to the serial flash memory that are used in this application note.

| Table 5.1 | Terms Related to Downloading to the Serial Flash Memory |

|-----------|---------------------------------------------------------|

|-----------|---------------------------------------------------------|

| Term                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Application program      | The application program is a program which is created by the customer to suit the system.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Flash downloader         | The flash downloader is a program for writing the SPI multi-I/O bus controller initial settings<br>program and application program to the serial flash memory. Customers should use this<br>application note for reference and create flash downloader programs to match their systems.                                                                                                                                                                                                                                 |

| Semihosting              | Semihosting is a mechanism where I/O request code running on an ARM <sup>®</sup> CPU uses the I/O functions of DS-5 through transfer to and from a debugger.<br>Running standard C language functions such as printf, scanf, etc. on the ARM <sup>®</sup> CPU allows I/O processing on the screen and keyboard of the host PC through the I/O functions of DS-5 rather than through the I/O functions in the ARM <sup>®</sup> CPU on the target system.<br>For details, see the document provided by ARM <sup>®</sup> . |

| Application project      | This project is used to generate an application program executable file (axf file) in DS-5.<br>The application program includes parameter information for the loader to be referred to by the<br>RZ/T1 group microcontroller and the loader program itself.                                                                                                                                                                                                                                                             |

| Flash downloader project | This project is used to generate a flash downloader executable file (axf file) in DS-5.<br>The application program includes parameter information for the loader to be referred to by the RZ/T1 group microcontroller and the loader program itself.                                                                                                                                                                                                                                                                    |

| Application binary file  | The application binary file is a data file containing the application program to be written to the serial flash memory. A binary file generator tool (fromelf.exe) <sup>*1</sup> is used to generate this file from the application program executable file (axf file) that is generated when the application project is built in DS-5.                                                                                                                                                                                 |

Note 1. The binary file generator tool is included in DS-5. For details, see "ARM® DS-5<sup>TM</sup> DS-5 Getting Started Guide, ARM DS-5 Product Overview" provided by ARM®.

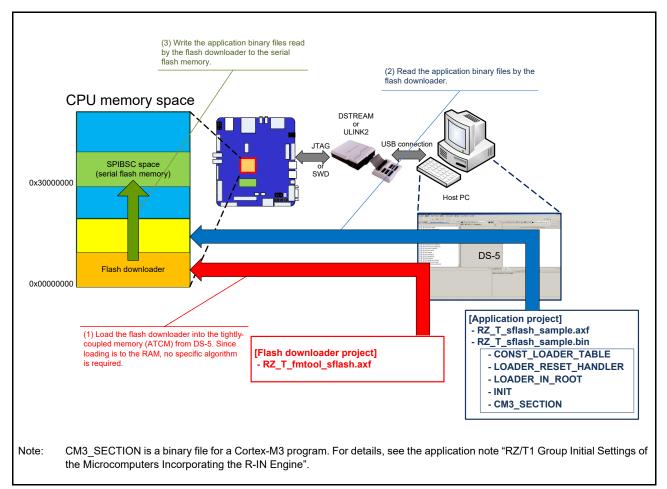

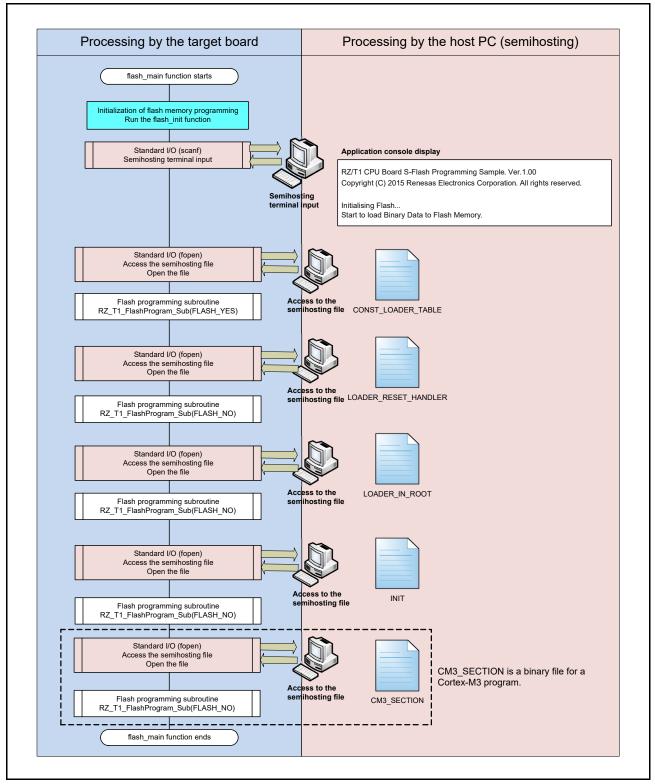

# 5.2 Schematic View of Flash Downloader Operation

Figure 5.1 is a schematic view of the operation of the flash downloader. The flash downloader runs in the tightlycoupled memory (ATCM) of the RZ/T1 group microcontroller; it uses semihosting to refer to the application binary files stored on the hard disk of the host computer on which DS-5 is running and to write them to the serial flash memory.

Figure 5.1 Schematic View of Flash Downloader Operation

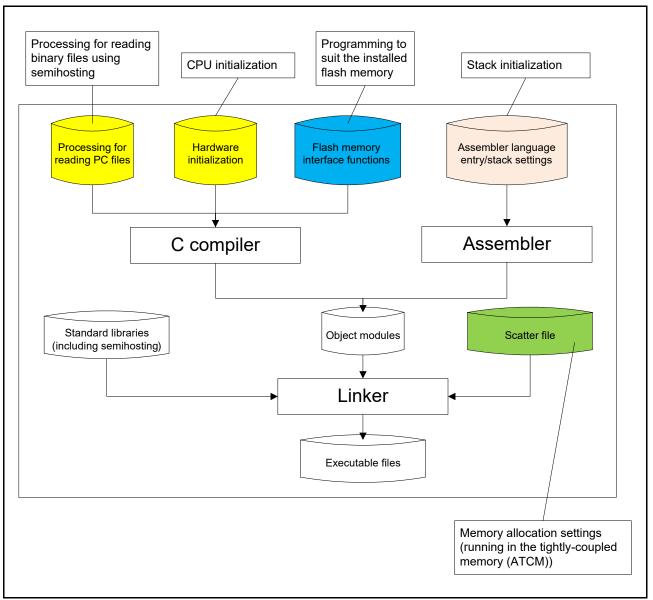

# 5.3 Developing a Flash Downloader

Figure 5.2 shows the flow of developing a flash downloader. The flash downloader is developed as a DS-5 project. This project is called the flash downloader project. The flash downloader handles processing for reading the application binary files by means of semihosting, CPU initialization, and programming to suit the given serial flash memory. The sample program covered in this application note handles programming of the serial flash memory on the RZ/T1 evaluation board as a serial flash memory interface function. For details of the serial flash memory interface functions, see Section 7, Flash Memory Interface Functions.

Figure 5.2 Flash Downloader Development Flow

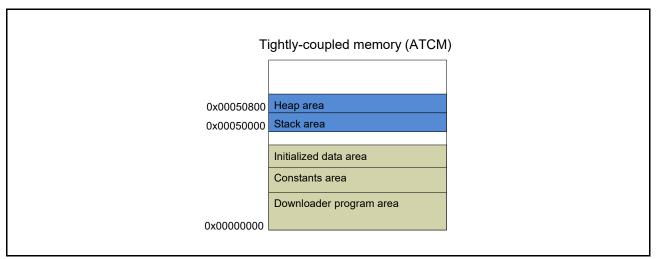

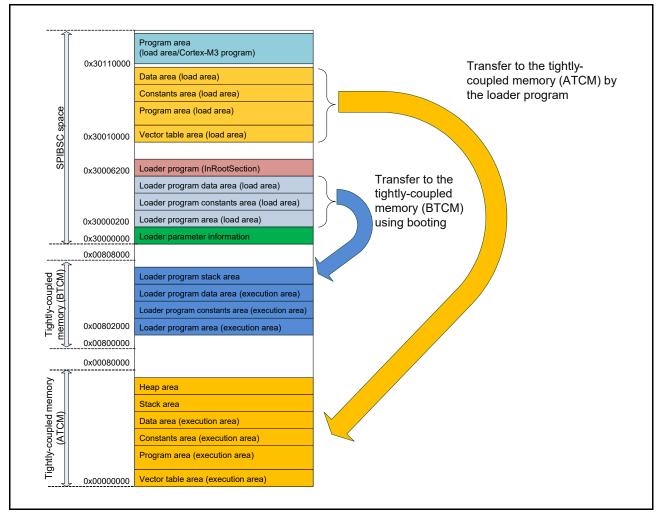

#### 5.3.1 Memory Map

Since the flash downloader runs in the tightly-coupled memory (ATCM) of the RZ/T1 group microcontroller, a scatter file\*1 is used to allocate it to the tightly-coupled memory (ATCM). Figure 5.3 shows the memory allocation of the flash downloader.

Note 1. A scatter file is text in which memory layout and allocation of codes and data are described. For details, see "ARM<sup>®</sup> Compiler toolchain Using the Linker, Image structure and generation".

Figure 5.3 Memory Allocation of the Flash Downloader

- 1. The flash downloader is allocated to the tightly-coupled memory (ATCM) area of the RZ/T1 group microcontroller. Address 0x00000000 is set as the entry point of the flash downloader.

- 2. The stack area, heap area, etc. used by the flash downloader are allocated to the tightly-coupled memory (ATCM) area.

- 3. An exception handler vector table need not be implemented for the flash downloader since semihosting provides this functionality.

## 5.4 Customizing the Examples of Downloading to the Serial Flash Memory

This section describes the procedure for customizing the examples of downloading to the serial flash memory presented in this application note.

You can customize the items listed in Table 5.2. Customize them to suit the specifications of your system.

#### Table 5.2 Customizable Items

| Item                                                           | Description                                                                                                                                                            |

|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Customization to suit the application project to be downloaded | The names of the application binary files and the write start addresses can be customized to suit the application project to be downloaded to the serial flash memory. |

|                                                                | For details of the customization procedure, see Section 10.1, Changing the Binary File Names and Destination Addresses for Writing.                                    |

| Customization of the serial flash memory interface functions   | The flash memory interface functions can be customized to suit the serial flash memory to be programmed.                                                               |

|                                                                | For details of the customization procedure, see Section 10.2, Changing the Sample Program to Suit the Given Flash Memory.                                              |

# 6. Example of Downloading to the RZ/T1 Evaluation Board (RTK7910022C00000BR)

This section presents the procedure for downloading the application program ( $RZ_T_sflash_sample$ ) to the serial flash memory on the RZ/T1 evaluation board (RTK7910022C0000BR) by using DS-5 and the  $ARM^{\mbox{\sc B}}$  emulator according to the method of downloading presented in this application note.

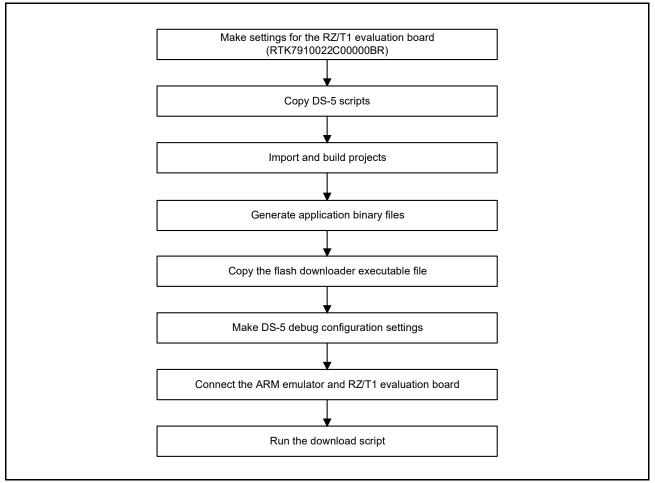

Figure 6.1 shows an outline of the downloading procedure.

Figure 6.1 Outline of Downloading Procedure

## 6.1 Settings for the RZ/T1 Evaluation Board (RTK7910022C00000BR)

Table 6.1 lists the settings for the RZ/T1 evaluation board (RTK7910022C00000BR) to run the sample program in this application note.

Make settings for the RZ/T1 evaluation board (RTK7910022C00000BR) as indicated in Table 6.1.

| Table 6.1 | Settings for the RZ/T1 Evaluation Board (RTK7910022C00000BR) |

|-----------|--------------------------------------------------------------|

|-----------|--------------------------------------------------------------|

| SW    | Setting | Description        |

|-------|---------|--------------------|

| SW4-1 | ON      | MD0 = low level    |

| SW4-2 | ON      | MD1 = low level    |

| SW4-3 | ON      | MD2 = low level    |

| SW4-4 | ON      | BSCANP = low level |

| SW4-5 | ON      | OSCTH = low level  |

| SW4-6 | OFF     | PU7 = high level   |

## 6.2 Copying DS-5 Scripts

Create a directory [script\_sflash] under the application project (RZ\_T\_sflash\_sample) directory and copy the DS-5 scripts listed in Table 6.2 into it.

Note: For details of the DS-5 workspace directory, see "Using the ARM<sup>®</sup> DS-5<sup>™</sup> Debugger" provided by ARM<sup>®</sup>.

| Script Name           | Description                                                                                                                                                                                                                                                                                 |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| init_RZ-T.ds          | This is the RZ/T1 evaluation board initialization script.<br>This DS-5 script is for executing processing, such as enabling writing to the tightly-coupled memory<br>(ATCM) of the RZ/T1 group microcontroller, when DS-5 is connected to the RZ/T1 evaluation board.                       |

| RZ_T_sflash_sample.ds | This is the application downloading script.<br>This DS-5 script contains commands for the sequence of operations for writing the application program to<br>the serial flash memory allocated to the external address space (SPI multi-I/O bus space) of the RZ/T1<br>group microcontroller. |

| init_RZ-T2.ds         | This is the RZ/T1 evaluation board initialization script to be executed from the application downloading script. It is identical to init_RZ-T.ds, except that it does not make settings for the DS-5 memory area.                                                                           |

#### Table 6.2List of DS-5 Script Files

# 6.3 Importing and Building Projects

Import the projects listed in Table 6.3 to the DS-5 workspace directory. Then, build the projects to generate executable files.

[Procedure]

- 1. Select [All Programs] [ARM DS-5 v5.21.1] [Eclipse for DS-5] from the DS-5 start menu.

- 2. Select [File (F)] [Import (I)], then open the [Import Select] window.

- 3. Select [General] [Existing Projects into Workspace], then click [Next].

- 4. Display the projects by clicking [Reference] in the [Import Import Projects] window, then select the projects to be imported. In the option, check [Copy Projects into Workspace (C)], then click [End].

- 5. Select the projects imported by the project explorer in order, then select [Project (P) Build Projects (B)] to build the projects.

#### Table 6.3 List of Projects

| Project            | Description                                                                                         | Executable File        |

|--------------------|-----------------------------------------------------------------------------------------------------|------------------------|

| RZ_T_fmtool_sflash | This project is used to build the flash downloader. We refer to it as the flash downloader project. | RZ_T_fmtool_sflash.axf |

| RZ_T_sflash_sample | This project is used to build the application program. We refer to it as the application project.   | RZ_T_sflash_sample.axf |

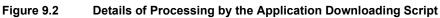

#### 6.4 Generating Application Binary Files

Run the command<sup>\*1</sup> in Figure 6.3 from [DS-5 Command Prompt] of DS-5 to generate application binary files  $(RZ_T_sflash_sample.bin)$ . Table 6.4 lists the binary files generated when this command is run.

In the project included in this application note, this processing is handled by a batch file (¥RZ T sflash sample¥Debug¥after build.bat) when building the project.

[Procedure]

- 1. Select [All Programs] [ARM DS-5 v5.21.1] [DS-5 Command Prompt] from the DS-5 Command Prompt start menu.

- 2. Type [select\_toolchain] and press enter. Select a toolchain to use and press enter (see Figure 6.2).

- 3. Set a path to the [fmtool] folder created in Section 6.3, Importing and Building Projects, and then run the command\*<sup>1</sup> listed in Figure 6.3

- Note 1. For details of the command, see "ARM<sup>®</sup> DS-5<sup>TM</sup> DS-5 Getting Started Guide, ARM DS-5 Product Overview" provided by ARM<sup>®</sup>.

```

You can change the compiler toolchain for this environment at any time by

running the 'select_toolchain' command. A default for all future environments

can be set with the 'select_default_toolchain' command.

C:\Program Files\DS-5 v5.21.1\Dim bin>select_toolchain

Select a toolchain to use in the current environment

1 - ARM Compiler 5 (DS-5 built-in)

2 - GCC 4.x [arm-linux-gnueabihf] (DS-5 built-in)

Enter a number or <return> for no toolchain: 1

Environment configured for ARM Compiler 5 (DS-5 built-in)

C:\Program Files\DS-5 v5.21.1\Dim bin>

```

Figure 6.2 Configuring a Toolchain

$from elf \ \mbox{--bin } \ \mbox{--output=RZ\_T\_sflash\_sample.bin } RZ\_T\_sflash\_sample.axf$

#### Figure 6.3 Application Binary File Generation Command

#### Table 6.4 List of Application Binary Files

| Directory              | Binary File          | Description                                                    |

|------------------------|----------------------|----------------------------------------------------------------|

| RZ_T_sflash_sample.bin | CONST_LOADER_TABLE   | Application (1) (loader parameter information) binary file     |

|                        | LOADER_RESET_HANDLER | Application (2) (loader program) binary file                   |

|                        | LOADER_IN_ROOT       | Application (3) (loader program) binary file                   |

|                        | INIT                 | Application (4) (user program) binary file                     |

|                        | CM3_SECTION*1        | Application (5) (user program) binary file (Cortex-M3 program) |

Note 1. CM3\_SECTION is a binary file for a Cortex-M3 program. For details, refer to the application note "RZ/T1 Group Initial Settings of the Microcomputers Incorporating the R-IN Engine".

# 6.5 Copying the Flash Downloader Executable File

Create a directory [fmtool] directly under the application project (RZ\_T\_sflash\_sample) directory that was imported in Section 6.3, Importing and Building Projects, and copy the flash downloader project executable file (RZ\_T\_fmtool\_sflash.axf) into it.

In the project included in this application note, this processing is handled by a batch file (l¥RZ\_T\_fmtool\_sflash¥Debug¥after\_build.bat) when building the project.

# 6.6 DS-5 Debug Configuration Settings

Follow the procedure below to make settings for a DS-5 debug configuration. The DS-5 debug configuration settings specify that the RZ/T1 evaluation board initialization script (init\_RZ-T.ds) is run when DS-5 is connected to the RZ/T1 evaluation board\*<sup>1</sup>. For details of processing by the RZ/T1 evaluation board initialization script (init\_RZ-T.ds), see Section 9.2, RZ/T1 Evaluation Board Initialization Script.

[Procedure]

- 1. In DS-5, select [Run (R)] [Debug Configurations (B)] to display the [Debug Configurations] window.

- 2. In the [Connection] tab of the DS-5 [Debug Configurations] window, select the target. As the target, select [Renesas] / [RZ/T1 R7S910x17(Generic)] / [Bare Metal Debug] / [Debug of Cortex-R4]\*2.

- 3. In the [Connection] tab of the DS-5 [Debug Configurations] window, select target connection and connection browser. In [Target Connection], select the debugger to connect, and then press the [Browse] button in [Bare Metal Debug] to select the connected debugger in [Connection Browser].

- 4. In the [Debugger] tab of the DS-5 [Debug Configurations] window, check the box for [Connect only] under Run control.

- 5. In the [Debugger] tab of the DS-5 [Debug Configurations] window, check the box for [Run target initialization debugger script (.ds/.py)] under Run control, and set a path to the RZ/T1 evaluation board initialization script (init\_RZ-T.ds).

- Note 1. The above procedure assumes that the RZ/T1 evaluation board has been registered with the DS-5 platform. If the RZ/T1 evaluation board has not been registered with the DS-5 platform, use the DS-5 debugger hardware configuration tools to register it.

- Note 2. The name of the target to select may differ according to the version of the DS-5 you are using.

| Create, manage, and run configurations                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 🗅 🗊 🗶 📄 🐡 🗸                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Name: connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| type filter text                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 🐟 Connection 🛛 🙀 Files 🏘 Debugger 🚱 OS Awareness 🚳 Arguments 🖉 Environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <ul> <li>C/C++ Application</li> <li>C/C++ Attach to Application</li> <li>C/C++ Postmortem Debugger</li> <li>C/C++ Remote Application</li> </ul>                                                                                                                                                                                                                                                                                                                                                     | Select target Select the manufacturer, board, project type and debug operation to use. Currently selected: Renesas / RZ/T1 R7S910x17 (Generic) / Bare Metal Debug / Debug Cortex-R4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| <ul> <li>DS-5 Debugger</li> <li>connect</li> <li>R.Z_T_fmtool_nor</li> <li>IronPython Run</li> <li>IronPython Run</li> <li>IronPython nunttest</li> <li>Java Applet</li> <li>Java Applet</li> <li>Java Applet</li> <li>Java Applet</li> <li>Java Applet</li> <li>Jython run</li> <li>Jython run</li> <li>Yython run</li> <li>PyDev Django</li> <li>PyDev Coogle App Run</li> <li>Python Run</li> <li>Python Run</li> <li>Python Run</li> <li>Python Run</li> <li>Remote Java Application</li> </ul> | Filter platforms <ul> <li>RZ/T1 R75910x16 (Generic)</li> <li>RZ/T1 R75910x17 (Generic)</li> <li>Bare Metal Debug</li> <li>Debug Cortex-R4</li> <li>RZ/T1 R75910x18 (Generic)</li> <li>Configure ULINK2 trace or other target options. Using "default" configuration options</li> <li>DS-S Debugger will connect to a ULINK2 to debug a bare metal application.</li> <li>Connections</li> <li>Bare Metal Debug Connection : Keil Software Keil ULINK2 CMSIS-DAP</li> <li>Browse.</li> </ul> |

| Filter matched 20 of 20 items                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Apply Revert                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Debug Close                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

Figure 6.4 Selecting a Debugger in DS-5

# 6.7 Connecting the RZ/T1 Evaluation Board with an ARM<sup>®</sup> Emulator

Follow the procedure below to connect the RZ/T1 evaluation board with an ARM<sup>®</sup> emulator.

#### [Procedure]

- 1. In the [Debug Control] tab of DS-5, select the connection under the name specified in step 2 of Section 6.6, DS-5 Debug Configuration Settings. Then right click to select [Connect to Target].

- 2. Connection starts in step 1. After the connection is established, the RZ/T1 evaluation board initialization script (init\_RZ-T.ds) registered in step 4 of Section 6.6, DS-5 Debug Configuration Settings, is run.

# 6.8 Running the Download Script

Follow the procedure below to run the download script (RZ\_T\_sflash\_sample.ds).

[Procedure]

- 1. In the [Scripts] tab of DS-5, register the download script (RZ\_T\_sflash\_sample.ds).

- 2. Double-click the download script (RZ\_T\_sflash\_sample.ds) registered in step 1 to run the script.

- 3. When the download script runs, the flash downloader is launched and starts writing to the flash memory. Figure 6.5 shows the message displayed in [Application Console].

- 4. When downloading is complete, the symbol information of the flash downloader is discarded, the RZ/T1 evaluation board initialization script (init\_RZ-T2.ds) is run from the download script (RZ\_T\_sflash\_sample.ds), and the symbol information of the application program (RZ\_T\_sflash\_sample) is loaded.

```

RZ/T1 CPU Board S-Flash Programming Sample. Ver.1.00

Copyright (C) 2015 Renesas Electronics Corporation. All rights reserved.

Initializing Flash...

Start to load Binary Data to Flash Memory.

loop=1, file=CONST_LOADER_TABLE, flash address=0x30000000.

Calculating Data Size...

Data Size is 76

Programing Flash...

Calcurating Checksum of Loader Parameter.

Verifying Flash...

loop=1, Flash Programming Success!!

loop=2, file=LOADER RESET HANDLER, flash address=0x30000200.

Calculating Data Size ...

Data Size is 11812

Programing Flash...

Verifying Flash...

loop=2, Flash Programming Success!!

loop=3, file=LOADER_IN_ROOT, flash address=0x30006200.

Calculating Data Size ...

Data Size is 236

Programing Flash...

Verifying Flash...

loop=3, Flash Programming Success!!

loop=4, file=INIT, flash address=0x30010000.

Calculating Data Size ...

Data Size is 2592

Programing Flash...

Verifying Flash...

loop=4, Flash Programming Success!!

loop=5, Could not open file. Exiting.

Flash Programming Complete

Note:

Processing by loop = 5 is dedicated to writing a Cortex-M3 program. When writing a Cortex-R4F program, the required

writing of the program is completed by loop = 4.

```

Figure 6.5 Messages Output to the Application Console

# 7. Flash Memory Interface Functions

This section describes the flash memory interface functions.

#### 7.1 Fixed-Width Integers

Table 7.1 lists fixed-width integers used in the sample program.

Table 7.1

Fixed-Width Integers Used in the Sample Program

| Symbol   | Description             |

|----------|-------------------------|

| char8_t  | 8-bit signed integer    |

| int16_t  | 16-bit signed integer   |

| int32_t  | 32-bit signed integer   |

| uint8_t  | 8-bit unsigned integer  |

| uint16_t | 16-bit unsigned integer |

| uint32_t | 32-bit unsigned integer |

# 7.2 Structures and Unions

Table 7.2 to Table 7.9 list the structures used in the sample program.

| Member Description                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| uint8_t udef_cmd                                                                 | <ul> <li>Read command</li> <li>Sets the read command output to the serial flash memory when converting read operations for the SPI multi-I/O bus space to SPI communications.</li> <li>The value of this member is set in the CMD[7:0] bits of the data read command setting register (DRCMR).</li> </ul>                                                                                                                                                                                                            |

| uint8_t udef_cmd_width                                                           | <ul> <li>Read command bit width</li> <li>Sets the bit width for issuing read commands.</li> <li>Available settings:<br/>SPIBSC_1BIT: 1-bit width<br/>SPIBSC_4BIT: 4-bit width</li> <li>The value of this member is set in the CDB[1:0] bits of the data read enable register<br/>(DRENR).</li> </ul>                                                                                                                                                                                                                 |

| uint8_t udef_opd3<br>uint8_t udef_opd2<br>uint8_t udef_opd1<br>uint8_t udef_opd0 | <ul> <li>Optional data</li> <li>Set the optional data output to the serial flash memory when converting read operations for the SPI multi-I/O bus space to SPI communications.</li> <li>The values of these members are set in the OPD3[7:0], OPD2[7:0], OPD1[7:0], and OPD0[7:0] bits of the data read option setting register (DROPR).</li> </ul>                                                                                                                                                                  |

| uint8_t udef_opd_enable                                                          | <ul> <li>Optional data enable</li> <li>Selects whether the optional data is to be issued.</li> <li>Available settings:<br/>SPIBSC_OUTPUT_DISABLE: No data is output<br/>SPIBSC_OUTPUT_OPD_3: OPD3 is output<br/>SPIBSC_OUTPUT_OPD_32: OPD3 and OPD2 are output<br/>SPIBSC_OUTPUT_OPD_321: OPD3, OPD2, and OPD1 are output<br/>SPIBSC_OUTPUT_OPD_3210: OPD3, OPD2, OPD1, and OPD0 are output.</li> <li>The value of this member is set in the OPDE[3:0] bits of the data read enable register<br/>(DRENR).</li> </ul> |

| uint8_t udef_opd_width                                                           | <ul> <li>Optional data bit width</li> <li>Sets the bit width for issuing the optional data.</li> <li>Available settings:<br/>SPIBSC_1BIT: 1-bit width<br/>SPIBSC_4BIT: 4-bit width</li> <li>The value of this member is set in the OPDB[1:0] bits of the data read enable register<br/>(DRENR).</li> </ul>                                                                                                                                                                                                           |

| Table 7.2 | Structure of SPIBSC External Address Read Settings (st_spibsc_cfg_t) (1) |

|-----------|--------------------------------------------------------------------------|

|-----------|--------------------------------------------------------------------------|

| Member  |                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|---------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| uint8_t | udef_dmycyc_num    | <ul> <li>Number of dummy cycles</li> <li>Sets the number of dummy cycles output to the serial flash memory when converting read operations for the SPI multi-I/O bus space to SPI communications.</li> <li>Available settings:<br/>SPIBSC_DUMMY_1CYC: 1 cycle<br/>SPIBSC_DUMMY_2CYC: 2 cycles<br/>SPIBSC_DUMMY_3CYC: 3 cycles<br/>SPIBSC_DUMMY_4CYC: 4 cycles<br/>SPIBSC_DUMMY_4CYC: 5 cycles<br/>SPIBSC_DUMMY_5CYC: 5 cycles<br/>SPIBSC_DUMMY_6CYC: 6 cycles<br/>SPIBSC_DUMMY_7CYC: 7 cycles<br/>SPIBSC_DUMMY_8CYC: 8 cycles</li> <li>The value of this member is set in the DMCYC[2:0] bits of the data read dummy cycle setting register (DRDMCR).</li> </ul> |  |

| uint8_t | udef_dmycyc_enable | <ul> <li>Dummy cycle enable</li> <li>Selects whether dummy cycles are to be inserted.</li> <li>Available settings:<br/>SPIBSC_DUMMY_CYC_DISABLE: Dummy cycles are not inserted<br/>SPIBSC_DUMMY_CYC_ENABLE: Dummy cycles are inserted</li> <li>The value of this member is set in the DME bit of the data read enable register (DRENR).</li> </ul>                                                                                                                                                                                                                                                                                                               |  |

| uint8_t | udef_dmycyc_width  | <ul> <li>Dummy cycle bit width</li> <li>Sets the bit width for issuing dummy cycles.</li> <li>Available settings:<br/>SPIBSC_1BIT: 1-bit width<br/>SPIBSC_4BIT: 4-bit width</li> <li>The value of this member is set in the DMDB[1:0] bits of the data read dummy cycle<br/>setting register (DRDMCR).</li> </ul>                                                                                                                                                                                                                                                                                                                                                |  |

| uint8_t | udef_data_width    | <ul> <li>Data read bit width</li> <li>Sets the bit width for reading data from the serial flash memory when converting read operations for the SPI multi-I/O bus space to SPI communications.</li> <li>Available settings:<br/>SPIBSC_1BIT: 1-bit width<br/>SPIBSC_4BIT: 4-bit width</li> <li>The value of this member is set in the DRDB[1:0] bits of the data read enable register (DRENR).</li> </ul>                                                                                                                                                                                                                                                         |  |

#### Table 7.3 Structure of SPIBSC External Address Read Settings (st\_spibsc\_cfg\_t) (2)

| Member                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| uint8_t udef_spbr       | <ul> <li>Bit rate</li> <li>Sets the bit rate of the serial clock (SPBCLK) output to the serial flash memory when converting read operations for the SPI multi-I/O bus space to SPI communications.</li> <li>Available settings:<br/>Make settings to match the bit-rate division setting (udef_brdv).</li> <li>The value of this member is set in the SPBR[7:0] bits of the bit rate setting register (SPBCR).</li> </ul>                            |

| uint8_t udef_brdv       | <ul> <li>Bit-rate division setting</li> <li>Sets the bit rate of the serial clock (SPBCLK) output to the serial flash memory when converting read operations for the SPI multi-I/O bus space to SPI communications.</li> <li>Available settings:<br/>Make settings to match the bit-rate division setting (udef_brdv).</li> <li>The value of this member is set in the BRDV[1:0] bits of the bit-rate setting register (SPBCR).</li> </ul>           |

| uint8_t udef_addr_width | <ul> <li>Address bit width <ul> <li>Sets the width in bits of the address line or lines for output to the serial flash memory when converting read operations for the SPI multi-I/O bus space to SPI communications.</li> <li>Available settings:</li> <li>SPIBSC_1BIT: 1-bit width</li> <li>SPIBSC_4BIT: 4-bit width</li> <li>The value of this member is set in the ADB[1:0] bits of the data read enable register (DRENR).</li> </ul> </li> </ul> |

| uint8_t udef_addr_mode  | <ul> <li>Address enable</li> <li>Sets the address for output to the serial flash memory when converting read operations for the SPI multi-I/O bus space to SPI communications.</li> <li>Available settings:<br/>SPIBSC_OUTPUT_ADDR_24: 24-bit address output<br/>SPIBSC_OUTPUT_ADDR_32: 32-bit address output</li> <li>The value of this member is set in the ADE[3:0] bits of the data read enable register (DRENR).</li> </ul>                     |

#### Table 7.4 Structure of SPIBSC External Address Read Settings (st\_spibsc\_cfg\_t) (3)

| Member   |       | Description                                                                                                                                                                                                                                                                                                                      |

|----------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| uint32_t | cdb   | <ul> <li>Command bit width</li> <li>Sets the command bit width in SPI operation mode.</li> <li>Available settings:<br/>SPIBSC_1BIT: 1-bit width<br/>SPIBSC_4BIT: 4-bit width</li> <li>The value of this member is set in the CDB[1:0] bits of the SPI mode enable register<br/>(SMENR).</li> </ul>                               |

| uint32_t | ocdb  | <ul> <li>Optional command bit width</li> <li>Specifies the optional command bit width in SPI operation mode.</li> <li>Available settings:<br/>SPIBSC_1BIT: 1-bit width<br/>SPIBSC_4BIT: 4-bit width</li> <li>The value of this member is set in the OCDB[1:0] bits of the SPI mode enable register<br/>(SMENR).</li> </ul>       |

| uint32_t | adb   | <ul> <li>Address bit width</li> <li>Specifies the width in bits of the address line or lines in SPI operation mode.</li> <li>Available settings:<br/>SPIBSC_1BIT: 1-bit width<br/>SPIBSC_4BIT: 4-bit width</li> <li>The value of this member is set in the ADB[1:0] bits of the SPI mode enable register<br/>(SMENR).</li> </ul> |

| uint32_t | opdb  | <ul> <li>Optional data bit width</li> <li>Specifies the optional data bit width in SPI operation mode.</li> <li>Available settings:<br/>SPIBSC_1BIT: 1-bit width<br/>SPIBSC_4BIT: 4-bit width</li> <li>The value of this member is set in the OPDB[1:0] bits of the SPI mode enable register<br/>(SMENR).</li> </ul>             |

| uint32_t | spidb | <ul> <li>Transfer data bit width</li> <li>Specifies the transfer data bit width in SPI operation mode.</li> <li>Available settings:<br/>SPIBSC_1BIT: 1-bit width<br/>SPIBSC_4BIT: 4-bit width</li> <li>The value of this member is set in the SPIDB[1:0] bits of the SPI mode enable register<br/>(SMENR).</li> </ul>            |

| uint32_t | cde   | <ul> <li>Sets whether commands are to be output in SPI operation mode.</li> <li>Available settings:<br/>SPIBSC_OUTPUT_DISABLE: Output is disabled.<br/>SPIBSC_OUTPUT_ENABLE: Output is enabled.</li> <li>The value of this member is set in the CDE bit of the SPI mode enable register (SMENR)</li> </ul>                       |

#### Table 7.5 Structure of SPIBSC SPI Mode Settings (st\_spibsc\_spimd\_reg\_t) (1)

| Member   |       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| uint32_t | ocde  | <ul> <li>Optional command enable</li> <li>Sets whether the optional command is to be output in SPI operation mode.</li> <li>Available settings:<br/>SPIBSC_OUTPUT_DISABLE: Output is disabled.<br/>SPIBSC_OUTPUT_ENABLE: Output is enabled.</li> <li>The value of this member is set in the OCDE bit of the SPI mode enable register<br/>(SMENR).</li> </ul>                                                                                                                                                                                        |

| uint32_t | ade   | <ul> <li>Address enable</li> <li>Sets whether the address is to be output in SPI operation mode.</li> <li>Available settings:<br/>SPIBSC_OUTPUT_DISABLE: Output is disabled.<br/>SPIBSC_OUTPUT_ADDR_24: ADR[23:0] is output.<br/>SPIBSC_OUTPUT_ADDR_32: ADR[31:0] is output.</li> <li>The value of this member is set in the ADE[3:0] bits of the SPI mode enable register<br/>(SMENR).</li> </ul>                                                                                                                                                  |

| uint32_t | opde  | <ul> <li>Optional data enable</li> <li>Sets whether the optional data is to be issued in SPI operation mode.</li> <li>Available settings:<br/>SPIBSC_OUTPUT_DISABLE: Output is disabled.<br/>SPIBSC_OUTPUT_OPD_3: OPD3 is output.<br/>SPIBSC_OUTPUT_OPD_32: OPD3 and OPD2 are output.<br/>SPIBSC_OUTPUT_OPD_321: OPD3, OPD2, and OPD1 are output.<br/>SPIBSC_OUTPUT_OPD_3210: OPD3, OPD2, OPD1, and OPD0 are output.</li> <li>The value of this member is set in the OPDE[3:0] bits of the SPI mode enable setting<br/>register (SMENR).</li> </ul> |

| uint32_t | spide | <ul> <li>Transfer data enable</li> <li>Sets whether data transfer is to proceed in SPI operation mode.</li> <li>Available settings:<br/>SPIBSC_OUTPUT_DISABLE: Output is disabled.<br/>SPIBSC_OUTPUT_SPID_8: 8- (or 16-) bit transfer<br/>SPIBSC_OUTPUT_SPID_16: 16- (or 32-) bit transfer<br/>SPIBSC_OUTPUT_SPID_32: 32- (or 64-) bit transfer</li> <li>The value of this member is set in the SPIDE[3:0] bits of the SPI mode enable register<br/>(SMENR).</li> </ul>                                                                             |

| uint32_t | sslkp | <ul> <li>SPBSSL signal level retention</li> <li>Sets the state of the SPBSSL signal after the end of transfer in SPI operation mode.</li> <li>Available settings:<br/>SPIBSC_SPISSL_NEGATE: The signal is negated at the end of transfer.<br/>SPIBSC_SPISSL_KEEP: The level of the SPBSSL signal is retained from the end of transfer to the start of next access.</li> <li>The value of this member is set in the SSLKP bit of the SPI mode control register (SMCR).</li> </ul>                                                                    |

#### Table 7.6 Structure of SPIBSC SPI Mode Settings (st\_spibsc\_spimd\_reg\_t) (2)

| Member   |        | Description                                                                                                                                                                                                                                                                                                                                                           |

|----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| uint32_t | spire  | <ul> <li>Data read enable</li> <li>Enables or disables reading of data in SPI operation mode.</li> <li>Available settings:<br/>SPIBSC_SPIDATA_DISABLE: Reading of data is disabled.<br/>SPIBSC_SPIDATA_ENABLE: Reading of data is enabled.</li> <li>The value of this member is set in the SPIRE bit of the SPI mode control register<br/>(SMCR).</li> </ul>          |

| uint32_t | spiwe  | <ul> <li>Data write enable</li> <li>Enables or disables writing of data in SPI operation mode.</li> <li>Available settings:<br/>SPIBSC_SPIDATA_DISABLE: Writing of data is disabled.<br/>SPIBSC_SPIDATA_ENABLE: Writing of data is enabled.</li> <li>The value of this member is set in the SPIWE bit of the SPI mode control register<br/>(SMCR).</li> </ul>         |

| uint32_t | dme    | <ul> <li>Dummy cycle enable</li> <li>Sets whether dummy cycles are to be inserted in SPI operation mode.</li> <li>Available settings:<br/>SPIBSC_DUMMY_CYC_DISABLE: Dummy cycles are not inserted.<br/>SPIBSC_DUMMY_CYC_ENABLE: Dummy cycles are inserted.</li> <li>The value of this member is set in the DME bit of the SPI mode enable register (SMENR)</li> </ul> |

| uint32_t | adder  | <ul> <li>Address DDR enable</li> <li>Selects SDR or DDR transfer of the address for output in SPI operation mode.</li> <li>Available setting:<br/>SPIBSC_SDR_TRANS SDR transfer</li> <li>The value of this member is set in the ADDRE bit of the SPI mode DDR enable register<br/>(SMDRENR).</li> </ul>                                                               |

| uint32_t | opdre  | <ul> <li>Optional data DDR enable</li> <li>Selects SDR or DDR transfer of the optional data for output in SPI operation mode.</li> <li>Available settings:<br/>SPIBSC_SDR_TRANS: SDR transfer</li> <li>The value of this member is set in the OPDRE bit of the SPI mode DDR enable register<br/>(SMDRENR).</li> </ul>                                                 |

| uint32_t | spidre | <ul> <li>Transfer data DDR enable</li> <li>Selects SDR or DDR transfer of the data for transfer in SPI operation mode.</li> <li>Available setting:<br/>SPIBSC_SDR_TRANS: SDR transfer</li> <li>The value of this member is set in the SPIDRE bit of the SPI mode DDR enable register<br/>(SMDRENR).</li> </ul>                                                        |

#### Table 7.7 Structure of SPIBSC SPI Mode Settings (st\_spibsc\_spimd\_reg\_t) (3)

| Member         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| uint8_t dmdb   | <ul> <li>Dummy cycle bit width</li> <li>Sets the bit width of dummy cycles in SPI operation mode.</li> <li>Available settings:<br/>SPIBSC_1BIT: 1-bit width<br/>SPIBSC_4BIT: 4-bit width</li> <li>The value of this member is set in the DMDB[1:0] bits of the SPI mode dummy cycle<br/>setting register (SMDMCR).</li> </ul>                                                                                                                                                                                                     |  |

| uint8_t dmcyc  | <ul> <li>Number of dummy cycles</li> <li>Sets the number of dummy cycles in SPI operation mode.</li> <li>Available settings:<br/>SPIBSC_DUMMY_1CYC: 1 cycle<br/>SPIBSC_DUMMY_2CYC: 2 cycles<br/>SPIBSC_DUMMY_3CYC: 3 cycles<br/>SPIBSC_DUMMY_4CYC: 4 cycles<br/>SPIBSC_DUMMY_5CYC: 5 cycles<br/>SPIBSC_DUMMY_6CYC: 6 cycles<br/>SPIBSC_DUMMY_7CYC: 7 cycles<br/>SPIBSC_DUMMY_8CYC: 8 cycles</li> <li>The value of this member is set in the DMCYC[2:0] bits of the SPI mode dummy cycle<br/>setting register (SMDMCR).</li> </ul> |  |

| uint8_t cmd    | <ul> <li>Command</li> <li>Sets the command for output in SPI operation mode.</li> <li>The value of this member is set in the CMD[7:0] bits of the SPI mode command setting register (SMCMR).</li> </ul>                                                                                                                                                                                                                                                                                                                           |  |

| uint8_t ocmd   | <ul> <li>Optional command</li> <li>Sets the optional command for output in SPI operation mode.</li> <li>The value of this member is set in the OCMD[7:0] bits of the SPI mode command setting register (SMCMR).</li> </ul>                                                                                                                                                                                                                                                                                                        |  |

| uint32_t addr  | <ul> <li>Address</li> <li>Sets the address for output in SPI operation mode.</li> <li>The value of this member is set in the ADR[31:0] bits of the SPI mode address setting register (SMADR).</li> </ul>                                                                                                                                                                                                                                                                                                                          |  |

| uint8_t opd[4] | <ul> <li>Optional data</li> <li>Sets the optional data for output in SPI operation mode.</li> <li>The value of this member is set in the OPDn[7:0] bits of the SPI mode option setting register (SMOPR) as follows.</li> <li>OPD3[7:0] ← opd[0]</li> <li>OPD2[7:0] ← opd[1]</li> <li>OPD1[7:0] ← opd[2]</li> <li>OPD0[7:0] ← opd[3]</li> </ul>                                                                                                                                                                                    |  |

#### Table 7.8 Structure of SPIBSC SPI Mode Settings (st\_spibsc\_spimd\_reg\_t) (4)

| Member            | Description                                                                                                                                                                                                                          |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| uint32_t smrdr[2] | <ul> <li>Read data storage buffer</li> <li>Holds the data read in SPI operation mode (the value of the SPI mode read data register n (SMRDRn)) as follows.</li> <li>SMRDR0 → smrdr[0]</li> <li>SMRDR1 → smrdr[1]</li> </ul>          |