# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# SuperH RISC engine C/C++ Compiler Package

**APPLICATION NOTE:** [Reference] Additional functions

This document explains features added to each version of the SuperH RISC engine C/C++ compiler, as well as provides notes on upgrading from an earlier version.

| A.1   | Features Added between Ver. 1.0 and Ver. 2.0              | 2 |

|-------|-----------------------------------------------------------|---|

| A.2   | Features Added between Ver. 2.0 and Ver. 3.0              | 3 |

| A.3   | Features Added between Ver. 3.0 and Ver. 4.1              | 6 |

| A.4   | Features Added between Ver. 4.1 and Ver. 5.0              | 9 |

| A.5   | Features Added between Ver. 5.0 and Ver. 5.1 1            | 1 |

| A.6   | Features Added between Ver. 5.1 and Ver. 6.0 1            | 3 |

| A.7   | Features Added between Ver. 6.0 and Ver. 7.0 1            | 5 |

| A.8   | Features Added between Ver. 7.0 and Ver. 7.1              | 8 |

| A.9   | Features Added between Ver. 7.1 and Ver. 8.0 4            | 0 |

| A.10  | Features Added between Ver. 8.0 and Ver. 9.0 4            | 1 |

| A.11  | Features Added between Ver. 9.0 and Ver. 9.1 4            | 3 |

| A.12  | Features Added between Ver. 9.1 and Ver. 9.25             | 2 |

| B. 1  | Notes on Version Upgrade                                  | 4 |

|       | Guaranteed Program Operation7                             |   |

| B.2 ( | Compatibility with Earlier Version7                       | 5 |

| Webs  | ite and Support <website and="" support,ws="">7</website> | 6 |

| Revis | ion Record <revision history,rh=""></revision>            | 6 |

# A.1 Features Added between Ver. 1.0 and Ver. 2.0

Table A.1 summarizes the features added to version 2.0 of the SHC compiler.

|     | Table A.1 Summary of Features Added to Version 2.0 of the SHC Compiler |                                                                                                                                    |  |  |  |  |

|-----|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| No. | Feature                                                                | Description                                                                                                                        |  |  |  |  |

| 1   | Support for SH7600 Series                                              | In addition to the SH7000 Series, objects can be<br>created which use instructions for the SH7600<br>Series as well.               |  |  |  |  |

| 2   | Position-independent code                                              | SH7600 Series objects can be created with program sections assigned to arbitrary addresses.                                        |  |  |  |  |

| 3   | Specification of output area for character strings                     | An option can be used to select whether to place character string data in a constant section (ROM) or in a data section (RAM).     |  |  |  |  |

| 4   | Comment nesting                                                        | An option is supported to specify whether<br>comments are nested or not.                                                           |  |  |  |  |

| 5   | Optimize for speed or for size                                         | An option is provided to specify whether to optimize for speed or for size at time of object creation.                             |  |  |  |  |

| 6   | Support for section name switching                                     | By using #pragma instructions midway through a program, object output section names can be switched.                               |  |  |  |  |

| 7   | mac embedded function                                                  | An embedded function is supported for<br>performing multiply-and-accumulate operations<br>on two arrays using the MAC instruction. |  |  |  |  |

| 8   | Embedded functions for system calls                                    | Embedded functions are supported for making direct system calls to the ITRON-specification OS HI-SH7.                              |  |  |  |  |

| 9   | Single-precision elementary function library                           | A single-precision elementary function library is supported.                                                                       |  |  |  |  |

| 10  | char-type bit fields                                                   | char-type bit fields are supported.                                                                                                |  |  |  |  |

### A.2 Features Added between Ver. 2.0 and Ver. 3.0

Table A.2 summarizes the features added to version 3.0 of the SHC compiler.

| No. | Table A.2 Summary of Fea<br><b>Feature</b>                      | tures Added to Version 3.0 of the SHC Compiler<br>Description                                                                                                                                                          |

|-----|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Strengthened optimization                                       | Optimization performance was greatly enhanced.<br>Also, provisions were made for selective use of the<br>option to optimize for speed or for size.                                                                     |

| 2   | SH-3 support                                                    | An option was provided for generating objects for the SH-3, and the little-endian format characteristic of the SH-3 was also supported. Also, an SH-3 data prefetch instruction was supported as an embedded function. |

| 3   | Extension of compiler limits                                    | The number of files that can be compiled at once, the maximum nesting levels for include files, and other compiler limits were extended.                                                                               |

| 4   | Support for Japanese<br>character codes in character<br>strings | Provisions were added for character string data containing shift-JIS and EUC Japanese character codes.                                                                                                                 |

| 5   | Specification of options using files                            | Files can be used to specify command line options.                                                                                                                                                                     |

| 6   | Utilization of the SH-2 divider                                 | Division operation code is generated which makes use of the SH-2 divider.                                                                                                                                              |

| 7   | Inline expansion                                                | Specifications can be added for inline expansion of user routines written in C and assembly languages.                                                                                                                 |

| 8   | Use of short address specifications                             | Variables can be specified for short addressing, including two-byte addresses and GBR-relative data.                                                                                                                   |

| 9   | Control of register save/restore operations                     | Statements can be added to suppress register<br>save/restore operations, to improve function speed and<br>size.                                                                                                        |

#### (1) Strengthened optimization

Optimization in ver. 3.0 provides options for emphasizing speed (the -SPEED option) and size (the -SIZE option), and both types of optimization have been reinforced.

To enhance speed, loop optimization has been improved and inline expansion employed to improve execution speed by about 10%, achieving an execution speed of 1 MIPS/MHz.

In order to reduce program size, instructions which shrink code size are generated and overlapping processing is combined for significant improvements, to cut object size by approximately 20%. And, by using expansion features introduced in ver.3.0 (8. Use of short address specifications, and 9. Control of register save/restore operations), object size can be further reduced.

#### (2) SH-3 support

In addition to the SH-1 and SH-2, objects can now be created for the SH-3 (using the -CPU=SH3 option). Also, the following features for the SH-3 are supported.

- (a) An -ENDIAN option (-ENDIAN=BIG or LITTLE) corresponding to a feature for setting the order of bits in memory is supported.

- (b) A prefetch extended embedded function for generating a cache prefetch instruction (PREF) is supported.

#### (3) Extension of compiler limits

Compiler limits were extended as indicated in the following table.

| No. | Description                                               | Ver.2.0      | Ver.3.0        |

|-----|-----------------------------------------------------------|--------------|----------------|

| 1   | Number of source programs that can be<br>compiled at once | 16 files     | unlimited      |

| 2   | Number of source code lines per file                      | 32,767 lines | 65535<br>lines |

| 3   | Number of source code lines in an entire<br>compiled unit | 32,767 lines | unlimited      |

| 4   | Maximum number of #include nesting levels                 | 8 levels     | 30 levels      |

#### (4) Support for Japanese character codes in character strings

Shift-JIS and EUC Japanese character codes can also be included in programs as character string data.

When input codes are shift-JIS (-SJIS option), output codes are also shift-JIS; when input codes are EUC (-EUC option), output codes are also EUC.

However, the graphical user interface currently does not support display of Japanese character code data.

#### (5) Specification of options using files

By using the -SUBCOMMAND option to specify a file name, options can be included in the specified file rather than on the command line. As a result, numerous complex options need not be entered on the command line each time.

#### (6) Utilization of the SH-2 divider

The following options are supported to enable use of the SH-2 divider.

- (a) Objects which do not use the divider can be generated through the -DIVISION=CPU option.

- (b) Objects which use the divider can be generated by using the -DIVISION=PERIPHERAL option. During use of the divider, interrupts are disabled.

- (c) Objects which use the divider can be generated through the -DIVISION=NOMASK option. This assumes that the divider will not be used during interrupt processing.

#### (7) Inline expansion

#### (a) Inline expansion of C functions

When the -SPEED option is used, the compiler automatically inline-expands small functions. Also, by using the -INLINE option, the maximum size of functions for inline expansion can be modified. Inline expansion can also be explicitly specified using a #pragma statement. The "#pragma inline" statement specifies inline expansion of a user function written in C.

Example (inline expansion of C function):

```

#pragma inline(func) main()

int func(int a, int b)

{

{

i=func(10,20); /* expanded to i=(10+20)/2 */

return(a+b)/2;

}

}

```

(b) Inline expansion of an assembler function

The "#pragma inline\_asm" option can be used to specify inline expansion of user functions written in assembly language. However, when using "#pragma inline\_asm" for inline expansion, the output of the compiler is assembly language source code. In such cases debugging at the C language level is not possible.

Example (inline expansion of an assembler function):

```

#pragma inline_asm(rotl)

int rotl(int a)

{

ROTL R4

MOV R4,R0

}

```

```

main()

```

```

{

i=rotl(i); /* set the variable i in the register R4, and expand the code for the function rotl

*/

}

```

(8) Use of short address specifications

(a) Specifying two-byte address variables

Using the "#pragma abs16(<variable name>)" statement, variables can be specified for assignment to an address range addressable using two bytes (-32768 to 32767). By this means, the size of an object referring to such a variable can be reduced.

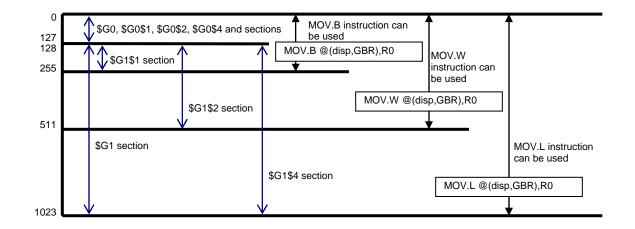

#### (b) Specification of GBR base variables

Using the "#pragma gbr(<variable name>)" statement, a variable can be specified for referencing in GBR-relative addressing mode. By this means, the size of an object referencing this variable can be reduced, and memory-based bit manipulation instructions specific to the GBR-relative addressing mode can be employed.

#### (9) Control of register save/restore operations

The "#pragma noregsave(<function name>)" statement can be used to suppress register save/restore operations at the entry and exit points of functions. This can be used to produce fast, compact functions without register save/restore overhead. A function for which "#pragma noregsave" is specified cannot be called by ordinary functions, but can be called by C language functions which are specified explicitly (using "#pragma regsave") for calling a function for which "#pragma noregsave" has been specified.

By using "#pragma noregsave" with functions which are executed frequently, program size can be reduced and speed of execution increased.

### A.3 Features Added between Ver. 3.0 and Ver. 4.1

The features added to version 4.1 of the SuperH RISC engine C/C++ compiler are summarized below.

#### (1) Register assignment of external variables

The "#pragma global\_register(<variable name>=<register number>)" statement can be used to assign external variables to registers.

#### (2) Cache-savvy optimization

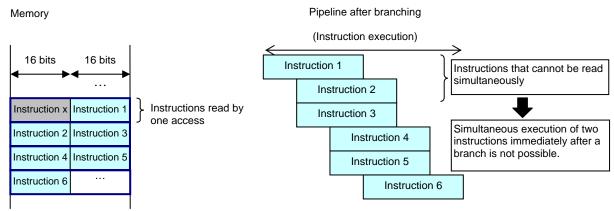

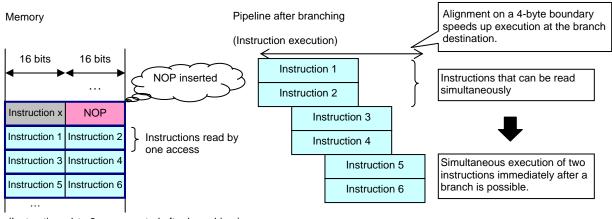

An "-align16" option is supported for assigning labels with 16-byte alignments, for efficient use of cache memory and fetch instructions.

#### (3) Strengthened inline expansion feature

A feature was added such that, when as a result of inline expansion a function is itself no longer used, it is deleted. Functions which are not themselves necessary after inline expansion should be declared using "static". Similarly, static functions which are not called or referenced by address are deleted.

Examples:

```

#pragma inline(func) #pragma inline(func)

int a; int a;

static int func() { /* func() function is itself deleted */

a++;

}

main() { main() {

func(); a++; /* inline expansion

}

```

#### (4) **Recursive inline expansion**

A feature was added for recursive inline expansion of functions. The depth of recursion can be specified using the "-nestinline" option.

#### (5) Option for loop expansion optimization

The "-loop" and "-noloop" options can be used to specify whether or not loop processing is expanded in optimization, independently of the "-speed" and "-size" options. (These options are invalid when the option to omit optimization is specified.)

#### (6) Option for two-byte-address variables

Previously, variables with two-byte addresses had to be specified individually using the "#pragma abs16" statement, but now an "-abs16" option enables specification for all variables at once. The option "-abs16=run" specifies two-byte addresses only for runtime routines; "-abs16=all" specifies two-byte addresses for all variables and functions, including runtime routines.

#### (7) Upper byte of function return value guaranteed

Previously, the upper byte of values returned by functions in the (unsigned) char and short types was not guaranteed. By specifying the "-rtnext" option, the upper byte of the return value is now guaranteed (the upper byte of R0 is signextended or zero-extended).

# RENESAS

#### (8) More complete listing files

Compared with previous versions, the information contained in object lists and assembly lists is now more complete and easier to read.

By the simultaneously output in statement units of C source and assembly language source in a list file, the correspondence between them is easier to grasp (using the "-show=source,object" option).

(in addition, the default for the "-show" option was changed from source to nosource.)

A list of runtime routine names used in a function has been added, as information for computing the amount of stack space used by the function.

The data loaded by an instruction for data loading from a constant pool is added as a comment.

Examples:

```

1: float x;

2: func() {

x/=1000;

3:

4:

}

Listing file

func.c 1

float x;

func(){*(a) Simultaneous output of C source and assembly language

func.c 2

code

000000

func:

; function: func

; frame size=4

; used runtime library name:

; divs *(b) Runtime routine name

000000

4F22

STS.L PR,@-R15

3 x/=1000;

func.c

000002

D404

MOV.L L216+2,R4 ; x

D004

MOV.L L216+6,R0 ; H'447A0000 *(c) Load data

000004

000006

D305

MOV.L L216+10,R3 ; divs

800000

430B

JSR

@R3

MOV.L @R4,R1

A00000

6142

func.c

4

}

00000C

4F26

LDS.L

@R15+,PR

00000E

000B

RTS

000010

2402

MOV.L

R0,@R4

000012

L216:

000012 00000002 .RES.W

1

<00000000> .DATA.L _x

000014

000018

447A0000 .DATA.L H'447A0000

<00000000> .DATA.L __divs

00001C

000000 _ x:

000000 00000004 .RES.L 1

; static:

х

```

# RENESAS

#### (9) More complete error messages

By specifying the "-message" option to output information messages, programming errors can be checked more easily. Examples:

```

1: void func(){

2: int a;

3: a++;

4: sub(a);

5: }

```

#### Information messages

| line 3: 0011 (I) Used before set symbol: "a" | (reference of undefined auto variable) |

|----------------------------------------------|----------------------------------------|

| line 4: 0200 (I) No prototype function       | (no prototype declaration)             |

In addition, the identifier, token or number causing the error is added to the message to make it easier to find the error location.

#### Examples:

- : 2118 (E) Prototype mismatch "identifier"

- : 2119 (E) Not a parameter name "identifier"

- : 2201 (E) Cannot covert parameter "number"

- : 2225 (E) Undeclared name "identifier"

- : 2500 (E) Illegal token "token"

#### (10) Automatic conversion of Japanese character codes

When a character string containing either EUC or shift-JIS Japanese character codes is output to an object file, the Japanese character codes are automatically converted to the encoding specified by an encoding option.

- (a) An "-outcode=euc" option causes automatic conversion to EUC codes.

- (b) An "-outcode=sjis" option results in automatic conversion to shift-JIS codes.

#### (11) Specification of CPU type by an environment variable

It is now possible to use an environment variable instead of a command line option to specify the CPU type.

Environment variable specification

| SHCPU=SH1 | (equivalent | to | the | "-cpu=sh1" | option) |

|-----------|-------------|----|-----|------------|---------|

| SHCPU=SH2 | (equivalent | to | the | "-cpu=sh2" | option) |

| SHCPU=SH3 | (equivalent | to | the | "-cpu=sh3" | option) |

#### (12) Option to treat double data types as float types

By using the "-double=float" option, data declared as the double type can be read as the float type. In programs where the precision of the double type is not required, execution speed can be improved without the need to modify the source code.

### A.4 Features Added between Ver. 4.1 and Ver. 5.0

The features added to version 5.0 of the SuperH RISC engine C/C++ compiler are summarized below.

#### (1) Extension of the number of characters in a line

The limit on the number of characters in a single logical line was extended from 4,096 characters to 32,768 characters.

#### (2) Removal of the limit on compiler source lines

The limit of 65,535 lines in a single file for compiling was removed. However, that part of the file exceeding 65,535 lines cannot be debugged.

#### (3) Compatibility with SH-4 instructions

This compiler version is also compatible with the SH-4, to maintain compliance with the SH Family of CPUs. By using the "-cpu=sh4" option, SH-4 objects can be generated.

#### (4) Addition of a normalize mode

By using the "-denormalize=on|off" option, it is possible to choose whether to handle non-normalized numbers or set them to zero. This is valid only when "-cpu=sh4" is used.

However, when "-denormalize=on", if a non-normalized number is input to the FPU, an exception occurs. Hence an exception handler must be written to handle processing of non-normalized numbers.

#### (5) Addition of a rounding mode

By using the "-round=nearest|zero" option, it is possible to choose whether to round to zero or to the nearest number. This is valid only when "-cpu=sh4" is used.

#### (6) Compatibility of compiler option environment variable with SH-4

Instead of using command line options to specify the CPU, the environment variable "SHCPU" can be used to specify the SH-4, by setting "SHCPU=SH4".

#### (7) Compatibility with the SH-2E

By using the "-cpu-sh2e" option, objects for the SH-2E can be generated.

#### (8) Compatibility of compiler option environment variable with SH-2E

Instead of using command line options to specify the CPU, the environment variable "SHCPU" can be used to specify the SH-2E, by setting "SHCPU=SH2E".

#### (9) Use of extensions to distinguish between C and C++ files

By selective use of the shc and shcpp commands, the compiler enables determination of the syntax used. Now, C++ files can be compiled based on file extensions or an options even when using the shc command. For details refer to the table below.

| Table A.4 Conditions for Determining Compiling Syntax |                    |                                    |                             |  |  |  |  |

|-------------------------------------------------------|--------------------|------------------------------------|-----------------------------|--|--|--|--|

| Command                                               | Option             | Extension of File<br>for Compiling | Syntax Used in<br>Compiling |  |  |  |  |

| shcpp                                                 | Arbitrary          | Arbitrary                          | Compiled as C++             |  |  |  |  |

|                                                       | -lang=c            | - Arbitrary                        | Compiled as C               |  |  |  |  |

|                                                       | -lang=cpp          | Albitrary                          | Compiled as C++             |  |  |  |  |

| shc                                                   | No long            | *.C                                | Compiled as C               |  |  |  |  |

|                                                       | No -lang<br>option | *.cpp, *.cc, *.cp,<br>*.CC         | Compiled as C++             |  |  |  |  |

### A.5 Features Added between Ver. 5.0 and Ver. 5.1

The features added to version 5.1 of the SuperH RISC engine C/C++ compiler are summarized below.

#### (1) Support for the SH3-DSP library

In addition to the older SH-DSP, support is now also available for libraries that can be applied to SH3-DSP.

#### (2) Support for embedded C++ language

Support is now available for embedded C++ language specification, which is the C++ specification compatible with embedded systems.

- Support for bool-type

- Multiple inheritance warnings

- Support for embedded C++ language class libraries

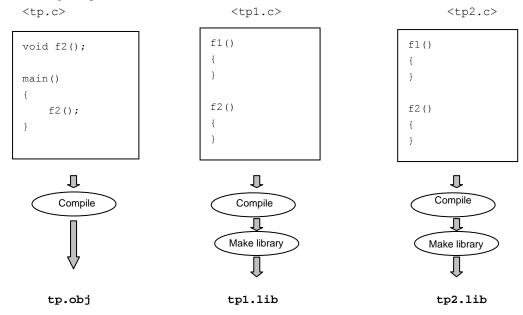

#### (3) Support for inter-module optimization functions

Implements the following optimization, and generates objects with optimal size/speed.

With this optimization, size is reduced by approximately 10%, and execution speed is improved by 7 to 8%.

- Reduction of superfluous register save/restore code

- Deletion of unreferenced variables/functions

- Routinization of common codes

- Optimization of function call codes

- (4) Improved compiling speed

Fast compiling speed has been achieved through improved optimization processing.

A maximum of double speed, and an average speed increase of 130% has been achieved.

#### (5) Extension of limits

- The limit on command line length has been extended from 256 to 4,096.

- The limit on file name length has been extended from 128 to 251.

- The limit on character string literal length has been extended from 512 to 32,767.

- (6) Strengthened optimization

The various kinds of optimization for improving object performance have been strengthened.

#### (7) Support for C++ comments

In the C language, use of "//" comments is now possible.

#### (8) Changes to the integrated environment (PC version)

The older PC integrated environment HIM (Hitachi Integration Manager) has been replaced by the new integrated environment HEW (High-performance Embedded Workshop).

The following functions have been added, as compared with HIM.

Project generator Automatically generates header files that define peripheral I/Os for each CPU. Combination interface with the version management tools Supports the interface with the version management tools provided by the third party. Hierarchy project support Can define multiple subprojects in a project and hierarchically manage them. Network support Provides development environment under WindowsNT CSS.

# RENESAS

# A.6 Features Added between Ver. 5.1 and Ver. 6.0

The features added to version 6.0 of the SuperH RISC engine C/C++ compiler are summarized below.

#### (1) Relaxation of limits

Limits for source programs and command lines have been greatly relaxed.

- File name length: 251 bytes  $\rightarrow$  No limit

- Symbol length: 251 bytes  $\rightarrow$  No limit

- Number of symbols: 32,767 symbols  $\rightarrow$  No limit

- Number of source program rows: C/C++: 32,767 rows, ASM: 65,535 rows  $\rightarrow$  No limit

- C program character string length: 512 characters  $\rightarrow$  32,766 characters

- Assembly program row length: 255 characters  $\rightarrow$  8,192 characters

- Subcommand file row length: ASM: 300 bytes, optlnk: 512 bytes  $\rightarrow$  No limit

- Number of parameters for the Optimizing Linkage Editor rom option: 64 parameters  $\rightarrow$  No limit

#### (2) Hyphens (-) in directory names and filenames

Hyphens (-) can now be specified in directory names and filenames

#### (3) Elimination of copyright notice

By specifying the logo/nologo option, it is now possible to specify whether or not to display a copyright notice.

#### (4) Error message prefixes

Along with support for the error help function in the Integrated Development Environment, the start of error messages in the compiler and Optimizing Linkage Editor have been ascribed prefixes.

#### (5) Addition of fpscr options

If the cpu=sh4 option is specified, and the fpu option is not specified, it is now possible to specify whether to guarantee the FPSCR register precision mode before and after calling on the function.

#### (6) **#pragma extensions**

#pragma extensions can now be written without ().

#### (7) Addition of embedded functions

trace functions have been added.

#### (8) Addition of implicit declarations

\_\_HITACHI\_\_ and \_\_HITACHI\_VERSION\_ \_ are implicitly declared with #define.

#### (9) static label name

In order that static labels inside the file can be referenced by #pragma inline\_asm, the label name has been changed to \_\_\_\_\_\_\$ (name). However, it is displayed as \_\_(name) in the linkage list.

#### (10) Extension and changes to the language specification

• Errors when unions are initialized have been eliminated.

#### Example:

```

union{

char c[4];

} uu={{'a','b','c'}};

```

• It is now possible to substitute a structure and make a declaration at the same time.

# Example: struct{

```

int a, int b;

} s1

void test()

{

struct S s2=s1;

}

```

- The boundary alignment of bool-type data is now 4 bytes.

- Exception processing and template functions are now supported as the C++ language specification.

- The C preprocessor is now ANSI/ISO compliant.

# A.7 Features Added between Ver. 6.0 and Ver. 7.0

From the SuperH RISC engine C/C++ Compiler Ver.7.0 algorithm and code generation has been greatly improved. So the options and generated codes are much different from those of Ver.6.0. The features added to version 7.0 of the SuperH RISC engine C/C++ compiler are summarized below.

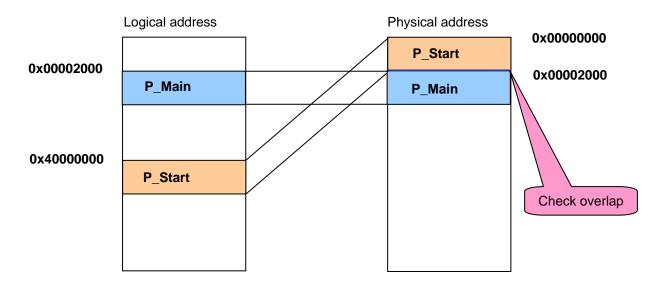

#### (1) External access optimization function (map option support)

This function performs optimization of external variable access and function branch instructions based on the allocated address of the variables and functions at linkage. Optimization is implemented by recompiling the external symbol allocation information files which are output (specified to map option) by the Optimizing Linkage Editor at the time of the first linkage.

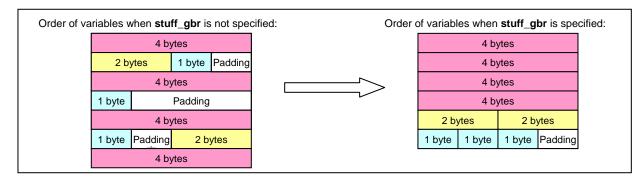

#### (2) Automatic generation of GBR relative access code (gbr option support)

If gbr=auto is specified, the compiler automatically generates GBR settings and GBR relative access code. Before and after a function call, the GBR value is guaranteed. However, GBR-related embedded functions cannot be used.

#### (3) Strengthened speed/size selection options

speed/size selection options (shift, blockcopy, division, approxdiv options) have been added, and it is now possible to make finer size/speed adjustments.

#### (4) Strengthened functions for embedded systems

- Addition of embedded functions Double precision multiplication, SWAP instruction, LDTLB instruction, NOP instruction

- Addition and change of #pragma extension Support for #pragma entry entry function specification and SP setting Support for #pragma stacksize stack size specification Support for #pragma interrupt sp=<variable>+<constant> and sp=&<variable>+<constant>

- Support for section operators Supports functions of coding the size references in C language.

- Relaxation of address cast errors

Errors of cast expressions with regard to address initialization when initializing external variables have been relaxed.

#### (5) Improved libraries

- Support for reentrant libraries If the reent option is specified with the Library Creation Tool, a reentrant library is generated.

- The units of the malloc reserve size and the number of input and output files has been made variable. It is now possible to specify the malloc reserve size with \_sbrk\_size, and the number of input and output files with \_nfiles in the initial settings of the C/C++ library functions. This substantially reduces RAM capacity. If this specification is omitted, the malloc reserve size is 520, and the number of input and output files is 20.

### • Support for easy I/O If the nofloat option is specified with the Library Creation Tool, floating point conversions are not supported, and a small I/O routine is generated.

#### (6) Addition of optimization options (V7.0.06)

#### • Added Options

The following shows the options added to Ver.7.0.06. Uppercase letters indicate the abbreviations and characters underlined indicate the defaults.

|   | ltem                                 | Command Line Format                             | Specification                                                                                                              |

|---|--------------------------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| 1 | Treatment of global variables        | GLOBAL_Volatile = { 0                           | Treat global variables as non-volatile-qualified except variables which are volatile-qualified                             |

|   |                                      | 1 }                                             | Treats global variables as volatile-qualified                                                                              |

| 2 | Optimizing range of global variables | OPT_Range = {All                                | Optimizes all the global variables in a whole function                                                                     |

|   |                                      | NOLoop                                          | Suppresses a motion of global variables out of a loop or optimization of a loop control variable                           |

|   |                                      | NOBlock }                                       | Suppresses an optimization of the global variables cross over a branch or a loop                                           |

| 3 | Deletion of vacant                   | DEL_vacant_loop ={ 0                            | Suppresses a deletion of a vacant loop                                                                                     |

|   | loops                                | 1}                                              | Deletes a vacant loop                                                                                                      |

| 4 | Specification of maximum unroll      | MAX_unroll = <numeric<br>value&gt;</numeric<br> | Specifies the maximum number of loop unroll factor                                                                         |

|   | factor                               | <numeric value="">:1-32</numeric>               | Default : 1                                                                                                                |

|   |                                      |                                                 | (when the speed or loop option is specified, the                                                                           |

|   |                                      |                                                 | default is 2)                                                                                                              |

| 5 | Deletion of assignments before       | INFinite_loop = {0                              | Suppresses a deletion of assignments to global<br>variables before an infinite loop                                        |

|   | an infinite loop                     | 1 }                                             | Deletes assignments to global variables before an infinite loop                                                            |

| 6 | Allocation of global variable        | GLOBAL_Alloc = {0                               | Suppresses register allocation of global variables                                                                         |

|   |                                      | 1}                                              | Allocates registers of global variables                                                                                    |

| 7 | Allocation of struct/union           | STRUCT_Alloc = {0                               | Suppresses register allocation of struct or union members                                                                  |

|   | member                               | 1 }                                             | Allocates registers to struct or union members                                                                             |

| 8 | Propagation of const-qualified       | CONST_Var_propagate = {0                        | Suppresses the propagation of variables which are const-qualified                                                          |

|   | variable                             | 1 \                                             | Propagates variables which are const-qualified                                                                             |

| 9 | Inline expansion of                  | CONST_Load = {Inline                            | Performs inline expansion of constant load                                                                                 |

|   | constant load                        | Literal }                                       | Loads constant data from literal pool<br>Default : When size is specified, up to<br>two or three instructions are expanded |

| 1 | Scheduling of                        | SChedule = {0                                   | Suppresses instruction scheduling                                                                                          |

| 0 | instructions                         |                                                 |                                                                                                                            |

Treatment of global variables

#### GLOBAL\_Volatile

Optimize[Details][Global variables][Treat global variables as volatile qualified]

#### **Command Line Format**

$GLOBAL_Volatile = \{ \underline{0} | 1 \}$

#### Description

When **global\_volatile=0** is specified, the compiler optimizes accesses of the global variables which are non-volatilequalified. So a count or an order of accesses to global variables may differ from that of the C/C++ program.

When **global\_volatile=1** is specified, all the global variables are treated as volatile-qualified. So a count or an order of accesses to global variables may be the same as that of the C/C++ program.

The default for this option is **global\_volatile=**0.

#### Remarks

When **global\_volatile=1** is specified, **schedule=0** becomes the default.

Optimizing range of global variables

#### **OPT\_Range**

Optimize[Details][Global variables][Specify optimizing range :]

#### **Command Line Format**

```

OPT_Range = { <u>All</u> | NOLoop | NOBlock }

```

#### Description

When **opt\_range=all** is specified, the compiler optimizes accesses to all the global variables in a function.

When **opt\_range=noloop** is specified, the compiler does not optimize accesses to the global variables which are used in a loop or a loop conditional expression.

When **opt\_range=noblock** is specified, the compiler does not optimize accesses to the global variable cross over a branch or a loop.

The default for this option is **opt\_range=all**.

#### Example

(1) Example of optimization across a branch (opt\_range=all or noloop is specified)

```

int A, B, C;

void f(int a) {

A = 1;

if (a) {

B = 1;

}

C = A;

}

<source image after optimizing>

void f(int a) {

A = 1;

if (a) {

B = 1;

}

C = 1; /* Deletes reference of variable A and propagates A=1 */

}

```

(2) Example of optimization against loop (opt\_range=all is specified)

```

int A, B, C[100];

void f() {

int i;

for (i=0;i<A;i++) {

C[i] = B;

}

}

<source image after optimizing>

void f() {

int i;

int temp A, temp B;

temp_A = A; /* Remove reference of variable A used in loop conditional expression */

temp_B = B; /* Remove reference of variable B in a loop */

for (i=0;i<temp A;i++) { /* Delete reference of variable A */</pre>

C[i] = temp B; /* Delete reference of variable B */

}

}

```

#### Remarks

Whenever **opt\_range=noloop** is specified, **max\_unroll=1** becomes the default. Whenever **opt\_range=noloblock** is specified, **max\_unroll=1**, **const\_var\_propagate=**0, and **global\_alloc=0** becomes the default.

Deletion of vacant loops

#### DEL\_vacant\_loop

Optimize[Details][Miscellaneous][Delete vacant loop]

#### **Command Line Format**

DEL\_vacant\_loop =  $\{ \underline{0} | 1 \}$

#### Description

When **del\_vacant\_loop=0** is specified, the compiler does not delete a vacant loop.

When **del\_vacant\_loop=1** is specified, the compiler deletes a vacant loop.

The default for this option is **del\_vacant\_loop=0**.

#### Remarks

Note that the default differs between version 7.0.04 and 7.0.06. Up to V7.0.04 : Delete vacant loop V7.0.06 or later : Does not delete vacant loop

Specification of maximum unroll factor

#### MAX\_unroll

Optimize[Details][Miscellaneous][Specify maximum unroll factor :]

#### **Command Line Format**

MAX\_unroll = <numeric value>

#### Description

Specifies the maximum unroll factor when a loop is expanded.

The <numeric value> accepts a decimal number from 1 to 32. If < numeric value > is specified out of the range, an error will occur.

When the **speed** or **loop** option is specified, the default for this option is **max\_unroll=2**.

Otherwise the default for this option is **max\_unroll=1**.

#### Remarks

Whenever **opt\_range=noloop** or **opt\_range=noblock** is specified, the default for this option is **max\_unroll=1**.

Deletion of assignments before an infinite loop

#### INFinite\_loop

Optimize[Details][Global variables]

[Delete assignment to global variables before an infinite loop]

#### **Command Line Format**

INFinite\_loop =  $\{ \underline{0} | 1 \}$

#### Description

When **infinite\_loop=0** is specified, the compiler does not delete an assignment to a global variable before an infinite loop.

When **infinite\_loop=1** is specified, the compiler deletes an assignment before an infinite loop to a global variable which is not referred to in the infinite loop.

The default for this option is **infinite\_loop =0.**

#### Example

```

int A;

void f()

{

A = 1; /* Assignment to variable A */

while(1) {} /* Variable A is not referred in a loop */

}

<source image when specified infinite_loop=1)

void f()

{

/* Delete assignment to variable A */

while(1) {}

}

```

#### Remarks

Note that the default differs between version 7.x (up to V7.0.04) and 7.0.06 or later.

Up to V7.0.04 : Deletes an assignment before an infinite loop to a global variable which is not referred to in the infinite loop

V7.0.06 or later : Does not delete an assignment to a global variable before an infinite loop

Allocation of global variable

#### GLOBAL\_Alloc

Optimize[Details][Global variables][Allocate registers to global variables :]

#### **Command Line Format**

$GLOBAL\_Alloc = \{ 0 \mid \underline{1} \}$

#### Description

When **global\_alloc=0** is specified, the compiler does not allocate registers to global variables.

When global\_alloc=1 is specified, the compiler allocates registers to global variables.

The default for this option is **global\_alloc=1**.

#### Remarks

When opt\_range=noblock is specified, global\_alloc=0 becomes the default.

When **optimize=0** is specified, note that the default differs between version 7.x (up to V.7.0.04) and 7.0.06 or later.

Up to V7.0.04 : Allocates registers to global variables V7.0.06 or later : Does not allocate registers to global variables

Allocation of struct/union member

#### STRUCT\_Alloc

Optimize[Details][Miscellaneous][Allocate registers to struct/union members]

#### **Command Line Format**

STRUCT\_Alloc =  $\{ 0 | \underline{1} \}$

#### Description

When **struct\_alloc=0** is specified, the compiler does not allocate registers to struct or union members.

When **struct\_alloc=1** is specified, the compiler allocates registers to struct or union members.

The default for this option is **struct\_alloc=1**.

#### Remarks

When either opt\_range=noblock or global\_alloc=0, and struct\_alloc=1 is specified, the compiler

allocates registers only to local struct or union members.

When **optimize=0** is specified, note that the default differs between version 7.x (up to V7.0.04) and 7.0.06 or later.

Up to V7.0.04 : Allocate registers to struct or union members

V7.0.06 or later : Does not allocate registers to struct or union members

# **APPLICATION NOTE**

Propagation of const-qualified variable

#### CONST\_Var\_propagate

Optimize[Details][Global variables][Propagate variables which are const qualified :]

#### **Command Line Format**

$CONST_Var_propagate = \{ 0 | 1 \}$

#### Description

When **const\_var\_propagate=0** is specified, the compiler does not propagate global variables which are const-qualified.

When const\_var\_propagate=1 is specified, the compiler propagates global variables which are

#### const-qualified.

The default for this option is **const\_var\_propagate=1**.

#### Example

```

const int X = 1;

int A;

void f() {

A = X;

}

<source image when specified const_var_propagate=1>

void f() {

A = 1; /* Propagates X=1 */

}

```

#### Remarks

When **opt\_range=noblock** is specified, the default for this option is **const\_var\_propagate=0**.

Variables which are const-qualified in C++ program are always propagated even if const\_var\_propagate=0 is specified.

Inline expansion of constant load

#### CONST\_Load

Optimize[Details][Miscellaneous][Load constant value as :]

#### **Command Line Format**

```

CONST_Load = { Inline | Literal }

```

#### Description

When const\_load=inline is specified, the load of all the 2-byte constant data or some 4-byte constant data is expanded.

When **const\_load=literal** is specified, all the 2-byte or 4-byte constant data are loaded from literal pool.

The default for this option is below.

When the **speed** option is specified:

The default is **const\_load=inlin**e.

When the **size** or **nospeed** option is specified:

If 2-byte or 4-byte constant data can be expanded into 2 or 3 instructions respectively,

**const\_load=inline** is applied.

Otherwise the default is **const\_load=litera**l.

#### Example

}

```

int f() {

return (257);

```

(1) When const load=inline or speed option is specified:

MOV #1,R0 ; R0 <- 1 SHLL8 R0 ; R0 <- 256 (1<<8) RTS ADD #1,R0 ; R0 <- 257 (256+1)

(2) When const\_load=literal, size or nospeed is specified:

```

MOV.W L11,R0

RTS

NOP

L11:

.DATA.W H'0101

```

#### SChedule

Optimize[Details][Global variables][Schedule instructions :]

#### **Command Line Format**

SChedule =  $\{ 0 \mid \underline{1} \}$

#### Description

When **schedule=0** is specified, the compiler does not schedule instructions. They will be executed in the order written in the C/C++ program.

When **schedule=1** is specified, the compiler schedules instructions paying attention to the pipeline or superscalar (only SH-4) mechanism.

The default for this option is **schedule=1**.

#### Remarks

When **opt\_range=noblock** is specified, **schedule=0** becomes the default.

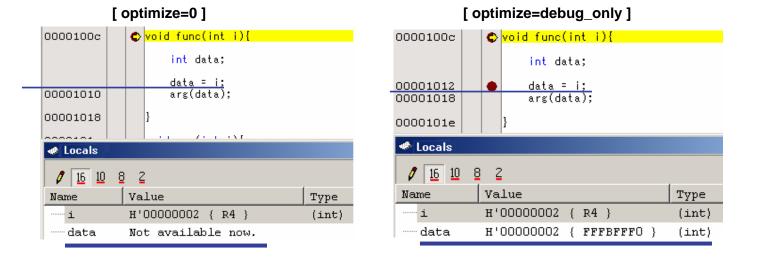

• The default in optimize=0

When **optimize=0** is specified, the defaults of the added options are shown below.

global\_volatile=0

opt\_range=noblock

del\_vacant\_loop=0

max\_unroll=1

infinite\_loop=0

global\_alloc=0

struct\_alloc=0

const\_var\_propagate=0

const\_load=literal

schedule=0

The defaults of the following options differ from optimize=1.

|                     | optimize=0 | optimize=1                         |

|---------------------|------------|------------------------------------|

| opt_range           | noblock    | all                                |

| global_alloc        | 0          | 1                                  |

| struct_alloc        | 0          | 1                                  |

| const_var_propagate | 0          | 1                                  |

| const_load          | literal    | Depending on<br>speed/size/nospeed |

| schedule            | 0          | 1                                  |

# RENESAS

#### • Compatibility in V7 (up to V7.0.04)

The defaults of the following options differ between version 7.x (up to V.7.0.04) and 7.0.06 or later.

(i) Deletion of a vacant loop (del\_vacant\_loop)

Up to V7.0.04 : Deletes a vacant loop

V7.0.06 or later : Does not delete a vacant loop

(ii) Deletion of an assignment before an infinite loop (infinite\_loop)

Up to V7.0.04 : Deletes an assignment before an infinite loop to global variable which is not referred to in the infinite loop

V7.0.06 or later : Does not deletes assignment to global variable before an infinite loop

The specification of the following with **optimize=0** differs between version 7.x (up to V.7.0.04) and 7.0.06 or later.

(i) Allocation of global variables (global\_alloc)

Up to V7.0.04 : Allocates global variables to registers

V7.0.06 or later : Does not allocate global variables to registers

(ii) Allocation of struct or union members (struct\_alloc)

Up to V7.0.04 : Allocates struct or union members to registers

V7.0.06 or later : Does not allocate struct or union members to registers

#### • System of Optimization

The levels of the optimization of global variables are shown below. When one of those levels is selected in HEW, the options related to the optimization of global variables can be controlled together.

The level is set at Optimize[Details][Level :].

(i) Level 1

All the optimizations of global variables are suppressed.

```

global_volatile=1

opt_range=noblock

infinite_loop=0

global_alloc=0

const_var_propagate=0

schedule=0

```

#### (ii) Level 2

The optimizations of global variables which are not volatile-qualified are done within a basic block

(sequence of instructions which have no labels or branches except at beginning or end).

```

global_volatile=0

opt_range=noblock

infinite_loop=0

global_alloc=0

```

const\_var\_propagate=0

schedule=1

#### (iii) Level 3

All the optimizations of global variables which are non-volatile-qualified are done.

```

global_volatile=0

opt_range=all

infinite_loop=0

global_alloc=1

const_var_propagate=1

schedule=1

```

(iv) Custom

User specifies these options according to the programs.

When level 1, level 2, or level 3 is specified, above-mentioned options cannot be changed separately.

• The followings are features added to Optimizing Linkage Editor.

#### (7) Support for wild cards

It is possible to specify wild cards for input files and start option section names.

#### (8) Search path

It is possible to specify search paths for multiple input files and library files with the environment variable (HLNK\_DIR).

#### (9) Separate output of load modules

It is possible to perform separate output of absolute load module files.

#### (10) Changed error levels

The error level for messages for information, warnings, and error levels, and whether or not to output them can be changed individually.

#### (11) Support for binary and HEX

It is now possible to input and output binary files.

In addition, it is now possible to choose to output in the Intel HEX format.

#### (12) Output of the stack capacity usage information

With the stack option, it is possible to output data files for the stack analysis tools.

#### (13) Debug information deletion tool

With the strip option, it is possible to delete just the debug information within the load module files and library files.

The features added to version 7.1 of the SuperH RISC engine C/C++ Optimizing Linkage Editor are summarized below.

#### (14) Output external symbol allocation information files (map option support)

If the map option is specified, the compiler generates an external symbol allocation information file to be used for external variable access optimization.

### A.8 Features Added between Ver. 7.0 and Ver. 7.1

• The features added to version 7.1 of the SuperH RISC engine C/C++ compiler are summarized below.

#### (1) Strengthened optimization

#### (a) Deletion of EXTU immediately after MOVT

Deletes the unnecessary EXTU immediately after MOVT. (As nothing besides 1 or 0 can be set, EXTU is unnecessary)

| Before optimization |                    |         | Af             | After optimization |   |  |

|---------------------|--------------------|---------|----------------|--------------------|---|--|

| _f:                 |                    |         | _f:            |                    |   |  |

| MOV.L               | L12+2,R6           | ;       | MOV.L          | L12+2,R6           | ; |  |

| _a1                 |                    |         | _a1            |                    |   |  |

| MOV.B               | @R6,R0             |         | MOV.B          | @R6,R0             |   |  |

| TST                 | #128,R0            |         | TST            | #128,R0            |   |  |

| MOVT                | RO                 |         | MOVT           | R0                 |   |  |

| EXTU.B              | R0,R0              |         |                |                    |   |  |

|                     |                    |         | _              |                    |   |  |

| As nothing b        | besides 1 or 0 car | n be se | t for R0, EXTU | is unnecessary.    |   |  |

(b) Deletion of EXTU after a right shift of a zero extended register

Even if a zero extended register is zero extended after a right shift, the value does not change so it is deleted.

|     | Before optimization |           |     | After op | otimization |

|-----|---------------------|-----------|-----|----------|-------------|

| f:  |                     |           | f:  |          |             |

|     | MOV.L               | L13+2,R2; |     | MOV.L    | L13+2,R2;   |

| _a2 |                     |           | _a2 |          |             |

|     | MOV                 | #1,R5     |     | MOV      | #1,R5       |

|     | MOV.W               | @R2,R6    |     | MOV.W    | @R2,R6      |

|     | EXTU.W              | R6,R6     |     | EXTU.W   | R6,R6       |

|     | MOV                 | R6,R2     |     | MOV      | R6,R2       |

|     | SHLR2               | R2        |     | SHLR2    | R2          |

|     | SHLR                | R2        |     | SHLR     | R2          |

|     | EXTU.W              | R2,R2     |     | CMP/GE   | R5,R2       |

|     | CMP/GE              | R5,R2     |     |          | :           |

|     |                     | :         |     |          |             |

As the upper 2 bytes are zero-cleared with EXTU, the value does not change even if EXTU is performed again.

#### (c) Unifying consecutive AND

**ENESAS**

If ANDs to the same variable are made consecutively, they are grouped into 1 AND.

| Before optimization |                     |                |   | After | optimization |   |

|---------------------|---------------------|----------------|---|-------|--------------|---|

| _f:                 |                     |                |   | _f:   |              |   |

|                     | MOV.L               | L11+2,R6       | ; | MOV.L | L11+2,R6     | ; |

| _a5                 |                     |                |   | _a5   |              |   |

|                     | MOV.B               | @R6,R0         |   | MOV.B | @R6,R0       |   |

| Z                   | ND                  | #3 <b>,</b> R0 |   | RTS   |              |   |

| F                   | RTS                 |                |   | AND   | #1,R0        |   |

| A                   | ND                  | #1,R0          |   |       |              |   |

|                     |                     |                |   |       |              |   |

| Grou                | Grouped into 1 AND. |                |   |       |              |   |

#### (d) Bit field comparison and combination

Unifies evaluation (TST#n, R0) of multiple bit fields.

| Before             | optimization             | After c            | ptimization       |

|--------------------|--------------------------|--------------------|-------------------|

| _f:                |                          | _f:                |                   |

| :                  |                          | :                  |                   |

| MOV                | R4,R0                    | MOV                | R4,R0             |

| TST                | #64,R0                   | TST                | #96,R0            |

| BF                 | L12                      | BF                 | L12               |

| TST                | #32,R0                   | MOV                | R6,R0             |

| BF                 | L12                      | :                  |                   |

| MOV                | R6,R0                    |                    |                   |

| :                  |                          |                    |                   |

|                    |                          |                    |                   |

| Unifies the criter | ia of the bit fields, ar | nd replaces them w | ith 1 evaluation. |

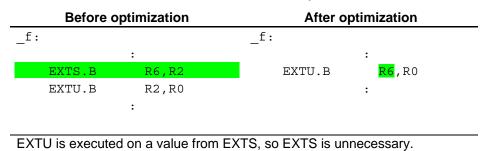

(e) Deletion of EXTS of consecutive EXTS+EXTU

After EXTS, if EXTU of the same size is executed, EXTS is unnecessary so it is deleted.

#### (f) Deletion of MOVT(+XOR)+EXTU+CMP/EQ

Deletes the unnecessary MOVT(+XOR)+EXTU+CMP/EQ after TST, and makes a conversion so as to reference the T bit with a direct branch instruction.

|          | Before o    | ptimization    |   |      | After opti | mization  |

|----------|-------------|----------------|---|------|------------|-----------|

| _f:      |             |                |   | _f:  |            |           |

|          | :           |                |   |      | :          |           |

|          | TST         | #4 <b>,</b> R0 |   |      | TST        | #4,R0     |

|          | MOVT        | R0             |   |      | MOV.L      | L23+6,R6; |

|          | MOV.L       | L23+6,R6       | ; | _st2 |            |           |

| _st2     |             |                |   |      | MOV.B      | @R6,R0    |

|          | XOR         | #1 <b>,</b> R0 |   |      | BT L16     |           |

|          | EXTU.B      | R0,R0          |   |      |            | :         |

|          | CMP/EQ      | #1 <b>,</b> R0 |   |      |            |           |

|          | MOV.B       | @R6,R0         |   |      |            |           |

|          | BF          | L16            |   |      |            |           |

|          |             | :              |   |      |            |           |

|          |             |                |   |      |            |           |

| Directly | y reference | es the T bit.  |   |      |            |           |

(g) AND #imm, R0+CMP/EQ #imm, R0  $\rightarrow$  TST #imm, R0

#### Replaces AND #imm, R0+CMP/EQ #imm, R0 with TST #imm, R0.

| Before | optimization | After | optimization |

|--------|--------------|-------|--------------|

| L17:   |              | L17:  |              |

| MOV.B  | @R6,R0       | MOV.B | @R6,R0       |

| AND    | #1,R0        | TST   | #1,R0        |

| CMP/EQ | #1,R0        | BT    | L19          |

| BF     | L19          | MOV.B | @R5,R0       |

| MOV.B  | @R5,R0       | AND   | #1,R0        |

| AND    | #1,R0        |       |              |

|        |              |       |              |

#### (h) Deletion of EXTU when comparing (==) unsigned char and constant

Deletes the unnecessary EXTU when comparing the unsigned char and constant immediately after the load.

| Before of        | optimization       |     | After o      | optimization |   |

|------------------|--------------------|-----|--------------|--------------|---|

| _f:              |                    |     | _f:          |              |   |

| MOV.L            | L11,R6             | ;   | MOV.L        | L11,R6       | ; |

| _b               |                    |     | _b           |              |   |

| MOV.B            | @R6,R2             |     | MOV.B        | @R6,R2       |   |

| MOV              | #-                 |     | MOV          | #-           |   |

| 128,R6; H'FF     | FFFF80             |     | 128,R6; H'FF | FFFF80       |   |

| EXTU.B           | R6,R6              |     | CMP/EQ       | R6,R2        |   |

| EXTU.B           | R2,R2              |     | MOVT         | R2           |   |

| CMP/EQ           | R6,R2              |     | MOV.L        | L11+4,R6     | ; |

| MOVT             | R2                 |     | _a           |              |   |

| MOV.L            | L11+4,R6           | ;   | RTS          |              |   |

| _a               |                    |     | MOV.B        | R2,@R6       |   |

| RTS              |                    |     |              |              |   |

| MOV.B            | R2,@R6             |     |              |              |   |

|                  |                    |     |              |              |   |

| Deletes the unne | ecessary extension | on. |              |              |   |

(i) Deletion of extension after LOAD / before STORE of bit field

Deletes the unnecessary extension of the bit field after LOAD and before STORE.

| Before           | optimization        | After | optimization |

|------------------|---------------------|-------|--------------|

| _f:              |                     | _f:   |              |

| MOV.L            | L11+2,R6;_st        | MOV.L | L11+2,R6;_st |

| MOV.B            | @R6,R2              | MOV.B | @R6,R2       |

| EXTU.B           | R2,R0               | OR    | #128,R0      |

| OR               | #128,R0             | :     |              |

| :                |                     |       |              |

|                  |                     |       |              |

| Deletes the unne | ecessary extension. |       |              |

# RENESAS

#### (j) Deletion of copy when evaluating switch-case

Deletes the copy of the value when performing each case evaluation of switch statements.

| Before optimizati         | on    | After optimizati | on    |

|---------------------------|-------|------------------|-------|

| _f:                       | -     | _f:              |       |

|                           |       |                  |       |

|                           | :     |                  | :     |

| MOV                       | R0,R2 | MOV              | R0,R2 |

| MOV                       | R2,R0 | MOV              | R2,R0 |

| CMP/EQ                    | #1,R0 | CMP/EQ           | #1,R0 |

| BT                        | L24   | BT               | L24   |

| CMP/EQ                    | #2,R0 | CMP/EQ           | #2,R0 |

| BT                        | L26   | BT               | L26   |

| MOV                       | R2,R0 | CMP/EQ           | #3,R0 |

| CMP/EQ                    | #3,R0 | BT               | L28   |

| BT                        | L28   | CMP/EQ           | #4,R0 |

| MOV                       | R2,R0 | BT               | L30   |

| CMP/EQ                    | #4,R0 |                  | :     |

| BT                        | L30   |                  |       |

| MOV                       | R2,R0 |                  |       |

| :                         |       |                  |       |

|                           |       |                  |       |

| Deletes the unnecessary c | opv.  |                  |       |

#### (k) Unifying consecutive OR

If ORs to the same variable are made consecutively, they are grouped into 1 OR.

| Before         | optimization |   | After | optimization |   |

|----------------|--------------|---|-------|--------------|---|

| _f:            |              |   | _f:   |              |   |

| MOV.L          | L11+2,R6     | ; | MOV.L | L11+2,R6     | ; |

| _a5            |              |   | _a5   |              |   |

| MOV.B          | @R6,R0       |   | MOV.B | @R6,R0       |   |

| OR             | #3,R0        |   | RTS   |              |   |

| RTS            |              |   | OR    | #3,,R0       |   |

| OR             | #1,R0        |   |       |              |   |

|                |              |   |       |              |   |

| Grouped into 1 | OR.          |   |       |              |   |

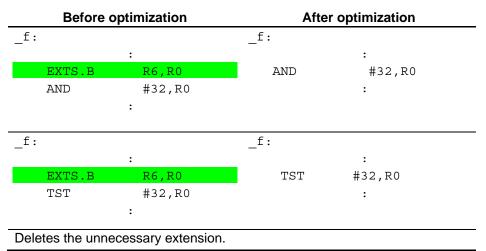

#### (1) Deletion of EXTS immediately in front of AND #imm,R0 or TST #imm,R0

Deletes the unnecessary extension immediately in front of;

#### (i) AND #imm,R0

(ii) TST #imm,R0

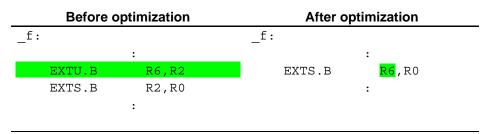

(m) Deletion of EXTU of consecutive EXTU+EXTS

After EXTU, if EXTS of the same size is executed, EXTU is unnecessary so it is deleted.

EXTS is executed on a value from EXTU, so EXTU is unnecessary.

(n) Deletion of EXTU immediately after XOR #imm,R0(OR,AND) after MOVT

Deletes the unnecessary EXTU immediately after;

(i) XOR #imm,R0

(ii) OR #imm,R0

(iii) AND #imm,R0

after MOVT

| E         | Before optimization       |      | After optimization |

|-----------|---------------------------|------|--------------------|

|           | :                         |      | :                  |

| MOVT      | R0                        | MOVT | RO                 |

| XOR       | #1,R0                     | RTS  |                    |

| RTS       |                           | XOR  | #1,R0              |

| EXTU.B    | R0,R0                     |      |                    |

|           |                           |      |                    |

| MOVT      | R0                        |      | :                  |

| OR        | #2,R0                     | MOVT | RO                 |

| RTS       |                           | RTS  |                    |

| EXTU.B    | R0,R0                     | OR   | #2,R0              |

|           |                           |      |                    |

|           | :                         |      | :                  |

| MOVT      | R0                        | MOVT | R0                 |

| AND       | #1,R0                     | RTS  |                    |

| RTS       |                           | AND  | #1,R0              |

| EXTU.B    | R0,R0                     |      |                    |

|           |                           |      |                    |

| Deletes t | he unnecessary extension. |      |                    |

#### (o) Deletion of unnecessary EXTS when making comparison

Deletes redundant EXTS re-output when comparing registers after sign expansion.

| Before | optimization | After o | ptimization |  |

|--------|--------------|---------|-------------|--|

| _f:    |              | _f:     |             |  |

|        | :            |         | :           |  |

| EXTS.B | R6,R6        | CMP/GT  | R6,R2       |  |

| CMP/GT | R6,R2        | BF      | L13         |  |

| BF     | L13          |         | :           |  |

|        | :            |         |             |  |

|        |              |         |             |  |

If R6 is already extended previously, EXTS is unnecessary.

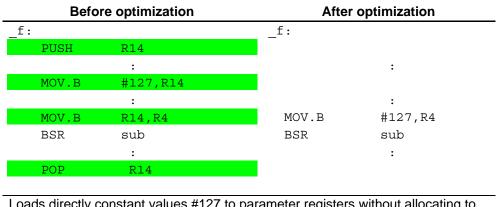

(p) Disabling (immediately) of allocation of constant values to registers

Disables allocation of functional parameter constants (-128 to 127) to registers.

Loads directly constant values #127 to parameter registers without allocating to registers.

## (q) Strengthened DT instructions

Performs DT instruction for variables allocated to registers.

| ore optimization | After                                                 | optimization                                                                         |

|------------------|-------------------------------------------------------|--------------------------------------------------------------------------------------|

|                  | _f:                                                   |                                                                                      |

| L16+2,R6; _x     | MOV.L                                                 | L16+2,R6; _x                                                                         |

| @R6,R2           | MOV.L                                                 | @R6,R2                                                                               |

| #-1,R2           | DT xxxx                                               | R2 xxxx                                                                              |

| R2,R2            | BT/S                                                  | L12                                                                                  |