# Pod for IE850 In-circuit Emulator RTE7701460EPA00000R

User's Manual

Target Devices: RH850/D1x Series

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

#### Notice

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information.

- 2. Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other disputes involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawing, chart, program, algorithm, application examples.

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copy or otherwise misappropriation of Renesas Electronics products.

- 5. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots etc.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

- Renesas Electronics products are neither intended nor authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems, surgical implantations etc.), or may cause serious property damages (space and undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for which the product is not intended by Renesas Electronics.

- 6. When using the Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat radiation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions or failure or accident arising out of the use of Renesas Electronics products beyond such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please ensure to implement safety measures to guard them against the possibility of bodily injury, injury or damage caused by fire, and social damage in the event of failure or malfunction of Renesas Electronics products, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures by your own responsibility as warranty for your products/system. Because the evaluation of microcomputer software alone is very difficult and not practical, please evaluate the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please investigate applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive carefully and sufficiently and use Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall not use Renesas Electronics products or technologies for (1) any purpose relating to the development, design, manufacture, use, stockpiling, etc., of weapons of mass destruction, such as nuclear weapons, chemical weapons, or biological weapons, or missiles (including unmanned aerial vehicles (UAVs)) for delivering such weapons, (2) any purpose relating to the development, design, manufacture, or use of conventional weapons, or (3) any other purpose of disturbing international peace and security, and you shall not sell, export, lease, transfer, or release Renesas Electronics products or technologies to any third party whether directly or indirectly with knowledge or reason to know that the third party or any other party will engage in the activities described above. When exporting, selling, transferring, etc., Renesas Electronics products or technologies, you shall comply with any applicable export control laws and regulations promulgated and administered by the governments of the countries asserting jurisdiction over the parties or transactions.

- 10. Please acknowledge and agree that you shall bear all the losses and damages which are incurred from the misuse or violation of the terms and conditions described in this document, including this notice, and hold Renesas Electronics harmless, if such misuse or violation results from your resale or making Renesas Electronics products available any third party.

- 11. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

#### **Important**

Before using this product, be sure to read this user's manual carefully. Keep this user's manual, and refer to it when you have questions about this product.

#### Emulator:

"Emulator" in this document collectively refers to the following products manufactured by Renesas Electronics Corp.

- (1) IE850 emulator main unit

- (2) Pod

"Emulator" herein encompasses neither the customer's target system nor the host machine.

#### Purpose of use of the emulator:

This emulator is a device to support the development of systems that use products from the RH850/D1x series of Renesas microcontrollers. It provides support for system development in both software and hardware.

Be sure to use this emulator correctly according to said purpose of use. Please avoid using this emulator other than for its intended purpose of use.

#### For those who use this emulator:

This emulator can only be used by those who have carefully read the user's manual and know how to use it. Use of this emulator requires basic knowledge of electric circuits, logical circuits, and MCUs.

#### When using the emulator:

- (1) This product is a development-support unit for use in your program development and evaluation stages. When a program you have finished developing is to be incorporated in a mass-produced product, the judgment as to whether it can be put to practical use is entirely your own responsibility, and should be based on evaluation of the device on which it is installed and other experiments.

- (2) In no event shall Renesas Electronics Corp. be liable for any consequence arising from the use of this product.

- (3) Renesas Electronics Corp. strives to provide workarounds for and correct trouble with products malfunctions, with some free and some incurring charges. However, this does not necessarily mean that Renesas Electronics Corp. guarantees the provision of a workaround or correction under any circumstances.

- (4) The product covered by this document has been developed on the assumption that it will be used for program development and evaluation in laboratories. Therefore, it does not fall within the scope of applicability of the Electrical Appliance and Material Safety Law and protection against electromagnetic interference when used in Japan.

- (5) Renesas Electronics Corp. cannot predict all possible situations and possible cases of misuse that carry a potential for danger. Therefore, the warnings in this user's manual and the warning labels attached to the emulator do not necessarily cover all such possible situations and cases. The customer is responsible for correctly and safely using this emulator.

- (6) The product covered by this document has not been through the process of checking conformance with UL or other safety standards and IEC or other industry standards in countries other than Japan. This fact must be taken into account when the product is taken from Japan to another country.

- (7) Renesas Electronics Corp. will not assume responsibility for direct or indirect damage caused by an accidental failure or malfunction of this emulator.

#### When disposing of the emulator:

Penalties may be applicable for incorrect disposal of this waste, in accordance with your national legislation.

#### Usage restrictions:

The emulator has been developed as a means of supporting system development by users. Therefore, do not use it as an embedded device in other equipment. Also, do not use it to develop systems or equipment for use in the following fields.

- (1) Transportation and vehicular

- (2) Medical (equipment that has an involvement in human life)

- (3) Aerospace

- (4) Nuclear power control

- (5) Undersea repeaters

If you are considering the use of the emulator for one of the above purposes, please be sure to consult your local distributor.

#### About product changes:

We are constantly making efforts to improve the design and performance of this emulator. Therefore, the specification or design of this emulator, or this user's manual, may be changed without prior notice.

#### About rights:

- (1) We assume no responsibility for any damage or infringement on patent rights or any other rights arising from the use of any information, products or circuits presented in this user's manual.

- (2) The information or data in this user's manual does not implicitly or otherwise grant a license to patent rights or any other rights belonging to Renesas or to a third party.

- (3) This user's manual and this emulator are copyrighted, with all rights reserved by Renesas. This user's manual may not be copied, duplicated or reproduced, in whole or part, without prior written consent from Renesas.

#### About diagrams:

Some diagrams in this user's manual may differ from the objects they represent.

# **Precautions for Safety**

This chapter, by showing the relevant diagrammatic symbols and their meanings, describes the precautions which should be taken in order to use this product safely and properly. Be sure to read and understand this chapter before using this product. Contact us if you have any questions about the precautions described here.

**WARNING** indicates a potentially dangerous situation that will cause death or heavy wound unless it is avoided.

**CAUTION** indicates a potentially dangerous situation that will cause a slight injury or a medium-degree injury unless it is avoided.

In addition to the two above, the following are also used as appropriate.

$\triangle$  means WARNING or CAUTION.

Example:

Example:

means A FORCIBLE ACTION.

Example:

# **⚠ WARNING**

Warnings for AC Power Supply:

If the separately sold AC power cable for the power adaptor does not fit the receptacle, do not alter the AC power cable and do not plug it in forcibly. Failure to comply may cause electric shock and/or fire.

Use an AC power cable which complies with the safety standard of the country.

Do not touch the plug of the AC power cable when your hands are wet. This may cause electric shock.

This product is connected signal ground with frame ground. If your developing product is transformless (not having isolation transformer of AC power), this may cause electric shock. Also, this may give an unrepairable damage to this product and your developing one. While developing, connect AC power of the product to commercial power through isolation transformer in order to avoid these dangers.

Connect the plug of the AC power cable to the outlet when connecting this emulator and the target system in order to eliminate differences in potential between the grounds of the emulator and of the user's system.

If other equipment is connected to the same branch circuit, care should be taken not to overload the circuit.

When installing this equipment, insure that a reliable ground connection is maintained.

If you smell a strange odor, hear an unusual sound, or see smoke coming from this product, then disconnect power immediately by unplugging the AC power cable from the outlet. Do not use this as it is because of the danger of electric shock and/or fire. In this case, contact your local distributor.

Before setting up this emulator and connecting it to other devices, turn off power or remove a power cable to prevent injury or product damage.

# **⚠ WARNING**

# Warnings to Be Taken for This Product:

Do not disassemble or modify this product. Personal injury due to electric shock may occur if this product is disassembled and modified. Disassembling and modifying the product will void your warranty.

Make sure nothing falls into the cooling fan on the top panel, especially liquids, metal objects, or anything combustible.

Note the following point on products which have a cooling fan.

When the fan does not operate due to, for example, a fault, the temperature of the emulator may be high enough to potentially cause injuries (such as burns) on contact. Accordingly, if the fan does not operate after the emulator is turned on, turn the emulator off immediately and send it to be repaired.

#### Warning for Installation:

Do not set this product in water or areas of high humidity. Make sure that the product does not get wet. Spilling water or some other liquid into the product may cause unrepairable damage.

#### Warning for Use Environment:

Care should be taken to ensure that the emulator is not used at temperatures exceeding the maximum ambient temperature.

# **↑** CAUTION

Point for Caution Regarding the Power Adaptor:

Use only the dedicated power adaptor which is separately sold. Also, do not use the power adaptor for other equipment.

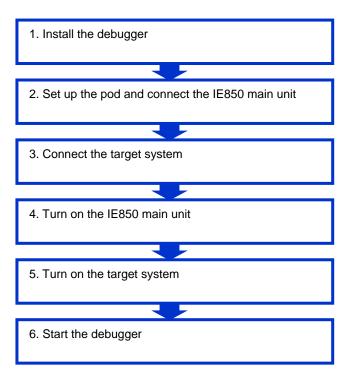

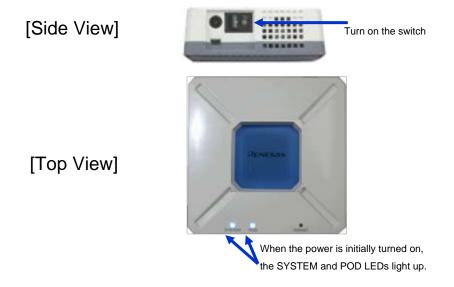

#### Cautions to Be Taken for Turning On the Power:

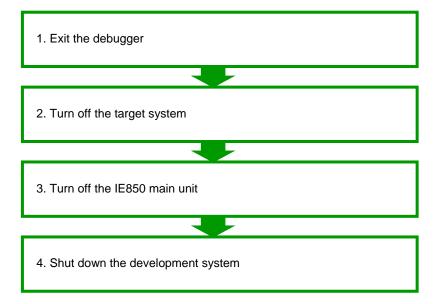

Take the steps below to turn the power to the emulator ON or OFF. Not following the order might cause damage to the target system or emulator.

When turning on the power: (1) Turn on the emulator; (2) turn on the target system; (3) connect the debugger (emulator software)

When turning off the power: (1) Disconnect the debugging session (emulator software); (2) turn off the target system; (3) turn off the emulator

## Cautions to Be Taken for Handling This Product:

Use caution when handling the emulator. Be careful not to apply a mechanical shock.

Do not touch the connector pins of the emulator and the target system directly. Doing so may lead to the discharge of static electricity and so damage the internal circuits.

When attaching and removing the pod cable, hold a fixture (such as a connector) to avoid pulling the pod cable. Do not pull the emulator and board by the communications interface cable or the cable for connecting the target system since this might lead to the breaking of wires in the pod cable. Also, do not flex the pod cable excessively when installing the cable since this might lead to the breaking of wires in the cable.

Do not use inch-size screws for this equipment. The screws used in this equipment are all ISO (meter-size) type screws.

#### Caution to Be Taken for System Malfunctions:

If the emulator malfunctions because of interference like external noise, do the following to remedy the trouble.

- (1) Exit the debugger (emulator software), and shut OFF the emulator and the target system.

- (2) After a lapse of 10 seconds, turn ON the power of the emulator and the target system again, then launch the debugger (emulator software).

# **↑** CAUTION

Note on Heat Generation While the Product is in Use:

Using this product for a long time might cause the product to have a high temperature. If this is the case, care must be taken to avoid injuries due to the heat such as low temperature burns.

Note on the Cover of the Emulation Pod:

Be sure to use the product with the cover of the emulation pod in place.

Note on Transporting the Product:

When sending your product for repair, use the packing box and cushioning material supplied with the product when it was delivered to you and specify caution in handling (handling as precision equipment). If packing of your product is not complete, it may be damaged during transportation. When you pack your product in a bag, make sure to use the conductive plastic bag supplied with the product. If you use a different bag, it may lead to further trouble with your product due to static electricity.

Caution to Be Taken for Disposal:

Penalties may be applicable for incorrect disposal of this waste, in accordance with your national legislation.

European Union Regulatory Notices:

The WEEE (Waste Electrical and Electronic Equipment) regulations put responsibilities on producers for the collection and recycling or disposal of electrical and electronic waste. Return of WEEE under these regulations is applicable in the European Union only. This equipment (including all accessories) is not intended for household use. After use the equipment cannot be disposed of as household waste, and the WEEE must be treated, recycled and disposed of in an environmentally sound manner.

Renesas Electronics Europe GmbH can take back end of life equipment, register for this service at "http://www.renesas.eu/weee".

# **How to Use This Manual**

Readers This manual is intended for users who wish to perform debugging using the

RTE7701460EPA00000R (generic name: pod). The readers of this manual are assumed to be familiar with the device functions and usage, and to have knowledge of debuggers.

Purpose This manual is intended

This manual is intended to give users an understanding of the basic specifications and correct usage of the pod.

**Organization** This manual is divided into the following sections.

Overview

- Names and Functions of Hardware

- Setup Procedure

- Notes

- Optional Product

- Maintenance and Warranty

**How to Read This Manual**

It is assumed that the readers of this manual have general knowledge in the fields of electrical engineering, logic circuits, and microcontrollers. This manual describes the basic setup procedures and how to set switches.

To understand the overall functions and usages of the IE850

→ Read this manual in the order of Contents.

To know the manipulations, command functions, and other software-related settings of the IE850

→ See the user's manual of the debugger to be used.

Conventions

Note: Footnote for item marked with Note in the text

Caution: Information requiring particular attention

Remark: Supplementary information

Numeric representation: Binary ... xxxx or xxxxB

Decimal ... xxxx

Hexadecimal ... xxxxH

Prefix indicating power of 2 (address space, memory capacity):

K (kilo):  $2^{10} = 1,024$ M (mega):  $2^{20} = 1,024^2$

# Terminology

The meanings of the terms used in this manual are described in the table below.

| Term          | Meaning                                                                                                                        |

|---------------|--------------------------------------------------------------------------------------------------------------------------------|

| Target device | This is the device to be emulated.                                                                                             |

| Target system | This is the system to be debugged (system provided by the user). This includes the hardware and software provided by the user. |

| IE850         | Name for IE850 emulator systems in general.                                                                                    |

| IE850 main    | QB-V850E2                                                                                                                      |

| Pod           | The pod is a peripheral of the IE850 main unit and serves as the interface with the target system.                             |

| Emulator      | This is the product to emulate the target device. Refers to the IE850 main unit and pod in this document.                      |

#### **Related Documents**

Please refer to the related documents listed below in addition to this manual before using the product.

|                  | Name of documents                                                                                                      | Document No. |

|------------------|------------------------------------------------------------------------------------------------------------------------|--------------|

| Release note     | E1/E20/E2 Emulator for the RH850 Family and the RH850 Pod for IE850 Release Note (Restrictions on the Emulator and the | R20UT3695E   |

| IE850 main unit  | Pod when Used with CS+)  Main unit for IE850 In-circuit Emulator                                                       | R20UT0824E   |

| Exchange adaptor | QB-V850E2 User's Manual  RTE7701412CBF484T000R                                                                         | R20UT2991E   |

| (EA)             | Exchange Adaptor for Connecting RH850/D1x Series in 484-<br>pin 1.0-mm-pitch BGA                                       |              |

|                  | RTE7701410CBF376T000R  Exchange Adaptor for Connecting RH850/D1x Series in 376-                                        | R20UT2992E   |

|                  | pin 1.0-mm-pitch BGA  RTE7701461CBF272T000R  Exchange Adaptor for Connecting RH850/D1x Series in 272-                  | R20UT3899E   |

|                  | pin 1.0-mm-pitch BGA  RTE7701463CFK176T000R  Exchange Adaptor for Connecting RH850/D1x Series in 176-                  | R20UT3900E   |

|                  | pin 0.5-mm-pitch LFQFP  RTE7701422CFK144T000R  Exchange Adaptor for Connecting RH850/D1x Series in 144-                | R20UT3901E   |

|                  | pin 0.5-mm-pitch LFQFP (Former type number: RTE7701401CFK144T000R)                                                     |              |

|                  | RTE7701421CFK144T000R  Exchange Adaptor for Connecting RH850/D1x Series in 144- pin 0.5-mm-pitch LFQFP                 | R20UT3902E   |

Caution: Related documents listed above are subject to change without prior notice. Thus, make sure that you have the latest documents for use in design.

# **Table of Contents**

| Importa  | nt                                                     | 3   |

|----------|--------------------------------------------------------|-----|

| Precauti | ions for Safety                                        | 5   |

| How to   | Use This Manual                                        | 10  |

| 1. Overv | view                                                   | 16  |

| 1.1 Ha   | ardware specification                                  | 17  |

| 1.2 Sy   | ystem overview                                         |     |

| 1.3 Fu   | ınctional overview                                     | 22  |

| 1.3.1    | Program execution function                             | 24  |

| 1.3.2    | Reset                                                  | 24  |

| 1.3.3    | Break (Program execution stop)                         | 24  |

| 1.3.4    | Event (Detection of specific operations)               | 25  |

| 1.3.5    | Trace (Program execution history)                      | 25  |

| 1.3.6    | Performance measurement                                | 26  |

| 1.3.7    | Masks                                                  | 27  |

| 1.3.8    | Real-time RAM monitor                                  |     |

| 1.3.9    | Change of direct memory                                |     |

| 1.3.10   | 1                                                      |     |

|          | egulatory notices                                      | 28  |

|          | verview of emulation                                   |     |

| 1.6 Pa   | ackage contents                                        | 30  |

| 2 Name   | es and Functions of Hardware                           | 31  |

|          | od                                                     |     |

|          | 850 main unit                                          |     |

|          |                                                        |     |

| 3. Setup | Procedure                                              | 34  |

| 3.1 In   | stalling the debugger                                  | 34  |

| 3.2 Se   | etting up the IE850 main unit                          |     |

| 3.3 Se   | etting up the pod and connecting the IE850 main unit   | 35  |

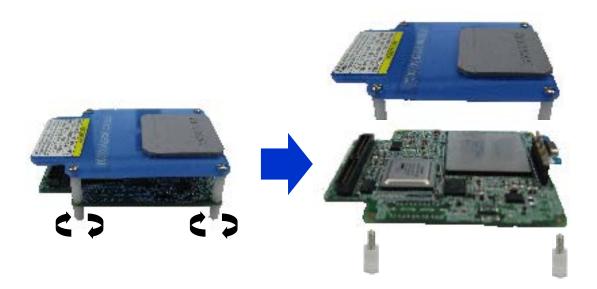

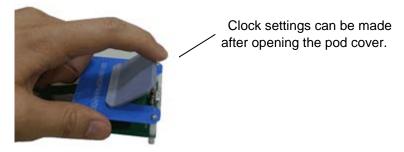

| 3.3.1    | Removing pod cover                                     |     |

| 3.3.2    | Replacing the clock                                    |     |

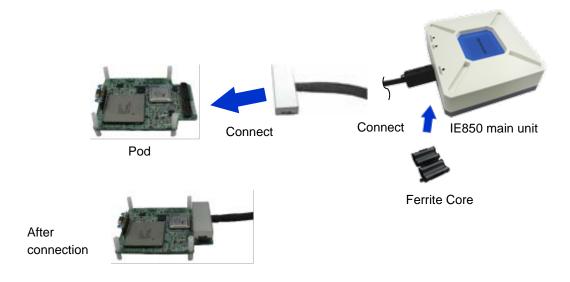

| 3.3.3    | Connecting the IE850 main unit to the pod              | 36  |

| 3.4 Co   | onnecting the target system                            |     |

| 3.4.1    | Connecting the pod and target system                   |     |

| 3.4.2    | Connecting the USB cable and AC adaptor                | 39  |

| 3.5 Tu   | urning on the IE850 main unit                          |     |

| 3.6 Tu   | urning on the target system                            | 40  |

| 3.7 St   | arting the debugger                                    | 40  |

| 3.8 Sh   | nut down procedure                                     | 40  |

| 1 Notes  | S                                                      | Л 1 |

|          |                                                        |     |

|          | otes on differences between actual device and emulator |     |

| 4.1.1    | Behavior after target system is powered on             |     |

| 4.1.2    | Downloaded programs                                    |     |

| 4.1.3    | Function of on-chip debugging emulator                 |     |

| 4.1.4    | DBTRAP instruction                                     |     |

| 4.1.5    | Serial programming function.                           |     |

| 4.1.6    | Halt mode (skipped number)                             | 41  |

| 4.1.7   | Current drawn                                                                               |           |

|---------|---------------------------------------------------------------------------------------------|-----------|

| 4.1.8   | ECC errors                                                                                  |           |

| 4.1.9   | OTP flag                                                                                    | 42        |

| 4.1.10  | Operations in response to resets and interrupts when an emulator is in use (skipped number) |           |

| 4.1.11  | Option byte register                                                                        |           |

| 4.1.12  | Oscillator                                                                                  | 42        |

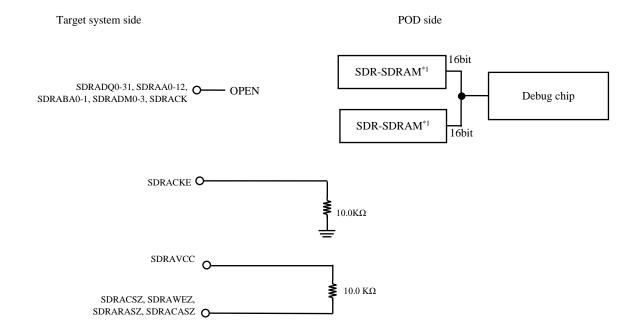

| 4.1.13  | SDR-SDRAM interface                                                                         | 42        |

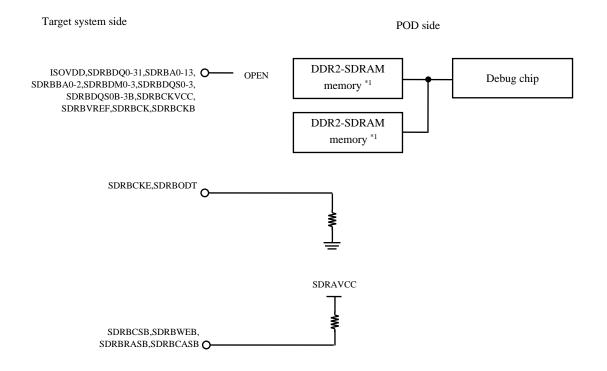

| 4.1.14  | DDR2-SDRAM interface                                                                        | 42        |

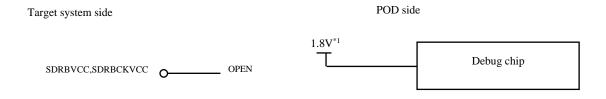

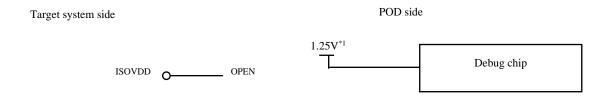

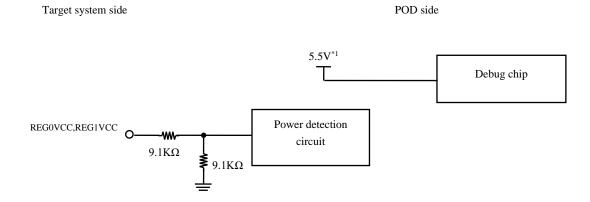

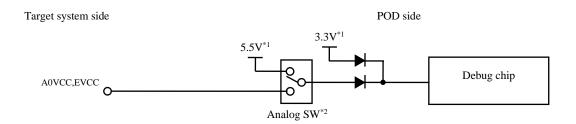

| 4.1.15  | REGOVCC,OSCVCC,ISOVDD,REG1VCC,PLLVCC,SDRBVCC,SDRBCKVCC, and SDRAVCC                         | c pins 43 |

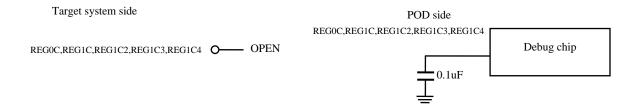

| 4.1.16  | REG0C, REG1C1, REG1C2, REG1C3, and REG1C4 pins                                              | 43        |

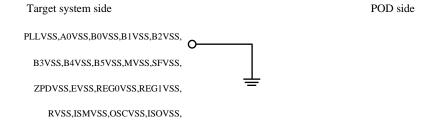

| 4.1.17  | VSS pins for each power subsystem                                                           | 43        |

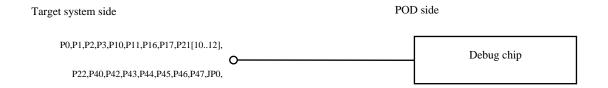

| 4.1.18  | A/D converter                                                                               | 43        |

| 4.1.19  | Power-On-Clear Reset 0 (POC0RES)                                                            | 43        |

| 4.1.20  | Power-On-Clear Reset 1 (POC1RES)                                                            | 43        |

| 4.1.21  | ISOPWRES                                                                                    | 43        |

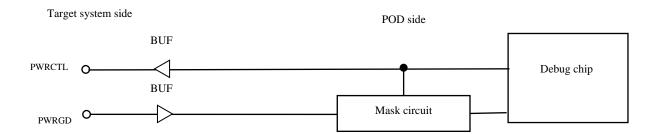

| 4.1.22  | PWRCTL pin                                                                                  | 43        |

| 4.1.23  | FCU RAM                                                                                     | 44        |

| 4.1.24  | OCTA                                                                                        | 44        |

| 4.1.25  | Serial RGB                                                                                  | 44        |

| 4.1.26  | Hyper Bus                                                                                   | 44        |

| 4.1.27  | SFMA0                                                                                       | 44        |

| 4.1.28  | SFMA1                                                                                       | 45        |

| 4.1.29  | SFMA2                                                                                       | 45        |

| 4.1.30  | NANDC                                                                                       | 45        |

| 4.1.31  | Error Control Module(ECM).                                                                  |           |

| 4.1.32  | Performance Monitor                                                                         |           |

| 4.1.33  | Open LDI                                                                                    | 46        |

| 4.2 Cau | tionary notes on debugging                                                                  | 47        |

| 4.2.1   | Hardware break (access) function (the timing of a break occurring)                          |           |

| 4.2.2   | Hardware break (access) function (forms of read or write access that are not detectable)    |           |

| 4.2.3   | Hardware break (access) function (EIINT table)                                              |           |

| 4.2.4   | Initialization of RAM areas                                                                 |           |

| 4.2.5   | Reset of pins(skipped number)                                                               |           |

| 4.2.6   | Trace function                                                                              |           |

| 4.2.7   | Power-saving modes                                                                          | 48        |

| 4.2.8   | PBG                                                                                         |           |

| 4.2.9   | Resets when an emulator is in use                                                           | 49        |

| 4.2.10  | Interrupts when an emulator is in use                                                       | 50        |

| 4.2.11  | HALT mode and stepped execution of the HALT instruction                                     |           |

| 4.2.12  | Stepped execution of an instruction which would lead to a transition to the DEEPSTOP mode   |           |

| 4.2.13  | Cautionary note on connecting an emulator (pin reset)                                       |           |

| 4.2.14  | Access to I/O resources in the MCU                                                          |           |

| 4.2.15  | Registers in peripheral modules                                                             |           |

| 4.2.16  | Performance measurement                                                                     |           |

| 4.2.17  | Reset                                                                                       |           |

| 4.2.18  | Rewriting of on-chip flash memory (RAM)                                                     | 52        |

| 4.2.19  | Rewriting of on-chip flash memory (clock monitor)                                           |           |

| 4.2.20  | Rewriting of on-chip flash memory (register value)                                          |           |

| 4.2.21  | Breaks during execution of code for making clock settings                                   |           |

| 4.2.22  | Event functions (64-bit access)                                                             |           |

| 4.2.23  | Event functions (in the order of event detection)                                           |           |

| 4.2.24  | Event functions (bit-manipulation instructions)                                             |           |

| 4.2.25  | Satisfaction of two break conditions before a single break                                  |           |

| 4.2.26  | Software break function (RAM areas)                                                         |           |

|         |                                                                                             |           |

| 4.2.27   | 7 Pin-reset mask function                   | 54 |

|----------|---------------------------------------------|----|

| 4.2.28   | 3 Trace Ring Mode                           | 54 |

| 4.2.29   |                                             |    |

|          | onal Product                                |    |

| 5.1 Lo   | ong term trace option                       | 55 |

| 5.1.1    | General                                     | 55 |

| 5.1.2    | Setup procedure                             |    |

| 5.1.3    | Cautionary note when using the QB-V850E2-SP | 56 |

| 6. Maint | tenance and Warranty                        | 57 |

| 6.1 Ma   | Iaintenance                                 | 57 |

|          | Varranty                                    |    |

|          | epair provisions                            |    |

| 6.4 Ho   | ow to request repairs                       | 58 |

| Appendi  | lix A Characteristics of Target Interface   | 59 |

|          |                                             |    |

# 1. Overview

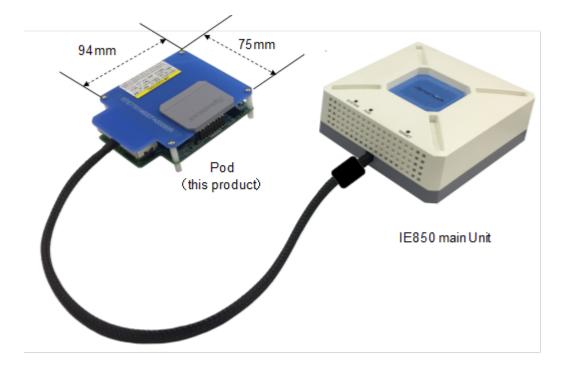

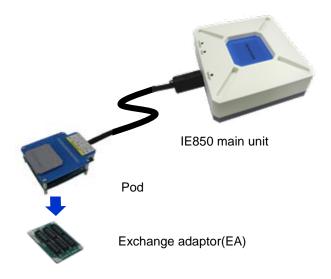

The RTE7701460EPA00000R (pod) is used together with the QB-V850E2 (IE850 main unit) in order to emulate RH850/D1x series microcontrollers from Renesas Electronics Corp.

The IE850 can be used to debug hardware and software efficiently when developing systems using the target device.

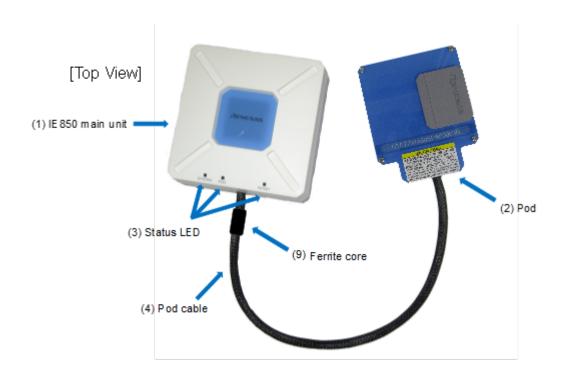

Figure 1-1 External Appearance

# 1.1 Hardware specification

The following table describes hardware specifications of the pod.

Table 1-1 Pod Hardware Specifications

| Parameter                         | Specification                                            |

|-----------------------------------|----------------------------------------------------------|

|                                   | 484-pin BGA: RH850/D1M2H                                 |

|                                   | 376-pin BGA: RH850/D1M2                                  |

|                                   | 272-pin BGA: RH850/D1M1A                                 |

| Emulation target device           | 272-pin BGA: RH850/D1M1H                                 |

| Emulation target device           | 176-pin QFP: RH850/D1M1                                  |

|                                   | 176-pin QFP: RH850/D1L2H                                 |

|                                   | 144-pin QFP: RH850/D1L2                                  |

|                                   | 144-pin QFP: RH850/D1L1                                  |

| Emulator system voltage           | 5.5V, 3.3V (supplied by IE850 main)                      |

| Target system interface voltage   | Depend on target device                                  |

| Maximum operating frequency       | 240 MHz                                                  |

| Input frequency of the oscillator | 8 MHz (for the oscillator mounted on the pod as shipped) |

| Operating temperature range       | 0°C to 40°C (No condensation)                            |

| Storage temperature range         | -15°C to 60 °C (No condensation)                         |

# 1.2 System overview

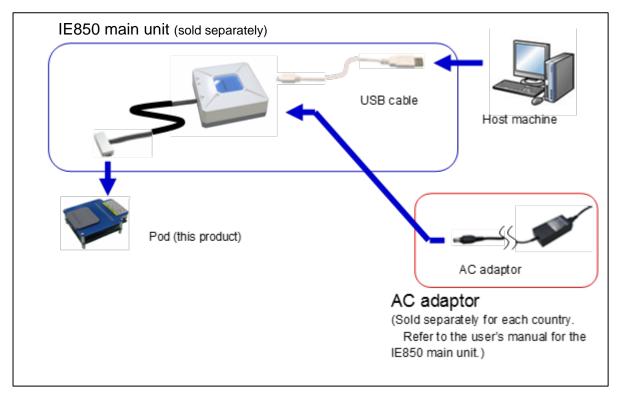

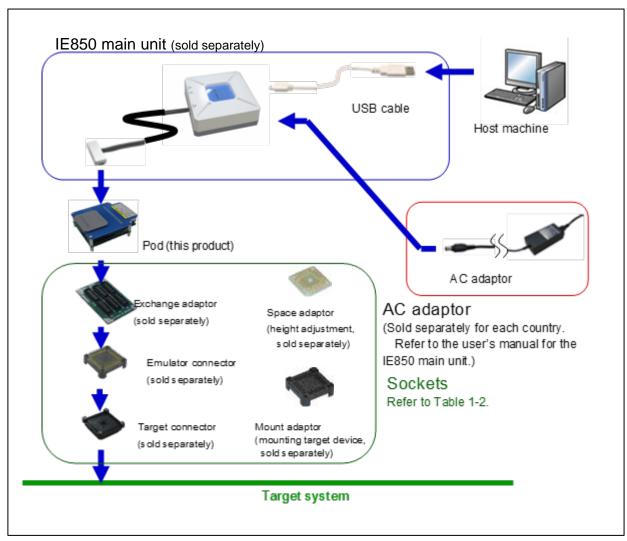

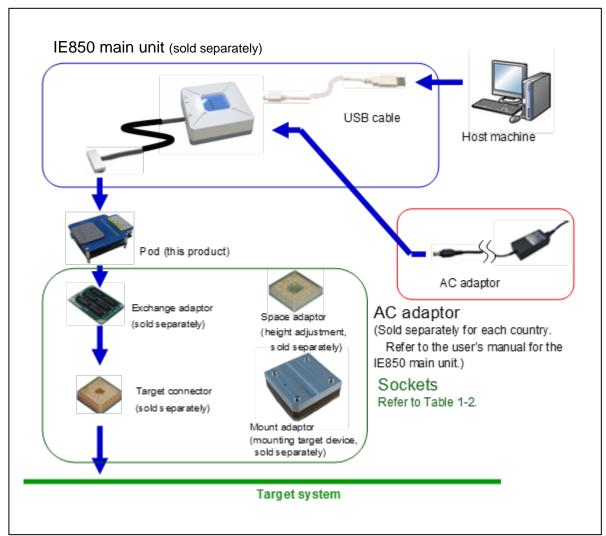

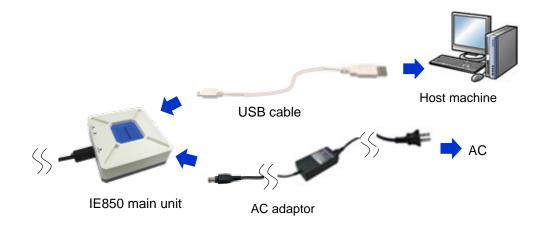

The system configuration is described below. The pod cannot be used on its own. The IE850, an AC adaptor, and sockets are also required. These are sold separately.

Figure 1-2 System Configuration (when the Target System is not Connected)

Figure 1-3 System Configuration (when the QFP Package is Selected)

Figure 1-4 System Configuration (when the BGA Package is Selected)

The following table describes the corresponding sockets for the target device. Socket products are sold separately from this product (the pod). You can purchase the target connector (BSSOCKET), the space adaptor (CSSOCKET), and the mounting adaptor (LSPACK) for the BGA packages from Tokyo Eletech Corporation and the other components are available from Renesas Electronics Corporation.

Table 1-2 Sockets for the Target Device

| Package<br>Device | Exchange<br>Adaptor       | Emulator<br>Connector | Target<br>Connector       | Space Adaptor            | Mount Adaptor                |

|-------------------|---------------------------|-----------------------|---------------------------|--------------------------|------------------------------|

| BGA484            | RTE7701412CB<br>F484T000R | _                     | BSSOCKET484<br>Z2627RE21N | CSSOCKET484<br>Z2627RE03 | LSPACK484Z2<br>627RE01       |

| D1M2H             |                           |                       |                           | CSSOCKET484<br>Z2627RE04 |                              |

| BGA376            | RTE7701410CB<br>F376T000R | _                     | BSSOCKET376<br>Z2223RE21N | CSSOCKET376<br>Z2223RE03 | LSPACK376Z2<br>223RE01       |

| D1M2              |                           |                       |                           | CSSOCKET376<br>Z2223RE04 |                              |

| BGA272            | RTE7701461CB<br>F272T000R | _                     | BSSOCKET272<br>Z2021RE21N | CSSOCKET272<br>Z2021RE03 | LSPACK272Z2<br>021RE11       |

| D1M1A<br>D1M1H    |                           |                       |                           |                          | LSPACK272Z2<br>021RE12<br>*1 |

| QFP176            | RTE7701463CF              | QB-176GM-YQ-          | QB-176GM-NQ-              | QB-176GM-YS-             | QB-176GM-                    |

| D1M1              | K176T000R                 | 01T                   | 01T                       | 01T                      | HQ-01T                       |

| D1L2H             |                           |                       |                           |                          |                              |

| QFP144            | RTE7701422CF              | QB-144GJ-YQ-          | QB-144GJ-NQ-              | QB-144GJ-YS-             | QB-144GJ-HQ-                 |

| D1L2              | K144T000R                 | 01T                   | 01T                       | 01T                      | 01T                          |

| QFP144            | RTE7701421CF              | QB-144GJ-YQ-          | QB-144GJ-NQ-              | QB-144GJ-YS-             | QB-144GJ-HQ-                 |

| D1L1              | K144T000R                 | 01T                   | 01T                       | 01T                      | 01T                          |

Notes: 1. Contact Tokyo Eletech Corporation and select which adaptor to use according to the assignment of components on the target system.

# 1.3 Functional overview

IE850 is provided with a wealth of debugging functions to enable efficient program debugging, in addition to being used to emulate the operation of a target device. An overview of the functions is provided in this section.

Some functions are not supported, depending on the debugger to be used. See also the manual of the debugger to be used to confirm.

**Table 1-3** System Specifications

|                   | Parameter                                             | Specification                                                                                                                                                                |

|-------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Program execution | Real-time execution                                   | Available                                                                                                                                                                    |

|                   | Step execution                                        | Available                                                                                                                                                                    |

| Reset             | Forced reset                                          | Available                                                                                                                                                                    |

| Break             | Software break                                        | In ROM and RAM areas combined: 2000 points                                                                                                                                   |

|                   | Hardware break                                        | 12 points including those used for both execution and CPU access conditions (8 points only for execution conditions, and 4 points for either execution or access conditions) |

|                   | Forced break                                          | Available                                                                                                                                                                    |

|                   | Trace-full break                                      | Available                                                                                                                                                                    |

|                   | Trace delay break                                     | Available                                                                                                                                                                    |

| Event             | Number of events that can be set                      | 8 points for execution, 8 points for CPU access, and 4 points for DMA access                                                                                                 |

|                   | Available function                                    | Break, trace, performance measurement                                                                                                                                        |

|                   | Combination of events                                 | OR, sequential                                                                                                                                                               |

| Trace             | Priority in trace acquisition                         | Real-time trace mode                                                                                                                                                         |

|                   |                                                       | Non-real-time trace mode                                                                                                                                                     |

|                   | Trace memory capacity                                 | IE850 main unit: 9 Mbytes (512-K frames)                                                                                                                                     |

|                   |                                                       | QB-V850E2-SP (long-term trace option): 2.25 Gbytes (128-M frames)                                                                                                            |

|                   |                                                       | One frame = one set of branch information (branch-source and branch-destination PC values)                                                                                   |

|                   | Recorded data                                         | Branch information, number of cycles for data access and for DMA access, software trace, time stamps                                                                         |

|                   | Conditions to start and end recording to trace memory | Halting execution of the program or setting events                                                                                                                           |

|                   | Conditions for tracing data                           | Event condition                                                                                                                                                              |

|                   | Modes for recording to trace memory                   | Ring mode (overwrite mode), trace-full stop mode, trace-delay stop mode, trace-full break mode, trace-delay break mode                                                       |

|                                                                                   | Paramet                  | er                           | Specification                                                                                                                                                                                                                                                                                                                                                                           |  |

|-----------------------------------------------------------------------------------|--------------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Performance measurement                                                           | Time Measurement section |                              | From run to break                                                                                                                                                                                                                                                                                                                                                                       |  |

| functions                                                                         |                          | Items measured               | Execution time                                                                                                                                                                                                                                                                                                                                                                          |  |

|                                                                                   |                          | Performance                  | 32-bit counters                                                                                                                                                                                                                                                                                                                                                                         |  |

|                                                                                   | Time<br>(2)              | Measurement section          | From run to break, or between two event points                                                                                                                                                                                                                                                                                                                                          |  |

|                                                                                   |                          | Items measured               | Execution time, total execution time, pass count, maximum execution time, minimum execution time                                                                                                                                                                                                                                                                                        |  |

|                                                                                   |                          | Performance                  | 32-bit counters (for three sections)                                                                                                                                                                                                                                                                                                                                                    |  |

|                                                                                   | Other<br>than<br>time    | Items measured               | Number of instructions executed (all or branches only), number of interrupts accepted (El level or FE level), number of exceptions accepted (instruction asynchronous or instruction synchronous), clock cycles (all, while interrupts are inhibited, or other than for the processing of interrupts), number of instruction fetches requested, number of hits on the instruction cache |  |

|                                                                                   |                          | Measurement section          | From run to break, or between two event points                                                                                                                                                                                                                                                                                                                                          |  |

|                                                                                   |                          | Items measured               | Maximum value, minimum value, latest value, total value, pass count                                                                                                                                                                                                                                                                                                                     |  |

|                                                                                   |                          | Performance                  | 32-bit counters (for four sections)                                                                                                                                                                                                                                                                                                                                                     |  |

| Masks                                                                             | Maskii                   | ng resets                    | Possible                                                                                                                                                                                                                                                                                                                                                                                |  |

|                                                                                   | Maskii<br>reset p        | ng resets through the<br>bin | Not possible                                                                                                                                                                                                                                                                                                                                                                            |  |

|                                                                                   | Maskii<br>signal         | ng the PWRGD                 | Possible: The PWRCTL signal in the debug chip is looped back and input to the PWRGD signal on the pod.                                                                                                                                                                                                                                                                                  |  |

| Pseudo real-time R                                                                | RAM mor                  | nitoring                     | Available (occupies a bus (steals cycles)) *1                                                                                                                                                                                                                                                                                                                                           |  |

| Direct memory mod                                                                 | dification               |                              | Available (occupies a bus (steals cycles)) *1                                                                                                                                                                                                                                                                                                                                           |  |

| Peripheral breaks                                                                 |                          |                              | Available *2                                                                                                                                                                                                                                                                                                                                                                            |  |

| Activating the settings of the Intelligent Cryptographic Unit (Slave type) (ICUS) |                          |                              | Possible (not possible if the settings of the ICUS is not activated)                                                                                                                                                                                                                                                                                                                    |  |

| , , ,                                                                             |                          | orograms                     | Available *3 Debugging startup register Initial value: 0000 0000 <sub>H</sub> Address: FA00 2078 <sub>H</sub> (CPU1)                                                                                                                                                                                                                                                                    |  |

Notes: 1. Only available for the general local RAM area.

- 2. The function to stop peripheral I/O operation in a break is called the peripheral break function. Whether peripheral emulation functions are set or not is determined by the debugger. Refer to the manual for the debugger you are using for how to set them. Refer to the manual for the MCU you are using to check whether peripheral emulation functions are set.

- 3. For this function, any 32-bit value which is debugging information from the debugger is specified and held in the debugging startup register while the emulator is connected. This function can be used to determine the state of the emulator being connected or not from within user programs (refer to cautionary note 4.2.29).

#### 1.3.1 Program execution function

The program execution function enables program execution equivalent to that of the target device. The executed program can be stopped under various conditions by using the break functions. The operation of only a function can be checked by executing a program, because a program can be executed from any address.

Single stepping (executing instructions one by one in units of assembly instructions) and source-level stepping (executing lines of C-language source code one by one) are available as types of stepped execution.

#### 1.3.2 Reset

The CPU can be reset from the debugger with the forced reset function. The function is used to start program execution from the reset vector or to initialize the CPU during debugging.

## 1.3.3 Break (Program execution stop)

The break functions are used to stop program execution. With the IE850, program execution can be stopped under the following various conditions. See (1) to (4) for an overview of each break function.

Table 1-4 Conditions for Breaks and their Types

| Condition for break                                       | Type of break              |

|-----------------------------------------------------------|----------------------------|

| Stopping after executing the instruction at an address    | Hardware break function    |

|                                                           | Software break function    |

| Stopping after access to a variable                       | Hardware break function    |

| Forcibly stopping                                         | Forced break               |

| Stopping if trace acquisition matches a certain condition | Trace-full break function  |

|                                                           | Trace delay break function |

#### (1) Hardware break

The hardware break function is used to set a break for a specific fetch or access operation. For example, a break is set by detecting a state where an address has been executed or a variable has been accessed.

#### (2) Software break

The software break function is used to set a break when a specific address has been executed (fetched). A break is set by temporarily replacing the instruction code of the specified address with the instruction for a break.

## Caution

Using the software break function for the on-board flash memory leads to rewriting of the on-board flash memory whenever a break is set, deleted, or executed. This reduces the number of cycles of rewriting relative to cases where the software break function is not used.

#### (3) Forced break

This function is used to forcibly stop a program when a user wants to stop a program.

#### (4) Other types of breaks

Trace-full break function

This function is used to stop a program when the trace memory is full.

Delay trigger break

This function is used to stop a program after acquiring a certain amount of trace data by hitting a certain event condition.

#### 1.3.4 Event (Detection of specific operations)

The event function is used to detect specific fetching or other access by monitoring the bus cycle of the CPU and the external master such as DMAC. Operations where the instruction at an address is executed by the CPU or access to a variable is made by the CPU or the external master can be detected. Such specific operations are referred to as events. The event function is used by the break function, trace function, and performance measurement function.

#### 1.3.5 Trace (Program execution history)

The trace function is used to check the execution history (trace information) of the CPU and the external master such as DMAC. Various types of functions shown from (1) to (4) can be used in the IE850.

#### (1) Priority of trace data acquisition

This feature enables selecting the priority for the acquisition of trace data.

**Table 1-5** Priority of Trace Acquisition

| Priority of Trace Acquisition | Descriptions                                                                                                                                                                                                                                                             |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Real-time trace mode          | Mode that gives priority to the program execution. If trace output is not fast enough, output of the trace information is temporarily halted. Thus, although the program runs in real time, trace information might be lost. This depends on the program being executed. |

| Non-real-time trace mode      | Mode that gives priority to trace acquisition. If trace output is not fast enough, operation of the CPU is temporarily halted. Thus, the loss of trace information is suppressed* but the program loses the characteristic of real-time operations.                      |

|                               | Caution *: Using this mode will always decrease the degree of information loss compared with the real-time trace mode.  However, losing information might still not be avoidable.  Whether this is so depends on the program being run.                                  |

RENESAS

## (2) Types of trace data

Types of trace data (trace information that can be acquired) are listed below.

Table 1-6 List of Types of Trace Data

| Type of trace data              | Descriptions                                                                                                                                                                 |  |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Branch source PC value          | Branch source and branch destination PC values can be recorded in the history.                                                                                               |  |

| Branch destination PC value     | The debugger complements the program with the instructions that would otherwise be executed between branch points and displays the complemented                              |  |

| (PC stands for program counter) | data. Thus, a program that was practically executed could be confirmed.                                                                                                      |  |

| counter)                        | Caution: Execution history that can be displayed depends on the number of branches acquired.                                                                                 |  |

| Access-execution PC             | History of the PC values for executed access instructions for the memory or                                                                                                  |  |

| Access address                  | peripheral I/O register, access addresses, and accessed data from the CPU can be recorded. A history of reading and writing can also be recorded.                            |  |

| Accessed data                   |                                                                                                                                                                              |  |

|                                 | Caution: Access to the program registers of the CPU (such as r1 and r2) and system registers cannot be recorded in the history.                                              |  |

| DMA access cycle                | History of access addresses and accessed data for the memory or peripheral I/O register from the DMA can be recorded. A history of reading and writing can also be recorded. |  |

| Time stamp (time tag)           | Elapsed time between traced data can be added to each trace datum. The CPU clock is used in measurement for the time stamps.                                                 |  |

#### (3) Conditions for recording in trace memory

This feature allows you to select how the trace memory is utilized.

Table 1-7 List of Conditions for Recording in Trace Memory

| Conditions for recording in trace memory | Descriptions                                                                                                                                                                                                                                                                                                       |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ring mode (overwrite mode)               | New information is written over old information so that the latest information is consistently acquired. Trace acquisition continues until a break is reached.                                                                                                                                                     |

| Trace-full stop mode                     | When trace memory becomes full, further trace information is not acquired. The program continues to run.                                                                                                                                                                                                           |

| Trace-full break mode                    | When trace memory becomes full, further trace information is not acquired and the program is stopped.                                                                                                                                                                                                              |

| Delay trigger stop mode                  | The latest information is consistently acquired by writing new information over old information until a specific condition occurs. After the specific condition occurs, the selected amount of trace information is acquired, after which further trace information is not acquired. The program continues to run. |

| Delay trigger break mode                 | The latest information is consistently acquired by writing new information over old information until a specific condition occurs. After the specific condition occurs, the selected amount of trace information is acquired, after which further trace information is not acquired. The program is also stopped.  |

#### 1.3.6 Performance measurement

Performance measurement is for measuring execution time from the time a program is started until it is stopped, the execution times of specific segments, or the items listed in Table 1-3, System Specifications.

#### 1.3.7 Masks

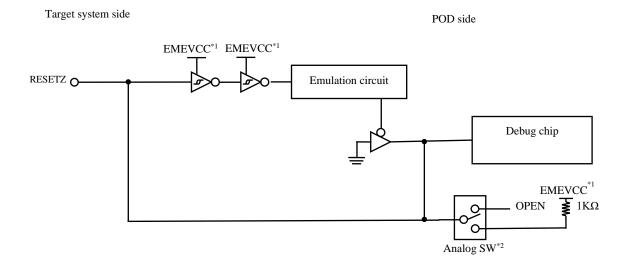

Masks are used to help in debugging when the generation of an unintended reset might be thought possible or doubts exist about a signal level on the target system. The following items can be masked.

#### (1) System resets

System resets are completely masked (both the pin reset and internal resets). Masking is enabled by a setting in the debug chip (microcontroller).

Caution Masking only the pin reset is not possible with this pod, although this is selectable in some debuggers.

#### (2) PWRGD signal

Masking of the PWRGD signal on the target system leads to the PWRCTL signal in the debug chip (microcontroller) being looped back and input to the PWRGD signal on the pod.

#### 1.3.8 Real-time RAM monitor

Display of on-board RAM areas during program execution is possible.

#### 1.3.9 Change of direct memory

On-board RAM can be changed to a desired value during program execution.

#### 1.3.10 Peripheral break

When the break function has been used to stop program execution, peripheral functions other than the watchdog timer continue to operate in general, but some peripheral functions can be stopped by using the peripheral break function. Refer to the user's manual of the target device for information on the peripheral functions.

# 1.4 Regulatory notices

## European Union regulatory notices

This product complies with the following EU Directives. (These directives are only valid in the European Union.)

#### **CE Certifications:**

This product complies with the following European EMC standards.

• EMC Directive (2014/30/EU)

EN 55032 Class A

**WARNING:** This is a Class A product. This equipment can cause radio frequency noise when used in the residential area. In such cases, the user/operator of the equipment may be required to take appropriate countermeasures under his responsibility.

EN 55024

## Information for traceability:

· Authorised representative & Manufacturer

Name: Renesas Electronics Corporation

Address: TOYOSU FORESIA, 3-2-24, Toyosu, Koto-ku, Tokyo, 135-0061, Japan

· Person responsible for placing on the market

Name: Renesas Electronics Europe GmbH

Address: Arcadiastrasse 10, 40472 Dusseldorf, Germany

· Trademark and Type name

Trademark: Renesas

Product name: IE850 Emulator

Type name: RTE7701460EPA00000R

#### Environmental Compliance and Certifications:

• Waste Electrical and Electronic Equipment (WEEE) Directive 2012/19/EC

#### United States Regulatory notices on Electromagnetic compatibility

This product complies with the following EMC regulation. (This is only valid in the United States.)

#### FCC Certifications:

This equipment has been tested and found to comply with the limits for a Class A digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference in which case the user will be required to correct the interference at his own expense.

This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions: (1) this device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation.

**CAUTION:** Changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to operate the equipment.

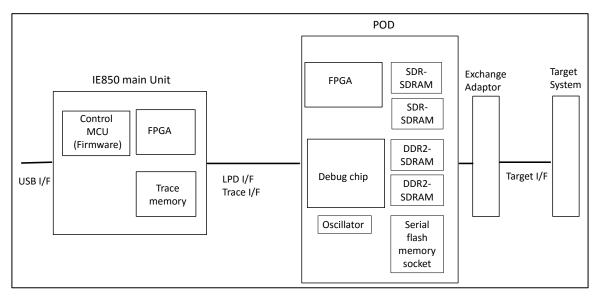

#### 1.5 Overview of emulation

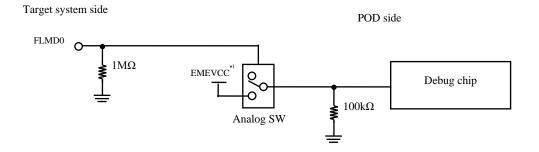

An internal block diagram of this pod is shown below.

Figure 1-5 Overview of Internal Blocks

#### Debug chip:

The debug chip is used to emulate the operation of the individual target devices of the RH850/D1x series.

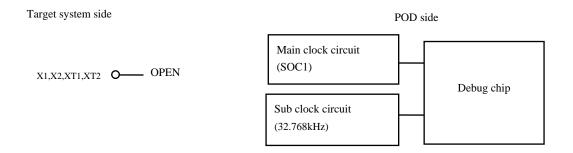

#### Oscillator:

In consideration of the oscillation characteristics, the oscillator on the pod provides the main and sub-oscillator signals instead of the oscillator on the target system. That is, the debug chip is driven by the oscillator on the pod. For details, refer to section 3.3.2, Replacing the clock.

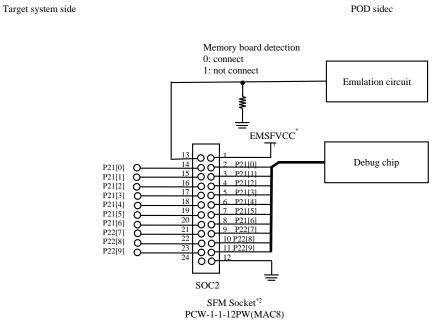

#### Serial flash memory socket:

This socket can be used to mount serial flash memory. Due to the high-speed interface, the debug chip may have difficulty in access to the serial flash memory. In such cases, it is possible to place a memory circuit which is equivalent to the serial flash memory on the target system in this memory socket and emulate access to the serial flash memory.

#### SDR-SDRAM:

Since the SDR-SDRAM interface for the D1M1H is high speed, access to the SDR-SDRAM on the target system by the debug chip via a socket such as the EA is difficult. Mounting SDR-SDRAM (IS42S16320F-6BL from ISSI) on the pod and using it as if it were memory on the target system enables emulation of the SDR-SDRAM interface. In this case, there is no access to the SDR-SDRAM on the target system.

#### DDR2-SDRAM:

The DDR2-SDRAM interface for the D1M2(H) series is also high speed, access to the SDR-SDRAM on the target system by the debug chip via a socket such as the EA is difficult. Mounting DDR2 memory (MT47H128M16-25E-C from Micron) on the pod and using it as if it were memory on the target system enables emulation of the DDR2-SDRAM interface. In this case, there is no access to the DDR2 memory on the target system.

# 1.6 Package contents

RTE7701460EPA00000R package includes the items below. Confirm the items in the attached contents of the package.

Products supplied with RTE7701460EPA00000R:

- Pod

- Table of Toxic and Hazardous Substance and Elements

- Ferrite core

Page 30 of 69

# 2. Names and Functions of Hardware

The following shows the names of pod and IE850 hardware units and their features.

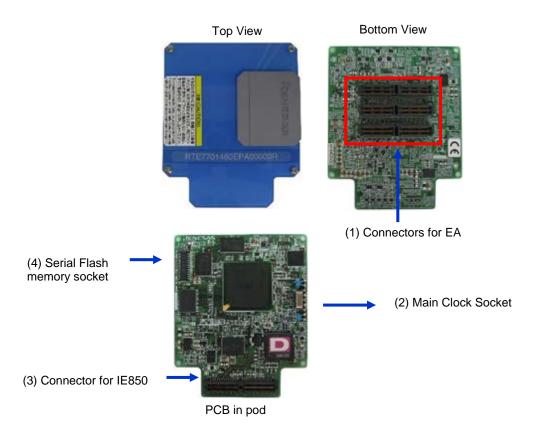

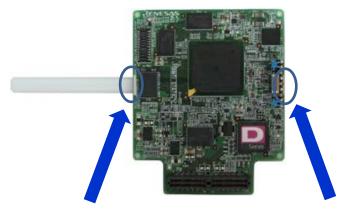

#### 2.1 Pod

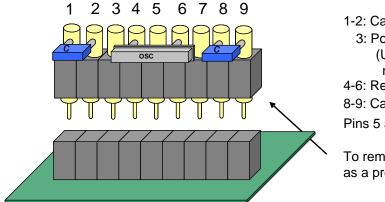

Figure 2-1 Names of Parts of Pod

#### (1) Connector for EA

This is the connector for connecting to the exchange adaptor (EA).

#### (2) Clock Socket (SOC1)

This is the socket for the main oscillator. An 8-MHz oscillator is mounted upon shipment.

#### (3) Connector for the IE850

This is the connector for connecting the pod cable of the IE850 main unit.

# (4) Serial flash memory socket (SOC2)

This socket is for mounting serial flash memory on the pod. All pins of the socket are short-circuited to each other by shunts in the product as shipped. When flash memory is not mounted, be sure to leave the pins of this socket short-circuited. When flash memory is mounted, refer to the equivalent circuits in appendix A.

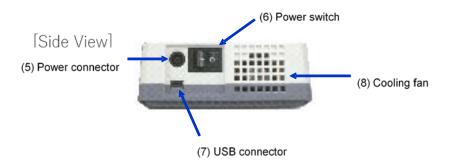

# 2.2 IE850 main unit

Figure 2-2 Names of Pars of IE850

## (1) IE850 main unit

The IE850 main unit is the main controller of debugging. The IE850 main unit is sold separately. The control program (firmware) and FPGA data will need to be rewritten in accord with the pod to be connected. For more information on rewriting, refer to http://www.renesas.com/ie850.

# (2) Pod

This product. Please refer to section 2.1.

#### (3) Status LED

The status LEDs turn on or blink according to specific causes as described in the table below. If any LED does not turn on or not blink, IE850 main unit might be broken. In this case, contact a Renesas Electronics sales representative or distributor.