# **Microcontroller Technical Information**

|                                                                                                           |                                                         | Document No.   | ZBG-C                                                                                                                                          | D-08-0022             | 1/2 |  |  |

|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----|--|--|

|                                                                                                           | QB-78K0RKX3                                             | Date issued    | June 5, 2008                                                                                                                                   |                       |     |  |  |

| In-Circuit Emulator for<br>78K0R/KE3, 78K0R/KF3, 78K0R/KG3,<br>78K0R/KH3, 78K0R/KJ3<br>Usage Restrictions |                                                         | Issued by      | Development Tool Solution Group<br>Multipurpose Microcomputer Systems Division<br>Microcomputer Operations Unit<br>NEC Electronics Corporation |                       |     |  |  |

| Related                                                                                                   | QB-78K0RKX3 User's Manual:                              | Notification   |                                                                                                                                                | Usage restriction     |     |  |  |

| documents                                                                                                 | U17866EJ4V0UM00                                         | classification |                                                                                                                                                | Upgrade               |     |  |  |

|                                                                                                           | QB-78K0RKX3 (Control Code: E, F, G,                     |                |                                                                                                                                                | Document modification |     |  |  |

|                                                                                                           | H, J, K, L, M) Operating Precautions:<br>ZUD-CD-08-0072 |                |                                                                                                                                                | Other notification    |     |  |  |

### 1. Affected product

| Product     | Outline                                                  | Control Code <sup>Note</sup> |

|-------------|----------------------------------------------------------|------------------------------|

| QB-78K0RKX3 | In-circuit emulator for 78K0R/KE3, 78K0R/KF3, 78K0R/KG3, | E, F, G, H, J, K, L, M       |

|             | 78K0R/KH3, 78K0R/KJ3                                     |                              |

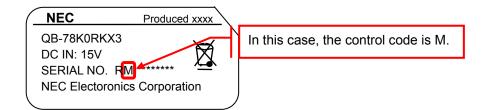

**Note** The "control code" is the second digit from the left in the 10-digit serial number.

If the product has been upgraded, the control code can be checked in the About dialog box in the ID78K0R-QB.

"X" in version information "IECUBE \*\*\*\* X F/W: V\*.\*\*" is the control code.

# 2. New items

New restrictions (No. 15 and No. 16) have been added. See the attachment for details.

# 3. Workarounds

See the attachment for details.

#### 4. Modification schedule

Products in which No. 15 and No. 16 are corrected are scheduled for release as follows.Newly shipped products (control code: M): Shipments as of June 19, 2008Upgrade for already shipped products: Available from June 19, 2008

\* Note that this schedule is subject to change without notice. For the detailed release schedule of modified products, contact an NEC Electronics sales representative.

# 5. List of restrictions

See the attachment.

#### 6. Document revision history

| Document Number | Issued on          | Description                                                                |

|-----------------|--------------------|----------------------------------------------------------------------------|

| ZBG-CD-06-0077  | September 1, 2006  | Newly created.                                                             |

|                 |                    | Addition of new bugs (No. 1 to No. 12)                                     |

| ZBG-CD-06-0086  | September 21, 2006 | Addition of new bugs (No. 13 to No. 16)                                    |

|                 |                    | Addition of caution (No. 8)                                                |

| ZBG-CD-07-0008  | January 18, 2007   | Addition of new bugs (No. 17 and No. 18)                                   |

| ZBG-CD-07-0027  | May 21, 2007       | Division of Product History into two sections: Additions and Changes to    |

|                 |                    | Specifications and Restrictions.                                           |

|                 |                    | Addition of new bugs (No. 18 and No. 19)                                   |

| ZBG-CD-08-0022  | June 5, 2008       | Correction on descriptions in 1. Affected product and 2. New items         |

|                 |                    | Deletion of restrictions on products with control code D or earlier        |

|                 |                    | (Restrictions No. 1 to No. 7 in ZBG-CD-07-0027)                            |

|                 |                    | Renumbering of No. 8 to No. 19 as No. 1 to No. 12 in 3. Product history in |

|                 |                    | conjunction with deletion of restrictions                                  |

|                 |                    | Addition of specification changes No. 13 and No. 14 described in           |

|                 |                    | upgrade notification (ZBG-CD-07-0073)                                      |

|                 |                    | Addition of restrictions No. 15 and No. 16                                 |

# **Operating Precautions for QB-78K0RKX3**

This document describes the following items. Refer to the user's manual for cautions on using an in-circuit emulator.

- Restrictions not applicable to the target device but applicable to an in-circuit emulator

- Restrictions applicable to both the target device and an in-circuit emulator but the correction is planned only for the in-circuit emulator

Also refer to the following documents for the restrictions in the target device.

- User's manual of target device

- Restrictions notification document for target device

#### 1. Product Version

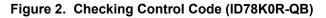

The product versions of NEC Electronics in-circuit emulators are indicated by a control code. The control code is the second digit from the left in the 10-digit serial number. If the product has been upgraded, the control code can be checked by selecting [About] from the [Help] menu while the ID78K0R-QB is running. "X" in version information "IECUBE \*\*\*\* X F/W: V\*.\*\*" is the control code.

#### Figure 1. Checking Control Code (Label on QB-78K0RKX3)

| About      |                                                                                                                                                           |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| (comesti ) | NEC Integrated Debugger ID78K0R-QB<br>Version V3.40 [29 Jun 2007] In this case, the control code is M.                                                    |

| 32         | 78KOR IECUBE Monitor ¥1.00<br>Tcl/Tk 8.4.9<br>IECUBE 3001 M /W: ¥1.00<br>Flash Firmware ¥3.40<br>Control Board 0003 01.00 30.04<br>I/O Board 0101 02.01 ✓ |

|            | Copyright(C) NEC Electronics Corporation 1993,2007<br>All rights reserved by NEC Electronics Corporation                                                  |

#### 2. Supported Devices

(1) Emulation environment for -A devices<sup>Note</sup>

Use a QB-78K0RKX3 with control code L or later when performing emulation of an -A device. Emulation of -A devices is not available when a QB-78K0RKX3 with control code K or earlier is used. (Use the QB-78K0RKX3 with the latest control code.)

(2) Emulation environment for non-A devices<sup>Note</sup>

Emulation of non-A devices is available only when a QB-78K0RKX3 with control code K is used. (If not, the QB-78K0RKX3 must be upgraded to control code K.)

Contact an NEC Electronics sales representative or a distributor from whom you purchased this product for how to update the control code.

- Note Identification of -A devices and non-A devices

- "A" in the part number indicates whether the product has been revised and this classifies devices as -A or non-A.

The parts of part number "PD78F1166AGF-GAS-AX" are explained below, as an example.

| Family type | Part<br>number | Revised |    | Package type<br>stom code/speed<br>ass, pin type, etc. | Lead-free |

|-------------|----------------|---------|----|--------------------------------------------------------|-----------|

| μPD         | 78F1166        | А       | GF | - GAS                                                  | -AX       |

## 3. Product History

|     |                                                                           |   |   | С | ontro | l Cod | le |   |   |

|-----|---------------------------------------------------------------------------|---|---|---|-------|-------|----|---|---|

| No. | Restrictions and Added/Changed Specifications                             | Е | F | G | Н     | J     | К  | L | М |

| 1   | Restriction whereby trace information or pass count becomes invalid       | × | 0 | 0 | 0     | 0     | 0  | 0 | 0 |

|     | after execution of manipulation instruction for the operation speed       |   |   |   |       |       |    |   |   |

|     | mode control register (OSMC)                                              |   |   |   |       |       |    |   |   |

| 2   | Restriction on reset control flag register (RESF)                         | 0 | × | × | 0     | 0     | 0  | 0 | 0 |

| 3   | Restriction whereby invalid display of the BCDCY bit during a break       | × | × | × | 0     | 0     | 0  | 0 | 0 |

| 4   | Restriction on break before execution                                     | × | × | × | 0     | 0     | 0  | 0 | 0 |

| 5   | Restriction whereby stack overflow or stack underflow illegally occurs    | × | × | × | 0     | 0     | 0  | 0 | 0 |

| 6   | Restriction whereby invalid data may be fetched or read from external     | × | × | × | 0     | 0     | 0  | 0 | 0 |

|     | memory                                                                    |   |   |   |       |       |    |   |   |

| 7   | Restriction whereby word misalign access illegally occurs                 | × | × | × | 0     | 0     | 0  | 0 | 0 |

| 8   | Restriction on downloading programs                                       | × | × | × | ×     | 0     | 0  | 0 | 0 |

| 9   | Restrictions on coverage function                                         | × | × | × | ×     | 0     | 0  | 0 | 0 |

| 10  | Restriction related to block erase function during self-programming       | × | × | × | ×     | ×     | 0  | 0 | 0 |

| 11  | Restriction whereby invalid operations occur if there is a ROM            | × | × | × | ×     | ×     | 0  | 0 | 0 |

|     | instruction several instructions before an instruction for which a "break |   |   |   |       |       |    |   |   |

|     | before execution" is set                                                  |   |   |   |       |       |    |   |   |

| 12  | Restriction whereby a fail-safe break for uninitialized RAM occurs        | × | × | × | ×     | ×     | 0  | 0 | 0 |

|     | when an interrupt is generated during flash self-programming              |   |   |   |       |       |    |   |   |

| 13  | Support for interrupt servicing during self-programming                   | × | × | 0 | 0     | 0     | 0  | 0 | 0 |

| 14  | Support of 78K0R/Kx3 (µPD78F11xxA)                                        | × | × | × | ×     | ×     | ×  | 0 | 0 |

| 15  | Restriction on trace data when an interrupt occurs                        | × | × | × | ×     | ×     | ×  | × | 0 |

| 16  | Restriction on program execution on RAM                                   | × | × | × | ×     | ×     | ×  | × | 0 |

-: Not relevant, ×: Applicable, O: Corrected

# 4. Details on Bugs and Specification Changes

No. 1 Restriction whereby trace information or pass count becomes invalid after execution of a manipulation instruction for the operation speed mode control register (OSMC)

#### [Description]

After bit 0 (FSEL) of the operation speed mode control register (OSMC) is set to 1 by using an instruction, the following illegal operations may occur.

(1) Trace information near the instruction is displayed redundantly.

(2) The pass count is not counted normally if an event (instruction or access) is set near the instruction.

#### [Workaround]

There is no workaround.

#### [Correction]

This issue has been corrected in products with control code F and later.

ZBG-CD-08-0022 Attachment - 4/9

No. 2 Restriction on reset control flag register (RESF)

[Description]

Even if data in the reset control flag register (RESF) is read by using a memory manipulation instruction, the RESF register is not reset to 00H. The RESF register can normally be reset to 00H by using a \_RESET input or the power-on-clear (POC) circuit.

[Workaround]

There is no workaround.

[Correction]

This issue has been corrected in products with control code H and later.

No. 3 Restriction whereby invalid display of the BCDCY bit during a break

[Description]

If a break occurs after the BCDCY bit (bit 0 of the BCD correction carry register) is cleared to 0 as a result of an addition or subtraction instruction, the BCDCY bit may show "1". This bug only affects the display, not the program.

[Workaround]

There is no workaround.

[Correction]

This issue has been corrected in products with control code H and later.

No. 4 Restriction on break before execution

[Description]

If a break before execution is set to an area that has been overwritten by flash self-programming, the subsequent program execution may become invalid.

[Workaround]

There is no workaround.

[Correction]

This issue has been corrected in products with control code H and later.

No. 5 Restriction whereby stack overflow or stack underflow illegally occurs

[Description]

If execution of a stack manipulation instruction (such as the RET instruction) conflicts with DMA transfer, the stack detection function operates illegally; consequently, a fail-safe break for stack overflow or stack underflow may occur.

[Workaround]

Implement the following setting so as to disable detection of stack overflows and stack underflows.

• Open the Configuration dialog box and click the [Detail] button to open the Fail-Safe Break dialog box. Clear the Stack Underflow and Stack Overflow check boxes. [Correction]

This issue has been corrected in products with control code H and later.

No. 6 Restriction whereby invalid data may be fetched or read from external memory

[Description]

If an external memory address whose lower 16 bits match "00D0H" or "00D2H" is accessed, invalid data may be fetched or read from external memory.

[Workaround]

There is no workaround.

#### [Correction]

This issue has been corrected in products with control code H and later.

No. 7 Restriction whereby word misalign access illegally occurs

#### [Description]

If processing of 16-bit DMA transferring conflicts with accessing of an odd address in a data memory space by an instruction, a word misalign access is illegally detected; consequently, a fail-safe break occurs.

#### [Workaround]

Implement the following setting so as to disable detection of word misalign accesses.

• Open the Configuration dialog box, click the [Detail] button to open the Fail-Safe Break dialog box, and then clear the "Word Miss-align Access" check box.

#### [Correction]

This issue has been corrected in products with control code H and later.

#### No. 8 Restriction on downloading programs

[Description]

When downloading a program using the ID78K0R-QB, the error message "F0200: Verification error occurred. Failed in writing memory. (0xxxxx)" may be output. In such a case, downloading of the program was not completed normally, nor was the program written to the memory of the QB-78K0RKX3 normally.

[Workaround]

Retry downloading the program until the error no longer occurs.

#### [Correction]

This issue has been corrected in products with control code J and later.

#### No. 9 Restrictions on coverage function

#### [Description]

The following restrictions (a) to (c) concerning the coverage function exist.

(a) The coverage measurement function (C0 coverage) measures not only ROM fetch but also ROM read.

ZBG-CD-08-0022 Attachment - 6/9

- (b) When the read access status is displayed by the access monitor function on the Memory window, the window displays not only the ROM read status but also the ROM fetch status.

- (c) The general-purpose register value displayed in the Memory window may become invalid after accessing of a RAM area to which the general-purpose register is assigned. In addition, the Register window display may be invalid during program execution.

[Workaround]

- (a) There is no workaround. This issue has been corrected in products with control code J and later so as to measure ROM fetch only.

- (b) There is no workaround. This issue has been corrected in products with control code J and later so as to display ROM read only.

- (c) There is no workaround. This issue has been corrected in products with control code J and later.

The modification for the above items affects integrated debugger ID78K0R-QB and IECUBE self-diagnostic tool IEQBUTL, so be sure use them in the following combination.

| Control Code | Integrated Debugger | IECUBE Self-Diagnostic Tool |  |  |  |

|--------------|---------------------|-----------------------------|--|--|--|

|              | ID78K0R-QB          | IEQBUTL                     |  |  |  |

| E, F, G, H   | V3.20               | V2.11                       |  |  |  |

| J and later  | V3.30 and later     | V2.13 and later             |  |  |  |

[Correction]

This issue has been corrected in products with control code J and later.

No. 10 Restriction related to block erase function during self-programming

#### [Description]

An erase error may occur if an interrupt occurs multiple times in an interval shorter than "21,066/fcLK + time taken by interrupt servicing execution by user program" when the block erase function (\_FlashBlockErase) is being executed during self-programming. The "time taken by interrupt servicing execution by user program" is the time from when execution branches to a vector reference address, interrupt servicing execution by user program, and until when execution returns to the block erase function (see figure below).

Block erase function execution time

Time shorter than 21,066/fcLK + time taken by interrupt servicing

Interrupt occurs

Interrupt occurs

[Workaround]

There is no workaround.

[Correction]

This issue has been corrected in products with control code K and later.

No. 11 Restriction whereby invalid operations occur if there is a ROM instruction several instructions before an instruction for which a "break before execution" is set

#### [Description]

If there is an instruction to read the ROM area several instructions before an instruction for which a "break before execution" is set (up to nine instructions in case of an 8-bit instruction), the break may not occur, or the program may not operate correctly.

If the instruction subject to the break does not extend over a 4-byte boundary<sup>Note</sup>, the instruction is not replaced and the break does not occur.

If the instruction subject to the break extends over a 4-byte boundary<sup>Note</sup>, only the code immediately before the boundary is replaced. As a result, the instruction becomes invalid and may loop.

**Note** The 4-byte boundaries are portions shown as red dotted lines in the following figure.

| 🜌 Me                                      | mor | У                          |                            |                            |                            |                            |                      |                |                            |                            |                            |                            |                            |                            |    |    |

|-------------------------------------------|-----|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------|----------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|----|----|

| Sear                                      | ch  |                            | ~<                         |                            | >>                         | Re                         | efres                | n              | DM                         | M                          |                            | Clos                       | se                         |                            |    |    |

| Addr                                      | +0  | +1                         | +2                         | +3                         | +4                         | +5                         | +6                   | +7             | +8                         | +9                         | +A                         | +B                         | +C                         | +D                         | +E | +F |

| 00000<br>00010<br>00020<br>00030<br>00040 |     | 00<br>00<br>00<br>00<br>00 | 00<br>00<br>00<br>00<br>00 | 00<br>00<br>00<br>00<br>00 | 00<br>00<br>00<br>00<br>00 | 00<br>00<br>00<br>00<br>00 | 00<br>00<br>00<br>00 | 00<br>00<br>00 | 00<br>00<br>00<br>00<br>00 | 00<br>00<br>00<br>00<br>00 | 00<br>00<br>00<br>00<br>00 | 00<br>00<br>00<br>00<br>00 | 00<br>00<br>00<br>00<br>00 | 00<br>00<br>00<br>00<br>00 |    |    |

[Workaround]

There is no workaround.

#### [Correction]

This issue has been corrected in products with control code K and later.

No. 12 Restriction whereby a fail-safe break for uninitialized RAM occurs when an interrupt is generated during flash self-programming

#### [Description]

When an interrupt is generated by the program during flash self-programming, a fail-safe break for uninitialized RAM (Uninitialize Memory Read) may occur.

#### [Workaround]

Implement the following setting so as to disable detection of Read From Uninitialized RAM.

• Open the Configuration dialog box, click the [Detail] button to open the Fail-Safe Break dialog box, and then clear the "Read From Uninitialize RAM" check box.

#### [Correction]

This issue has been corrected in products with control code K and later.

No. 13 Support for interrupt servicing during self-programming

[Description]

Interrupt servicing during self-programming is now supported.

ZBG-CD-08-0022 Attachment - 8/9

[Correction]

This function is supported in products with control code G and later. The QB-78K0RKX3 with control code F and earlier versions include firmware installed in 78K0R/Kx3 Ver. 2.1, so the device restriction "interrupts during self-programming not supported" is still applicable.

No. 14 Support of 78K0R/Kx3 (µPD78F11xxA)

[Description]

The 78K0R/Kx3 ( $\mu$ PD78F11xxA) is now supported.

[Correction]

This change has been implemented in products with control code L and later.

The QB-78K0RKX3 control code L or later versions do not support the 78K0R/Kx3 (µPD78F11xx).

Consult an NEC Electronics sales representative or distributor if downgrading is necessary.

A common device file is provided for all 78K0R/Kx3 products ( $\mu$ PD78F11xx and  $\mu$ PD78F11xxA).

No. 15 Restriction on trace data when an interrupt occurs

[Description]

If a read access or write access is performed immediately before occurrence of an interrupt, this access may not be reflected to the trace result.

[Workaround]

There is no workaround.

[Correction]

This issue has been corrected in products with control code M and later.

An example of trace data before and after the correction of this restriction is shown below.

|                                      |        |      |       |      | A re | ad access    | by this MOV instru | ction is |

|--------------------------------------|--------|------|-------|------|------|--------------|--------------------|----------|

|                                      |        |      |       |      | not  | reflected to | the trace result.  |          |

| [Before correction]                  |        |      |       |      |      |              | 1                  |          |

| _ A 131064 0:00:00.516 208 000 01065 | AA02   | M1   |       |      |      | MOV          | W AX,[DE+2H]       |          |

| _ A 131065 0:00:00.516 209 000       |        |      | F3FFE | 9700 | W    |              |                    |          |

| _ A 131066 0:00:00.516 209 500 0002E | 4A01FF | VECT | F3FFC | 1067 | W    |              |                    |          |

| _ A 131067 0:00:00.516 211 500 0014A | 84     | M1   |       |      |      | INC          | E                  |          |

| _ A 131068 0:00:00.516 212 000 0014B | 4C0F   | M1   |       |      |      | CMP          | A,#0FH             |          |

| _ A 131069 0:00:00.516 212 500 0014D | 8A02   | M1   |       |      |      | MOV          | A,[DE+2H]          |          |

| [After correction]                    |        |      | shows the r<br>cess by "MO<br>]". |      |   |     | ess by this MOV ins | truction is |

|---------------------------------------|--------|------|-----------------------------------|------|---|-----|---------------------|-------------|

| _ A 131063 0:00:00.258 053 000 01065  | AA02   | M1   |                                   |      |   | MO  | VW AX,[DE+2H])      |             |

| <u>← A 131064</u> 0:00:00.258 053 500 |        |      | F450C 8                           | 312  | R | >   |                     |             |

| _ A 131065 0:00:00.258 054 000        |        |      | F3FFE                             | 9700 | W |     |                     |             |

| _ A 131066 0:00:00.258 054 500 0002E  | 4A01FF | VECT | F3FFC                             | 1067 | W |     |                     |             |

| _ A 131067 0:00:00.258 056 500 0014A  | 84     | M1   |                                   |      |   | INC | E                   |             |

| _ A 131068 0:00:00.258 057 000 0014B  | 4C0F   | M1   |                                   |      |   | СМ  | P A,#0FH            |             |

No. 16 Restriction on program execution on RAM

[Description]

When a branch instruction is executed on RAM and if the branch destination is an odd address located in

RAM, a fail-safe break due to a word misalign access occurs.

[Workaround]

Clear the check box for the [Word Miss-align Access] in the Fail-Safe Break dialog box in the ID78K0R-QB.

A break source can be checked in the status bar in the ID78K0R-QB, as shown below.

| ID78K0-QB                                                       |                                              |                                    |                             |

|-----------------------------------------------------------------|----------------------------------------------|------------------------------------|-----------------------------|

| <u>File Edit View Option Run Event (</u>                        |                                              |                                    |                             |

|                                                                 |                                              | ▲ 📾 🛓 🛃 🛅 ! 🛡 🤊 🔞                  |                             |

| Assemble                                                        |                                              |                                    |                             |

| Search << >> Wate                                               |                                              | Close                              | A break source is displayed |

| * > 0FFFF<br>10000<br>* 10001<br>* 10002                        | FF ?<br>FF ?<br>FF ?<br>FF ?                 |                                    | on the status bar.          |

| ** 10003   ** 10004   ** 10005   ** 10006   ** 10007   ** 10008 | FF ?<br>FF ?<br>FF ?<br>FF ?<br>FF ?<br>FF ? |                                    |                             |

| * 10009<br>* 1000A<br>* 1000B<br>* 1000C<br>* 1000C             | FF ?<br>FF ?<br>FF ?<br>FF ?<br>FF ?         |                                    | Word Miss-align Access      |

| * 1000E<br>* 1000F<br>* 1000F<br>* 10010<br>* 10011<br>* 10012  | FF ?<br>FF ?<br>FF ?<br>FF ?<br>FF ?         |                                    |                             |

| 10013   10014   10015   10016   10017                           | FF ?<br>FF ?<br>FF ?<br>FF ?<br>FF ?<br>FF ? | <u>▼</u><br>4<br>⊽                 |                             |

| ·#                                                              | OFFFF POW OFF                                | 5us 000ns (Word Miss-align Access) |                             |

[Correction]

This issue has been corrected in products with control code M and later.