Date: Apr . 7, 2015

## **RENESAS TECHNICAL UPDATE**

1753, Shimonumabe, Nakahara-ku, Kawasaki-shi, Kanagawa 211-8668 Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                                                        | Document<br>No.         | TN-V85-A020A/E        | Rev.                                                               | 1.00 |  |

|-----------------------|----------------------------------------------------------------|-------------------------|-----------------------|--------------------------------------------------------------------|------|--|

| Title                 | V850E/IG4-H,V850E/IH4-H Usage Restrictio bus control function. | Information<br>Category | Usage Restriction     |                                                                    |      |  |

|                       | V850E/IG4-H,V850E/IH4-H series                                 | Lot No.                 |                       | * V850E/IG4-H,V850E/IH4-H                                          |      |  |

| Applicable<br>Product |                                                                | All lots                | Reference<br>Document | User's Manual: Hardware volume 3 (the 3rd edition) R01UH0306EJ0300 |      |  |

A restriction matter of a bus control function was revealed about V850E/IG4-H, V850E/IH4-H

## 1. The detail of restriction

When using a bus control function, AD0-AD15 terminal becomes unsettled at idle State.

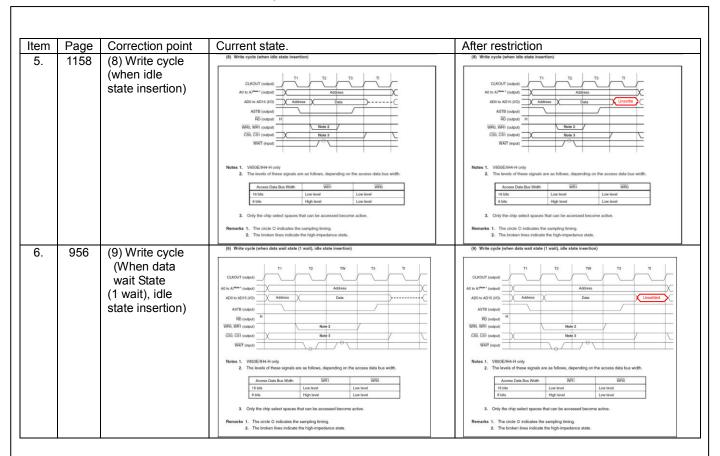

User's manual are corrected as follows.

| Item | Page | Correction point                                                                 | Current state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | After restriction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|------|------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1.   | 1148 | (1) bus cycle<br>control register<br>(BCC)                                       | Cautions 1. The internal ROM, internal RAM, and on-chip peripheral ¥O areas are not subject to idle state insertion.  2. Write to the BCC register after reset, and then do not change the set values. Also, when changing the initial values of the BSC register, do not access an external memory area until the settings are complete. Nowever, it is possible to access external memory areas whose initialization settings are complete.  3. The chip select signal (CSR) does not become active in the idle state (n = 0, 1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Cautions 1. The Internal ROM, internal RAM, and on-chip peripheral I/O areas are not subject to idle state insertion.  2. Write to the BCC register after reset, and then do not change the set values. Also, when changing the initial values of the BSC register, do not access an external memory area until the settings are complete. Novewer, it is possible to access external memory areas whose initialization settings are complete.  3. The chip select signal (CSfi) does not become active in the lide state (n = 0, 1).  4. ADO-AD15 pins will be unsettled output in the idle state                                |  |  |

| 2.   | 1153 | (3) Read cycle<br>(When idle<br>state insertion)                                 | (3) Read cycle (when life state insertion)  CLXCAT (sulput)  AD IS A ATTAIN (sulput)  FÖ (sulput)  WHO, WHT (sulput)  WHO, WHT (sulput)  Notes 1. V850EN44H only.  2. Only the clys select spaces that can be accessed become active.  Remarks 1. The click O indicates the sampling liming.  2. The broken lines indicate the high-impedance state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (3) Read cycle (when life state insertion)  CLXCUT (subput)  AD to ADTS (0) - ADDESS  AD STATE (subput)  AD to ADTS (0) - ADDESS  AD STATE (subput)  FIG. Subput)  WIN, WIT (subput)  Note 1. VBSCE/BH4 H only,  2. Only the city series spaces that can be accessed become active.  Remarks 1. The circle O indicates the sampling fining.  2. The broken lines indicate the high empolance state.                                                                                                                                                                                                                               |  |  |

| 4.   | 1154 | (4) Read cycle<br>(When data<br>wait state<br>(1 wait ),idle<br>state insertion) | (4) Read cycle (when data wait state (1 wall), liffe state insertion)  CLKOUT (output)  Address  Addre | (4) Read cycle (when data wait state (1 wait), side state insertion)  CAROUT (output)  Add to A <sup>(thick)</sup> (output)  WAIT (output)  WAIT (output)  WAIT (output)  Notes 1. VisionErisk H only,  Cob, Citi (output)  Notes 1. VisionErisk H only,  Cob, Citi (output)  Remarks 1. The circle O indicates the sampling fining,  2. The broken lines indicates the high-impedance state. |  |  |

## 2. Workaround

When using the bus function, be careful so that a signal of AD0-AD15 terminal doesn't collide with idle state.

This issue is not planned for correction. It will be made usage restriction.

Please inquire to our salesperson about details.