To our customers,

# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- 2. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics product is not intended without the prior written consent of Renesas Electronics. Renesas Electronics are product for any application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# Serial EEPROM of HN58X25xxx Series

Control Using Clock Synchronous Serial I/O (UART) of M16C

# Introduction

This document should be used for reference when implementing control of the HN58X25xxx Series serial EEPROM manufactured by Renesas Technology Corp., using the clock synchronous serial communication interface (hereafter referred to as UART) of the M16C family manufactured by Renesas Technology Corp.

The M16C family incorporates a clock synchronous serial I/O. The HN58X25xxx Series serial EEPROM can be controlled through the clock synchronous serial I/O and software.

This document describes sample programs for controlling the HN58X25xxx Series serial EEPROM by using the clock synchronous serial I/O.

# **Target Device**

The application examples described in this document are applicable when the following MCU and condition are used.

- MCU: M16C family

- Condition: Clock synchronous serial I/O is used

- Software Version: Ver.1.21

The programs can be executed by any M16C family MCU with the serial I/O.

Note however that since some functions may be altered by function addition, etc., the functions should be confirmed against the MCU manual.

Be sure to perform evaluation sufficiently when using this application note.

# Contents

| 1. | Control Method for HN58X25xxx Series Serial EEPROM 2 |

|----|------------------------------------------------------|

| 2. | Sample Programs                                      |

# 1. Control Method for HN58X25xxx Series Serial EEPROM

# 1.1 Overview of Operation

Control of the HN58X25xxx Series serial EEPROM is implemented by using the clock synchronous Serial I/O in the M16C.

The sample programs execute the following control operations.

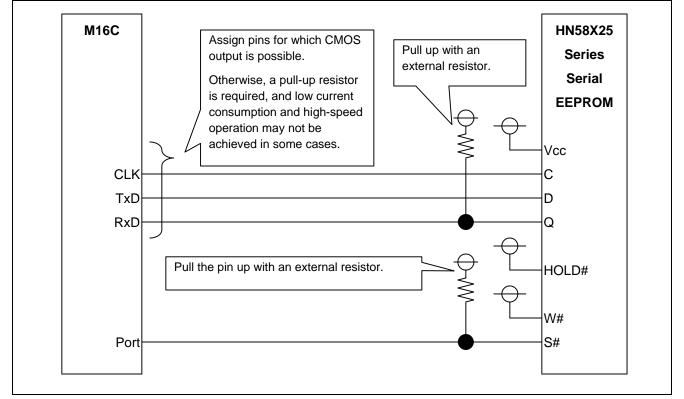

- Connects the S# pin of the serial EEPROM to a M16C port and controls it using output of the M16C general port.

- Controls data input/output by the clock synchronous serial I/O (using the internal clock). Assign the clock synchronous serial I/O pins for which CMOS output is possible and set the CMOS output to them, in order to implement the high-speed operation.

In order to control the data transmission, the empty of transmit buffer is detected and interrupt is not used but transmit interrupt request bit is used.

Therefore the register setting related to interrupt is described below.

- Set the interrupt priority level to 000b (Level 0; Interrupt disable).

- Set the transmit interrupt cause select bit to 0 (No data present in transmit buffer). (Set the DMA request cause to UART transmit interrupt request if DMA is used.)

- Control data transmission using DMAC as option.

Refer to the data sheets of the MCU and serial EEPROM and specify a usable clock frequency.

The connection method is described below.

#### Figure 1.1 Serial EEPROM Connection Example

# **1.2** Signal Timing Generation of Clock Synchronous Serial I/O

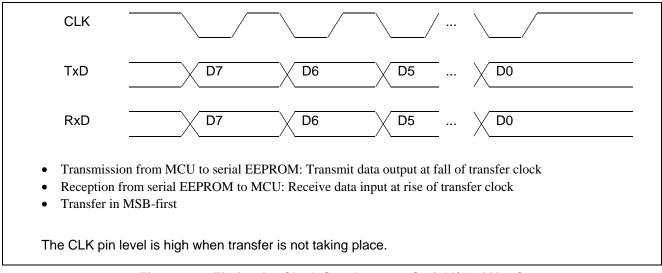

Signals are generated at the following timing to satisfy the serial EEPROM timing.

#### Figure 1.2 Timing for Clock Synchronous Serial I/O of M16C

Check the data sheets of the MCU and serial EEPROM for the maximum clock frequency that can be used.

# 1.3 Control of S# Pin of Serial EEPROM

The S# pin of the serial EEPROM is connected to a M16C port and controlled using output of the M16C general port.

The period from the falling edge of the S# pin (port of M16C) of the serial EEPROM to the falling edge of the C pin (CLK of M16C) is controlled by inserting software wait cycles.

The period from the rising edge of the C pin (CLK of M16C) to the rising edge of the S# pin (port of M16C) is controlled by inserting software wait cycles.

Check the data sheet of the serial EEPROM and set the software wait time according to the system.

# 1.4 Processing after function operating

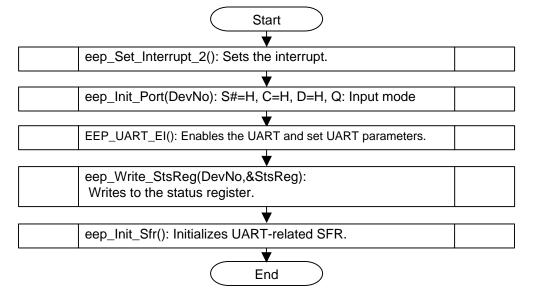

When function processing is begun, S# pin (Port of M16C) of EEPROM is set to high level first by setting the port function, and, next, C pin (CLK of M16C) of EEPROM is set to high level. Next, Serial I/O function is enabled and clock synchronous I/O mode is set. Command code etc. are output using serial I/O function after S# pin (Port of M16C) of EEPROM is set to low level.

After function processing is finished, S# pin (Port of M16C) of EEPROM is set to high level first and, next, Serial I/O function is disabled and changed to the function of general port, and next, Port/CLK/TxD/RxD pins are set to high level.

# 1.5 MCU Hardware Resources in Use

The hardware resources to be used are shown below.

In order to control the data transmission, the empty of transmit buffer is detected and interrupt is not used but transmit interrupt request bit is used.

Therefore the register setting related to interrupt is described below.

- Set the interrupt priority level to 000b (Level 0; Interrupt disable).

- Set the transmit interrupt cause select bit to 0 (No data present in transmit buffer).

(Set the DMA request cause to UART transmit interrupt request if DMA is used.)

#### Table 1.1 Hardware Resources in Use

| Resource in Use                                   | Number of Used Resources |

|---------------------------------------------------|--------------------------|

| Clock synchronous serial I/O                      | One channel (essential)  |

| Port (for control of the S# pin of serial EEPROM) | One port (essential)     |

| DMAC                                              | One channel (option)     |

The accessing mode between RAM and UART (transmit buffer or receive buffer) using DMAC is prepared as option.

# 1.6 M16C SFR (Peripheral Device Control Register) Setting - Clock Synchronous Serial I/O and Interrupt control Register

Set up the clock synchronous serial I/O as shown below to satisfy the serial EEPROM specifications/timing.

In order to control the data transmission, the empty of transmit buffer is detected and interrupt is not used but transmit interrupt request bit is used.

Therefore the register setting related to interrupt is described below.

- Set the interrupt priority level to 000b (Level 0; Interrupt disable).

- Set the transmit interrupt cause select bit to 0 (No data present in transmit buffer).

- (Set the DMA request cause to UART transmit interrupt request if DMA is used.)

#### 1.6.1 M32C/87

An example of setting based on the register descriptions of (Table 17.2 Registers to Be Used and Setting in Clock Synchronous Serial I/O Mode) in the M32C/87 Group Hardware Manual Rev. 1.00 is shown in the table below.

Clock synchronous serial I/O other than UART2 (N channel open drain output) to be used are recommended.

Continuous receive mode should be disabled. The details please refer to the technical update TN-16C-A162A/J.

| Register | Bit            | Function and Setting                                                          |

|----------|----------------|-------------------------------------------------------------------------------|

| UiTB     | 7 to 0         | Set the transmit data in these bits.                                          |

| UiRB     | 7 to 0         | The receive data is read from these bits.                                     |

|          | OER            | Overrun error flag                                                            |

| UiBRG    | 7 to 0         | Set the transfer speed in these bits.                                         |

|          |                | Clock frequency that can transfer data is different depending on the MCU.     |

| UiMR     | SMD2 to SMD0   | Write 001b to these bits. (Clock synchronous serial I/O mode)                 |

|          | CKDIR          | Write 0 to this bit. (Internal clock)                                         |

|          |                | Set the clock frequency to UiBRG.                                             |

|          | IOPOL          | Write 0 to this bit. (No reverse)                                             |

| UiC0     | CKS1, CKS0     | Select the count source of UiBRG register in these bits.                      |

|          | CRS            | Write 0 to this bit. (This function is disabled because of CRD=1.)            |

|          | TXEPT          | Transmit register empty flag (Read only)                                      |

|          | CRD            | Write 1 to this bit. (CTS# and RTS# functions are disabled.)                  |

|          | NCH            | Write 0 to this bit. (CMOS output)                                            |

|          | CKPOL          | Write 0 to this bit.                                                          |

|          |                | Transmit data is output at falling edge of transfer clock and receive data is |

|          |                | input at rising edge.                                                         |

|          | UFORM          | Write 1 to this bit. (MSB first)                                              |

|          | TE             | 0 is written to this bit at initialization. (Transmission disabled)           |

|          |                | Write 1 to this bit when transmission should be enabled.                      |

|          | TI             | Transmit buffer empty flag (Read only)                                        |

|          | RE             | 0 is written to this bit at initialization. (Reception disabled)              |

|          |                | Write 1 to this bit when reception should be enabled.                         |

|          | RI             | Receive complete flag (Read only)                                             |

|          | UilRS          | Write 0 to this bit at initialization.                                        |

|          |                | (No data present in UiTB register: TI=1)                                      |

|          | UiRRM          | Write 0 to this bit. (Continuous receive mode is disabled)                    |

|          | UiLCH          | Write 0 to this bit. (Data logic is not reversed)                             |

|          | SCLKSTPB       | UiC1                                                                          |

| UiSMR    | 7 to 0(Note 1) | Write 00 to these bits.                                                       |

| UiSMR2   | 7 to 0(Note 1) | Write 00 to these bits.                                                       |

| UiSMR3   | 7 to 0(Note 1) | Write 00 to these bits.                                                       |

| UiSMR4   | 7 to 0(Note 1) | Write 00 to these bits.                                                       |

|          | · /            |                                                                               |

#### Table 1.2 Clock Synchronous Serial I/O Mode Settings

Note 1: Sample program doesn't set 00 data to these registers because initial values of these registers after reset are 00.

The setting example of interrupt control register is shown in the table bellow.

In order to control the data transmission, the empty of transmit buffer is detected and interrupt is not used but transmit interrupt request bit is used.

**Table 1.3 Interrupt Control Register Settings**

| Register | Bit            | Function and Setting                                        |

|----------|----------------|-------------------------------------------------------------|

| SiTIC    | ILVL2 to ILVL0 | Write 000b to these bits. (Level 0: Interrupt is disabled.) |

|          | IR             | If this bit is 1, Interrupt is requested.                   |

|          |                | Write 0 to this bit according to the needs.                 |

# 1.6.2 M16C/80

An example of setting based on the register descriptions in the M16C/80 Group Hardware Manual Rev. 1.00 is shown in the table below.

Clock synchronous serial I/O other than UART2 (N channel open drain output) to be used are recommended.

Continuous receive mode should be disabled. The details please refer to the technical update TN-16C-A162A/J.

| 7 to 0<br>7 to 0        | Set the transmit data in these bits.                                                                                                                           |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         |                                                                                                                                                                |

| A                       | The receive data is read from these bits.                                                                                                                      |

| OER                     | Overrun error flag                                                                                                                                             |

| 7 to 0                  | Set the transfer speed in these bits.<br>Clock frequency that can transfer data is different depending on the MCU.                                             |

| SMD2 to SMD0            | Write 001b to these bits. (Clock synchronous serial I/O mode)                                                                                                  |

| CKDIR                   | Write 0 to this bit. (Internal clock)<br>Set the clock frequency to UiBRG.                                                                                     |

| SLEP<br>(U0MR, U1MR)    | Write 0 to this bit.                                                                                                                                           |

| IOPOL<br>(U2MR to U4MR) | Write 0 to this bit. (No reverse)                                                                                                                              |

| CKS1, CKS0              | Select the count source of UiBRG register in these bits.                                                                                                       |

| CRS                     | Write 0 to this bit. (This function is disabled because of CRD=1.)                                                                                             |

| TXEPT                   | Transmit register empty flag (Read only)                                                                                                                       |

| CRD                     | Write 1 to this bit. (CTS# and RTS# functions are disabled.)                                                                                                   |

| NCH                     | Write 0 to this bit. (CMOS output)                                                                                                                             |

| CKPOL                   | Write 0 to this bit.                                                                                                                                           |

|                         | Transmit data is output at falling edge of transfer clock and receive data is input at rising edge.                                                            |

| UFORM                   | Write 1 to this bit. (MSB first)                                                                                                                               |

| TE                      | 0 is written to this bit at initialization. (Transmission disabled)                                                                                            |

|                         | Write 1 to this bit when transmission should be enabled.                                                                                                       |

| TI                      | Transmit buffer empty flag (Read only)                                                                                                                         |

| RE                      | 0 is written to this bit at initialization. (Reception disabled)                                                                                               |

|                         | Write 1 to this bit when reception should be enabled.                                                                                                          |

| RI                      | Receive complete flag (Read only)                                                                                                                              |

| 7 to 4                  | These bits are always read as 0. The write value should always be 0.                                                                                           |

|                         | SMD2 to SMD0<br>CKDIR<br>SLEP<br>(U0MR, U1MR)<br>IOPOL<br>(U2MR to U4MR)<br>CKS1, CKS0<br>CRS<br>TXEPT<br>CRD<br>NCH<br>CKPOL<br>UFORM<br>TE<br>TI<br>RE<br>RI |

#### Table 1.4 Clock Synchronous Serial I/O Mode Settings

|         |                   | Control Using Clock Synchronous Serial I/O (UART) of M160                         |

|---------|-------------------|-----------------------------------------------------------------------------------|

| U2C1 to | TE                | 0 is written to this bit at initialization. (Transmission disabled)               |

| U4C1    |                   | Write 1 to this bit when transmission should be enabled.                          |

|         | TI                | Transmit buffer empty flag (Read only)                                            |

|         | RE                | 0 is written to this bit at initialization. (Reception disabled)                  |

|         |                   | Write 1 to this bit when reception should be enabled.                             |

|         | RI                | Receive complete flag (Read only)                                                 |

|         | UiIRS (i; 2 to 4) | 0 is written to this bit at initialization.                                       |

|         | (Note 1)          | (No data present in transmit buffer: TI=1)                                        |

|         | UiRRM (i; 2 to 4) | Write 0 to this bit. (Continuous receive mode is disabled.)                       |

|         | (Note 1)          |                                                                                   |

|         | UiLCH (i; 2 to 4) | Write 0 to this bit. (Data logic is not reversed.)                                |

|         | UiERE (i; 2 to 4) | Write 0 to this bit. (Error signal output disabled)                               |

| UCON    | U0IRS             | Write it as follows when UART0 is used.                                           |

|         |                   | Write 0 to this bit at initialization.                                            |

|         |                   | (No data present in transmit buffer: TI=1)                                        |

|         | U1IRS             | Write it as follows when UART1 is used.                                           |

|         |                   | Write 0 to this bit at initialization. (No data present in transmit buffer: TI=1) |

|         | U0RRM (Note 2)    | Write 0 to this bit. (Continuous receive mode is disabled.)                       |

|         | U1RRM (Note 2)    | Write 0 to this bit. (Continuous receive mode is disabled.)                       |

|         | 5 to 4            | The read data are invalid. The write value should always be 0.                    |

|         | RCSP              | Write 0 to this bit. (This function is disabled because of CRD are disabled.)     |

|         | 7                 | The read data is invalid. The write value should always be 0.                     |

| UiSMR   | 7 to 0(Note 3)    | Write 00 to these bits.                                                           |

| UiSMR2  | 7 to 0(Note 3)    | Write 00 to these bits.                                                           |

| UiSMR3  | 7 to 0(Note 4)    | Write 00 to these bits.                                                           |

|         |                   |                                                                                   |

Serial EEPROM of HN58X25xxx Series

Note 1: Set it similarly to UCON (UART transmit and reception control register 2) as for UART0 and UART1. Note 2: Set it similarly to UiC1 (UART transmit and reception control register 1) for UART2 to UART4.

Note 3: Sample program doesn't set 00 data to these registers because initial values of them after reset are 00.

Note 4: Sample program doesn't set 00 data to these registers other than U2SMR3 because initial values of them after reset are 00. Write 000b from DL2 to DL0 bits for U2SMR3.

The setting example of interrupt control register is shown in the table bellow.

In order to control the data transmission, the empty of transmit buffer is detected and interrupt is not used but transmit interrupt request bit is used.

| Table 1.5 Interrupt Contro | I Register Settings |

|----------------------------|---------------------|

|----------------------------|---------------------|

**PENIEGAG**

| Register | Bit            | Function and Setting                                        |

|----------|----------------|-------------------------------------------------------------|

| SiTIC    | ILVL2 to ILVL0 | Write 000b to these bits. (Level 0: Interrupt is disabled.) |

|          | IR             | If this bit is 1, Interrupt is requested.                   |

|          |                | Write 0 to this bit according to the needs.                 |

# 1.6.3 M16C/62P

An example of setting based on the register descriptions of (Table 17.2 Registers to Be Used and Setting in Clock Synchronous Serial I/O Mode) in the M16C/62P Group Hardware Manual Rev. 2.41 is shown in the table below.

Clock synchronous serial I/O other than UART2 (N channel open drain output) to be used are recommended.

Don't use UART3 and UART4.

| Set the transmit data in these bits.<br>The receive data is read from these bits. |

|-----------------------------------------------------------------------------------|

| The receive data is read from these bits.                                         |

|                                                                                   |

| Overrun error flag                                                                |

| Set the transfer speed in these bits.                                             |

| Clock frequency that can transfer data is different depending on the MCU.         |

| Write 001b to these bits. (Clock synchronous serial I/O mode)                     |

| Write 0 to this bit. (Internal clock)                                             |

| Set the clock frequency to UiBRG.                                                 |

| Write 0 to this bit. (No reverse)                                                 |

| Select the count source of UiBRG register in these bits.                          |

| Write 0 to this bit. (This function is disabled because of CRD=1.)                |

| Transmit register empty flag (Read only)                                          |

| Write 1 to this bit. (CTS# and RTS# functions are disabled.)                      |

| Write 0 to this bit. (CMOS output)                                                |

| Write 0 to this bit.                                                              |

| Transmit data is output at falling edge of transfer clock and receive data is     |

| input at rising edge.                                                             |

| Write 1 to this bit. (MSB first)                                                  |

| 0 is written to this bit at initialization. (Transmission disabled)               |

| Write 1 to this bit when transmission should be enabled.                          |

| Transmit buffer empty flag (Read only)                                            |

| 0 is written to this bit at initialization. (Reception disabled)                  |

| Write 1 to this bit when reception should be enabled.                             |

| Receive complete flag (Read only)                                                 |

| The read data are invalid. The write value should always be 0.                    |

| Write 0 to this bit. (Data logic is not reversed.)                                |

| Write 0 to this bit. (Error signal output disabled.)                              |

|                                                                                   |

# Table 1.6 Clock Synchronous Serial I/O Mode Settings

| 1004   |                |                                                                                   |  |

|--------|----------------|-----------------------------------------------------------------------------------|--|

| U2C1   | TE             | 0 is written to this bit at initialization. (Transmission disabled)               |  |

|        | <u> </u>       | Write 1 to this bit when transmission should be enabled.                          |  |

|        |                | Transmit buffer empty flag (Read only)                                            |  |

|        | RE             | 0 is written to this bit at initialization. (Reception disabled)                  |  |

|        |                | Write 1 to this bit when reception should be enabled.                             |  |

|        | RI             | Receive complete flag (Read only)                                                 |  |

|        | U2IRS (Note1)  | Write 0 to this bit at initialization.                                            |  |

|        |                | (No data present in transmit buffer: TI=1)                                        |  |

|        | U2RRM (Note1)  | Write 0 to this bit at initialization. (Continuous receive mode is disabled.)     |  |

|        |                | Select UART2 continuous receive mode according to the usage.                      |  |

|        | U2LCH          | Write 0 to this bit. (Data logic is not reversed.)                                |  |

|        | U2ERE          | Write 0 to this bit. (Error signal output disabled)                               |  |

| UiSMR  | 7 to 0(Note 3) | Write 00 to these bits.                                                           |  |

| UiSMR2 | 7 to 0(Note 3) | Write 00 to these bits.                                                           |  |

| UiSMR3 | 7 to 0(Note 3) | Write 00 to these bits.                                                           |  |

| UiSMR4 | 7 to 0(Note 3) | Write 00 to these bits.                                                           |  |

| UCON   | U0IRS          | Set it as follows when UART0 is used.                                             |  |

|        |                | Write 0 to this bit at initialization.                                            |  |

|        |                | (No data present in transmit buffer: TI=1)                                        |  |

|        | U1IRS          | Set it as follows when UART1 is used.                                             |  |

|        |                | Write 0 to this bit at initialization. (No data present in transmit buffer: TI=1) |  |

|        | U0RRM (Note 2) | Set it as follows when UART0 is used.                                             |  |

|        |                | Write 0 to this bit at initialization. (Continuous receive mode is disabled.)     |  |

|        |                | Select UART0 continuous receive mode according to the usage.                      |  |

|        | U1RRM (Note 2) | Set it as follows when UART1 is used.                                             |  |

|        |                | Write 0 to this bit at initialization. (Continuous receive mode is disabled.)     |  |

|        |                | Select UART1 continuous receive mode according to the usage.                      |  |

|        | CLKMD0         | Write 0 to this bit. (This function is disabled because of CLKMD1=1)              |  |

|        | CLKMD1         | Write 0 to this bit. (CLK is output from only CLK1.)                              |  |

|        | RCSP           | Write 0 to this bit. (This function is disabled because of CRD are disabled.      |  |

|        | 7              | The read data is invalid. The write value should always be 0.                     |  |

Serial EEPROM of HN58X25xxx Series

Note 2: Set it similarly to U2C1 (UART transmit and reception control register 1) for UART2. Note 3: Sample program doesn't set 00 data to these registers because initial values of them after reset are

00.

The setting example of interrupt control register is shown in the table bellow.

In order to control the data transmission, the empty of transmit buffer is detected and interrupt is not used but transmit interrupt request bit is used.

| Register | Bit            | Function and Setting                                        |

|----------|----------------|-------------------------------------------------------------|

| SiTIC    | ILVL2 to ILVL0 | Write 000b to these bits. (Level 0: Interrupt is disabled.) |

|          | IR             | If this bit is 1, Interrupt is requested.                   |

|          |                | Write 0 to this bit according to the needs.                 |

#### **Table 1.7 Interrupt Control Register Settings**

**PENIESAS**

# 1.6.4 M16C/30P

An example of setting based on the register descriptions of (Table 15.2 Registers to Be Used and Setting in Clock Synchronous Serial I/O Mode) in the M16C/30P Group Hardware Manual Rev. 1.11 is shown in the table below.

Clock synchronous serial I/O other than UART2 (N channel open drain output) to be used are recommended.

| Register | Bit          | Function and Setting                                                                                |

|----------|--------------|-----------------------------------------------------------------------------------------------------|

| UiTB     | 7 to 0       | Set the transmit data in these bits.                                                                |

| UiRB     | 7 to 0       | The receive data is read from these bits.                                                           |

|          | OER          | Overrun error flag                                                                                  |

| UiBRG    | 7 to 0       | Set the transfer speed in these bits.                                                               |

|          |              | Clock frequency that can transfer data is different depending on the MCU.                           |

| UiMR     | SMD2 to SMD0 | Write 001b to these bits. (Clock synchronous serial I/O mode)                                       |

|          | CKDIR        | Write 0 to this bit. (Internal clock)                                                               |

|          |              | Set the clock frequency to UiBRG.                                                                   |

|          | IOPOL        | Write 0 to this bit. (No reverse)                                                                   |

| UiC0     | CLK1, CLK0   | Select the count source of UiBRG register in these bits.                                            |

|          | CRS          | Write 0 to this bit. (This function is disabled because of CRD=1.)                                  |

|          | TXEPT        | Transmit register empty flag (Read only)                                                            |

|          | CRD          | Write 1 to this bit. (CTS# and RTS# functions are disabled.)                                        |

|          | NCH          | Write 0 to this bit. (CMOS output)                                                                  |

|          | CKPOL        | Write 0 to this bit.                                                                                |

|          |              | Transmit data is output at falling edge of transfer clock and receive data is input at rising edge. |

|          | UFORM        | Write 1 to this bit. (MSB first)                                                                    |

| U0C1,    | TE           | 0 is written to this bit at initialization. (Transmission disabled)                                 |

| U1C1     |              | Write 1 to this bit when transmission should be enabled.                                            |

|          | TI           | Transmit buffer empty flag (Read only)                                                              |

|          | RE           | 0 is written to this bit at initialization. (Reception disabled)                                    |

|          |              | Write 1 to this bit when reception should be enabled.                                               |

|          | RI           | Receive complete flag (Read only)                                                                   |

|          | 5 to 4       | The read data are invalid. The write value should always be 0.                                      |

|          | U0LCH/U1LCH  | Write 0 to this bit. (Data logic is not reversed.)                                                  |

|          | U0ERE/U1ERE  | Write 0 to this bit. (Error signal output disabled)                                                 |

#### Table 1.8 Clock Synchronous Serial I/O Mode Settings

| Re     | NESA           | Serial EEPROM of HN58X25xxx Series<br>Control Using Clock Synchronous Serial I/O (UART) of M16C                                               |

|--------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| U2C1   | TE             | 0 is written to this bit at initialization. (Transmission disabled)                                                                           |

|        |                | Write 1 to this bit when transmission should be enabled.                                                                                      |

|        | TI             | Transmit buffer empty flag (Read only)                                                                                                        |

|        | RE             | 0 is written to this bit at initialization. (Reception disabled)                                                                              |

|        |                | Write 1 to this bit when reception should be enabled.                                                                                         |

|        | RI             | Receive complete flag (Read only)                                                                                                             |

|        | U2IRS (Note1)  | Write 0 to this bit at initialization.                                                                                                        |

|        |                | (No data present in transmit buffer: TI=1)                                                                                                    |

|        | U2RRM (Note1)  | Write 0 to this bit at initialization. (Continuous receive mode is disabled.)<br>Select UART2 continuous receive mode according to the usage. |

|        | U2LCH          | Write 0 to this bit. (Data logic is not reversed.)                                                                                            |

|        | U2ERE          | Write 0 to this bit. (Error signal output disabled)                                                                                           |

| UiSMR  | 7 to 0(Note 3) | Write 00 to these bits.                                                                                                                       |

| UiSMR2 | 7 to 0(Note 3) | Write 00 to these bits.                                                                                                                       |

| UiSMR3 | 7 to 0(Note 3) | Write 00 to these bits.                                                                                                                       |

| UiSMR4 | 7 to 0(Note 3) | Write 00 to these bits.                                                                                                                       |

| UCON   | U0IRS          | Set it as follows when UART0 is used.                                                                                                         |

|        |                | Write 0 to this bit at initialization. (No data present in transmit buffer: TI=1)                                                             |

|        | U1IRS          | Set it as follows when UART1 is used.                                                                                                         |

|        |                | Write 0 to this bit at initialization. (No data present in transmit buffer: TI=1)                                                             |

|        | U0RRM (Note 2) | Set it as follows when UART0 is used.                                                                                                         |

|        | · · · · · ·    | Write 0 to this bit at initialization. (Continuous receive mode is disabled.)                                                                 |

|        |                | Select UART0 continuous receive mode according to the usage.                                                                                  |

|        | U1RRM (Note 2) | Set it as follows when UART1 is used.                                                                                                         |

|        |                | Write 0 to this bit at initialization. (Continuous receive mode is disabled.)                                                                 |

|        |                | Select UART1 continuous receive mode according to the usage.                                                                                  |

|        | CLKMD0         | Write 0 to this bit. (This function is disabled because of CLKMD1=1.)                                                                         |

|        | CLKMD1         | Write 0 to this bit. (CLK is output from only CLK1.)                                                                                          |

|        | RCSP           | Write 0 to this bit. (This function is disabled because of CRD are disabled.)                                                                 |

|        | 7              | The read data is invalid. The write value should always be 0.                                                                                 |

Note 1: Set it similarly to UCON (UART transmit and reception control register 2) for UART0 and UART1.

Note 2: Set it similarly to U2C1 (UART transmit and reception control register 1) for UART2.

Note 3: Sample program doesn't set 00 data to these registers because initial values of them after reset are 00.

The setting example of interrupt control register is shown in the table bellow.

In order to control the data transmission, the empty of transmit buffer is detected and interrupt is not used but transmit interrupt request bit is used.

| Register | Bit            | Function and Setting                                        |

|----------|----------------|-------------------------------------------------------------|

| SiTIC    | ILVL2 to ILVL0 | Write 000b to these bits. (Level 0: Interrupt is disabled.) |

|          | IR             | If this bit is 1, Interrupt is requested.                   |

|          |                | Write 0 to this bit according to the needs.                 |

#### **Table 1.9 Interrupt Control Register Settings**

# 1.6.5 M16C/29

An example of setting based on the register descriptions of (Table 14.2 Registers to Be Used and Setting in Clock Synchronous Serial I/O Mode) in the M16C/29 Group Hardware Manual Rev. 1.00 is shown in the table below.

# Don't use UART3 and UART4.

# Table 1.10 Clock Synchronous Serial I/O Mode Settings

|       | Bit            | Function and Setting                                                              |

|-------|----------------|-----------------------------------------------------------------------------------|

| UiTB  | 7 to 0         | Set the transmit data in these bits.                                              |

| UiRB  | 7 to 0         | The receive data is read from these bits.                                         |

|       | OER            | Overrun error flag                                                                |

| UiBRG | 7 to 0         | Set the transfer speed in these bits.                                             |

|       |                | Clock frequency that can transfer data is different depending on the MCU.         |

| UiMR  | SMD2 to SMD0   | Write 001b to these bits. (Clock synchronous serial I/O mode)                     |

|       | CKDIR          | Write 0 to this bit. (Internal clock)                                             |

|       |                | Set the clock frequency to UiBRG.                                                 |

|       | 7              | Write 0 to this bit.                                                              |

| UiC0  | CKS1, CKS0     | Select the count source of UiBRG register in these bits.                          |

|       | CRS            | Write 0 to this bit. (This function is disabled because of CRD=1.)                |

|       | TXEPT          | Transmit register empty flag (Read only)                                          |

|       | CRD            | Write 1 to this bit. (CTS# and RTS# functions are disabled.)                      |

|       | NCH            | Write 0 to this bit. (CMOS output)                                                |

|       | CKPOL          | Write 0 to this bit.                                                              |

|       |                | Transmit data is output at falling edge of transfer clock and receive data is     |

|       |                | input at rising edge.                                                             |

|       | UFORM          | Write 1 to this bit. (MSB first)                                                  |

| U0C1, | TE             | 0 is written to this bit at initialization. (Transmission disabled)               |

| U1C1  |                | Write 1 to this bit when transmission should be enabled.                          |

|       | TI             | Transmit buffer empty flag (Read only)                                            |

|       | RE             | 0 is written to this bit at initialization. (Reception disabled)                  |

|       |                | Write 1 to this bit when reception should be enabled.                             |

|       | RI             | Receive complete flag (Read only)                                                 |

|       | 7 to 4         | These bits are always read as 0. The write value should always be 0.              |

| U2C1  | TE             | 0 is written to this bit at initialization. (Transmission disabled)               |

|       |                | Write 1 to this bit when transmission should be enabled.                          |

|       | TI             | Transmit buffer empty flag (Read only)                                            |

|       | RE             | 0 is written to this bit at initialization. (Reception disabled)                  |

|       |                | Write 1 to this bit when reception should be enabled.                             |

|       | RI             | Receive complete flag (Read only)                                                 |

|       | U2IRS (Note 1) | Write 0 to this bit at initialization. (No data present in transmit buffer: TI=1) |

|       | U2RRM (Note 1) | Write 0 to this bit at initialization. (Continuous receive mode is disabled.)     |

|       |                | Select UART2 continuous receive mode according to the usage.                      |

|       | U2LCH          | Write 0 to this bit. (Data logic is not reversed.)                                |

|       | U2ERE          | Write 0 to this bit. (Error signal output disabled.)                              |

# RENESAS

| U2SMR  | 7 to 0(Note 3) | Write 00 to these bits.                                                           |

|--------|----------------|-----------------------------------------------------------------------------------|

| U2SMR2 | 7 to 0(Note 3) | Write 00 to these bits.                                                           |

| U2SMR3 | 7 to 0(Note 3) | Write 00 to these bits.                                                           |

| U2SMR4 | 7 to 0(Note 3) | Write 00 to these bits.                                                           |

| UCON   | U0IRS          | Set it as follows when UART0 is used.                                             |

|        |                | Write 0 to this bit at initialization. (No data present in transmit buffer: TI=1) |

|        | U1IRS          | Set it as follows when UART1 is used.                                             |

|        |                | Write 0 to this bit at initialization. (No data present in transmit buffer: TI=1) |

|        | U0RRM (Note 2) | Set it as follows when UART0 is used.                                             |

|        |                | Write 0 to this bit at initialization. (Continuous receive mode is disabled.)     |

|        |                | Select UART0 continuous receive mode according to the usage.                      |

|        | U1RRM (Note 2) | Set it as follows when UART1 is used.                                             |

|        |                | Write 0 to this bit at initialization. (Continuous receive mode is disabled.)     |

|        |                | Select UART1 continuous receive mode according to the usage.                      |

|        | CLKMD0         | Write 0 to this bit. (This function is disabled because of CLKMD1=1.)             |

|        | CLKMD1         | Write 0 to this bit. (CLK is output from only CLK1).                              |

|        | RCSP           | Write 0 to this bit. (This function is disabled because of CRD are disabled.)     |

|        | 7              | The read data is invalid. The write value should always be 0.                     |

|        |                |                                                                                   |

Note 1: Set it similarly to UCON (UART transmit and reception control register 2) for UART0 and UART1. Note 2: Set it similarly to U2C1 (UART transmit and reception control register 1) for UART2.

Note 3: Sample program doesn't set 00 data to these registers because initial values of them after reset are 00.

The setting example of interrupt control register is shown in the table bellow.

In order to control the data transmission, the empty of transmit buffer is detected and interrupt is not used but transmit interrupt request bit is used.

#### **Table 1.11 Interrupt Control Register Settings**

| Register | Bit            | Function and Setting                                        |

|----------|----------------|-------------------------------------------------------------|

| SiTIC    | ILVL2 to ILVL0 | Write 000b to these bits. (Level 0: Interrupt is disabled.) |

|          | IR             | If this bit is 1, Interrupt is requested.                   |

|          |                | Write 0 to this bit according to the needs.                 |

#### 1.6.6 R8C/25

An example of setting based on the register descriptions of (Table 15.2 Registers to Be Used and Setting in Clock Synchronous Serial I/O Mode) in the R8C/25 Group Hardware Manual Rev. 2.00 is shown in the table below.

#### UART1can't be used, because it is not supported Clock synchronous.

|            | •            | -                                                                                 |

|------------|--------------|-----------------------------------------------------------------------------------|

| Register   | Bit          | Function and Setting                                                              |

| UiTB       | 7 to 0       | Set the transmit data in these bits.                                              |

| Uirb       | 7 to 0       | The receive data is read from these bits.                                         |

|            | OER          | Overrun error flag                                                                |

| UiBRG      | 7 to 0       | Set the transfer speed in these bits.                                             |

|            |              | Clock frequency that can transfer data is different depending on the MCU.         |

| UiMR       | SMD2 to SMD0 | Write 001b to these bits. (Clock synchronous serial I/O mode)                     |

|            | CKDIR        | Write 0 to this bit. (Internal clock)                                             |

|            |              | Set the clock frequency to UiBRG.                                                 |

|            | 7            | Write 0 to this bit.                                                              |

| UiC0       | CKS1, CKS0   | Select the count source of UiBRG register in these bits.                          |

|            | 2            | Write 0 to this bit.                                                              |

|            | TXEPT        | Transmit register empty flag (Read only)                                          |

|            | 4            | This bit is always read as 0. The write value should always be 0.                 |

|            | NCH          | Write 0 to this bit. (CMOS output)                                                |

|            | CKPOL        | Write 0 to this bit.                                                              |

|            |              | Transmit data is output at falling edge of transfer clock and receive data is     |

|            |              | input at rising edge.                                                             |

|            | UFORM        | Write 1 to this bit. (MSB first)                                                  |

| UiC1       | TE           | 0 is written to this bit at initialization. (Transmission disabled)               |

|            |              | Write 1 to this bit when transmission should be enabled.                          |

|            | TI           | Transmit buffer empty flag (Read only)                                            |

|            | RE           | 0 is written to this bit at initialization. (Reception disabled)                  |

|            |              | Write 1 to this bit when reception should be enabled.                             |

|            | RI           | Receive complete flag (Read only)                                                 |

|            | UilRS        | Write 0 to this bit at initialization. (No data present in transmit buffer: TI=1) |

|            | UiRRM        | Write 0 to this bit at initialization. (Continuous receive mode is disabled.)     |

|            |              | Select UARTi continuous receive mode according to the usage.                      |

|            | 7 to 6       | These bits are always read as 0. The write value should always be 0.              |

| <b>T</b> 1 |              | control register is shown in the table bellow                                     |

#### Table 1.12 Clock Synchronous Serial I/O Mode Settings

The setting example of interrupt control register is shown in the table bellow.

In order to control the data transmission, the empty of transmit buffer is detected and interrupt is not used but transmit interrupt request bit is used.

| Register | Bit            | Function and Setting                                        |

|----------|----------------|-------------------------------------------------------------|

| SiTIC    | ILVL2 to ILVL0 | Write 000b to these bits. (Level 0: Interrupt is disabled.) |

|          | IR             | If this bit is 1, Interrupt is requested.                   |

|          |                | Write 0 to this bit according to the needs.                 |

# 1.7 M16C SFR (Peripheral Device Control Register) Setting - DMAC and Interrupt control Register

High-speed data transmission is possible using DMAC. The accessing mode between RAM and UART (transmit buffer or receive buffer) using DMAC is prepared as option.

# 1.7.1 M32C/87

An example of setting based on the register descriptions in the M32C/87 Group Hardware Manual Rev. 1.00 is shown in the table below.

The DMAC-related registers are CPU internal registers. Use LDC command when data are written to registers.

#### Table 1.14 DMAC Settings

| Register | Bit            | Function and Setting                                                                    |

|----------|----------------|-----------------------------------------------------------------------------------------|

| UMiSL    | DSEL4 to DSEL0 | Select either UARTi transmit interrupt request or UARTi receive interrupt               |

|          |                | request according to the transfer mode.                                                 |

|          |                | Change these bits while MDi0 and MDi1 bits are set to 00 (DMA inhibit).                 |

|          |                | Write 1 to DRQ bit at the same time when settings are changed.                          |

|          | DSR            | Write 0 to this bit. Because software trigger is not used                               |

|          | 6              | This bit is always read as 0. The write value should always be 0.                       |

|          | DRQ            | Don't write 0 to this bit.                                                              |

| DMD0     | MD01 to MD00   | Write 01b to these bits when DMA channel 0 is used. (Single transfer)                   |

|          | BW0            | Write 0 to this bit when DMA channel 0 is used. (8 bit)                                 |

|          | RW0            | Set the value according to the transmission or reception when DMA channel 0 is used.    |

|          | MD11 to MD10   | Write 01b to these bits when DMA channel 1 is used. (Single transfer)                   |

|          | BW1            | Write 0 to this bit when DMA channel 1 is used. (8 bit)                                 |

|          | RW1            | Set the value according to the transmission or reception when DMA channel 1 is used.    |

| DMD1     | MD21 to MD20   | Write 01b to these bits when DMA channel 2 is used. (Single transfer)                   |

|          | BW2            | Write 0 to this bit when DMA channel 2 is used. (8 bit)                                 |

|          | RW2            | Set the value according to the transmission or reception when DMA channel 2 is used.    |

|          | MD31 to MD30   | Write 01b to these bits when DMA channel 3 is used. (Single transfer)                   |

|          | BW3            | Write 0 to this bit when DMA channel 3 is used. (8 bit)                                 |

|          | RW3            | Set the value according to the transmission or reception when DMA channel 3 is used.    |

| DCTi     | 15 to 0        | Set the number of transfer count of transfer counter.                                   |

| DRCi     | 15 to 0        | Reload value of transfer count register. Set the number of transfer count.              |

| DMAi     | 23 to 0        | Set the source address or destination address.                                          |

| DSAi     | 23 to 0        | Set the source address or destination address.                                          |

| DRAi     | 23 to 0        | Reload value of memory address register. Set the source address or destination address. |

The setting example of interrupt control register is shown in the table bellow.

#### **Table 1.15 Interrupt Control Register Settings**

| Register | Bit            | Function and Setting                                        |

|----------|----------------|-------------------------------------------------------------|

| DMilC    | ILVL2 to ILVL0 | Write 000b to these bits. (Level 0: Interrupt is disabled.) |

|          | IR             | If this bit is 1, Interrupt is requested.                   |

|          |                | Write 0 to this bit according to the needs.                 |

This sample program for M32C/87 disables DMA control.

# 1.7.2 M16C/80

An example of setting based on the register descriptions in the M16C/80 Group Hardware Manual Rev. 1.00 is shown in the table below.

The DMAC-related registers are CPU internal registers. Use LDC command when data are written to registers.

#### Table 1.16 DMAC Settings

| Register | Bit            | Function and Setting                                                                    |

|----------|----------------|-----------------------------------------------------------------------------------------|

| UMiSL    | DSEL4 to DSEL0 | Select either UARTi transmit or UARTi receive according to the transfer                 |

|          |                | mode.                                                                                   |

|          |                | Change these bits while MDi0 and MDi1 bits are set to 00 (DMA inhibit).                 |

|          |                | Write 1 to DRQ bit at the same time when settings are changed.                          |

|          | DSR            | Write 0 to this bit. Because software trigger is not used                               |

|          | 6              | This bit is always read as 0. The write value should always be 0.                       |

|          | DRQ            | Don't write 0 to this bit.                                                              |

| DMD0     | MD01 to MD00   | Write 01b to these bits when DMA channel 0 is used. (Single transfer)                   |

|          | BW0            | Write 0 to this bit when DMA channel 0 is used. (8 bit)                                 |

|          | RW0            | Set the value according to the transmission or reception when DMA channel 0 is used.    |

|          | MD11 to MD10   | Write 01b to these bits when DMA channel 1 is used. (Single transfer)                   |

|          | BW1            | Write 0 to this bit when DMA channel 1 is used. (8 bit)                                 |

|          | RW1            | Set the value according to the transmission or reception when DMA                       |

|          |                | channel 1 is used.                                                                      |

| DMD1     | MD21 to MD20   | Write 01b to these bits when DMA channel 2 is used. (Single transfer)                   |

|          | BW2            | Write 0 to this bit when DMA channel 2 is used. (8 bit)                                 |

|          | RW2            | Set the value according to the transmission or reception when DMA channel 2 is used.    |

|          | MD31 to MD30   | Write 01b to these bits when DMA channel 3 is used. (Single transfer)                   |

|          | BW3            | Write 0 to this bit when DMA channel 3 is used. (8 bit)                                 |

|          | RW3            | Set the value according to the transmission or reception when DMA channel 3 is used.    |

| DCTi     | 15 to 0        | Set the number of transfer count of transfer counter.                                   |

| DRCi     | 15 to 0        | Reload value of transfer count register. Set the number of transfer count.              |

| DMAi     | 23 to 0        | Set the source address or destination address.                                          |

| DSAi     | 23 to 0        | Set the source address or destination address.                                          |

| DRAi     | 23 to 0        | Reload value of memory address register. Set the source address or destination address. |

The setting example of interrupt control register is shown in the table bellow.

#### **Table 1.17 Interrupt Control Register Settings**

| Register | Bit            | Function and Setting                                        |

|----------|----------------|-------------------------------------------------------------|

| DMilC    | ILVL2 to ILVL0 | Write 000b to these bits. (Level 0: Interrupt is disabled.) |

|          | IR             | If this bit is 1, Interrupt is requested.                   |

|          |                | Write 0 to this bit according to the needs.                 |

This sample program for M16C/80 disables DMA control.

# 1.7.3 M16C/62P

An example of setting based on the register descriptions in the M16C/62P Group Hardware Manual Rev. 2.41 is shown in the table below.

#### Table 1.18 DMAC Settings

| Register | Bit            | Function and Setting                                                          |

|----------|----------------|-------------------------------------------------------------------------------|

| UMiSL    | DSEL3 to DSEL0 | Select either UARTi transmit or UARTi receive according to the transfer mode. |

|          |                | Write 0 to DMS bit because the factor is UART transmit or UART reception.     |

|          | 5 to 4         | These bits are always read as 0. The write value should always be 0.          |

|          | DMS            | Write 0 to this bit because the factor is UART transmit or UART reception.    |

|          | DSR            | Write 0 to this bit because software trigger is not used                      |

| DMiCON   | DMBIT          | Write 1 to this bit. (8 bit)                                                  |

|          | DMASL          | Write 0 to these bits. (Single transfer)                                      |

|          | DMAS           | DMA request bit.                                                              |

|          |                | Write 0 to this bit at initialization. (DMA Not requested)                    |

|          | DMAE           | Write 0 to this bit at initialization. (Disable)                              |

|          |                | Write 1 to this bit when DMA is enabled                                       |

|          | DSD            | 0 is written to this bit at initialization. (Fixed)                           |

|          |                | Select according to the source address                                        |

|          | DAD            | 0 is written to this bit at initialization. (Fixed)                           |

|          |                | Select according to the destination address                                   |

|          | 7 to 6         | These bits are always read as 0. The write value should always be 0.          |

| SARi     | 19 to 0        | Set the source address of transfer.                                           |

|          | 23 to 20       | These bits are always read as 0. The write value should always be 0.          |

| DARi     | 19 to0         | Set the destination address of transfer.                                      |

|          | 23 to 20       | These bits are always read as 0. The write value should always be 0.          |

| TCRi     | 15 to 0        | Set the transfer count –1.                                                    |

The setting example of interrupt control register is shown in the table bellow.

#### Table 1.19 Interrupt Control Register Settings

| Register | Bit            | Function and Setting                                       |

|----------|----------------|------------------------------------------------------------|

| DMilC    | ILVL2 to ILVL0 | Write 000b to these bits. (Level 0: Interrupt is disable.) |

|          | IR             | If this bit is 1, Interrupt is requested.                  |

|          |                | Write 0 to this bit according to the needs.                |

Note: UART1 is recommended not to use when DMA transfer is used.

When UART1 is in transmit state, DMA request factor select register is assigned to DMA0. When UART1 is in reception state, DMA request factor select register is assigned to DMA1. In order to DMA transfer is implemented, Both DMA0 and DMA1 have to be used and software has to be modified.

# 1.7.4 M16C/30P

An example of setting based on the register descriptions in the M16C/30P Group Hardware Manual Rev. 1.11 is shown in the table below.

#### Table 1.20 DMAC Settings

| Register | Bit            | Function and Setting                                                 |

|----------|----------------|----------------------------------------------------------------------|

| UMiSL    | DSEL3 to DSEL0 | Select either UARTi transmit or UARTi receive according to the       |

|          |                | transfer mode.                                                       |

|          |                | Write 0 to DMS bit because the factor is UART transmit or UART       |

|          |                | reception.                                                           |

|          | 5 to 4         | These bits are always read as 0. The write value should always be 0. |

|          | DMS            | Write 0 to this bit because the factor is UART transmit or UART      |

|          |                | reception.                                                           |

|          | DSR            | Write 0 to this bit because software trigger is not used             |

| DMiCON   | DMBIT          | Write 1 to this bit. (8 bit)                                         |

|          | DMASL          | Write 0 to these bits. (Single transfer)                             |

|          | DMAS           | DMA request bit.                                                     |

|          |                | Write 0 to this bit at initialization. (DMA Not requested)           |

|          | DMAE           | Write 0 to this bit at initialization. (Disable)                     |

|          |                | Write 1 to this bit when DMA is enabled                              |

|          | DSD            | 0 is written to this bit at initialization. (Fixed)                  |

|          |                | Select according to the source address                               |

|          | DAD            | 0 is written to this bit at initialization. (Fixed)                  |

|          |                | Select according to the destination address                          |

|          | 7 to 6         | These bits are always read as 0. The write value should always be 0. |

| SARi     | 19 to 0        | Set the source address of transfer.                                  |

|          | 23 to 20       | These bits are always read as 0. The write value should always be 0. |

| DARi     | 19 to0         | Set the destination address of transfer.                             |

|          | 23 to 20       | These bits are always read as 0. The write value should always be 0. |

| TCRi     | 15 to 0        | Set the transfer count –1.                                           |

|          |                |                                                                      |

The setting example of interrupt control register is shown in the table bellow.

#### **Table 1.21 Interrupt Control Register Settings**

| Register | Bit            | Function and Setting                                        |

|----------|----------------|-------------------------------------------------------------|

| DMilC    | ILVL2 to ILVL0 | Write 000b to these bits. (Level 0: Interrupt is disabled.) |

|          | IR             | If this bit is 1, Interrupt is requested.                   |

|          |                | Write 0 to this bit according to the needs.                 |

Note: UART1 is recommended not to use when DMA transfer is used.

When UART1 is in transmit state, DMA request factor select register is assigned to DMA0. When UART1 is in reception state, DMA request factor select register is assigned to DMA1. In order to DMA transfer is implemented, Both DMA0 and DMA1 have to be used and software has to be modified.

# 1.7.5 M16C/29

An example of setting based on the register descriptions in the M16C/29 Group Hardware Manual Rev. 1.00 is shown in the table below.

#### Table 1.22 DMAC Settings

| Register | Bit            | Function and Setting                                                          |