改訂一覧は表紙をクリックして直接ご覧になれます。 改訂一覧は改訂箇所をまとめたものであり、詳細については、 必ず本文の内容をご確認ください。

# SH7080 グループ

ユーザーズマニュアル ハードウェア編 ルネサス 32 ビット RISC マイクロコンピュータ SuperH™ RISC engine ファミリ

| SH7083 | R5F7083 |

|--------|---------|

|        | R5M7083 |

|        | R5S7083 |

| SH7084 | R5F7084 |

|        | R5M7084 |

|        | R5S7084 |

| SH7085 | R5F7085 |

|        | R5M7085 |

|        | R5S7085 |

| SH7086 | R5F7086 |

#### ご注意書き

- 1. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、 応用例を説明するものです。お客様の機器・システムの設計において、回路、ソフトウェアお よびこれらに関連する情報を使用する場合には、お客様の責任において行ってください。これ らの使用に起因して、お客様または第三者に生じた損害に関し、当社は、一切その責任を負い ません。

- 2. 本資料に記載されている情報は、正確を期すため慎重に作成したものですが、誤りがないことを保証するものではありません。万一、本資料に記載されている情報の誤りに起因する損害がお客様に生じた場合においても、当社は、一切その責任を負いません。

3. 本資料に記載された製品デ-タ、図、表、プログラム、アルゴリズム、応用回路例等の情報の

- 3. 本資料に記載された製品デ・タ、図、表、プログラム、アルゴリズム、応用回路例等の情報の使用に起因して発生した第三者の特許権、著作権その他の知的財産権に対する侵害に関し、当社は、何らの責任を負うものではありません。当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 4 . 当社製品を改造、改変、複製等しないでください。かかる改造、改変、複製等により生じた損害に関し、当社は、一切その責任を負いません。

- 5. 当社は、当社製品の品質水準を「標準水準」および「高品質水準」に分類しており、 各品質水準は、以下に示す用途に製品が使用されることを意図しております。

音面員小学は、以下に小り用述に製品が使用されることを息図してのります。 標準水準: コンピュータ、OA機器、通信機器、計測機器、AV機器、

家電、工作機械、パーソナル機器、産業用ロボット等

高品質水準: 輸送機器(自動車、電車、船舶等) 交通用信号機器、

防災・防犯装置、各種安全装置等

当社製品は、直接生命・身体に危害を及ぼす可能性のある機器・システム(生命維持装置、人体に埋め込み使用するもの等)、もしくは多大な物的損害を発生させるおそれのある機器・システム(原子力制御システム、軍事機器等)に使用されることを意図しておらず、使用することはできません。 たとえ、意図しない用途に当社製品を使用したことによりお客様または第三者に損害が生じても、当社は一切その責任を負いません。 なお、ご不明点がある場合は、当社営業にお問い合わせください。

- 6. 当社製品をご使用の際は、当社が指定する最大定格、動作電源電圧範囲、放熱特性、実装条件 その他の保証範囲内でご使用ください。当社保証範囲を超えて当社製品をご使用された場合の 故障および事故につきましては、当社は、一切その責任を負いません。

- 7. 当社は、当社製品の品質および信頼性の向上に努めていますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は耐放射線設計については行っておりません。当社製品の故障または誤動作が生じた場合も、人身事故、火災事故、社会的損害等を生じさせないよう、お客様の責任において、冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、お客様の機器・システムとしての出荷保証を行ってください。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様の機器・システムとしての安全検証をお客様の責任で行ってください。

- 8. 当社製品の環境適合性等の詳細につきましては、製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 9. 本資料に記載されている当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器・システムに使用することはできません。また、当社製品および技術を大量破壊兵器の開発等の目的、軍事利用の目的その他軍事用途に使用しないでください。当社製品または技術を輸出する場合は、「外国為替及び外国貿易法」その他輸出関連法令を遵守し、かかる法令の定めるところにより必要な手続を行ってください。

- 10. お客様の転売等により、本ご注意書き記載の諸条件に抵触して当社製品が使用され、その使用から損害が生じた場合、当社は何らの責任も負わず、お客様にてご負担して頂きますのでご了承ください。

- 11. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを禁じます。

- 注 1. 本資料において使用されている「当社」とは、ルネサス エレクトロニクス株式会社およびルネ サス エレクトロニクス株式会社がその総株主の議決権の過半数を直接または間接に保有する 会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注1において定義された当社の開発、製造製品をいいます。

#### 製品ご使用上の注意事項

ここでは、マイコン製品全体に適用する「使用上の注意事項」について説明します。個別の使用上の注意事項については、本文を参照してください。なお、本マニュアルの本文と異なる記載がある場合は、本文の記載が優先するものとします。

#### 1. 未使用端子の処理

【注意】未使用端子は、本文の「未使用端子の処理」に従って処理してください。

CMOS製品の入力端子のインピーダンスは、一般に、ハイインピーダンスとなっています。未使用端子を開放状態で動作させると、誘導現象により、LSI周辺のノイズが印加され、LSI内部で貫通電流が流れたり、入力信号と認識されて誤動作を起こす恐れがあります。未使用端子は、本文「未使用端子の処理」で説明する指示に従い処理してください。

#### 2. 電源投入時の処置

【注意】電源投入時は,製品の状態は不定です。

電源投入時には、LSIの内部回路の状態は不確定であり、レジスタの設定や各端子の状態は不定です。 外部リセット端子でリセットする製品の場合、電源投入からリセットが有効になるまでの期間、端子の 状態は保証できません。

同様に、内蔵パワーオンリセット機能を使用してリセットする製品の場合、電源投入からリセットのかかる一定電圧に達するまでの期間、端子の状態は保証できません。

3. リザーブアドレスのアクセス禁止

【注意】リザーブアドレスのアクセスを禁止します。

アドレス領域には、将来の機能拡張用に割り付けられているリザーブアドレスがあります。これらのアドレスをアクセスしたときの動作については、保証できませんので、アクセスしないようにしてください。

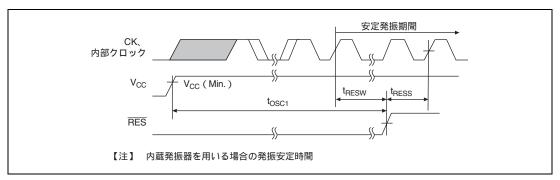

#### 4. クロックについて

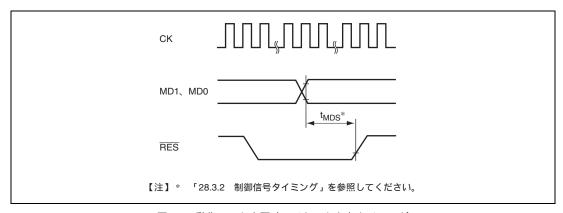

【注意】リセット時は、クロックが安定した後、リセットを解除してください。 プログラム実行中のクロック切り替え時は、切り替え先クロックが安定した後に切り替えてください。 リセット時、外部発振子(または外部発振回路)を用いたクロックで動作を開始するシステムでは、クロックが十分安定した後、リセットを解除してください。また、プログラムの途中で外部発振子(または外部発振回路)を用いたクロックに切り替える場合は、切り替え先のクロックが十分安定してから切り替えてください。

#### 5. 製品間の相違について

【注意】型名の異なる製品に変更する場合は、事前に問題ないことをご確認下さい。

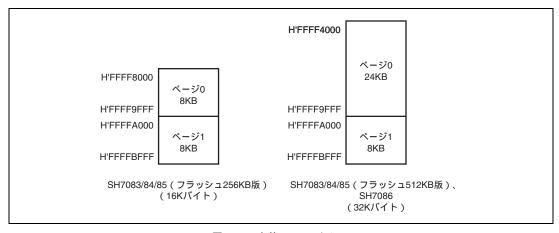

同じグループのマイコンでも型名が違うと、内部メモリ、レイアウトパターンの相違などにより、特性が異なる場合があります。型名の異なる製品に変更する場合は、製品型名ごとにシステム評価試験を実施してください。

# 本書の構成

本書は、以下の構成で制作しています。

- 1. 製品ご使用上の注意事項

- 2. 本書の構成

- 3. はじめに

- 4. 目次

- 5. 概要

- 6. 各機能モジュールの説明

- CPUおよびシステム制御系

- 内蔵周辺モジュール

各モジュールの機能説明の構成は、モジュールごとに異なりますが、一般的には、 特長、 入出力端子、 レジスタの説明、 動作説明、 使用上の注意事項、 等の節で構成されています。

本 LSI を用いた応用システムを設計する際、注意事項を十分確認のうえ設計してください。 各章の本文中には説明に対する注意事項と、各章の最後には使用上の注意事項があります。 必ずお読みください(使用上の注意事項は必要により記載されます)。

- 7. レジスター覧

- 8. 電気的特性

- 9. 付録

- 製品型名、外形寸法図など

- 10. 本版で改訂された箇所(改訂版のみ適用)

改訂来歴は、前版の記載内容について訂正・追加された主な箇所についてまとめたものです。 改訂内容のすべてについて記載したものではありませんので、詳細については、本書の本文上 でご確認ください。

11. 索引

# はじめに

SH7083/84/85/86 は、ルネサスオリジナルの RISC 方式の CPU をコアにして、システム構成に必要な周辺機能を 集積したシングルチップ RISC マイコンです。

対象者 このマニュアルは、SH7083/84/85/86 を用いた応用システムを設計するユーザを対象としています。このマニュアルを使用される読者には、電気回路、論理回路、およびマイクロコンピュータに関する基本的な知識を必要とします。

目的 このマニュアルは、SH7083/84/85/86 のハードウェア機能と電気的特性をユーザに理解していただくことを目的にしています。

なお、実行命令の詳細については、「SH-1/SH-2/SH-DSP ソフトウェアマニュアル」に記載しておりますので、あわせてご覧ください。

#### 読み方

• 機能全体を理解しようとするとき

目次に従って読んでください。

本書は、大きく分類すると、CPU、システム制御機能、周辺機能、電気的特性の順に構成されています。

• CPU機能の詳細を理解したいとき

別冊の「SH-1/SH-2/SH-DSP ソフトウェアマニュアル」を参照してください。

• レジスタ名がわかっていて、詳細機能を知りたいとき

本書の後ろに、「索引」があります。索引からページ番号を検索してください。

「第27章 レジスター覧」にアドレス、ビット内容、初期化についてまとめています。

凡例 レジスタ表記 : シリアルコミュニケーションなど、同一または類似した機能が複数チャネルに存在

する場合に、次の表記を使用します。

XXX N(XXX は基本レジスタ名称、N はチャネル番号)

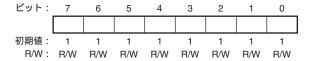

ビット表記 : 左側が上位ビット、右側が下位ビットの順に表記します。

数字の表記 : 2 進数は B'xxxx、16 進数は H'xxxx、10 進数は xxxx

信号の表記:ローアクティブの信号にはオーバーバーを付けます。xxxx

関連資料一覧 ウェブサイトに最新資料を掲載しています。ご入手の資料が最新版であるかを確認してください。 (http://japan.renesas.com/)

#### • SH7083/84/85/86に関するユーザーズマニュアル

| 資料名                          | 資料番号       |

|------------------------------|------------|

| SH7080 グループ ハードウェアマニュアル      | 本マニュアル     |

| SH-1/SH-2/SH-DSP ソフトウェアマニュアル | RJJ09B0228 |

#### • 開発ツール関連ユーザーズマニュアル

| 資料名                                                                   | 資料番号       |

|-----------------------------------------------------------------------|------------|

| SuperH RISC engine C/C++コンパイラ、アセンブラ、最適化リンケージエディタ V.9.04<br>ユーザーズマニュアル | RJJ10J2797 |

| High-performance Embedded Workshop ユーザーズマニュアル                         | RJJ10J2736 |

#### • アプリケーションノート

| 資料名                                           | 資料番号       |

|-----------------------------------------------|------------|

| SuperH RISC engine C/C++コンパイラパッケージアプリケーションノート | RJJ05B0557 |

# 目次

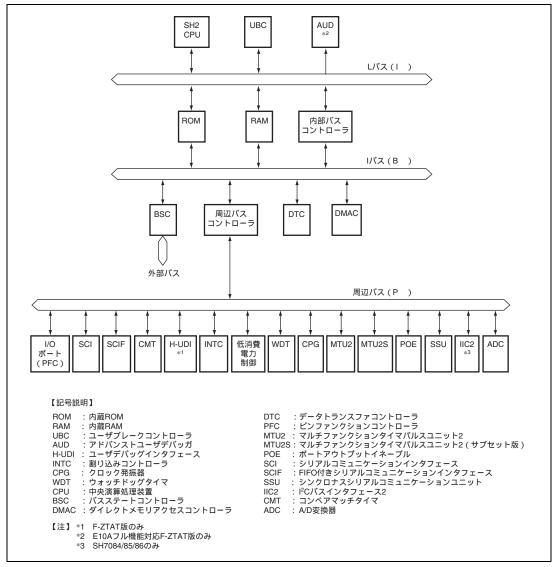

| 1.1 SH7083/84/85/86の特長 1-1 1.2 プロック図 1-6 1.3 ビン配置図 1-7 1.4 端子機能 1-12 2. CPU 2-1 2.1 特長 2-1 2.2 レジスタの構成 2-2 2.2.1 汎用レジスタ(Rn) 2-3 2.2.2 コントロールレジスタ 2-3 2.2.3 システムレジスタ 2-4 2.2.4 レジスタの初期値 2-5 2.3 データ形式 2-6 2.3.1 レジスタのデータ形式 2-6 2.3.2 メモリ上でのデータ形式 2-6 2.3.3 イミディエイトデータのデータ形式 2-6 2.3.3 イミディエイトデータのデータ形式 2-6 2.4.1 RISC 方式 2-7 2.4.1 RISC 方式 2-7 2.4.2 アドレッシングモード 2-9 2.4.3 命令形式 2-15 2.5.1 分類順命令セット 2-15 2.5.1 分類順命令 2-18 2.5.3 資イ演算命令 2-19 2.5.4 論理演算命令 2-19 2.5.5 グラト命令 2-21 2.5.6 分歧命令 2-22 2.5.7 システム制御命令 2-23 3.1 動作モードの選択 3-1 3.1 動作モードの選択 3-1 3.1 動作モードの選択 3-1 3.2 入出力端子 3-3                                                                                                                                                                                                                                                                                    | 1.  | 概要  |                    | 1-1  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|--------------------|------|

| 1.2 ブロック図 1-6 1.3 ピン配置図 1-7 1.4 端子機能 1-12 2. CPU 2-1 2.1 特長 2-1 2.2 レジスタの構成 2-2 2.2.1 汎用レジスタ (Rn) 2-3 2.2.2 コントロールレジスタ 2-3 2.2.3 システムレジスタ 2-4 2.2.4 レジスタの初期値 2-5 2.3 データ形式 2-6 2.3.1 レジスタのデータ形式 2-6 2.3.1 レジスタのデータ形式 2-6 2.3.2 メモリ上でのデータ形式 2-6 2.3.3 イミディエイトデータのデータ形式 2-6 2.3.3 イミディエイトデータのデータ形式 2-6 2.3.1 ならの特長 2-7 2.4.1 RISC方式 2-7 2.4.2 アドレッシングモード 2-9 2.4.3 命令形式 2-15 2.5.1 分類順命令セット 2-15 2.5.1 分類順命令セット 2-15 2.5.1 分類順命令セット 2-15 2.5.1 倫理演算命令 2-19 2.5.3 解析演算命令 2-19 2.5.4 論理演算命令 2-21 2.5.5 シフト命令 2-21 2.5.6 分岐命令 2-22 2.5.7 システム制御命令 2-23 3. MCU 動作モード 3-1 3.1 動作モードの選択 3-1 3.1 動作モードの選択 3-1 3.1 動作モードの選択 3-1                                                                                                                                                                                                                                                                                                                                                    | 1.1 |     | SH7083/84/85/86の特長 | 1-1  |

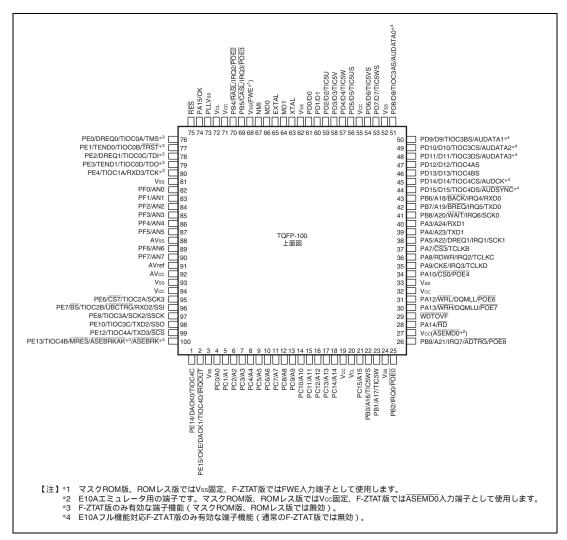

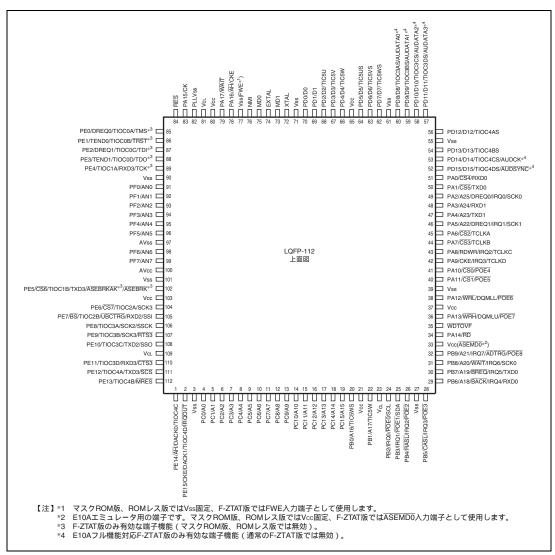

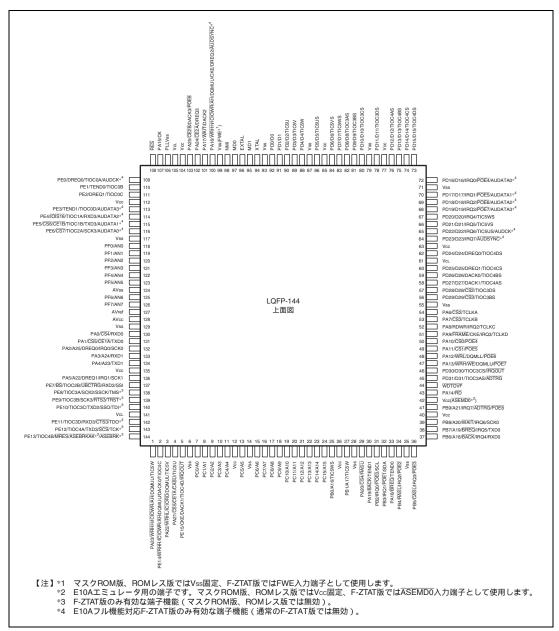

| 1.4 端子機能       1-12         2. CPU       2-1         2.1 特長       2-1         2.2 レジスタの構成       2-2         2.2.1 汎用レジスタ (Rn)       2-3         2.2.2 コントロールレジスタ       2-4         2.2.3 システムレジスタ       2-4         2.3 データ形式       2-6         2.3.1 レジスタのデータ形式       2-6         2.3.2 メモリ上でのデータ形式       2-6         2.3.3 イミディエイトデータのデータ形式       2-6         2.4 命令の特長       2-7         2.4.1 RISC 方式       2-7         2.4.2 アドレッシングモード       2-9         2.4.3 命令形式       2-12         2.5 命令セット       2-15         2.5.1 分類順命令セット       2-15         2.5.2 データ転送命令       2-18         2.5.3 算術演算命令       2-21         2.5.4 論理演算命令       2-21         2.5.5 シフト命令       2-21         2.5.6 分岐命令       2-22         2.5.7 システム制御命令       2-21         2.5. グレ戦が懸       2-23         3. MCU動作モード       3-1         3.1 動作モードの選択       3-1         3.2 入出力端子       3-2                                                                                               | 1.2 |     |                    |      |

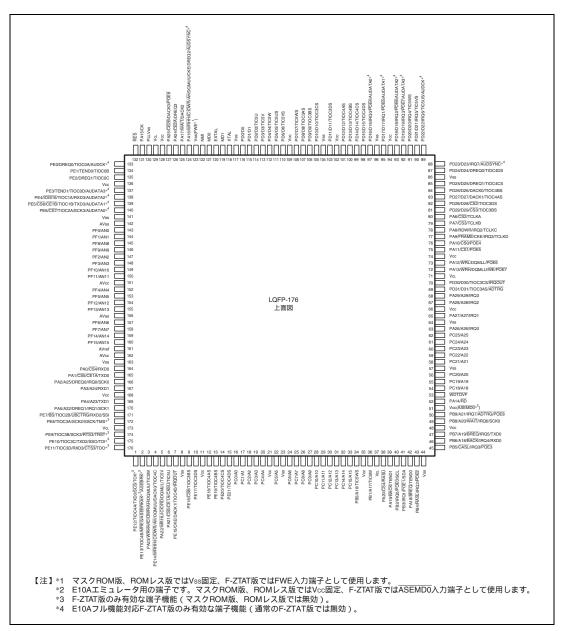

| 1.4 端子機能       1-12         2. CPU       2-1         2.1 特長       2-1         2.2 レジスタの構成       2-2         2.2.1 汎用レジスタ (Rn)       2-3         2.2.2 コントロールレジスタ       2-4         2.2.3 システムレジスタ       2-4         2.3 データ形式       2-6         2.3.1 レジスタのデータ形式       2-6         2.3.2 メモリ上でのデータ形式       2-6         2.3.3 イミディエイトデータのデータ形式       2-6         2.4 命令の特長       2-7         2.4.1 RISC 方式       2-7         2.4.2 アドレッシングモード       2-9         2.4.3 命令形式       2-12         2.5 命令セット       2-15         2.5.1 分類順命令セット       2-15         2.5.2 データ転送命令       2-18         2.5.3 算術演算命令       2-21         2.5.4 論理演算命令       2-21         2.5.5 シフト命令       2-21         2.5.6 分岐命令       2-22         2.5.7 システム制御命令       2-21         2.5. グレ戦が懸       2-23         3. MCU動作モード       3-1         3.1 動作モードの選択       3-1         3.2 入出力端子       3-2                                                                                               | 1.3 |     | ピン配置図              | 1-7  |

| 2.1       特長       2-1         2.2       レジスタの構成       2-2         2.2.1       汎用レジスタ (Rn)       2-3         2.2.2       コントロールレジスタ       2-4         2.2.3       システムレジスタ       2-4         2.2.4       レジスタの可力射値       2-5         2.3.1       レジスタのデータ形式       2-6         2.3.2       メモリ上でのデータ形式       2-6         2.3.3       イミディエイトデータのデータ形式       2-6         2.4       命令の特長       2-7         2.4.1       RISC 方式       2-7         2.4.2       アドレッシングモード       2-9         2.4.3       命令形式       2-12         2.5.1       分類順命令セット       2-15         2.5.2       データ転送命令       2-18         2.5.3       算術演算命令       2-21         2.5.4       論理演算命令       2-21         2.5.5       シフト命令       2-21         2.5.5       シフト命令       2-21         2.5.6       分岐命令       2-22         2.5.7       システム制御命令       2-22         2.5.7       システム制御命令       2-23         2.6       処理状態       2-25         3.       MCU動作モード       3-1         3.       加速の令 | 1.4 |     | 端子機能               | 1-12 |

| 2.1       特長       2-1         2.2       レジスタの構成       2-2         2.2.1       汎用レジスタ (Rn)       2-3         2.2.2       コントロールレジスタ       2-4         2.2.3       システムレジスタ       2-4         2.2.4       レジスタの可力射値       2-5         2.3.1       レジスタのデータ形式       2-6         2.3.2       メモリ上でのデータ形式       2-6         2.3.3       イミディエイトデータのデータ形式       2-6         2.4       命令の特長       2-7         2.4.1       RISC 方式       2-7         2.4.2       アドレッシングモード       2-9         2.4.3       命令形式       2-12         2.5.1       分類順命令セット       2-15         2.5.2       データ転送命令       2-18         2.5.3       算術演算命令       2-21         2.5.4       論理演算命令       2-21         2.5.5       シフト命令       2-21         2.5.5       シフト命令       2-21         2.5.6       分岐命令       2-22         2.5.7       システム制御命令       2-22         2.5.7       システム制御命令       2-23         2.6       処理状態       2-25         3.       MCU動作モード       3-1         3.       加速の令 |     |     |                    |      |

| 2.2 レジスタの構成 2.2.2 に                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2.  | CPU |                    | 2-1  |

| 2.2.1       汎用レジスタ (Rn)       2.3         2.2.2       コントロールレジスタ       2.4         2.2.3       システムレジスタ       2.4         2.2.4       レジスタの初期値       2.5         2.3       データ形式       2.6         2.3.1       レジスタのデータ形式       2.6         2.3.2       メモリ上でのデータ形式       2.6         2.3.3       イミディエイトデータのデータ形式       2.6         2.4       命令の特長       2.7         2.4.1       RISC 方式       2.7         2.4.2       アドレッシングモード       2.9         2.4.3       命令形式       2.12         2.5.1       分類順命令セット       2.15         2.5.2       データ転送命令       2.18         2.5.3       算術演算命令       2.19         2.5.4       論理演算命令       2.21         2.5.5       シフト命令       2.21         2.5.6       分岐命令       2.22         2.5.7       システム制御命令       2.22         2.5.7       システム制御命令       2.23         2.6       処理状態       2.25         3.       MCU 動作モード       3.1         3.1       動作モードの選択       3.1         3.2       入出力端子       3.2                      | 2.1 |     | 特長                 | 2-1  |

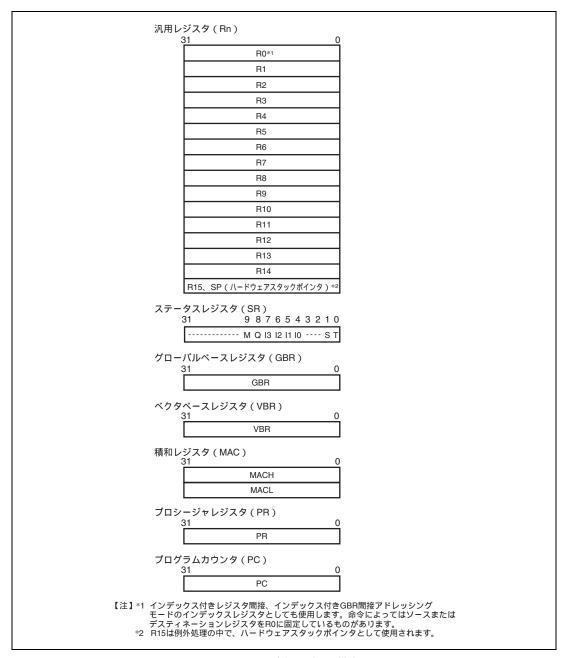

| 2.2.2       コントロールレジスタ       2.4         2.2.3       システムレジスタ       2.4         2.2.4       レジスタの初期値       2.5         2.3       データ形式       2.6         2.3.1       レジスタのデータ形式       2.6         2.3.2       メモリ上でのデータ形式       2.6         2.3.3       イミディエイトデータのデータ形式       2.6         2.4       命令の特長       2.7         2.4.1       RISC 方式       2.7         2.4.2       アドレッシングモード       2.9         2.4.3       命令形式       2.12         2.5.1       分類順命令形式       2.12         2.5.2       データ転送命令       2.18         2.5.3       算術演算命令       2.19         2.5.4       論理演算命令       2.21         2.5.5       シフト命令       2.21         2.5.6       分岐命令       2.22         2.5.7       システム制御命令       2.23         2.6       処理状態       2.23         3.1       動作モード       3-1         3.2       入出力端子       3-2                                                                                                                                                 | 2.2 |     | レジスタの構成            | 2-2  |

| 2.2.3       システムレジスタの初期値       2-4         2.2.4       レジスタの初期値       2-5         2.3       データ形式       2-6         2.3.1       レジスタのデータ形式       2-6         2.3.2       メモリ上でのデータ形式       2-6         2.3.3       イミディエイトデータのデータ形式       2-6         2.4       市令の特長       2-7         2.4.1       RISC 方式       2-7         2.4.2       アドレッシングモード       2-9         2.4.3       命令形式       2-12         2.5       命令をカット       2-15         2.5.1       分類順命令セット       2-15         2.5.2       データ転送命令       2-18         2.5.3       算術演算命令       2-19         2.5.4       論理演算命令       2-21         2.5.5       シフト命令       2-21         2.5.6       分岐命令       2-22         2.5.7       システム制御命令       2-23         2.6       処理状態       2-25         3.       MCU 動作モード       3-1         3.1       動作モードの選択       3-1         3.2       入出力端子       3-2                                                                                                         | 2.  | 2.1 | 汎用レジスタ(Rn)         | 2-3  |

| 2.2.4       レジスタの初期値       2.5         2.3       データ形式       2.6         2.3.1       レジスタのデータ形式       2.6         2.3.2       メモリ上でのデータ形式       2.6         2.3.3       イミディエイトデータのデータ形式       2.6         2.4       命令の特長       2.7         2.4.1       RISC 方式       2.7         2.4.2       アドレッシングモード       2.9         2.4.3       命令形式       2.12         2.5       命令をセット       2.15         2.5.1       分類順命令セット       2.15         2.5.2       データ転送命令       2.18         2.5.3       算術演算命令       2.19         2.5.4       論理演算命令       2.21         2.5.5       シフト命令       2.21         2.5.6       分岐命令       2.22         2.5.7       システム制御命令       2.23         2.6       処理状態       2.25         3.       MCU 動作モード       3-1         3.1       動作モードの選択       3-1         3.2       入出力端子       3-2                                                                                                                                                    | 2.  | 2.2 | コントロールレジスタ         | 2-3  |

| 2.3       データ形式       2-6         2.3.1       レジスタのデータ形式       2-6         2.3.2       メモリ上でのデータ形式       2-6         2.3.3       イミディエイトデータのデータ形式       2-6         2.4       命令の特長       2-7         2.4.1       RISC 方式       2-7         2.4.2       アドレッシングモード       2-9         2.4.3       命令形式       2-12         2.5       命令セット       2-15         2.5.1       分類順命令セット       2-15         2.5.2       データ転送命令       2-18         2.5.3       算術演算命令       2-21         2.5.4       論理演算命令       2-21         2.5.5       シフト命令       2-21         2.5.6       分岐命令       2-21         2.5.7       システム制御命令       2-22         2.6       処理状態       2-25         3.       MCU動作モード       3-1         3.1       動作モードの選択       3-1         3.2       入出力端子       3-2                                                                                                                                                                                             | 2.  | 2.3 | システムレジスタ           | 2-4  |

| 2.3.1       レジスタのデータ形式       2-6         2.3.2       メモリ上でのデータ形式       2-6         2.3.3       イミディエイトデータのデータ形式       2-6         2.4       命令の特長       2-7         2.4.1       RISC 方式       2-7         2.4.2       アドレッシングモード       2-9         2.4.3       命令形式       2-12         2.5       命令セット       2-15         2.5.1       分類順命令セット       2-15         2.5.2       データ転送命令       2-18         2.5.3       算術演算命令       2-19         2.5.4       論理演算命令       2-21         2.5.5       シフト命令       2-21         2.5.6       分岐命令       2-22         2.5.7       システム制御命令       2-23         2.6       処理状態       2-25         3.       MCU 動作モードの選択       3-1         3.1       動作モードの選択       3-1         3.2       入出力端子       3-2                                                                                                                                                                                                                           | 2.  | 2.4 | レジスタの初期値           | 2-5  |

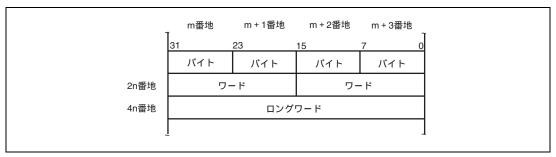

| 2.3.2       メモリ上でのデータ形式       2-6         2.3.3       イミディエイトデータのデータ形式       2-6         2.4       命令の特長       2-7         2.4.1       RISC 方式       2-7         2.4.2       アドレッシングモード       2-9         2.4.3       命令形式       2-12         2.5       命令セット       2-15         2.5.1       分類順命令セット       2-15         2.5.2       データ転送命令       2-18         2.5.3       算術演算命令       2-19         2.5.4       論理演算命令       2-21         2.5.5       シフト命令       2-21         2.5.6       分岐命令       2-22         2.5.7       システム制御命令       2-23         2.6       処理状態       2-25         3.       MCU動作モード       3-1         3.1       動作モードの選択       3-1         3.2       入出力端子       3-2                                                                                                                                                                                                                                                                        | 2.3 |     | データ形式              | 2-6  |

| 2.3.3       イミディエイトデータのデータ形式       2-6         2.4       命令の特長       2-7         2.4.1       RISC 方式       2-7         2.4.2       アドレッシングモード       2-9         2.4.3       命令形式       2-12         2.5       命令セット       2-15         2.5.1       分類順命令セット       2-15         2.5.2       データ転送命令       2-18         2.5.3       算術演算命令       2-19         2.5.4       論理演算命令       2-21         2.5.5       シフト命令       2-21         2.5.6       分岐命令       2-22         2.5.7       システム制御命令       2-23         2.6       処理状態       2-25         3.       MCU 動作モードの選択       3-1         3.1       動作モードの選択       3-1         3.2       入出力端子       3-2                                                                                                                                                                                                                                                                                                              | 2.  | 3.1 | レジスタのデータ形式         | 2-6  |

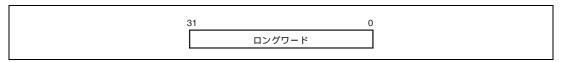

| 2.4命令の特長2-72.4.1RISC 方式2-72.4.2アドレッシングモード2-92.4.3命令形式2-122.5命令セット2-152.5.1分類順命令セット2-152.5.2データ転送命令2-182.5.3算術演算命令2-192.5.4論理演算命令2-212.5.5シフト命令2-212.5.6分岐命令2-222.5.7システム制御命令2-232.6処理状態2-253.MCU 動作モード3-13.1動作モードの選択3-13.2入出力端子3-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2.  | 3.2 | メモリ上でのデータ形式        | 2-6  |

| 2.4.1RISC 方式2-72.4.2アドレッシングモード2-92.4.3命令形式2-122.5命令セット2-152.5.1分類順命令セット2-152.5.2データ転送命令2-182.5.3算術演算命令2-192.5.4論理演算命令2-212.5.5シフト命令2-212.5.6分岐命令2-222.5.7システム制御命令2-232.6処理状態2-253.MCU動作モード3-13.1動作モードの選択3-13.2入出力端子3-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2.  | 3.3 | イミディエイトデータのデータ形式   | 2-6  |

| 2.4.2アドレッシングモード2-92.4.3命令形式2-122.5命令セット2-152.5.1分類順命令セット2-152.5.2データ転送命令2-182.5.3算術演算命令2-192.5.4論理演算命令2-212.5.5シフト命令2-212.5.6分岐命令2-222.5.7システム制御命令2-232.6処理状態2-253.MCU動作モード3-13.1動作モードの選択3-13.2入出力端子3-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2.4 |     | 命令の特長              | 2-7  |

| 2.4.3命令形式2-122.5命令セット2-152.5.1分類順命令セット2-152.5.2データ転送命令2-182.5.3算術演算命令2-192.5.4論理演算命令2-212.5.5シフト命令2-212.5.6分岐命令2-222.5.7システム制御命令2-232.6処理状態2-253.MCU 動作モード3-13.1動作モードの選択3-13.2入出力端子3-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2.  | 4.1 | RISC 方式            | 2-7  |

| 2.5命令セット2-152.5.1分類順命令セット2-152.5.2データ転送命令2-182.5.3算術演算命令2-192.5.4論理演算命令2-212.5.5シフト命令2-212.5.6分岐命令2-222.5.7システム制御命令2-232.6処理状態2-253.MCU 動作モード3-13.1動作モードの選択3-13.2入出力端子3-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.  | 4.2 | アドレッシングモード         | 2-9  |

| 2.5.1       分類順命令セット       2-15         2.5.2       データ転送命令       2-18         2.5.3       算術演算命令       2-19         2.5.4       論理演算命令       2-21         2.5.5       シフト命令       2-21         2.5.6       分岐命令       2-22         2.5.7       システム制御命令       2-23         2.6       処理状態       2-25         3.       MCU 動作モード       3-1         3.1       動作モードの選択       3-1         3.2       入出力端子       3-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.  | 4.3 | 命令形式               | 2-12 |

| 2.5.2       データ転送命令       2-18         2.5.3       算術演算命令       2-19         2.5.4       論理演算命令       2-21         2.5.5       シフト命令       2-21         2.5.6       分岐命令       2-22         2.5.7       システム制御命令       2-23         2.6       処理状態       2-25         3.       MCU 動作モード       3-1         3.1       動作モードの選択       3-1         3.2       入出力端子       3-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.5 |     | 命令セット              | 2-15 |

| 2.5.3       算術演算命令       2-19         2.5.4       論理演算命令       2-21         2.5.5       シフト命令       2-21         2.5.6       分岐命令       2-22         2.5.7       システム制御命令       2-23         2.6       処理状態       2-25         3.       MCU 動作モード       3-1         3.1       動作モードの選択       3-1         3.2       入出力端子       3-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2.: | 5.1 | 分類順命令セット           | 2-15 |

| 2.5.4       論理演算命令       2-21         2.5.5       シフト命令       2-21         2.5.6       分岐命令       2-22         2.5.7       システム制御命令       2-23         2.6       処理状態       2-25         3.       MCU 動作モード       3-1         3.1       動作モードの選択       3-1         3.2       入出力端子       3-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2.: | 5.2 | データ転送命令            | 2-18 |

| 2.5.5       シフト命令       2-21         2.5.6       分岐命令       2-22         2.5.7       システム制御命令       2-23         2.6       処理状態       2-25         3.       MCU 動作モード       3-1         3.1       動作モードの選択       3-1         3.2       入出力端子       3-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2   | 5.3 | 算術演算命令             | 2-19 |

| 2.5.6       分岐命令       2-22         2.5.7       システム制御命令       2-23         2.6       処理状態       2-25         3. MCU 動作モード       3-1         3.1       動作モードの選択       3-1         3.2       入出力端子       3-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2.: | 5.4 | 論理演算命令             | 2-21 |

| 2.5.7       システム制御命令       2-23         2.6       処理状態       2-25         3.       MCU 動作モード       3-1         3.1       動作モードの選択       3-1         3.2       入出力端子       3-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2.: | 5.5 | シフト命令              | 2-21 |

| 2.6       処理状態       2-25         3. MCU 動作モード       3-1         3.1 動作モードの選択       3-1         3.2 入出力端子       3-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2.: | 5.6 | 分岐命令               | 2-22 |

| 3. MCU 動作モード       3-1         3.1 動作モードの選択       3-1         3.2 入出力端子       3-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.: | 5.7 | システム制御命令           | 2-23 |

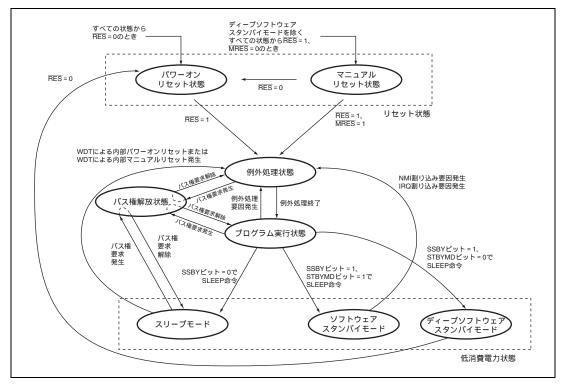

| 3.1       動作モードの選択                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2.6 |     | 処理状態               | 2-25 |

| 3.2 入出力端子                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.  | MCU | 動作モード              | 3-1  |

| 3.2 入出力端子                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.1 |     | 動作モードの選択           | 3-1  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |     |                    |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3.3 |     |                    |      |

| 3.3.1 | モード 0 ( MCU 拡張モード 0 ) | 3-3  |

|-------|-----------------------|------|

| 3.3.2 | モード 1 ( MCU 拡張モード 1 ) | 3-3  |

| 3.3.3 | モード 2 ( MCU 拡張モード 2 ) | 3-3  |

| 3.3.4 | モード3(シングルチップモード)      | 3-3  |

| 3.4   | アドレスマップ               | 3-4  |

| 3.5   | 本LSIの初期状態             | 3-11 |

| 3.6   | 動作モード変更時の注意事項         | 3-11 |

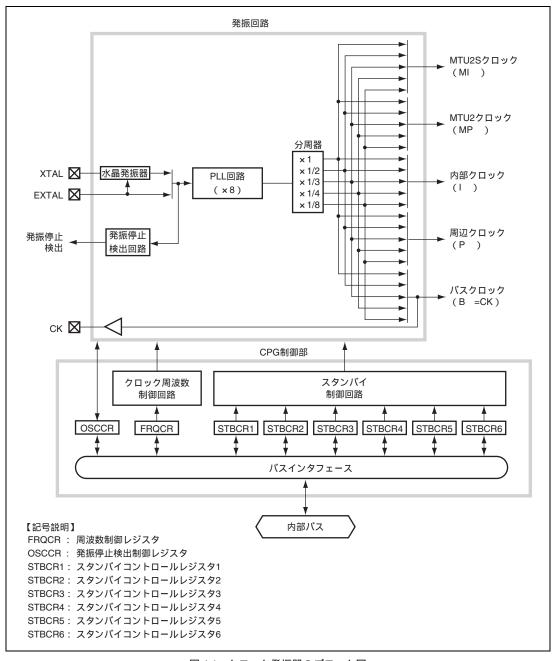

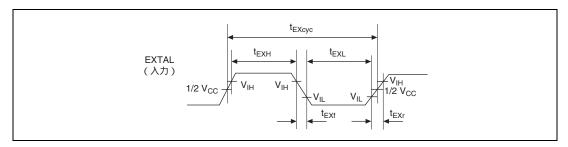

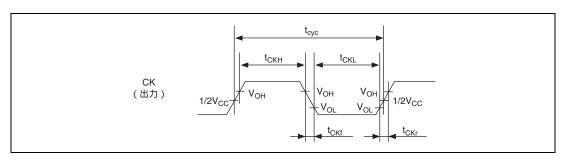

| 4. クロ | コック発振器(CPG)           | 4-1  |

| 4.1   | 特長                    | 4-1  |

| 4.2   | 入出力端子                 | 4-5  |

| 4.3   | クロック動作モード             | 4-6  |

| 4.4   | レジスタの説明               | 4-10 |

| 4.4.1 | 周波数制御レジスタ(FRQCR)      | 4-10 |

| 4.4.2 | 発振停止検出制御レジスタ(OSCCR)   | 4-12 |

| 4.5   | 周波数变更方法               | 4-13 |

| 4.6   | 発振器                   | 4-14 |

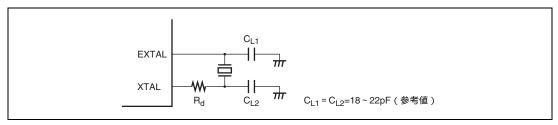

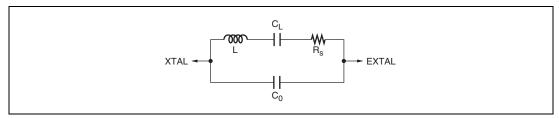

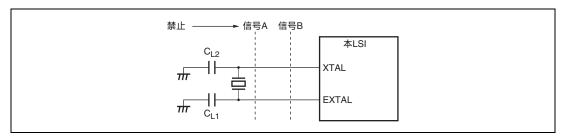

| 4.6.1 | 水晶発振子を接続する方法          | 4-14 |

| 4.6.2 | 外部クロックを入力する方法         | 4-15 |

| 4.7   | 発振停止検出機能              | 4-16 |

| 4.8   | 使用上の注意事項              | 4-17 |

| 4.8.1 | 発振子に関する注意事項           | 4-17 |

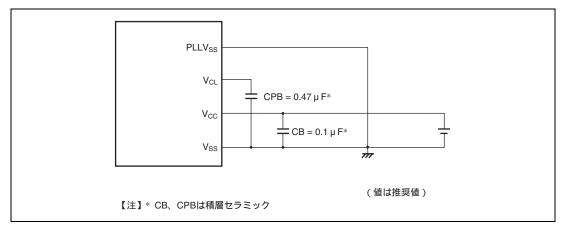

| 4.8.2 | ボード設計上の注意事項           | 4-17 |

| 5. 例夕 | 外処理                   | 5-1  |

| 5.1   | 概要                    | 5-1  |

| 5.1.1 | 例外処理の種類と優先順位          | 5-1  |

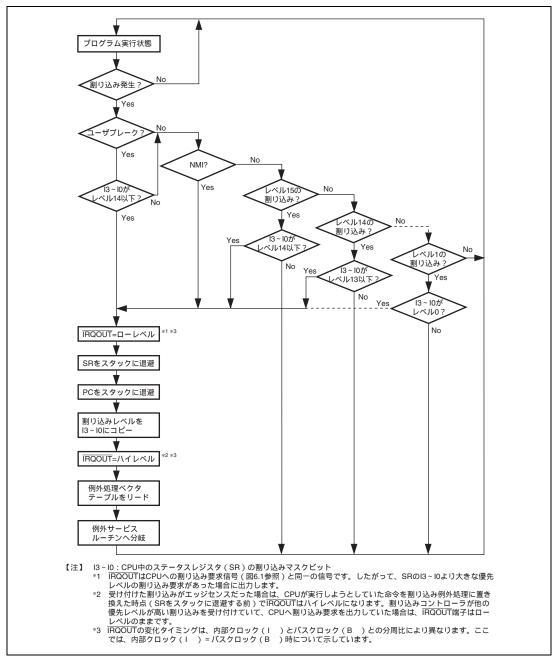

| 5.1.2 | 例外処理の動作               | 5-2  |

| 5.1.3 | 例外処理ベクタテーブル           | 5-3  |

| 5.2   | リセット                  | 5-5  |

| 5.2.1 | リセットの種類               | 5-5  |

| 5.2.2 | パワーオンリセット             | 5-5  |

| 5.2.3 | マニュアルリセット             | 5-6  |

| 5.3   | アドレスエラー               | 5-7  |

| 5.3.1 | アドレスエラー発生要因           | 5-7  |

| 5.3.2 | アドレスエラー例外処理           | 5-7  |

| 5.4   | 割り込み                  | 5-8  |

| 5.4.1 | 割り込み要因                | 5-8  |

| 5.4.2 | 割り込み優先順位              | 5-9  |

| 5.4.3 | 割り込み例外処理              | 5-9  |

| 5.5   | 命令による例外               | 5-10 |

| 5.5.1 | 命令による例外の種類                                             | 5-10 |

|-------|--------------------------------------------------------|------|

| 5.5.2 | トラップ命令                                                 | 5-10 |

| 5.5.3 | スロット不当命令                                               | 5-11 |

| 5.5.4 | 一般不当命令                                                 | 5-11 |

| 5.6   | 例外処理の受け付け                                              | 5-12 |

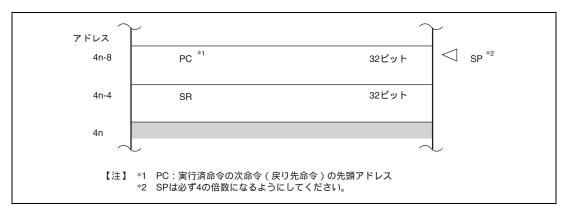

| 5.7   | 例外処理後のスタックの状態                                          | 5-13 |

| 5.8   | 使用上の注意事項                                               | 5-14 |

| 5.8.1 | スタックポインタ(SP ) の値                                       | 5-14 |

| 5.8.2 | ベクタベースレジスタ(VBR)の値                                      | 5-14 |

| 5.8.3 | アドレスエラー例外処理のスタッキングで発生するアドレスエラー                         | 5-14 |

| 5.8.4 | スロット不当命令例外処理に関する注意事項                                   | 5-15 |

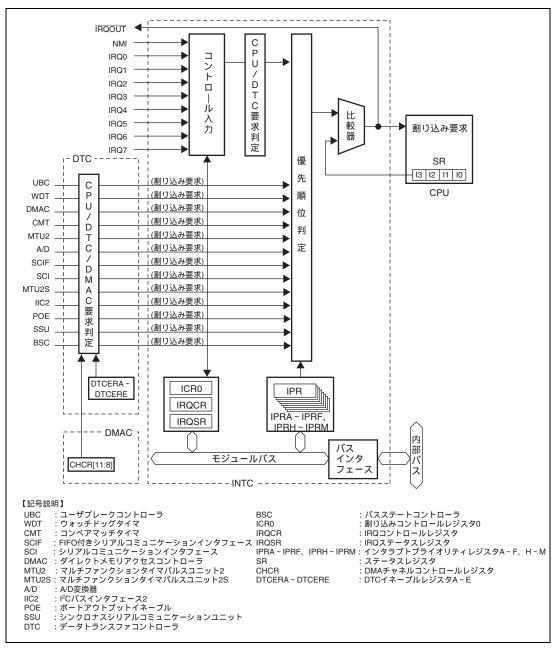

| 6. 割  | り込みコントローラ(INTC)                                        | 6-1  |

| 6.1   | 特長                                                     | 6-1  |

| 6.2   | 入出力端子                                                  | 6-3  |

| 6.3   | レジスタの説明                                                | 6-4  |

| 6.3.1 | 割り込みコントロールレジスタ 0 ( ICR0 )                              | 6-5  |

| 6.3.2 | IRQ コントロールレジスタ(IRQCR)                                  | 6-5  |

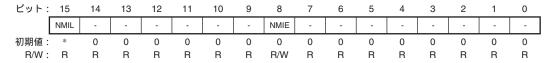

| 6.3.3 | IRQ ステータスレジスタ(IRQSR)                                   | 6-7  |

| 6.3.4 | インタラプトプライオリティレジスタ A~F、H~M(IPRA~IPRF、IPRH~IPRM)         | 6-13 |

| 6.4   | 割り込み要因                                                 | 6-15 |

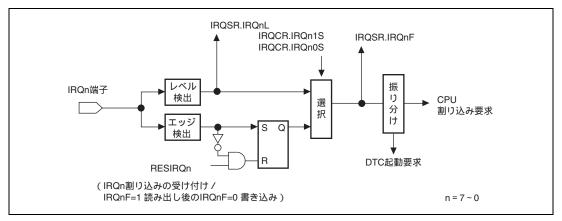

| 6.4.1 | 外部割り込み要因                                               | 6-15 |

| 6.4.2 | 内蔵周辺モジュール割り込み                                          | 6-16 |

| 6.4.3 | ユーザブレーク割り込み                                            | 6-16 |

| 6.5   | 割り込み例外処理ベクタテーブル                                        | 6-17 |

| 6.6   | 動作説明                                                   | 6-21 |

| 6.6.1 | 割り込み動作の流れ                                              | 6-21 |

| 6.6.2 | 割り込み例外処理終了後のスタックの状態                                    | 6-23 |

| 6.7   | 割り込み応答時間                                               | 6-24 |

| 6.8   | 割り込み要求信号によるデータ転送                                       | 6-25 |

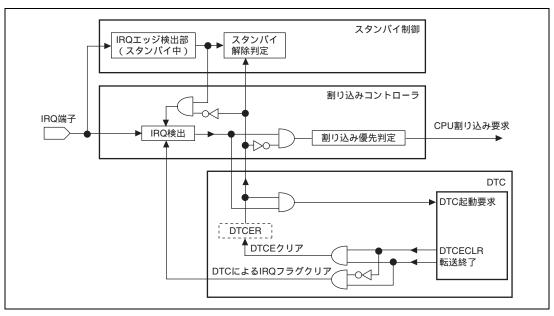

| 6.8.1 | 割り込み要求信号を DTC の起動要因、CPU の割り込み要因とし、<br>DMAC の起動要因としない場合 | 6-26 |

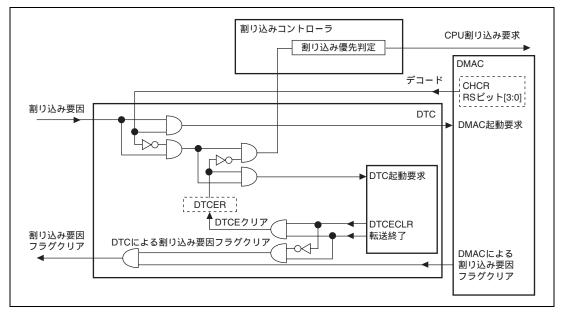

| 6.8.2 | 割り込み要求信号を DMAC の起動要因とし、CPU の割り込み要因、<br>DTC の起動要因としない場合 |      |

| 6.8.3 | 割り込み要求信号を DTC の起動要因とし、CPU の割り込み要因、<br>DMAC の起動要因としない場合 |      |

| 6.8.4 | 割り込み要求信号を CPU の割り込み要因とし、DTC の起動要因、                     |      |

|       | DMAC の起動要因としない場合                                       |      |

| 6.9   | 使用上の注意事項                                               | 6-28 |

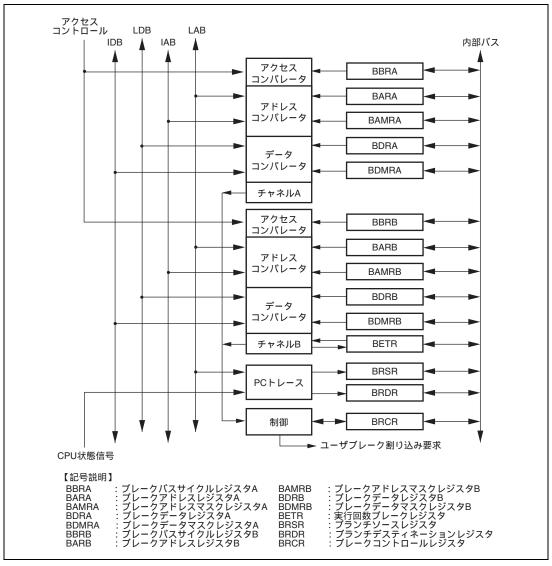

| 7. ユー  | -ザブレークコントローラ(UBC)                   | 7-1  |

|--------|-------------------------------------|------|

| 7.1    | 特長                                  | 7-1  |

| 7.2    | 入出力端子                               | 7-3  |

| 7.3    | レジスタの説明                             | 7-4  |

| 7.3.1  | プレークアドレスレジスタ A(BARA)                | 7-4  |

| 7.3.2  | プレークアドレスマスクレジスタ A(BAMRA)            | 7-5  |

| 7.3.3  | ブレークバスサイクルレジスタ A ( BBRA )           | 7-5  |

| 7.3.4  | ブレークデータレジスタ A(BDRA)(F-ZTAT 版のみ)     | 7-7  |

| 7.3.5  | ブレークデータマスクレジスタ A(BDMRA)(F-ZTAT 版のみ) | 7-8  |

| 7.3.6  | ブレークアドレスレジスタ B ( BARB )             | 7-9  |

| 7.3.7  | ブレークアドレスマスクレジスタ B(BAMRB)            | 7-9  |

| 7.3.8  | ブレークデータレジスタ B(BDRB)(F-ZTAT 版のみ)     | 7-10 |

| 7.3.9  | ブレークデータマスクレジスタ B(BDMRB)(F-ZTAT 版のみ) | 7-11 |

| 7.3.10 | ブレークバスサイクルレジスタ B ( BBRB )           | 7-12 |

| 7.3.11 | ブレークコントロールレジスタ ( BRCR )             | 7-13 |

| 7.3.12 | 実行回数プレークレジスタ(BETR)(F-ZTAT 版のみ)      | 7-17 |

| 7.3.13 | ブランチソースレジスタ(BRSR)(F-ZTAT 版のみ)       | 7-17 |

| 7.3.14 | ブランチデスティネーションレジスタ(BRDR)(F-ZTAT 版のみ) | 7-18 |

| 7.4    | 動作説明                                | 7-19 |

| 7.4.1  | ユーザプレーク動作の流れ                        | 7-19 |

| 7.4.2  | 命令フェッチサイクルでのユーザブレーク                 | 7-20 |

| 7.4.3  | データアクセスサイクルでのユーザブレーク                | 7-20 |

| 7.4.4  | シーケンシャルプレーク                         | 7-21 |

| 7.4.5  | 退避されるプログラムカウンタの値                    | 7-22 |

| 7.4.6  | PC トレース                             | 7-23 |

| 7.4.7  | 使用例                                 | 7-23 |

| 7.5    | 使用上の注意事項                            | 7-28 |

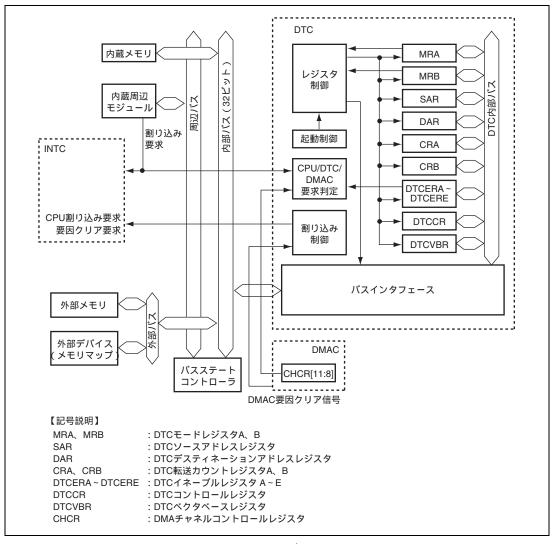

| 8. デー  | -タトランスファコントローラ(DTC)                 | 8-1  |

| 8.1    | 特長                                  | 8-1  |

| 8.2    | レジスタの説明                             | 8-3  |

| 8.2.1  | DTC モードレジスタ A(MRA)                  | 8-4  |

| 8.2.2  | DTC モードレジスタ B ( MRB )               | 8-5  |

| 8.2.3  | DTC ソースアドレスレジスタ(SAR)                | 8-6  |

| 8.2.4  | DTC デスティネーションアドレスレジスタ(DAR)          | 8-6  |

| 8.2.5  | DTC 転送カウントレジスタ A(CRA)               | 8-7  |

| 8.2.6  | DTC 転送カウントレジスタ B(CRB)               | 8-7  |

| 8.2.7  | DTC イネーブルレジスタ A~E(DTCERA~DTCERE)    | 8-8  |

| 8.2.8  | DTC コントロールレジスタ ( DTCCR )            | 8-9  |

| 8.2.9  | DTC ベクタベースレジスタ(DTCVBR)              | 8-10 |

| 8.2.10 | バス機能拡張レジスタ ( BSCEHR )                       | 8-10 |

|--------|---------------------------------------------|------|

| 8.3    | 起動要因                                        | 8-11 |

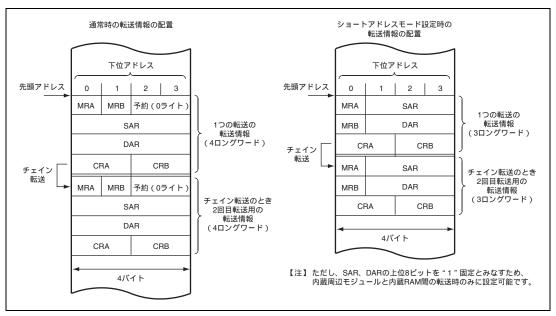

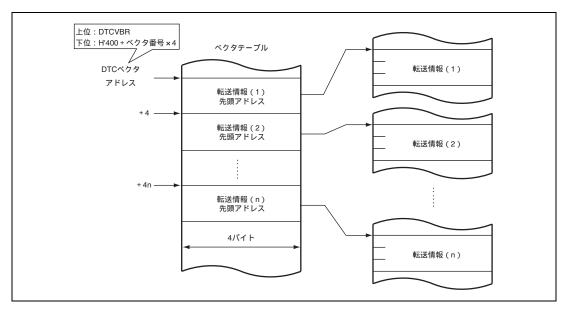

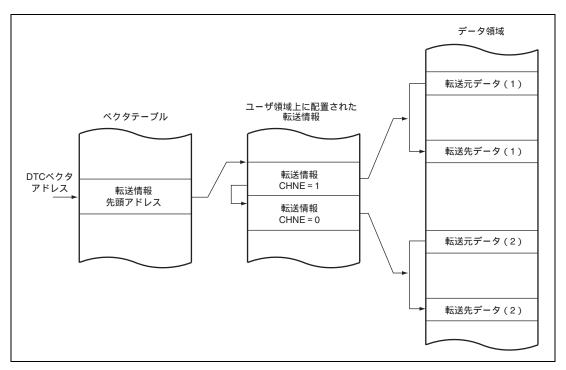

| 8.4    | 転送情報の配置とDTCベクタテーブル                          | 8-12 |

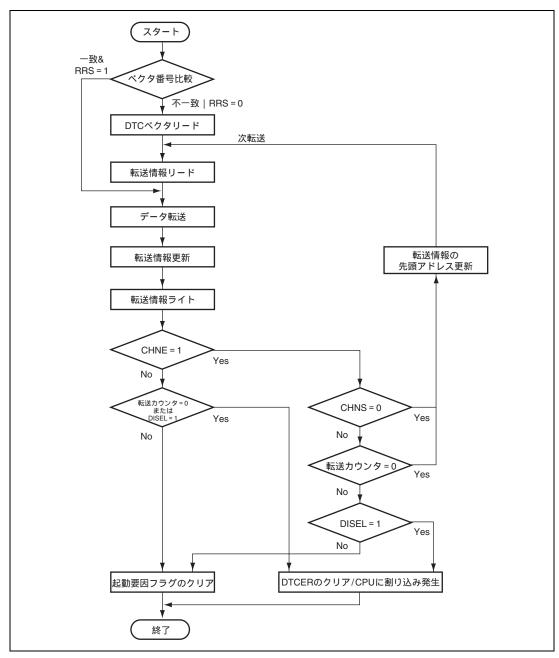

| 8.5    | 動作説明                                        | 8-16 |

| 8.5.1  | 転送情報リードスキップ機能                               | 8-20 |

| 8.5.2  | 転送情報ライトバックスキップ機能                            | 8-20 |

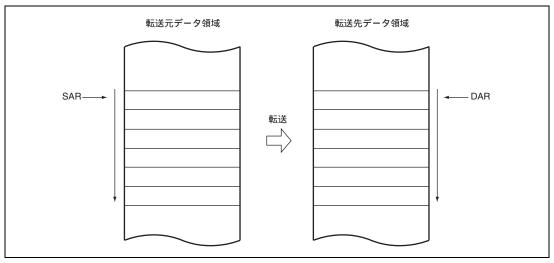

| 8.5.3  | ノーマル転送モード                                   | 8-21 |

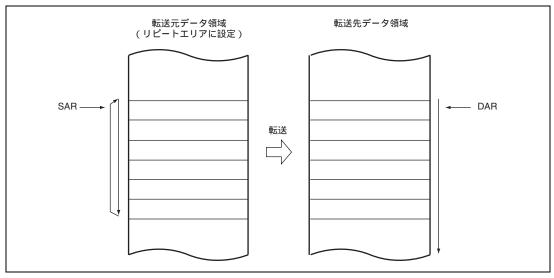

| 8.5.4  | リピート転送モード                                   | 8-22 |

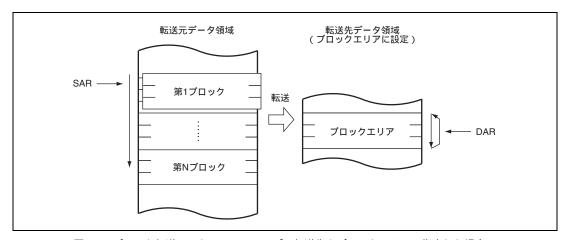

| 8.5.5  | ブロック転送モード                                   | 8-23 |

| 8.5.6  | チェイン転送                                      | 8-24 |

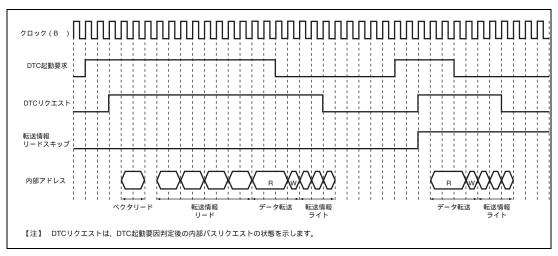

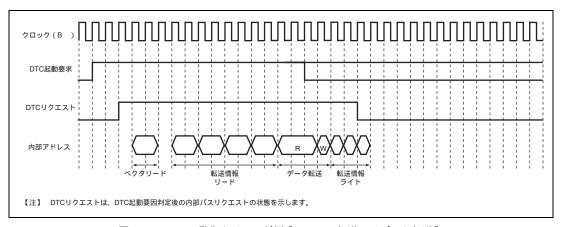

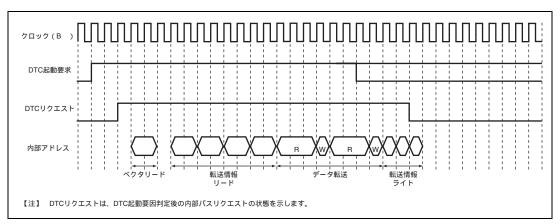

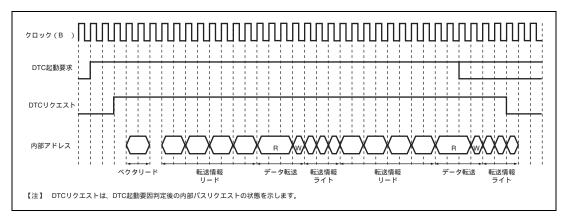

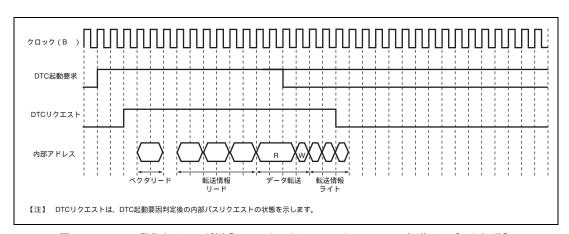

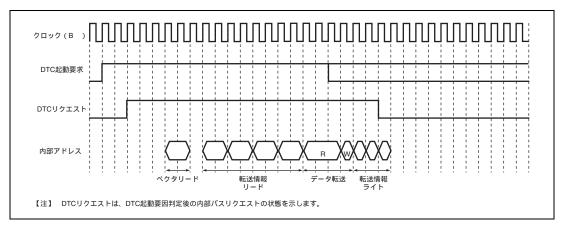

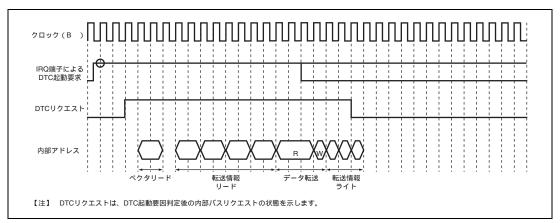

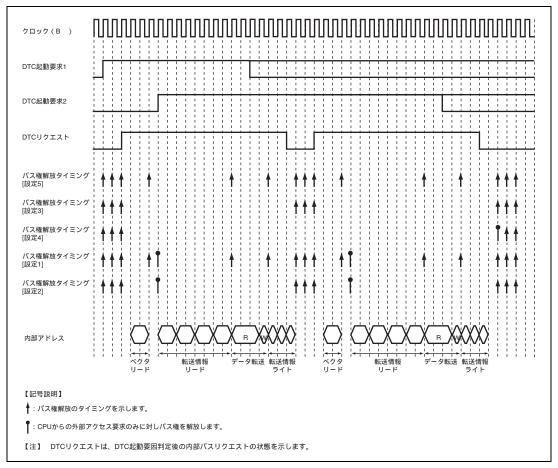

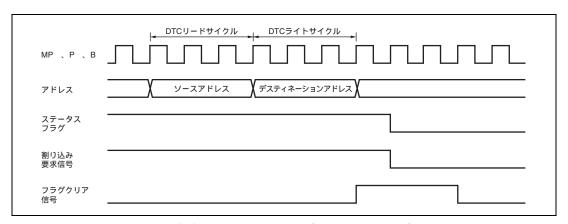

| 8.5.7  | 動作タイミング                                     | 8-25 |

| 8.5.8  | DTC の実行ステート                                 | 8-28 |

| 8.5.9  | DTC のバス権解放タイミング                             | 8-30 |

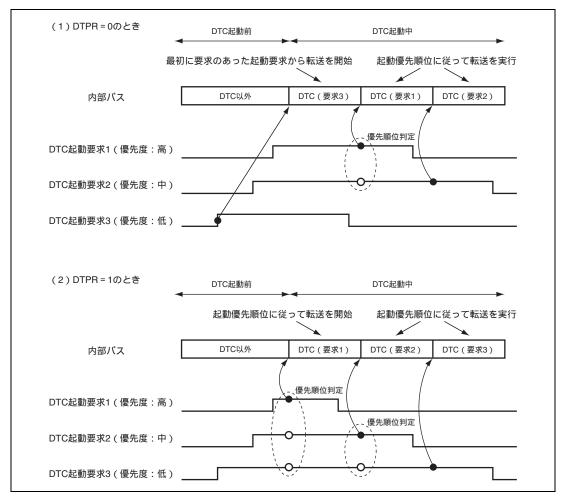

| 8.5.10 | DTC 起動の優先順位設定                               | 8-32 |

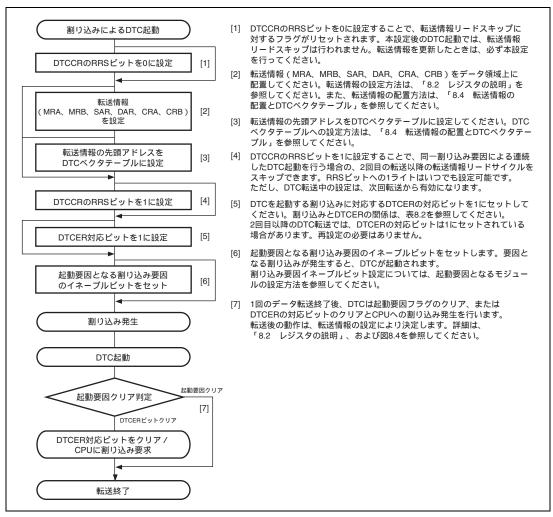

| 8.6    | 割り込みによるDTCの起動                               | 8-33 |

| 8.7    | DTC使用例                                      | 8-34 |

| 8.7.1  | ノーマル転送                                      | 8-34 |

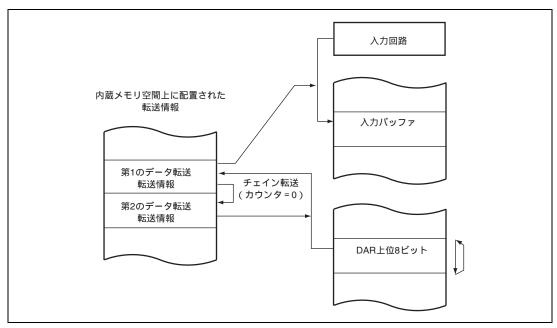

| 8.7.2  | カウンタ=0 のときのチェイン転送                           | 8-34 |

| 8.8    | 割り込み要因                                      | 8-36 |

| 8.9    | 使用上の注意事項                                    | 8-37 |

| 8.9.1  | モジュールスタンバイモードの設定                            | 8-37 |

| 8.9.2  | 内蔵 RAM                                      | 8-37 |

| 8.9.3  | DTCE ビットの設定                                 | 8-37 |

| 8.9.4  | チェイン転送                                      | 8-37 |

| 8.9.5  | 転送情報先頭アドレス / ソースアドレス / デスティネーションアドレス        | 8-37 |

| 8.9.6  | DTC による DMAC/DTC レジスタのアクセス                  | 8-37 |

| 8.9.7  | IRQ 割り込みを DTC 転送要因にした場合の注意事項                | 8-37 |

| 8.9.8  | SCI および SCIF を DTC 起動要因とする場合の注意事項           | 8-38 |

| 8.9.9  | 割り込み要因フラグのクリア                               | 8-38 |

| 8.9.10 | NMI 割り込みと DTC 起動の競合                         | 8-38 |

| 8.9.11 | DTC 起動要求が途中で取り下げられた場合の動作                    | 8-38 |

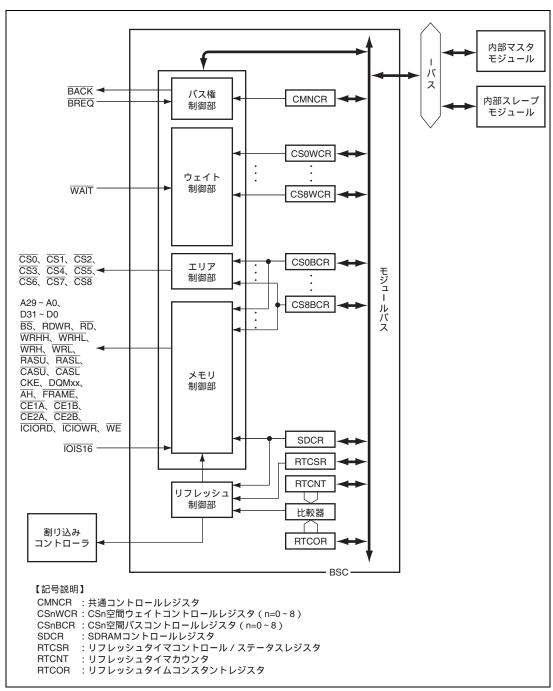

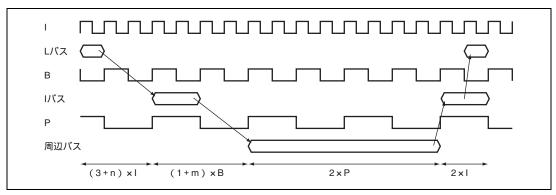

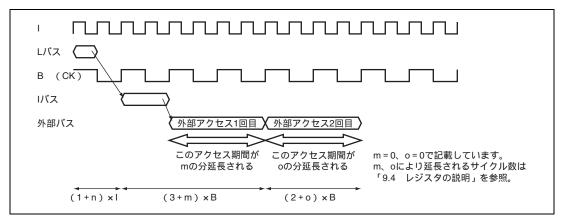

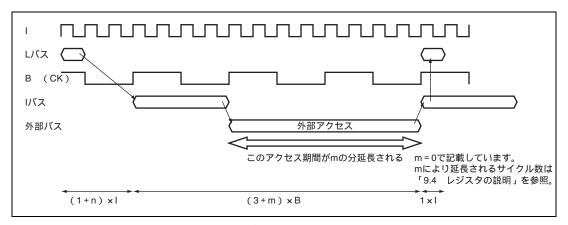

| 9. バス  | ステートコントローラ(BSC)                             | 9-1  |

| 9.1    | 特長                                          | 9-1  |

| 9.2    | 入出力端子                                       | 9-4  |

| 9.3    | エリアの概要                                      | 9-6  |

| 9.3.1  | 空間分割                                        | 9-6  |

| 9.3.2  | アドレスマップ                                     | 9-6  |

| 9.4    | レジスタの説明                                     | 9-20 |

| 9.4.1  | 共通コントロールレジスタ(CMNCR)                         | 9-21 |

| 9.4.2  | CSn 空間バスコントロールレジスタ ( CSnBCR ) ( n = 0 ~ 8 ) | 9-22 |

| 9.4.3  | CSn 空間ウェイトコントロールレジスタ(CSnWCR ) ( n = 0 ~ 8 ) | 9-26  |

|--------|---------------------------------------------|-------|

| 9.4.4  | SDRAM コントロールレジスタ ( SDCR )                   | 9-42  |

| 9.4.5  | リフレッシュタイマコントロール / ステータスレジスタ ( RTCSR )       | 9-44  |

| 9.4.6  | リフレッシュタイマカウンタ(RTCNT)                        | 9-45  |

| 9.4.7  | リフレッシュタイムコンスタントレジスタ(RTCOR)                  | 9-46  |

| 9.4.8  | バス機能拡張レジスタ ( BSCEHR )                       | 9-47  |

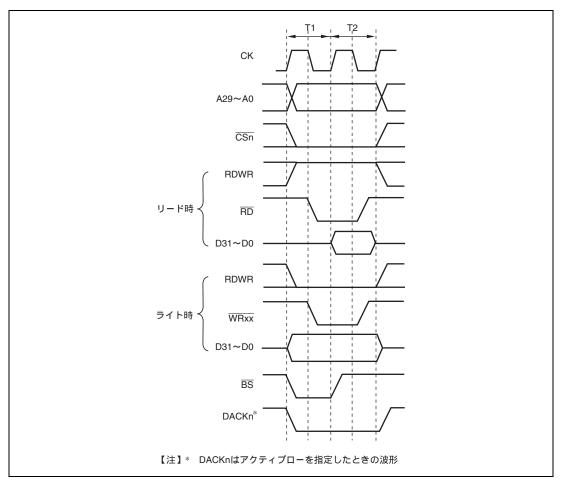

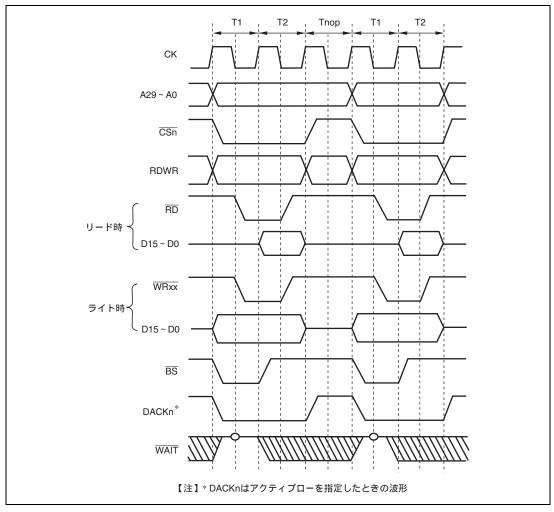

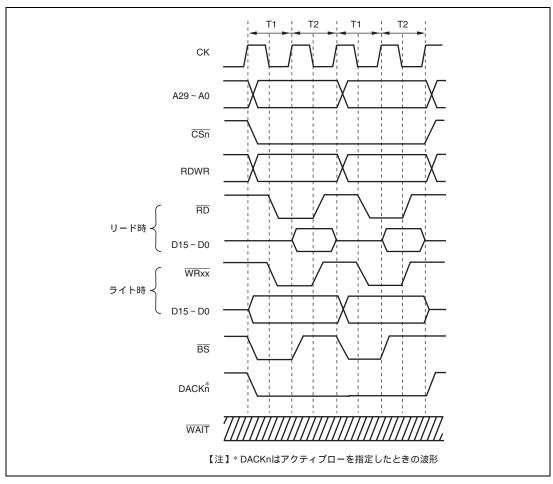

| 9.5    | 動作説明                                        | 9-51  |

| 9.5.1  | エンディアン / アクセスサイズとデータアライメント                  | 9-51  |

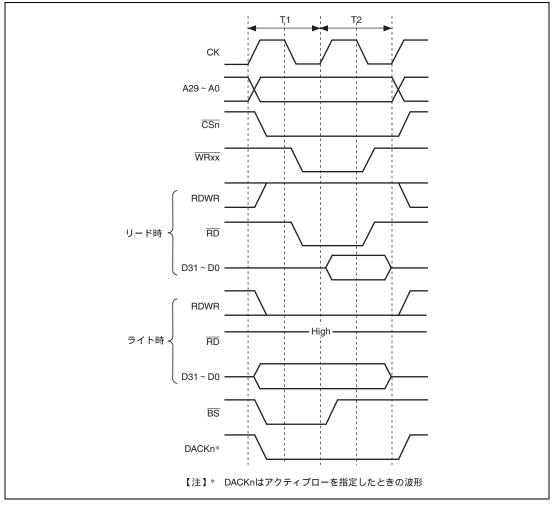

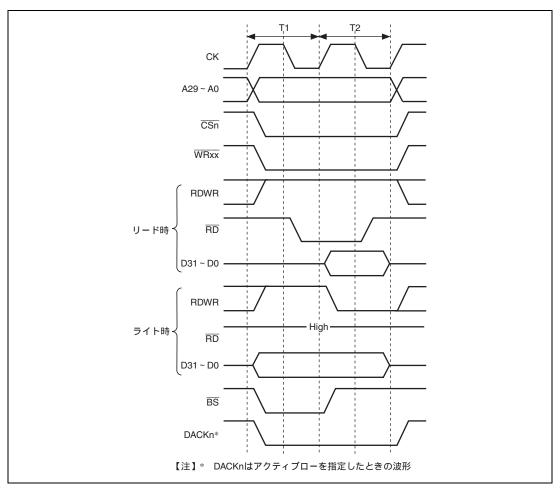

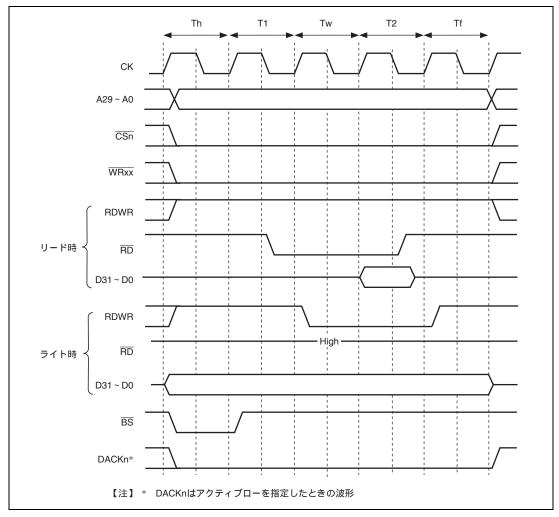

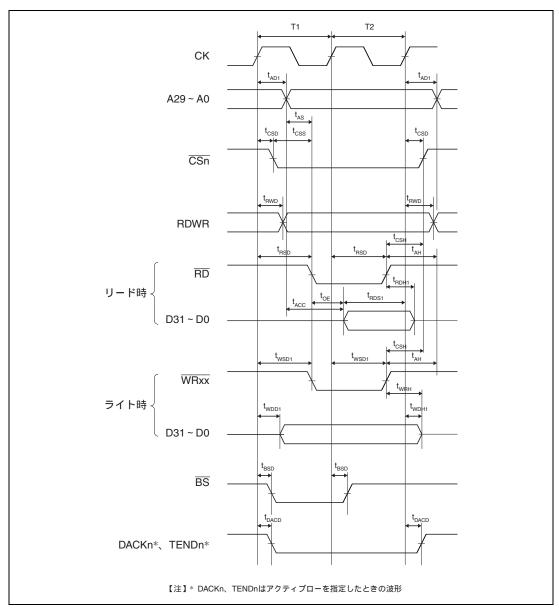

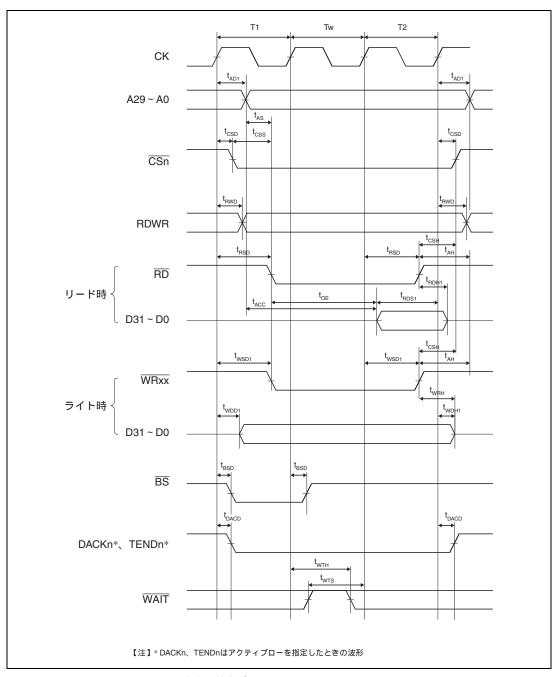

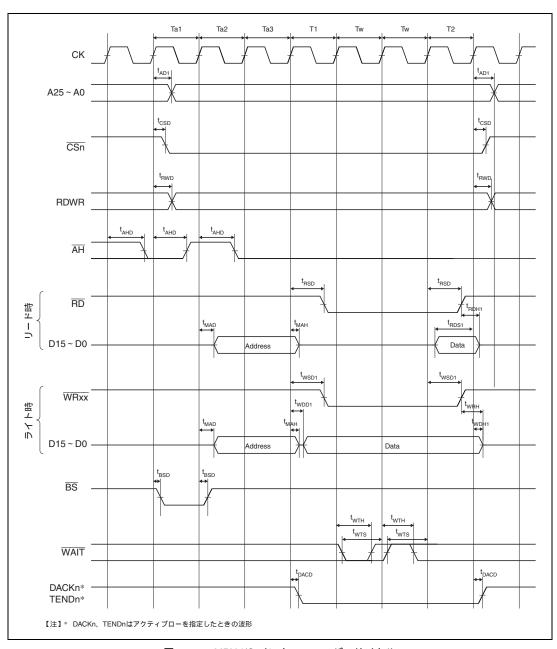

| 9.5.2  | 通常空間インタフェース                                 | 9-54  |

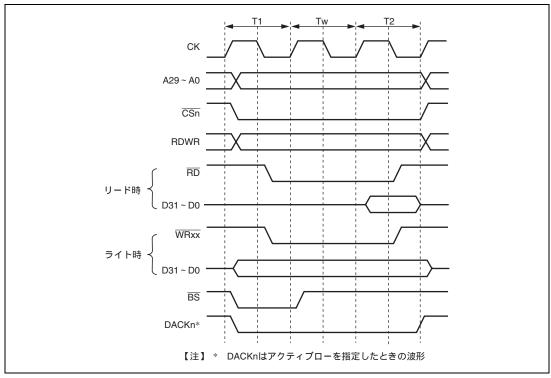

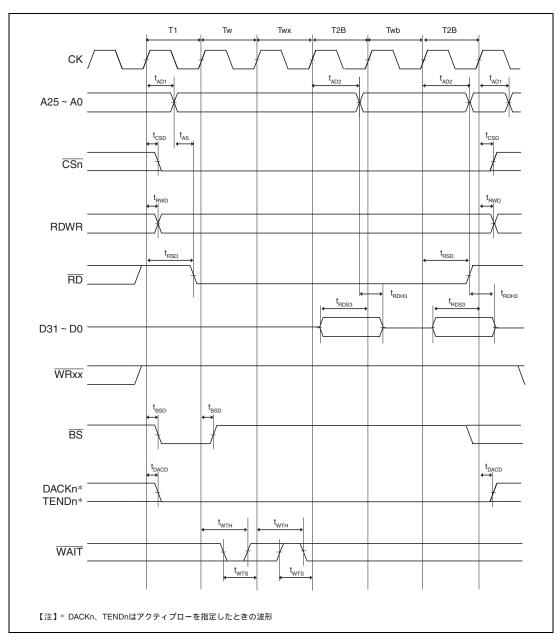

| 9.5.3  | アクセスウェイト制御                                  | 9-59  |

| 9.5.4  | CSn アサート期間拡張                                | 9-61  |

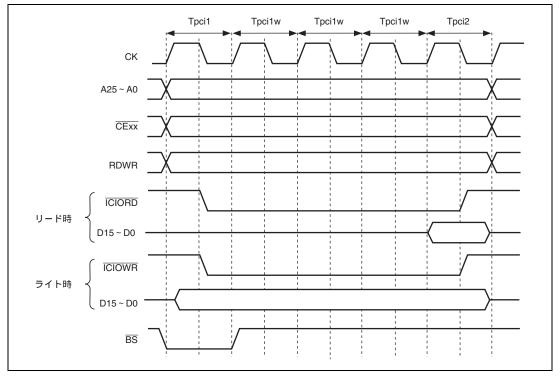

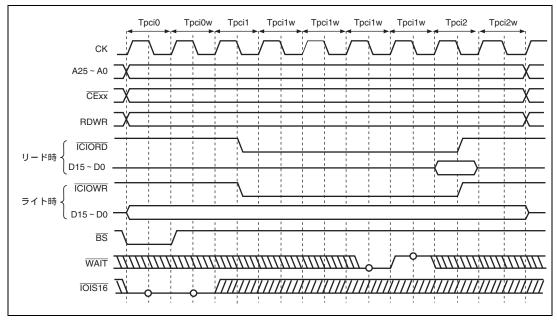

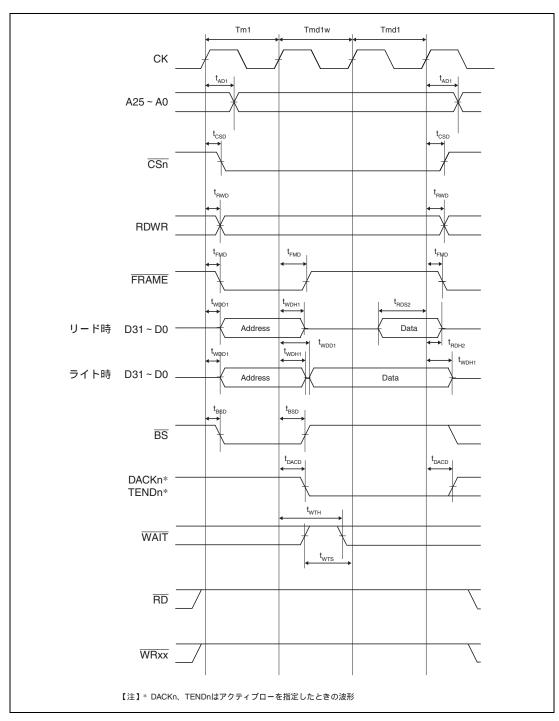

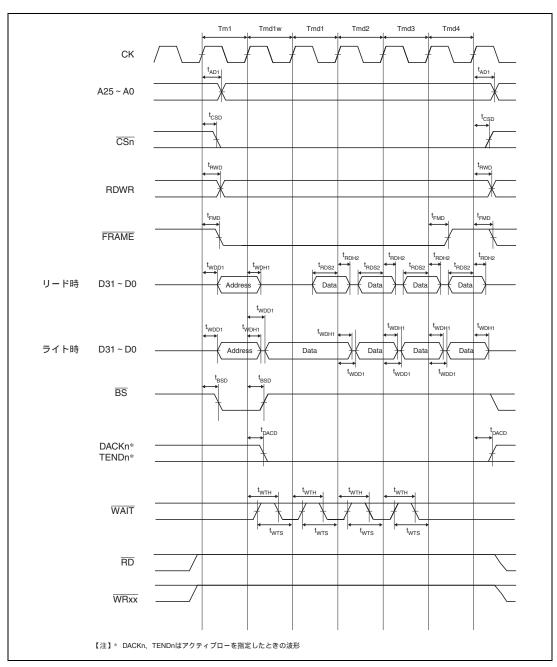

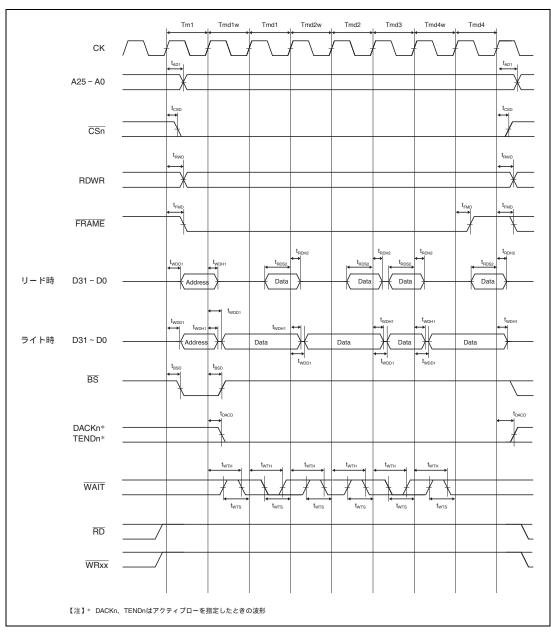

| 9.5.5  | MPX-I/O インタフェース                             | 9-62  |

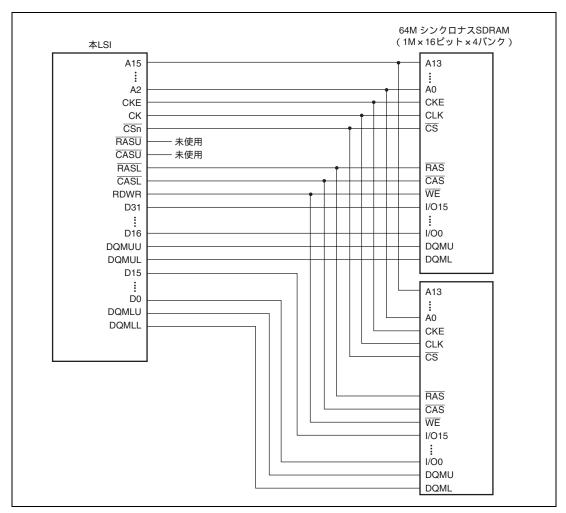

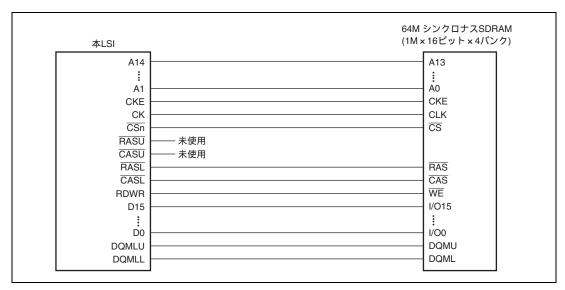

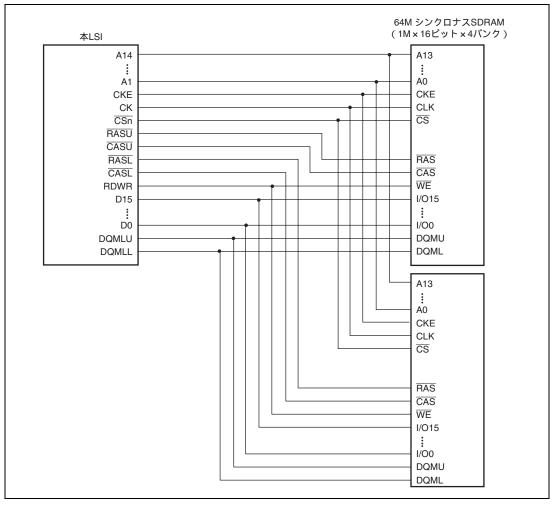

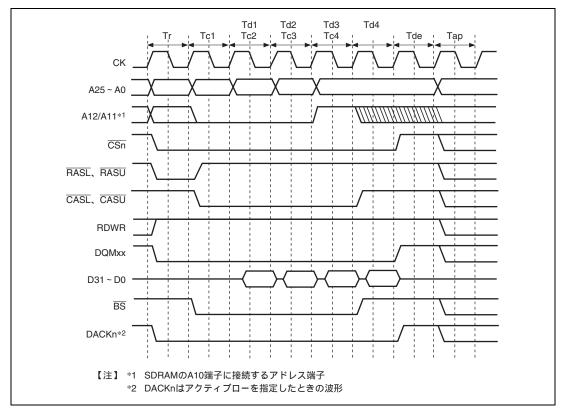

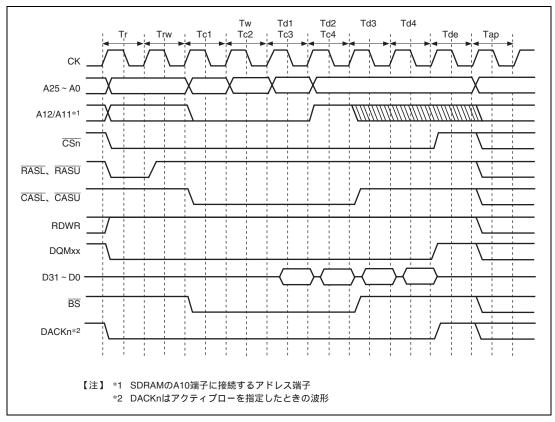

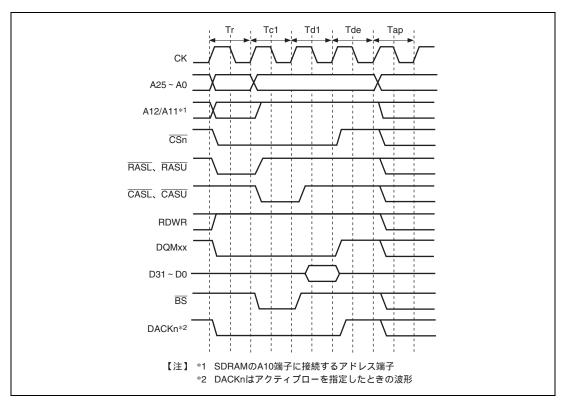

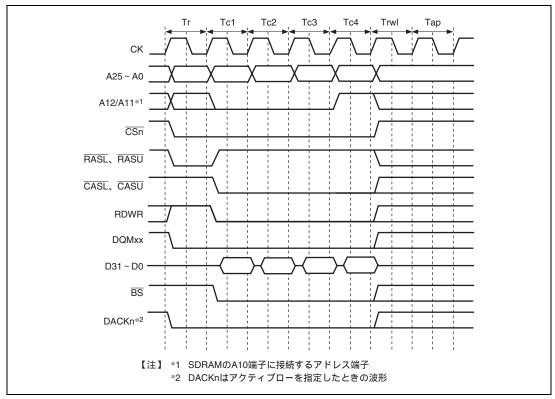

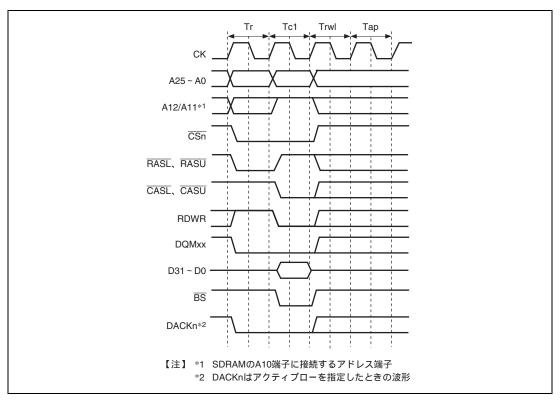

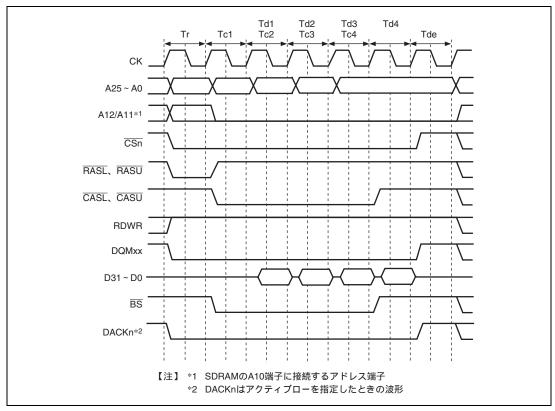

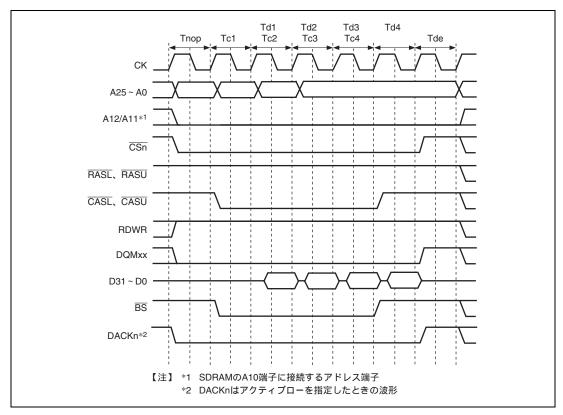

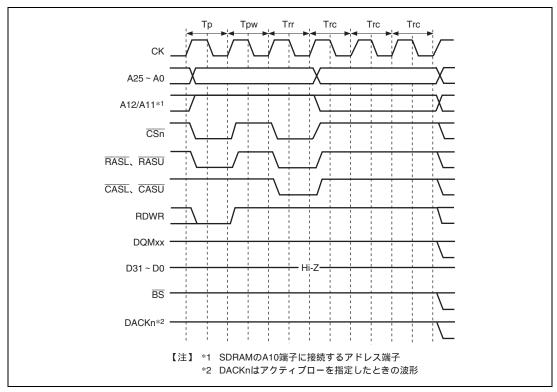

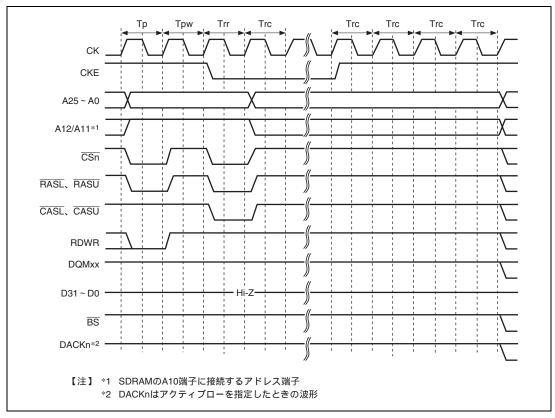

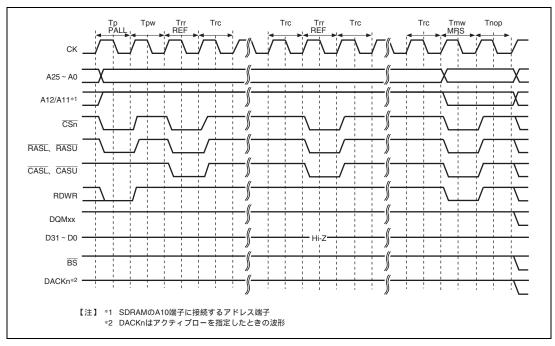

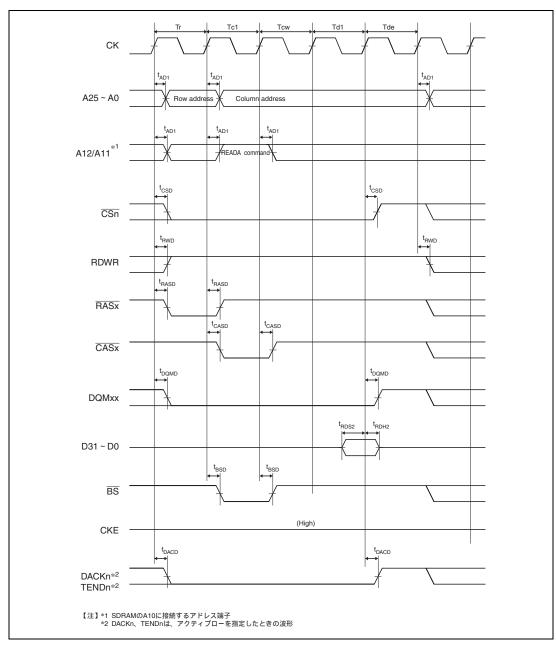

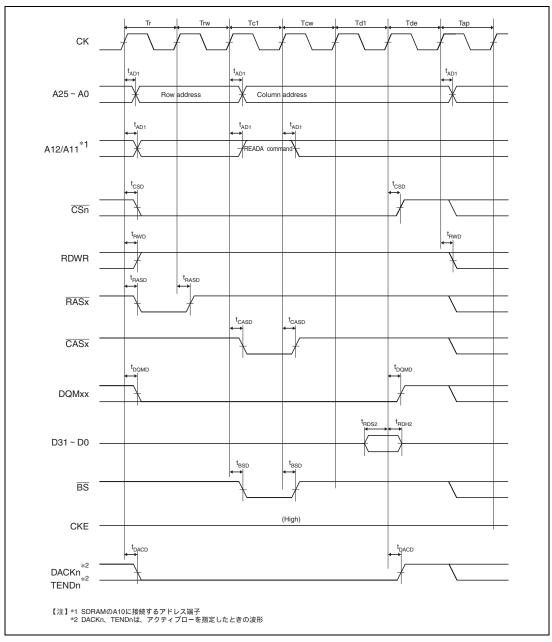

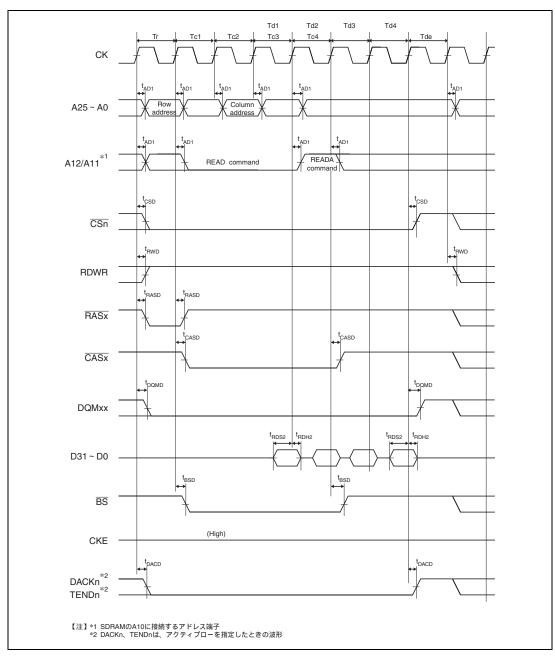

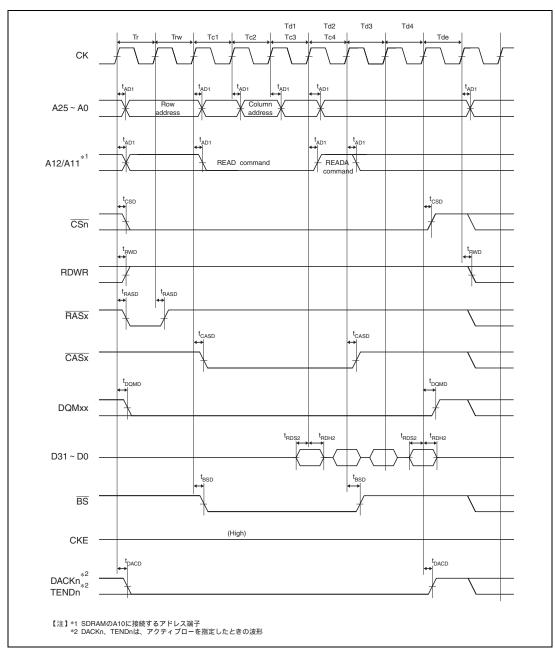

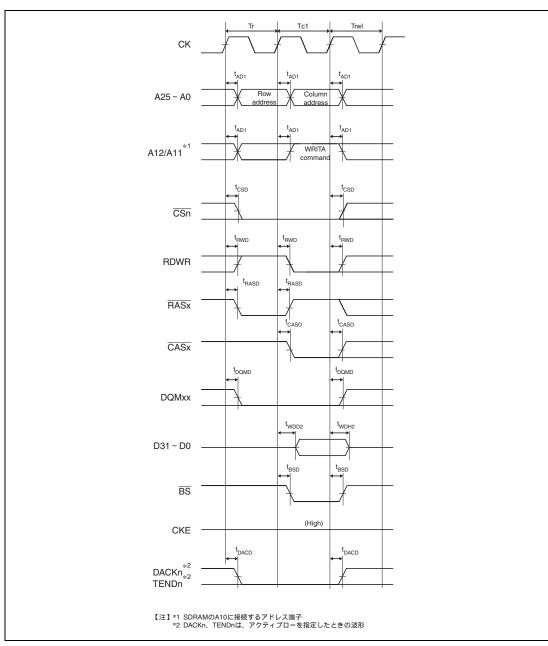

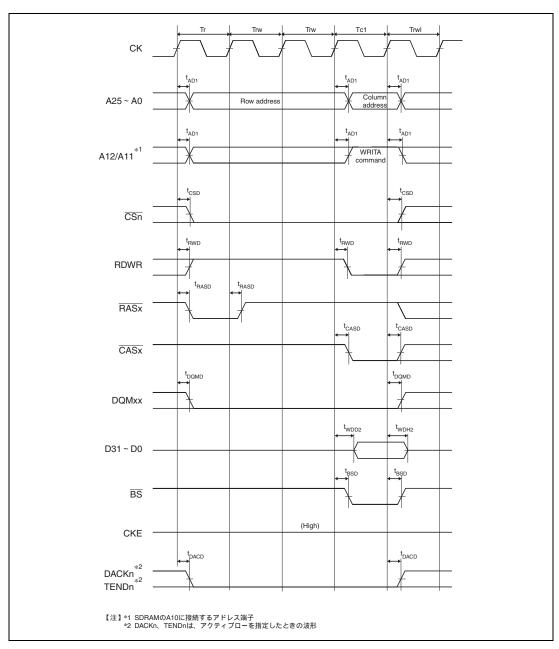

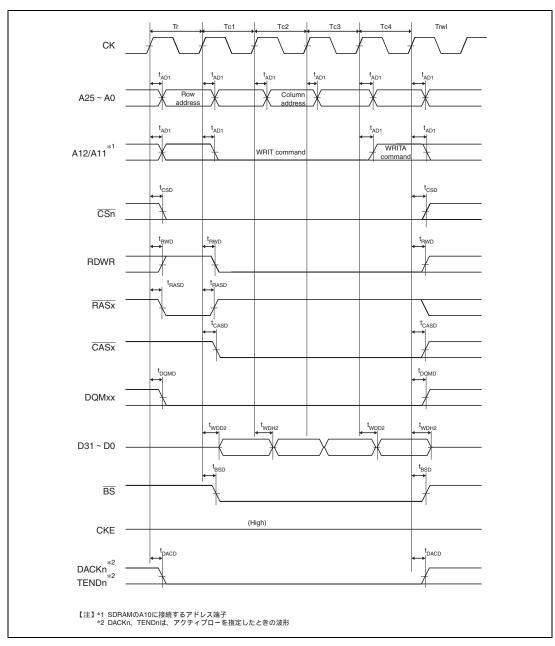

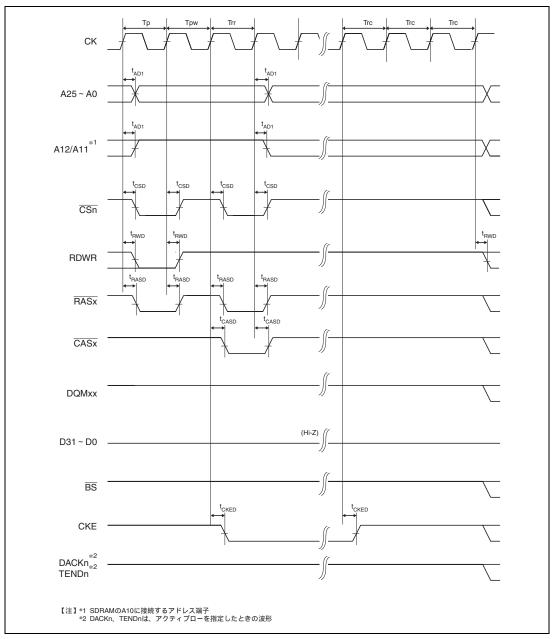

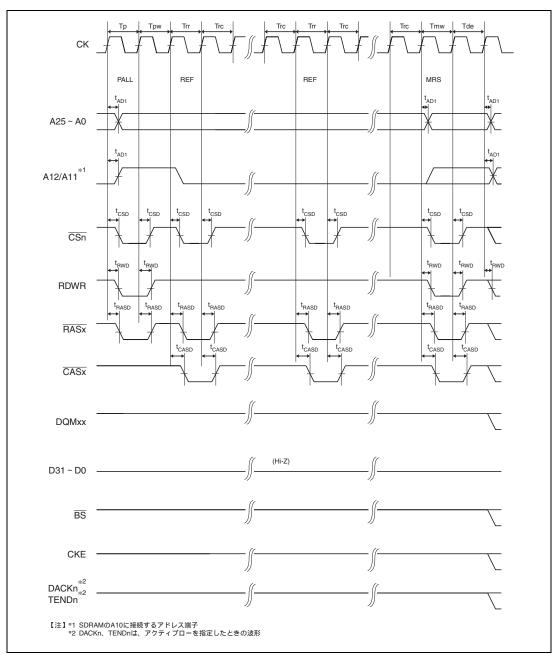

| 9.5.6  | SDRAM インタフェース                               | 9-66  |

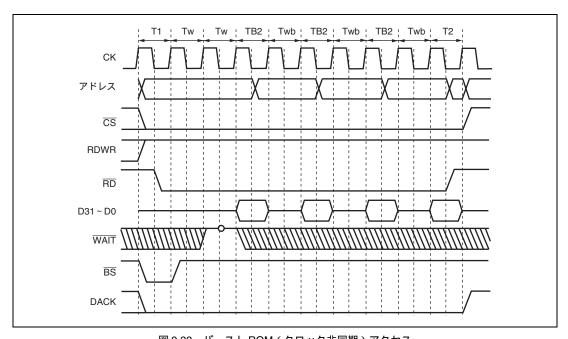

| 9.5.7  | バースト ROM ( クロック非同期 ) インタフェース                | 9-94  |

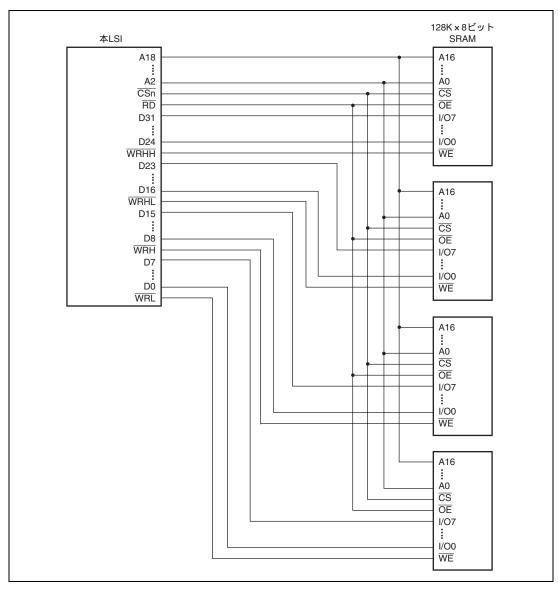

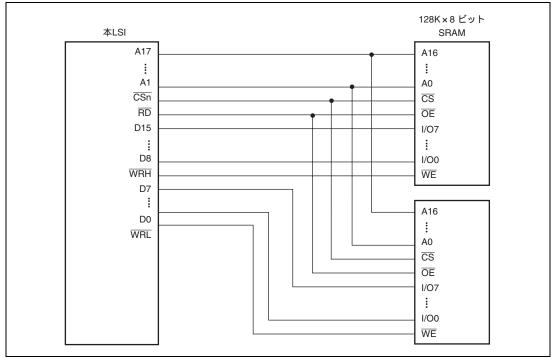

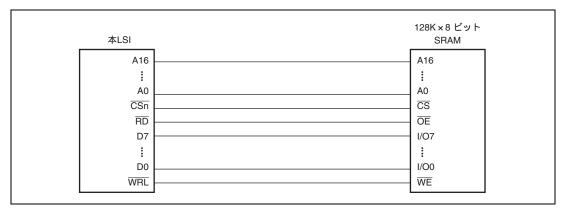

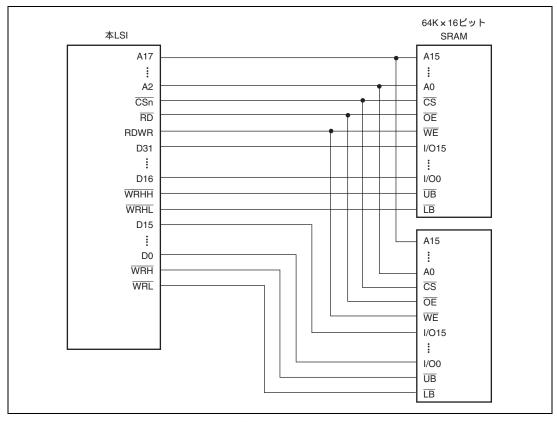

| 9.5.8  | バイト選択付き SRAM インタフェース                        | 9-96  |

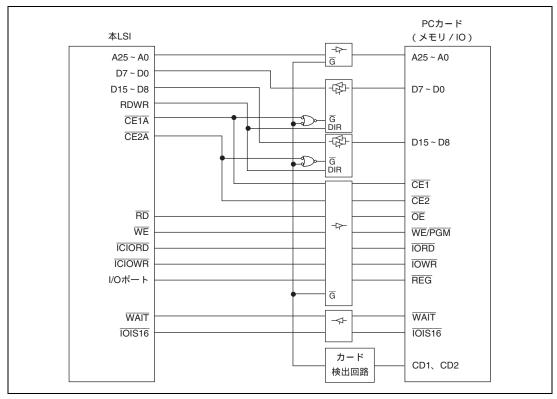

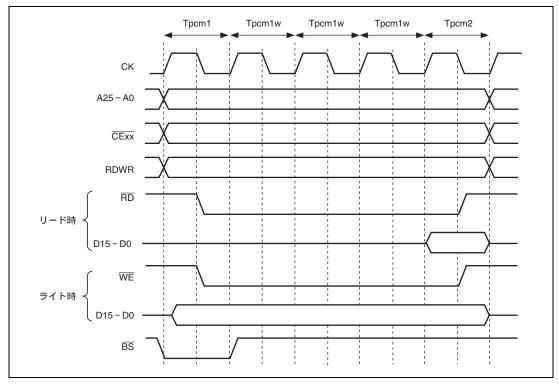

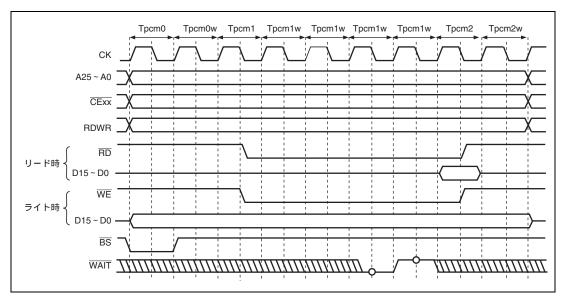

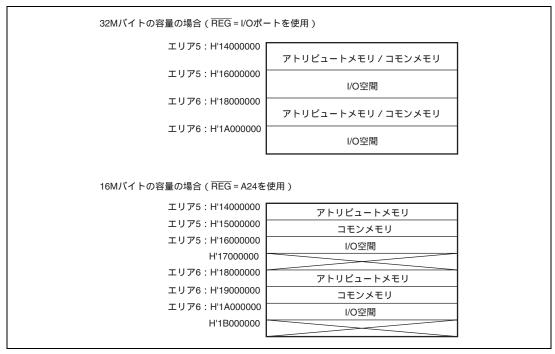

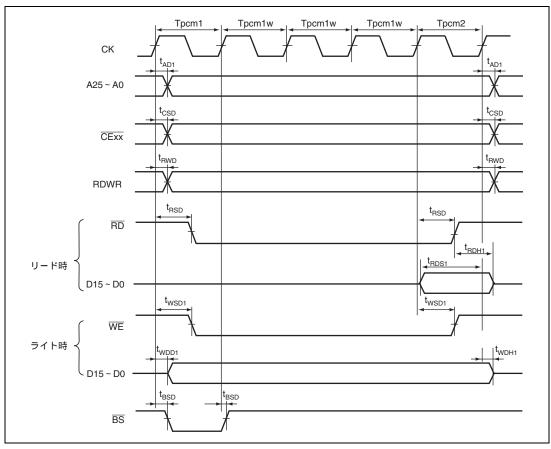

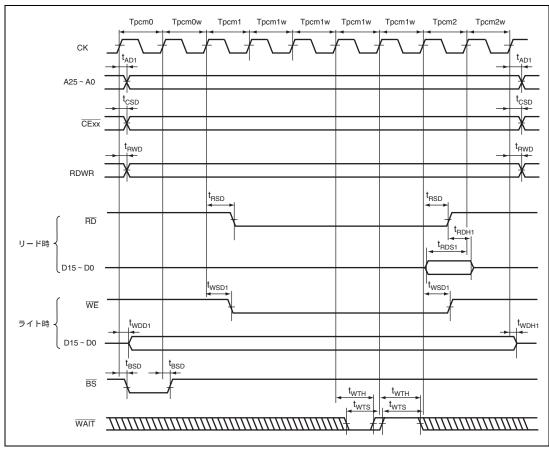

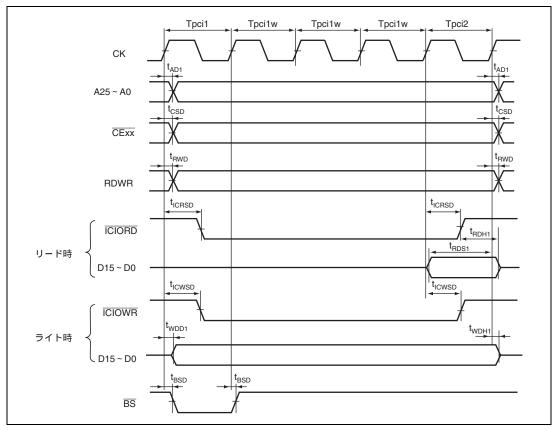

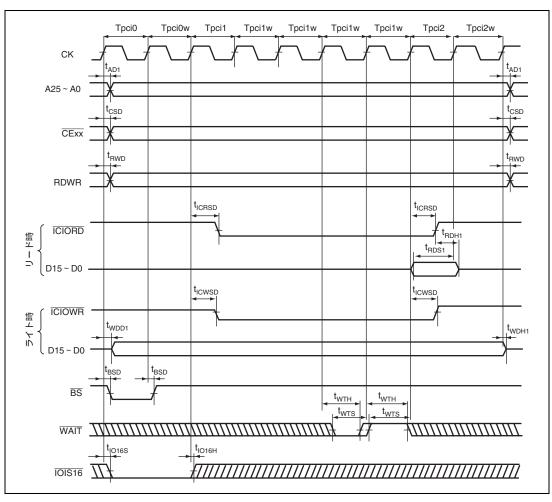

| 9.5.9  | PCMCIA インタフェース                              | 9-101 |

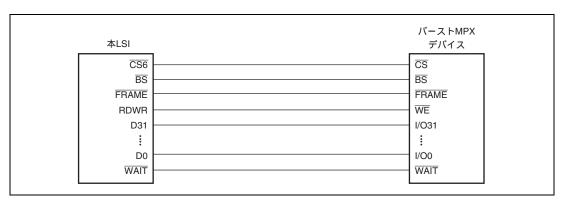

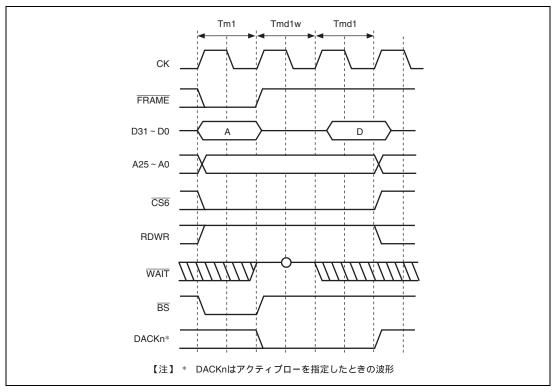

| 9.5.10 | バースト MPX-I/O インタフェース                        | 9-107 |

| 9.5.11 | バースト ROM ( クロック同期 ) インタフェース                 | 9-112 |

| 9.5.12 | アクセスサイクル間ウェイト                               | 9-113 |

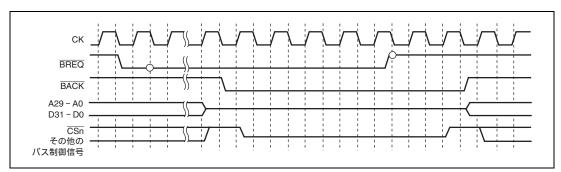

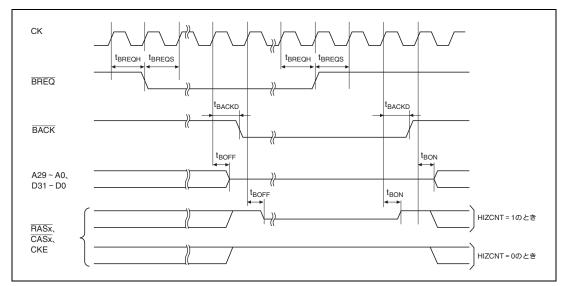

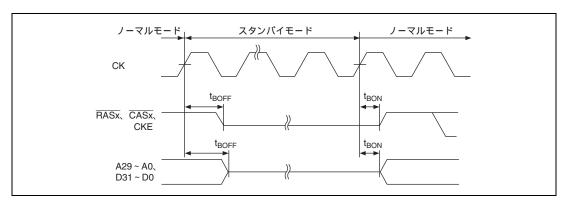

| 9.5.13 | バスアービトレーション                                 | 9-122 |

| 9.5.14 | その他                                         | 9-127 |

| 9.5.15 | CPU から内蔵 FLASH、内蔵 RAM へのアクセス                | 9-128 |

| 9.5.16 | CPU から内蔵周辺 I/O レジスタへのアクセス                   | 9-128 |

| 9.5.17 | CPU から外部メモリへのアクセス                           | 9-130 |

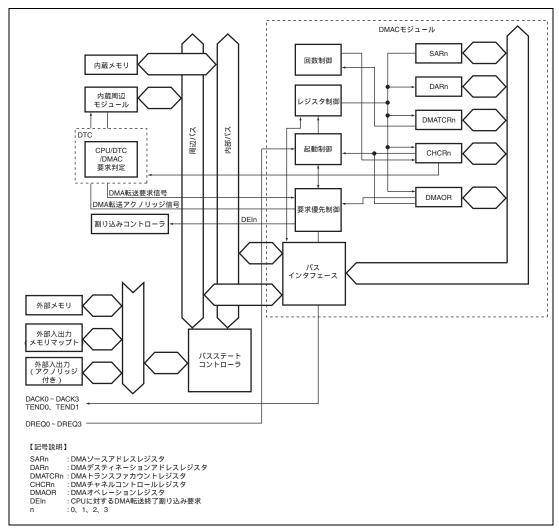

| 10. ダイ | (レクトメモリアクセスコントローラ(DMAC)                     | 10-1  |

| 10.1   | 特長                                          | 10-1  |

| 10.2   | 入出力端子                                       | 10-3  |

| 10.3   | レジスタの説明                                     | 10-4  |

| 10.3.1 | DMA ソースアドレスレジスタ_0~3 ( SAR_0~3 )             | 10-5  |

| 10.3.2 | DMA デスティネーションアドレスレジスタ_0~3 ( DAR_0~3 )       | 10-5  |

| 10.3.3 | DMA トランスファカウントレジスタ_0~3 ( DMATCR_0~3 )       | 10-6  |

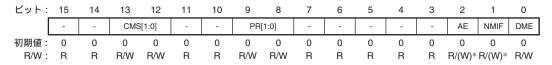

| 10.3.4 | DMA チャネルコントロールレジスタ_0~3 ( CHCR_0~3 )         | 10-7  |

| 10.3.5 | DMA オペレーションレジスタ(DMAOR)                      | 10-11 |

| 10.3.6 | バス機能拡張レジスタ ( BSCEHR )                       | 10-13 |

| 10.4   | 動作説明                                        | 10-14 |

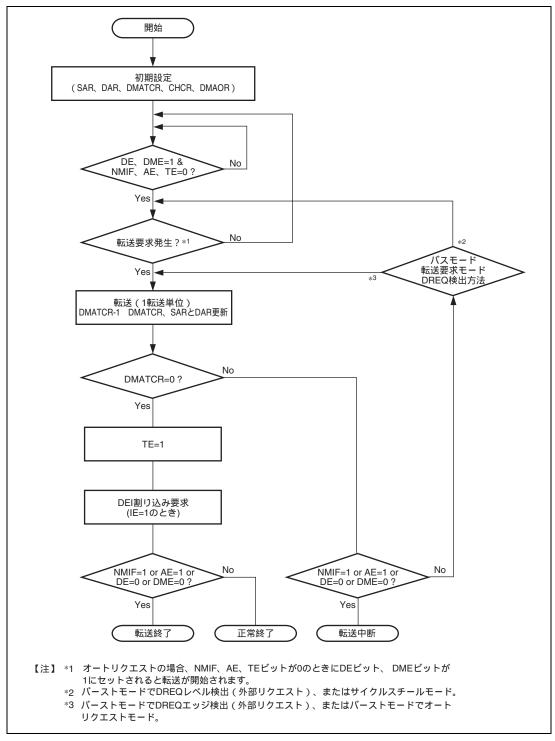

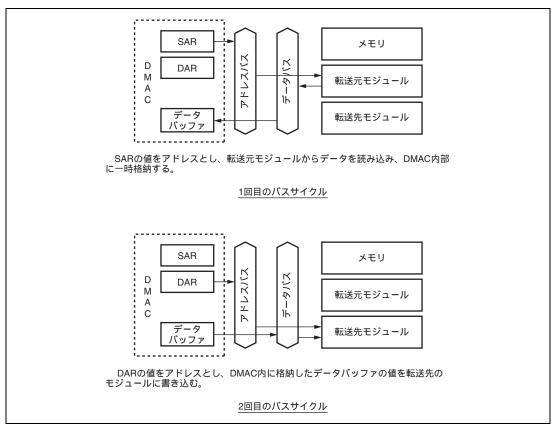

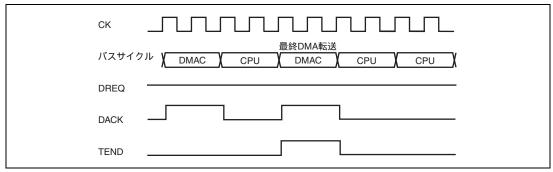

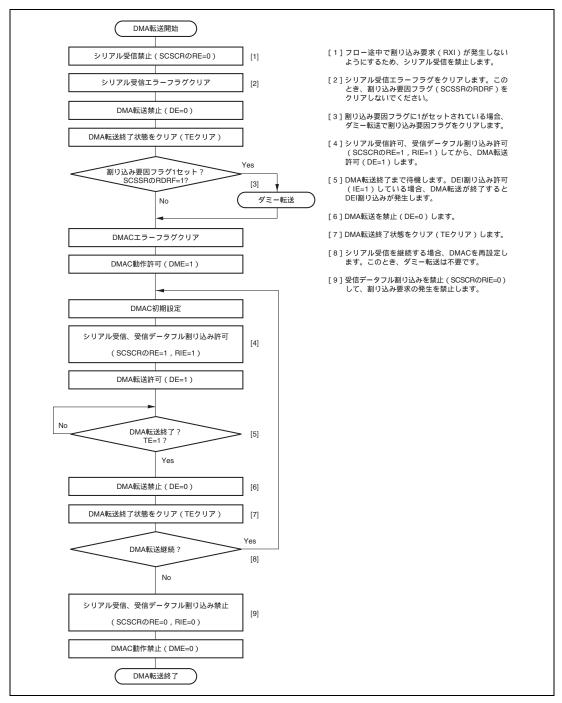

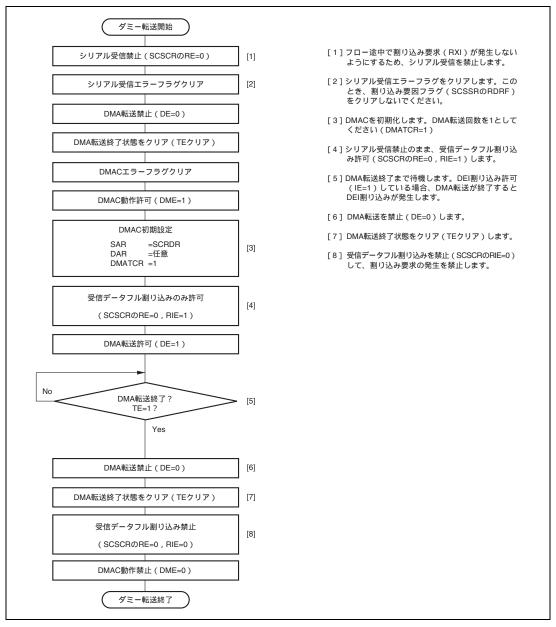

| 10.4.1 | 転送フロー                                       | 10-14 |

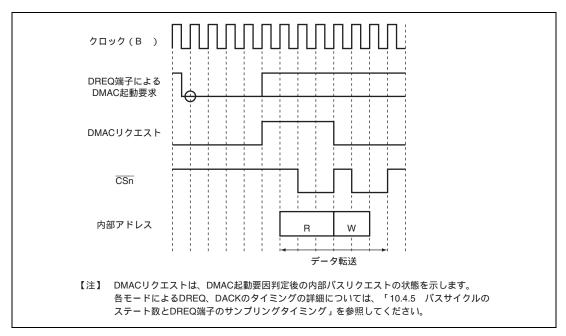

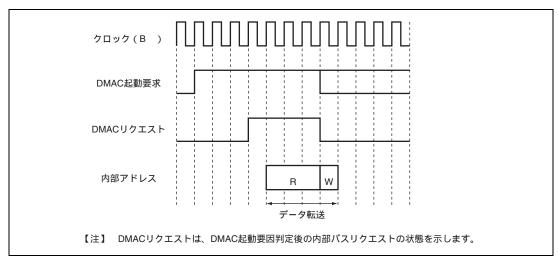

| 10.4.2 | DMA 転送要求                                    | 10-16 |

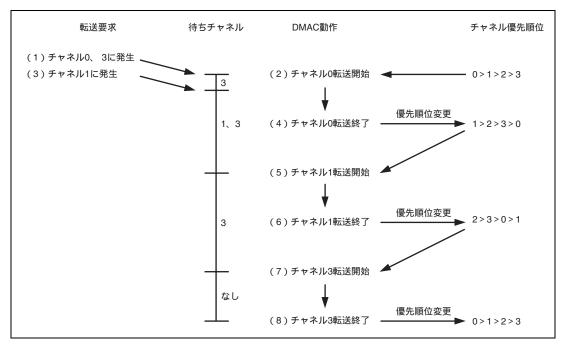

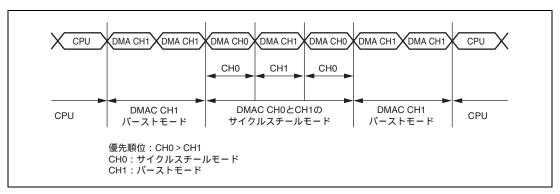

| 10.4.3 | チャネルの優先順位                                   | 10-19 |

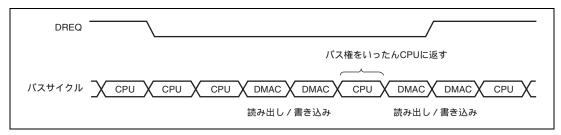

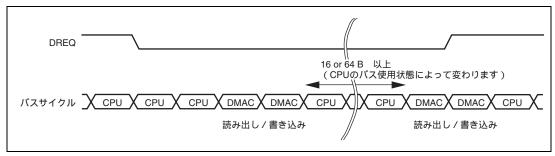

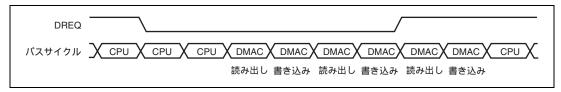

| 10.4.4 | DMA 転送の種類                                   | 10-23 |

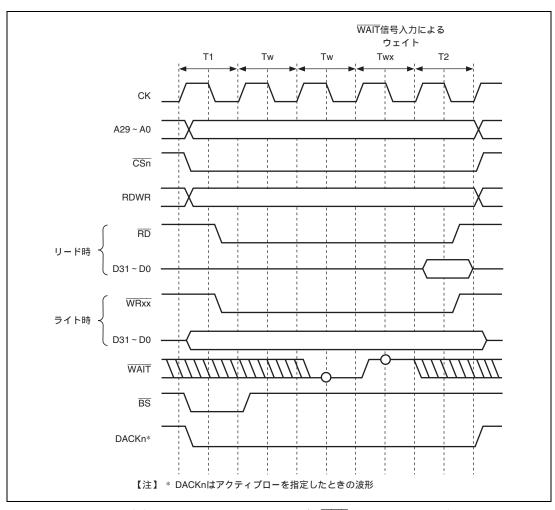

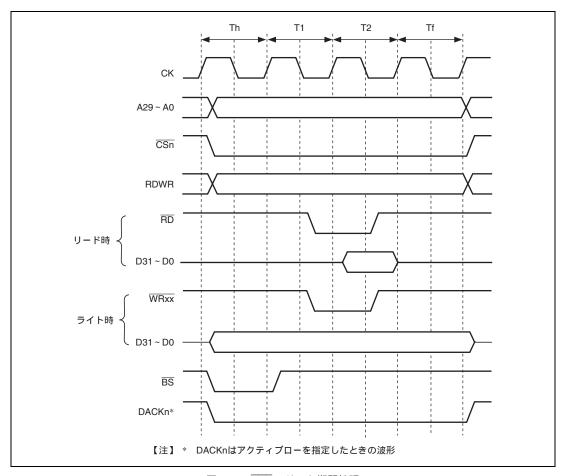

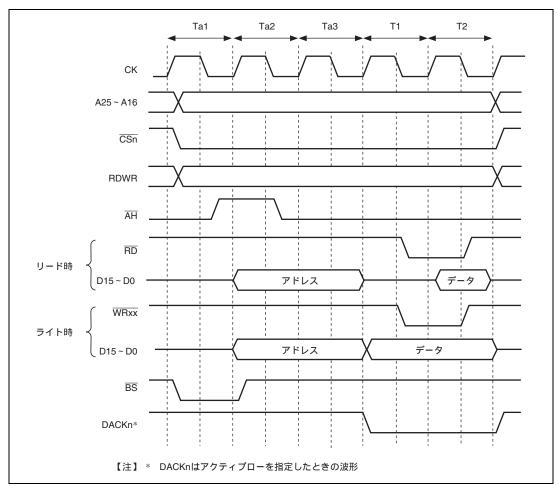

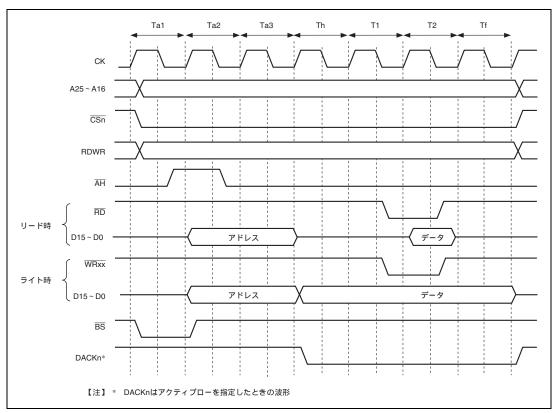

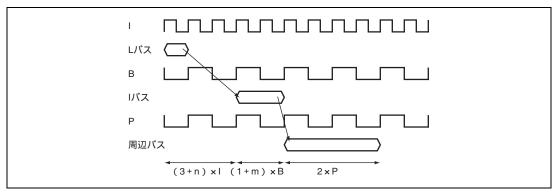

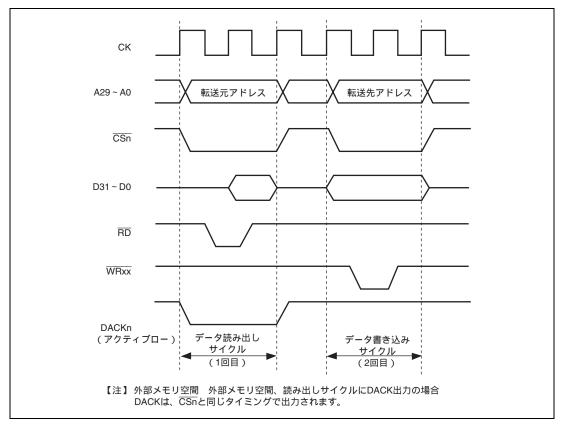

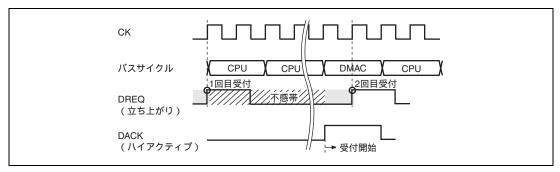

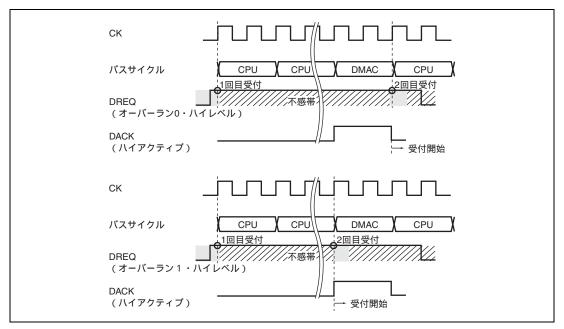

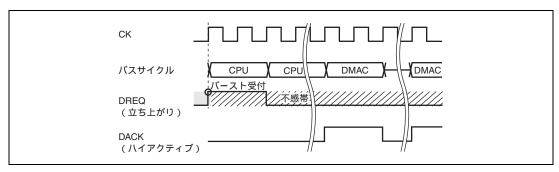

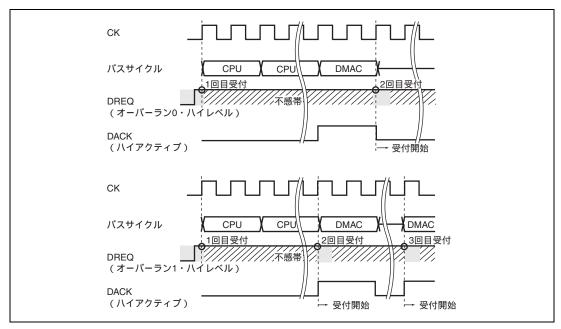

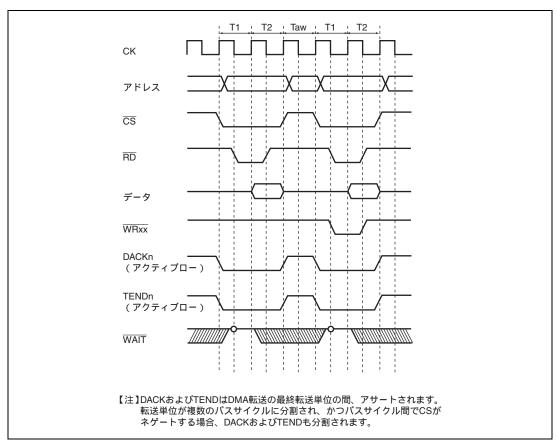

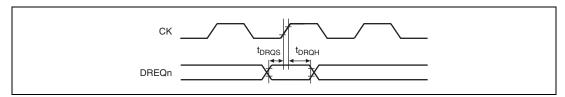

| 10.4.5 | バスサイクルのステート数と DREQ 端子のサンプリングタイミング           | 10-32 |

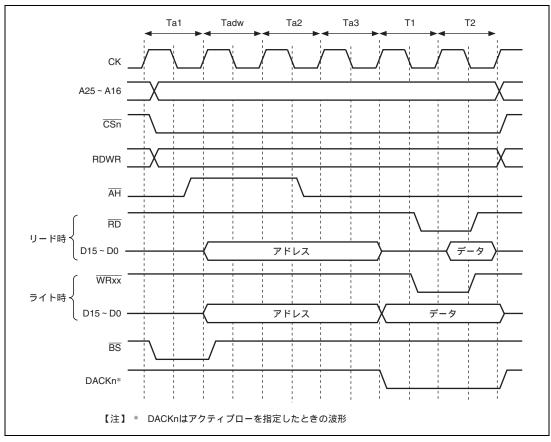

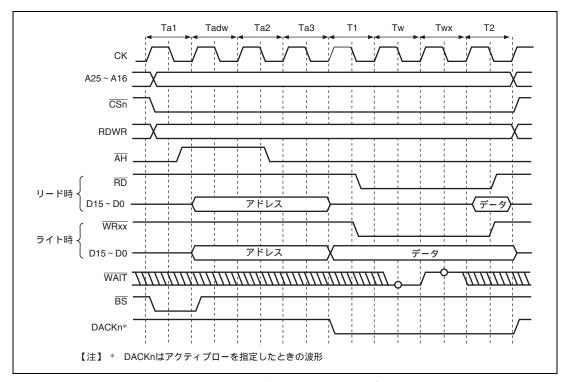

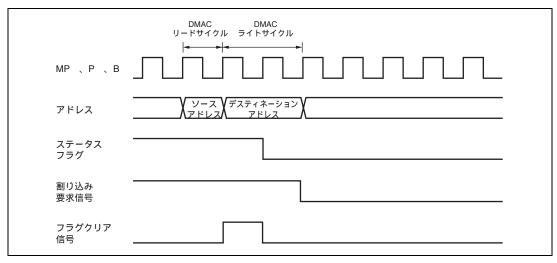

| 10.4.6  | 動作タイミング                                     | 10-36 |

|---------|---------------------------------------------|-------|

| 10.5 使  | 用上の注意事項                                     | 10-37 |

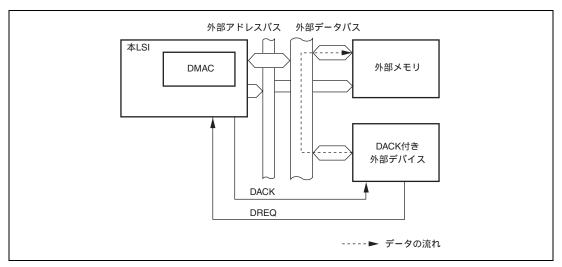

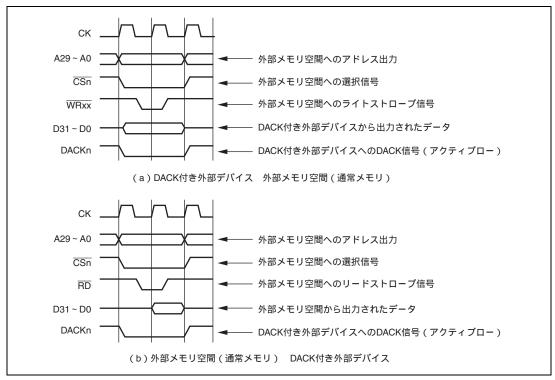

| 10.5.1  | DACK 端子出力の注意事項                              | 10-37 |

| 10.5.2  | 周辺モジュールによる DMA 転送                           | 10-37 |

| 10.5.3  | モジュールスタンバイモードの設定                            | 10-37 |

| 10.5.4  | DMAC による DMAC/DTC レジスタのアクセス                 | 10-38 |

| 10.5.5  | SCI を DMAC 起動要因とする場合の注意事項                   | 10-38 |

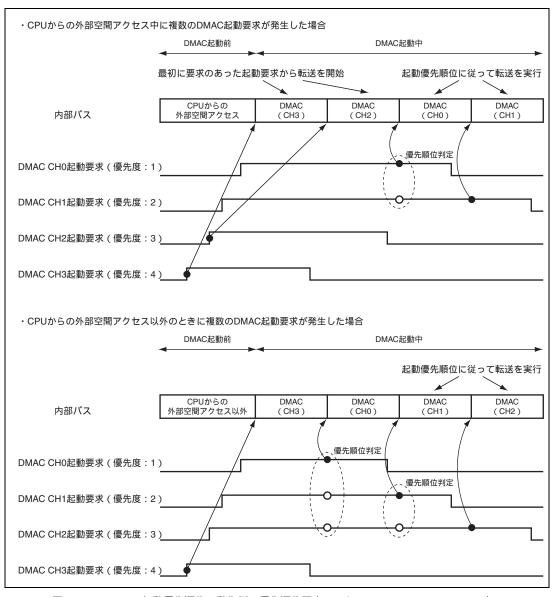

| 10.5.6  | CHCR の設定                                    | 10-38 |

| 10.5.7  | 複数チャネルの起動時の注意事項                             | 10-38 |

| 10.5.8  | 転送要求入力時の注意事項                                | 10-38 |

| 10.5.9  | NMI 割り込みと DMAC 起動の競合                        | 10-38 |

| 10.5.10 | 内蔵モジュールリクエストモード使用上の注意事項                     | 10-38 |

| 10.5.11 | DMAC からの内蔵 RAM アクセスサイクル数                    | 10-42 |

| 10.5.12 | MTU2 を起動要因とするバーストモードでの DMAC 転送時の注意事項        | 10-42 |

| 10.5.13 | バス機能拡張レジスタ ( BSCEHR )                       | 10-42 |

|         |                                             |       |

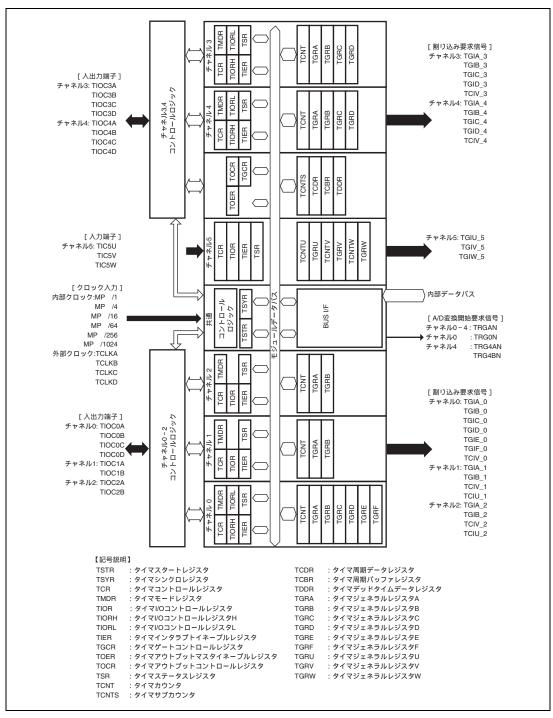

| 11. マルチ | ファンクションタイマパルスユニット2(MTU2)                    | 11-1  |

| 11.1 特  | <b></b>                                     | 11-1  |

| 11.2 入  | 出力端子                                        | 11-6  |

| 11.3 V  | ジスタの説明                                      | 11-7  |

| 11.3.1  | タイマコントロールレジスタ ( TCR )                       | 11-10 |

| 11.3.2  | タイマモードレジスタ ( TMDR )                         | 11-14 |

| 11.3.3  | タイマ I/O コントロールレジスタ ( TIOR )                 | 11-17 |

| 11.3.4  | タイマコンペアマッチクリアレジスタ(TCNTCMPCLR)               | 11-36 |

| 11.3.5  | タイマインタラプトイネーブルレジスタ(TIER)                    | 11-37 |

| 11.3.6  | タイマステータスレジスタ ( TSR )                        | 11-41 |

| 11.3.7  | タイマバッファ動作転送モードレジスタ(TBTM)                    | 11-47 |

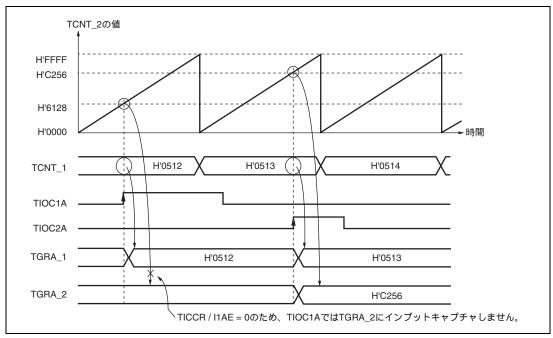

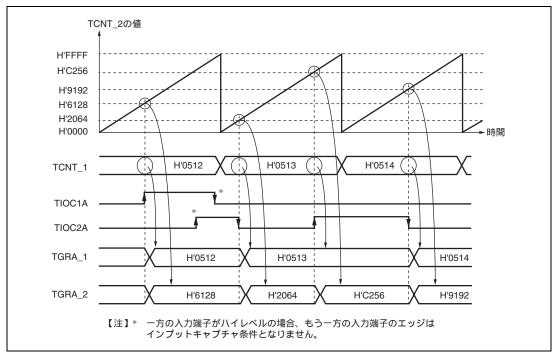

| 11.3.8  | タイマインプットキャプチャコントロールレジスタ ( TICCR )           | 11-48 |

| 11.3.9  | タイマシンクロクリアレジスタ (TSYCR)                      | 11-49 |

| 11.3.10 | タイマ A/D 変換開始要求コントロールレジスタ(TADCR)             | 11-50 |

| 11.3.11 | タイマ A/D 変換開始要求周期設定レジスタ(TADCORA/B_4)         | 11-52 |

| 11.3.12 | タイマ A/D 変換開始要求周期設定バッファレジスタ ( TADCOBRA/B_4 ) | 11-53 |

| 11.3.13 | タイマカウンタ ( TCNT )                            | 11-53 |

| 11.3.14 | タイマジェネラルレジスタ(TGR)                           | 11-53 |

| 11.3.15 | タイマスタートレジスタ ( TSTR )                        | 11-54 |

| 11.3.16 | タイマシンクロレジスタ ( TSYR )                        | 11-56 |

| 11.3.17 | タイマカウンタシンクロスタートレジスタ ( TCSYSTR )             | 11-57 |

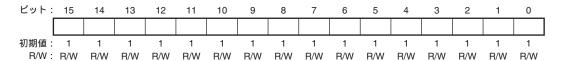

| 11.3.18 | タイマリードライトイネーブルレジスタ(TRWER)                   | 11-59 |

| 11.3.19 | タイマアウトプットマスタイネーブルレジスタ(TOER)                 | 11-60 |

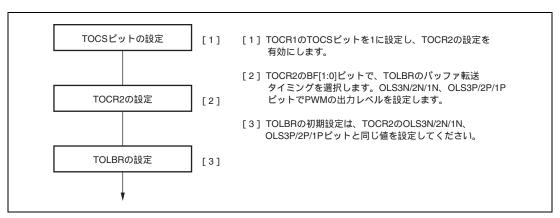

| 11.3.20 | タイマアウトプットコントロールレジスタ 1(TOCR1)                | 11-61 |

| 11.3.21 | タイマアウトプットコントロールレジスタ 2 ( TOCR2 )             | 11-63 |

| 11.3.2 | 2 タイマアウトプットレベルバッファレジスタ(TOLBR)         | 11-66  |

|--------|---------------------------------------|--------|

| 11.3.2 | 3 タイマゲートコントロールレジスタ(TGCR)              | 11-67  |

| 11.3.2 | 4 タイマサブカウンタ(TCNTS)                    | 11-68  |

| 11.3.2 | 5 タイマデッドタイムデータレジスタ(TDDR)              | 11-68  |

| 11.3.2 | 6 タイマ周期データレジスタ(TCDR)                  | 11-69  |

| 11.3.2 | 7 タイマ周期バッファレジスタ(TCBR)                 | 11-69  |

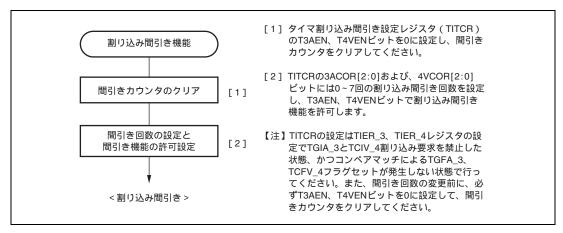

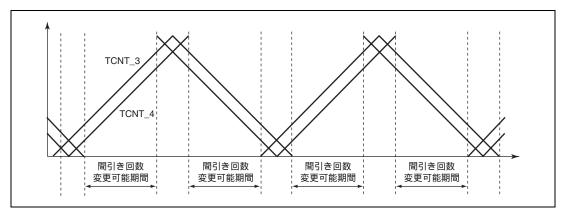

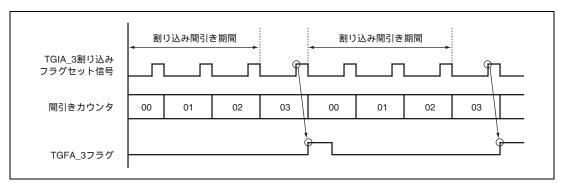

| 11.3.2 | 8 タイマ割り込み間引き設定レジスタ(TITCR)             | 11-70  |

| 11.3.2 | 9 タイマ割り込み間引き回数カウンタ(TITCNT)            | 11-71  |

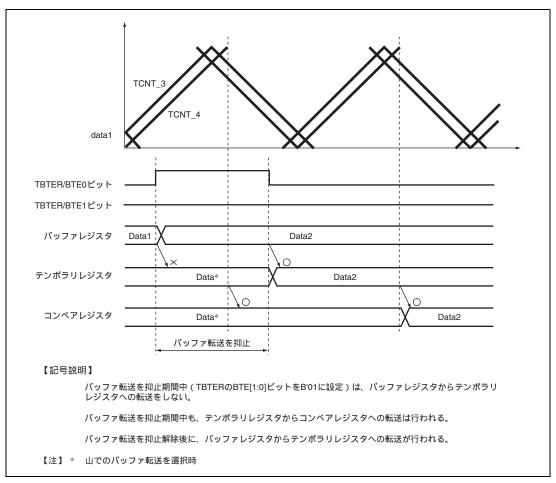

| 11.3.3 | 0 タイマバッファ転送設定レジスタ(TBTER)              | 11-72  |

| 11.3.3 | 1 タイマデッドタイムイネーブルレジスタ ( TDER )         | 11-73  |

| 11.3.3 | 2 タイマ波形コントロールレジスタ(TWCR)               | 11-74  |

| 11.3.3 | 3 バスマスタとのインタフェース                      | 11-75  |

| 11.4   | 動作説明                                  | 11-76  |

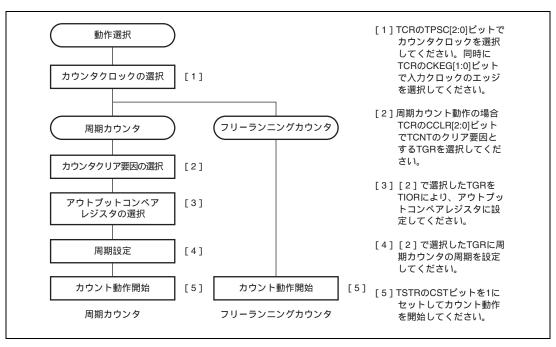

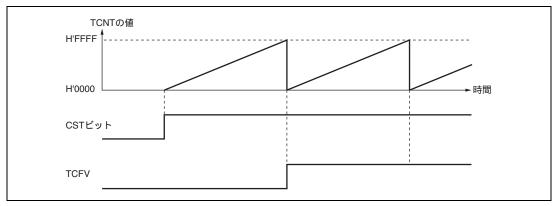

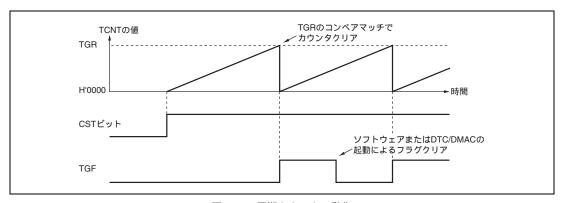

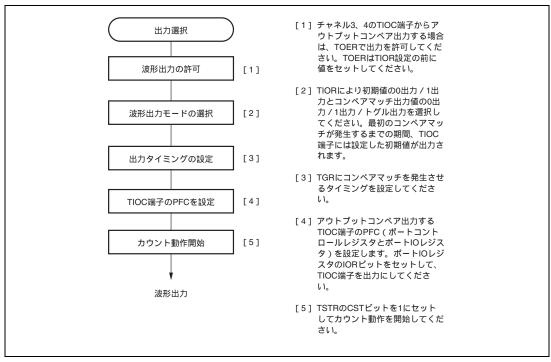

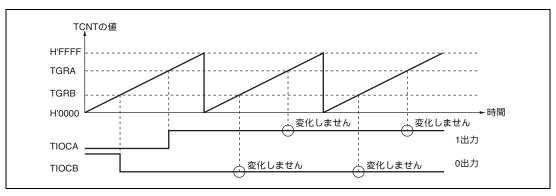

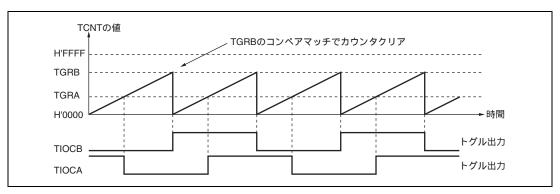

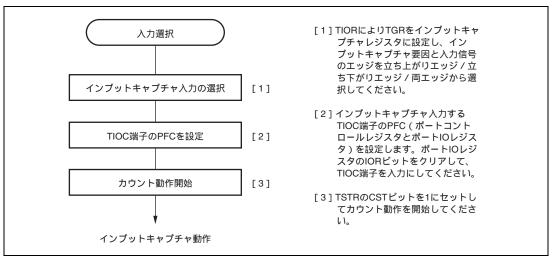

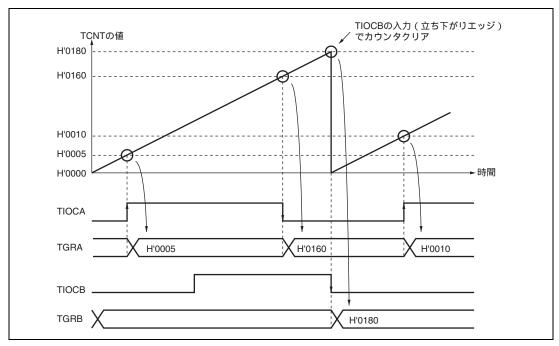

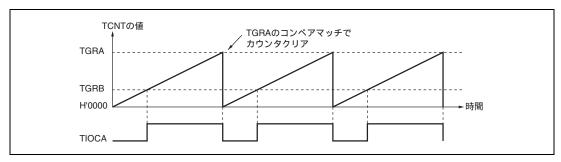

| 11.4.1 | 基本動作                                  | 11-76  |

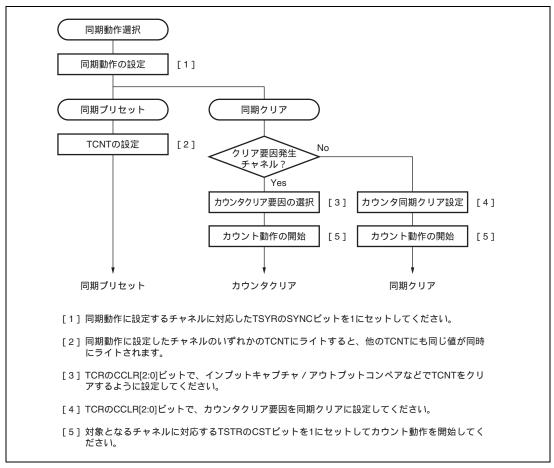

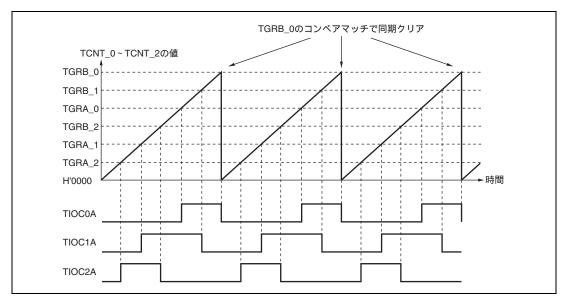

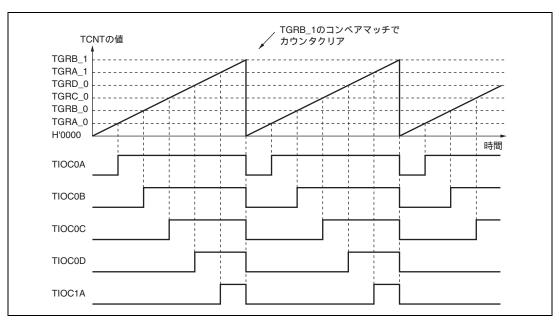

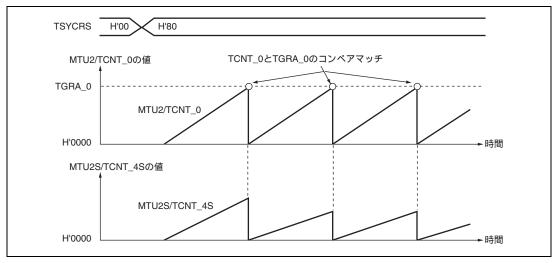

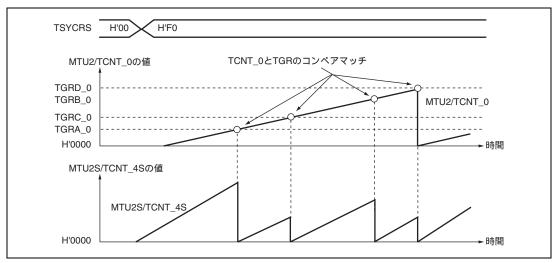

| 11.4.2 | 同期動作                                  | 11-82  |

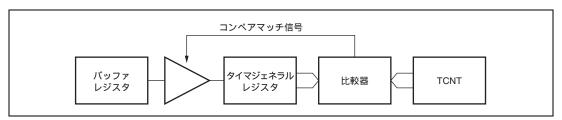

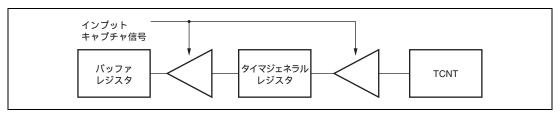

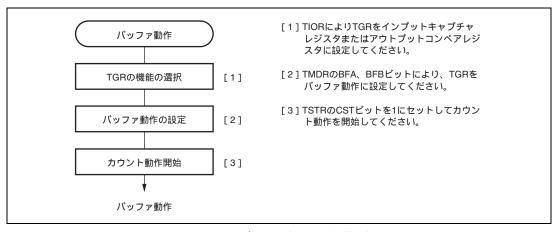

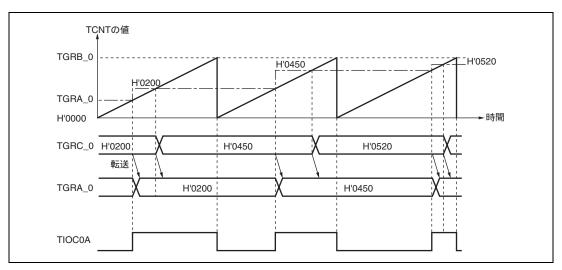

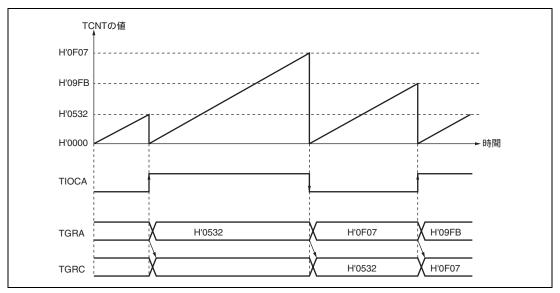

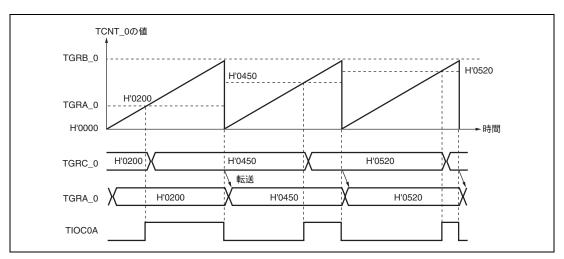

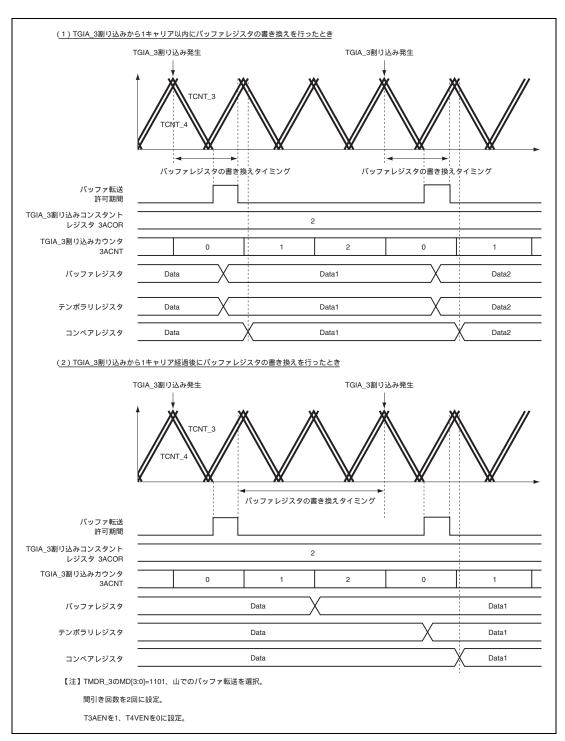

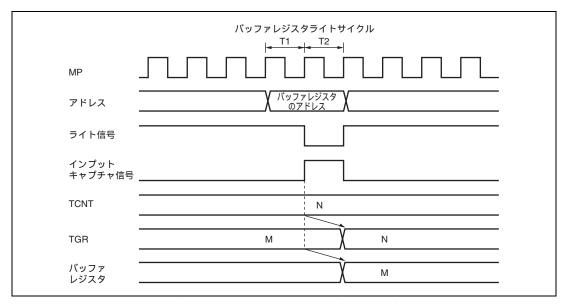

| 11.4.3 | バッファ動作                                | 11-84  |

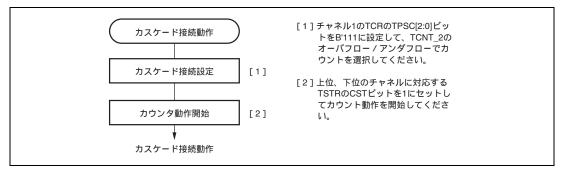

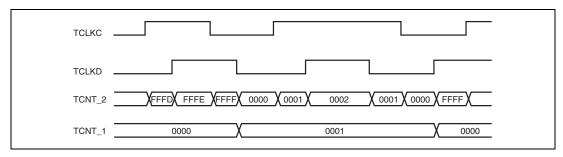

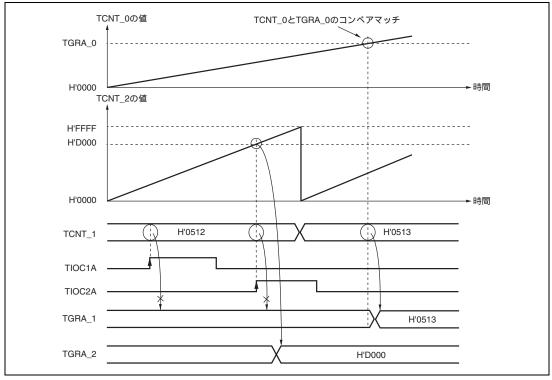

| 11.4.4 | カスケード接続動作                             | 11-88  |

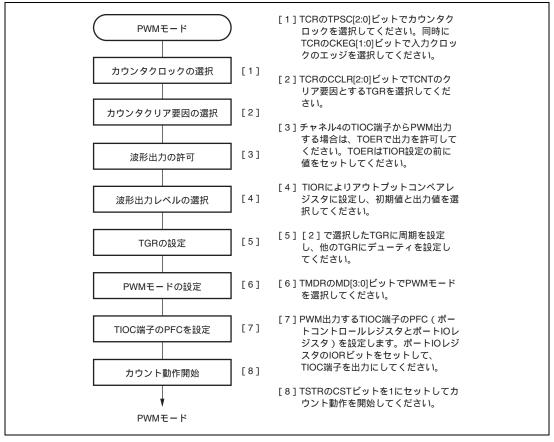

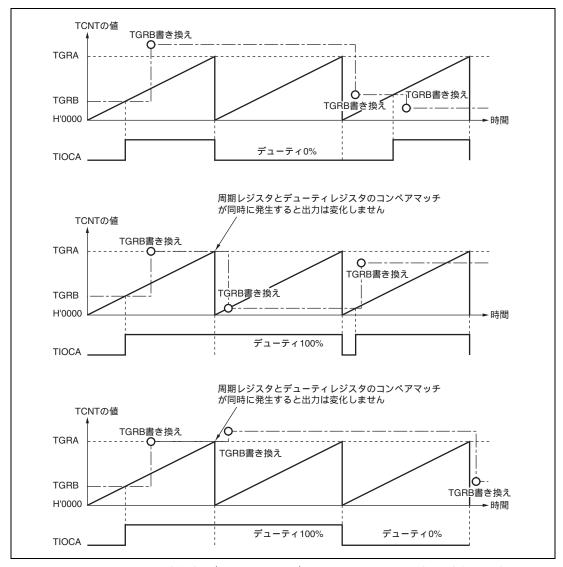

| 11.4.5 | PWM モード                               | 11-92  |

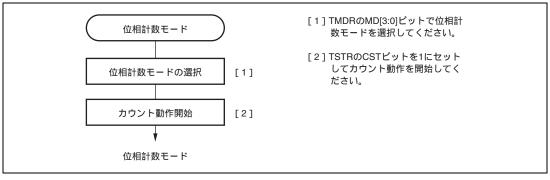

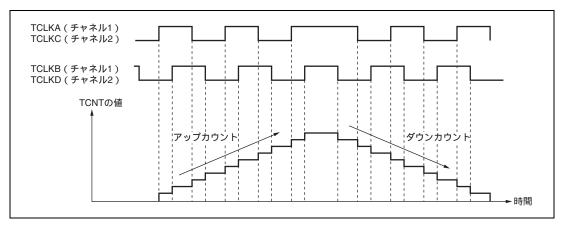

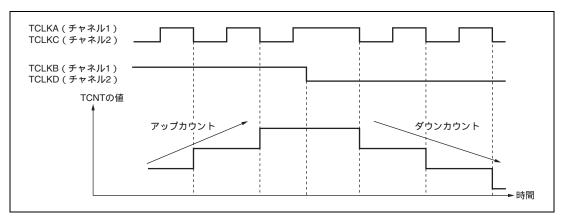

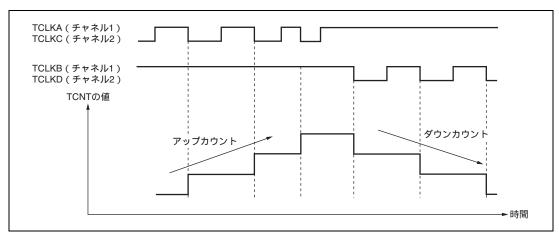

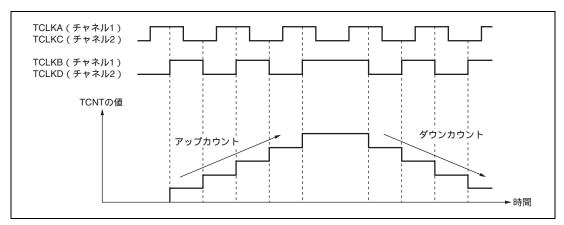

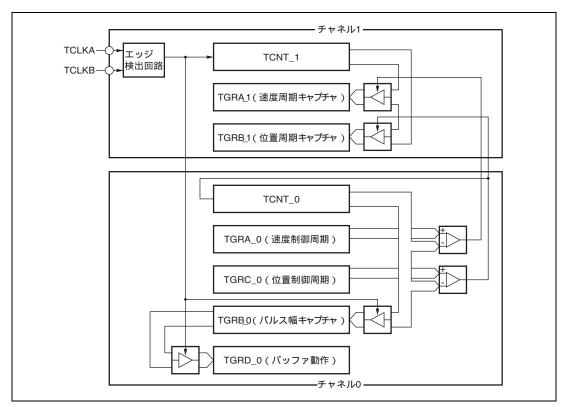

| 11.4.6 | 位相計数モード                               | 11-97  |

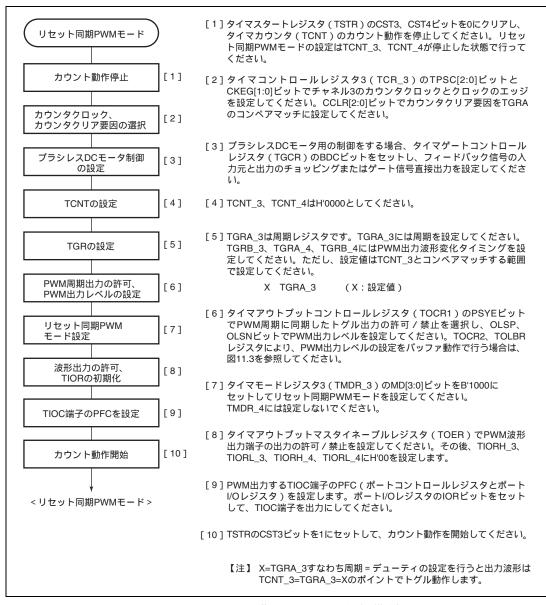

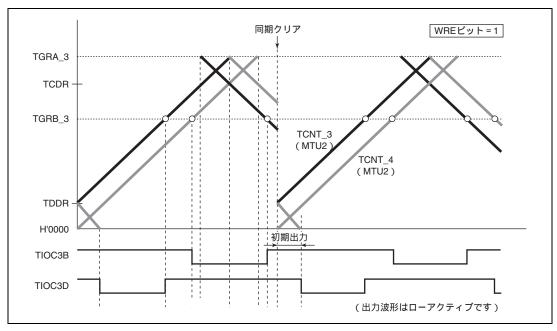

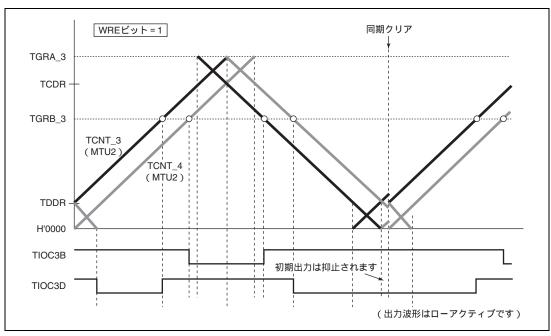

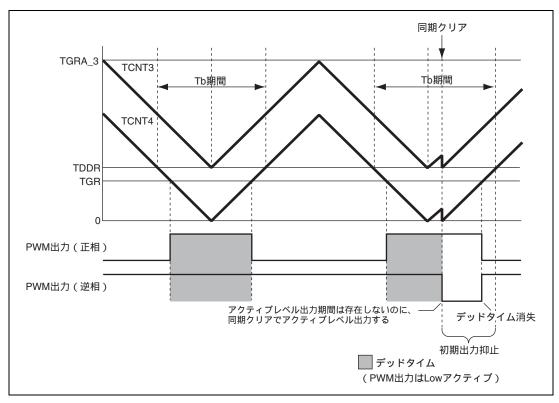

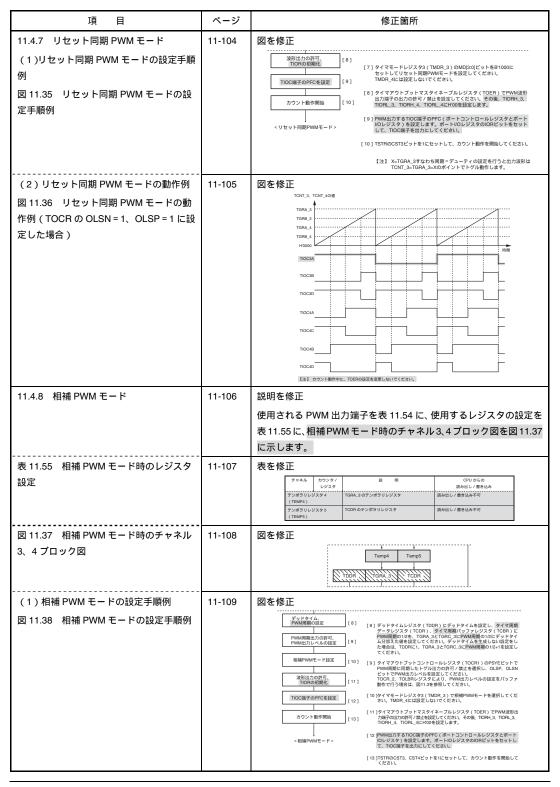

| 11.4.7 | リセット同期 PWM モード                        | 11-103 |

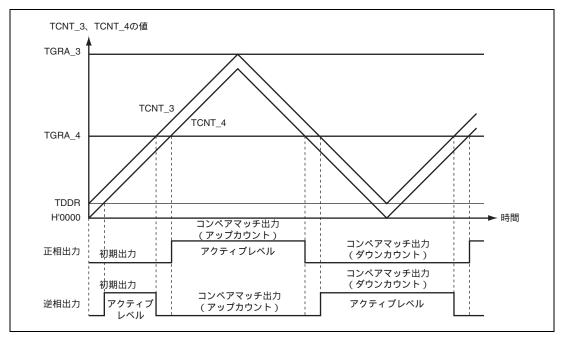

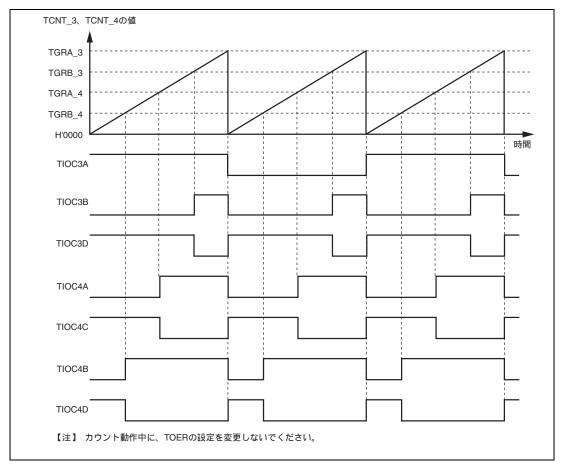

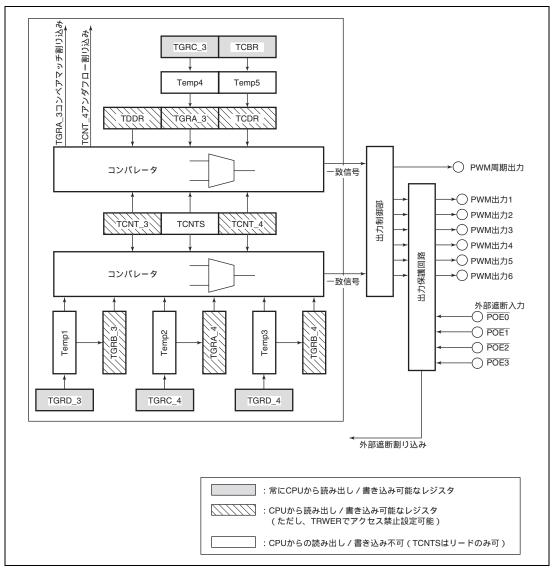

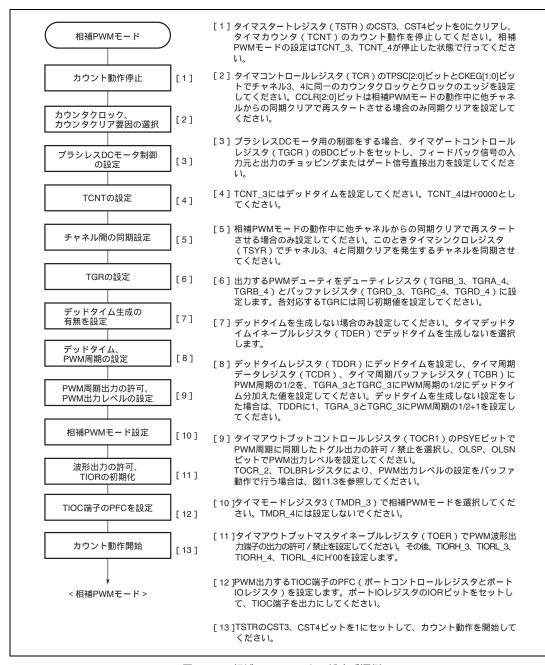

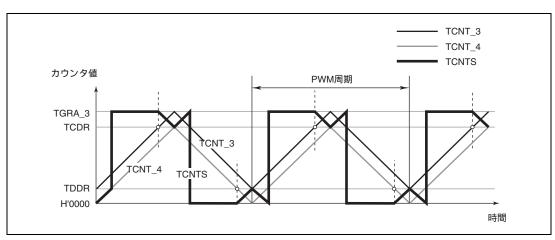

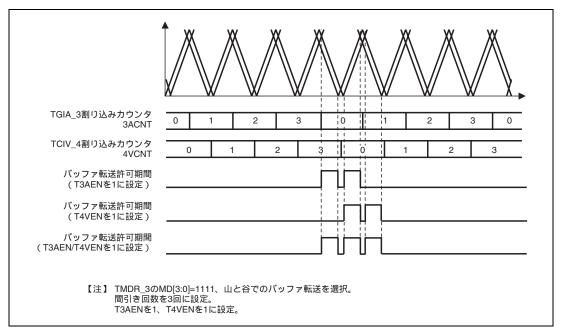

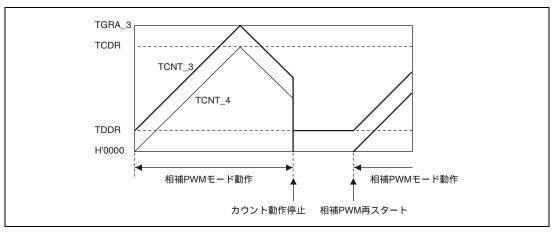

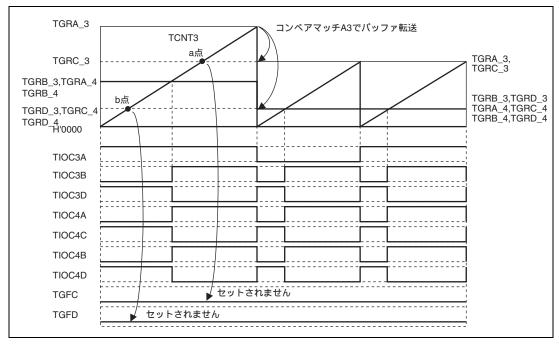

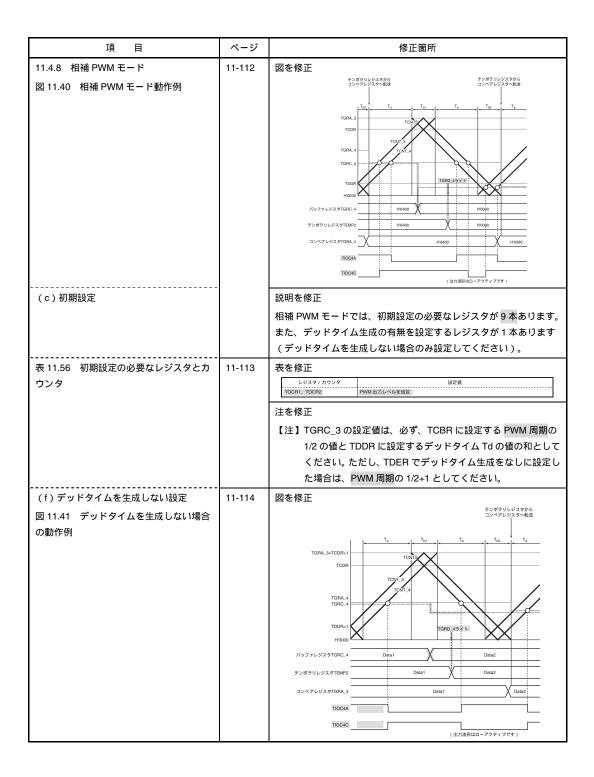

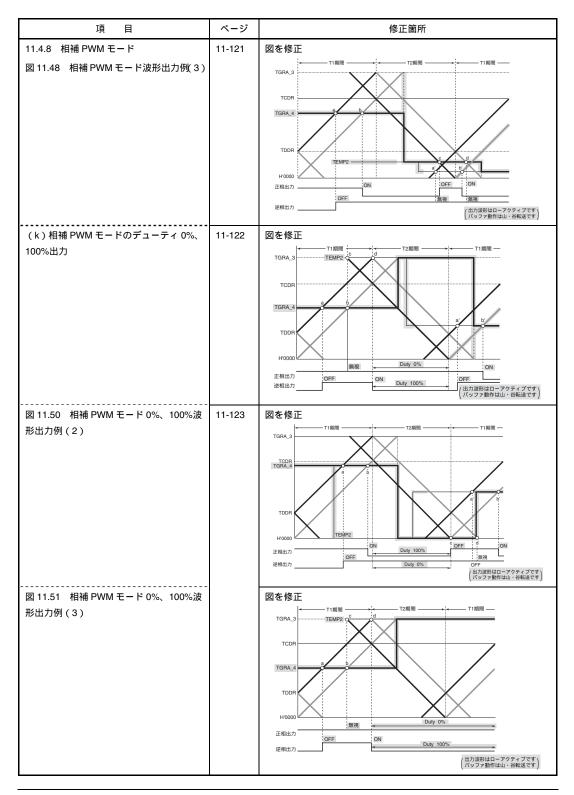

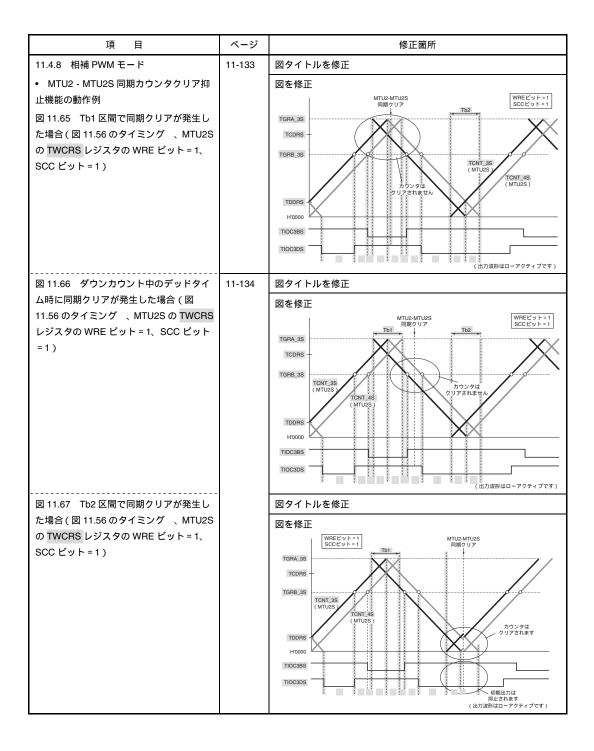

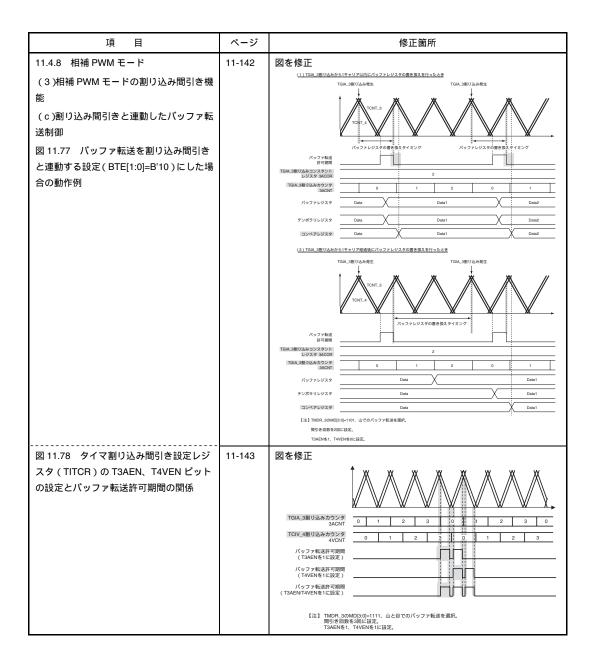

| 11.4.8 | 相補 PWM モード                            | 11-106 |

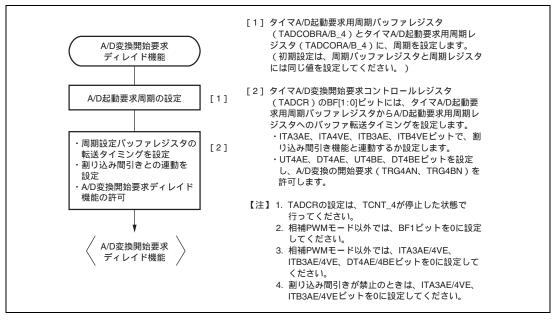

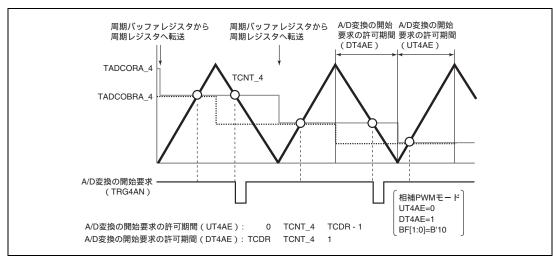

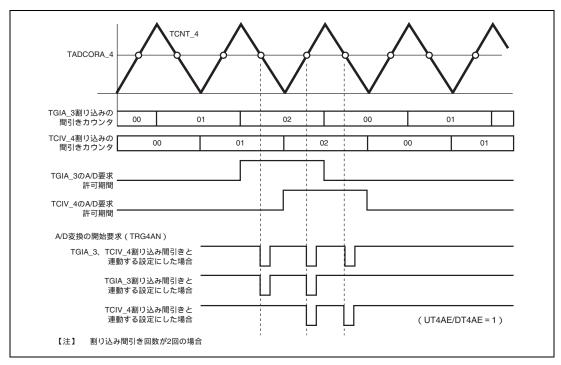

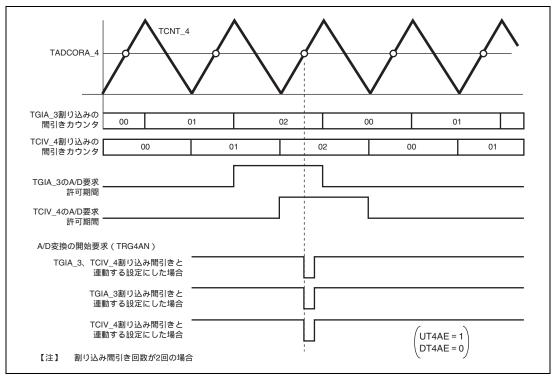

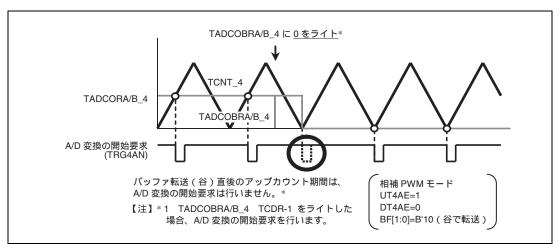

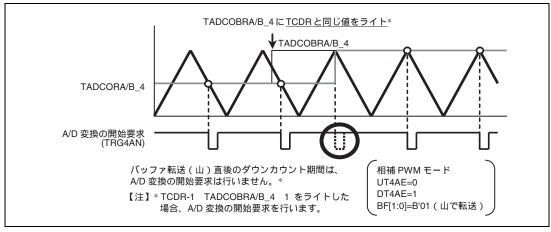

| 11.4.9 | A/D 変換開始要求ディレイド機能                     | 11-144 |

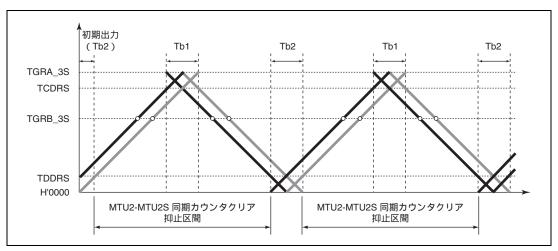

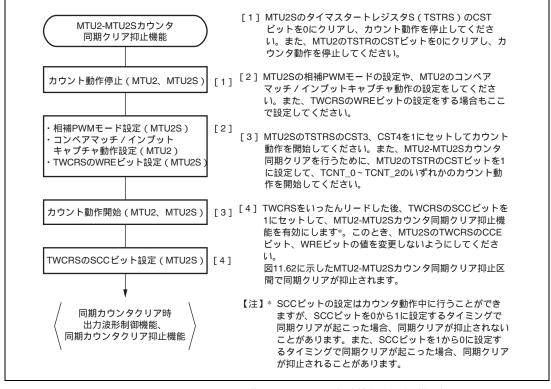

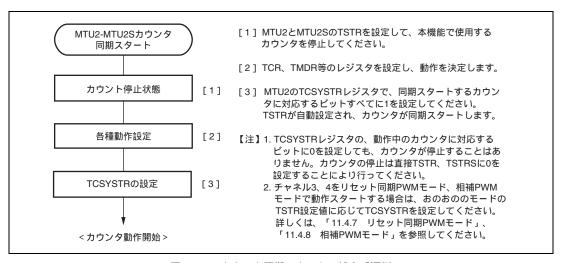

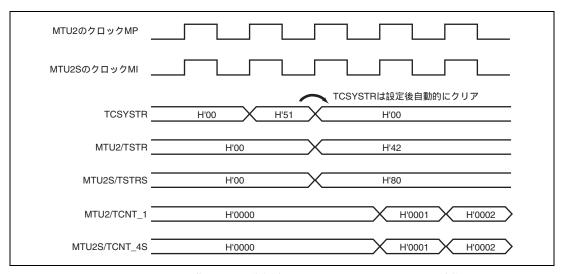

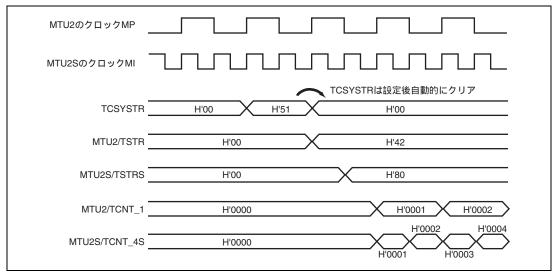

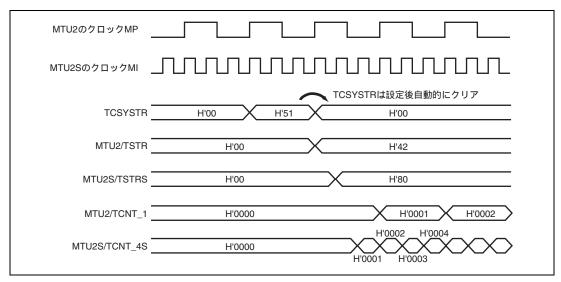

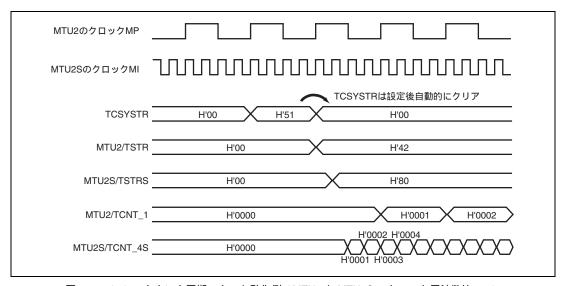

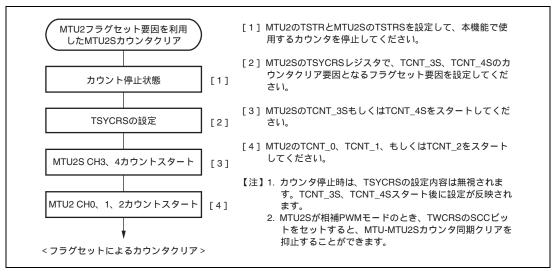

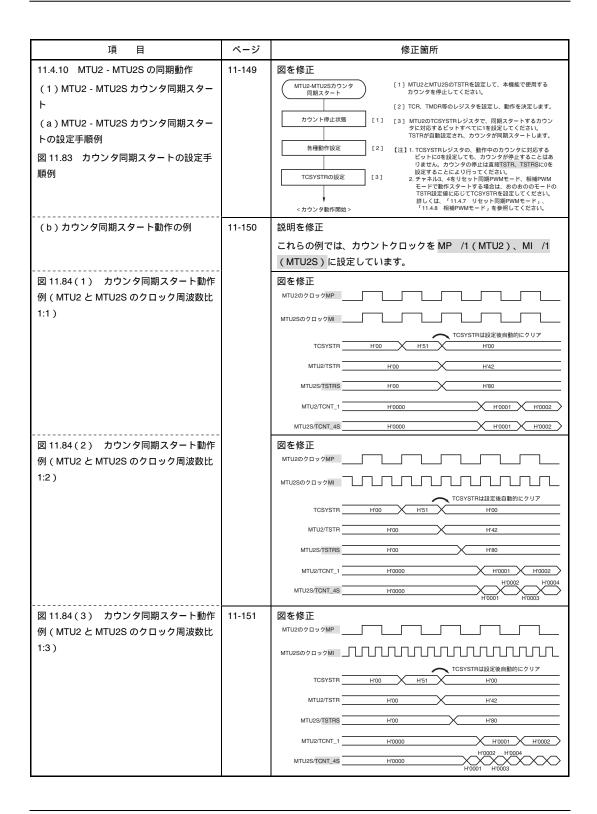

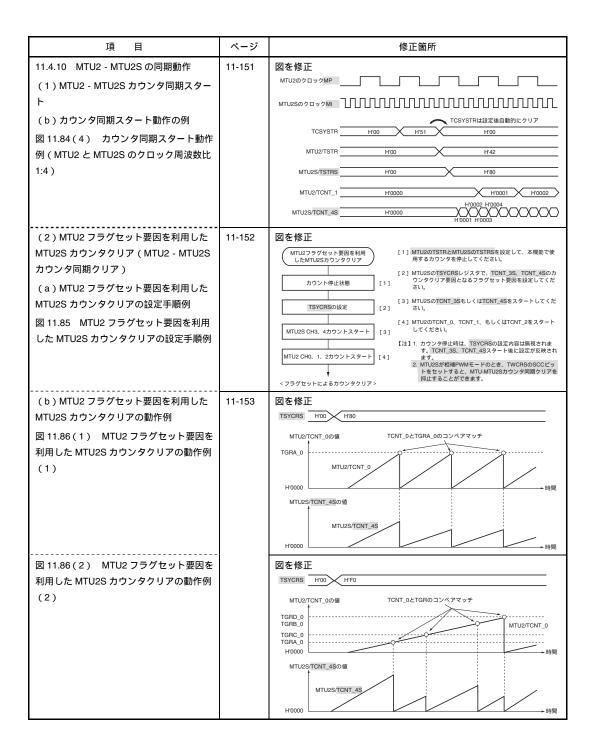

| 11.4.1 | 0 MTU2 - MTU2S の同期動作                  | 11-149 |

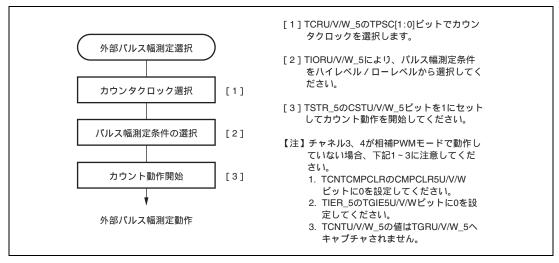

| 11.4.1 | 1 外部パルス幅測定機能                          | 11-154 |

| 11.4.1 | 2 デッドタイム補償用機能                         | 11-155 |

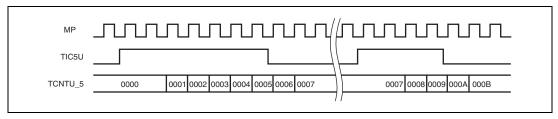

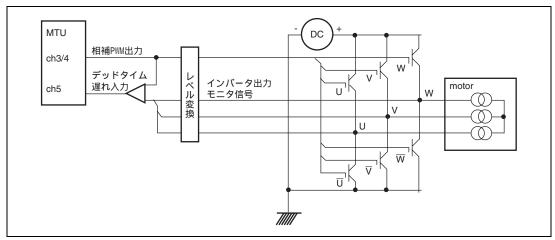

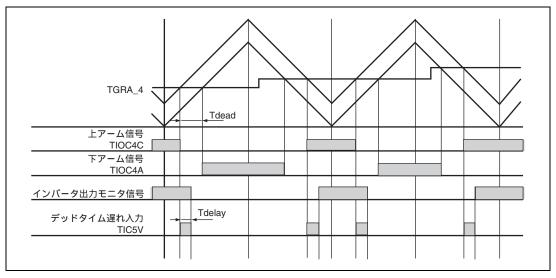

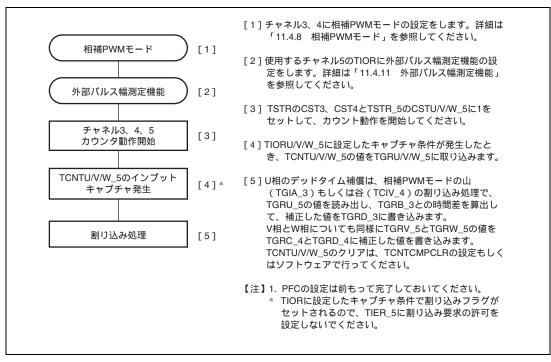

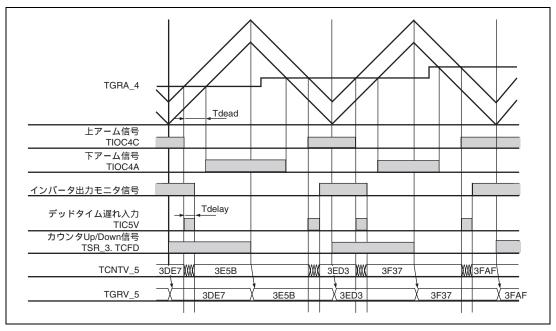

| 11.4.1 | 3 相補 PWM の「山/谷」での TCNTU/V/W_5 キャプチャ動作 | 11-157 |

| 11.5   | 割り込み要因                                | 11-158 |

| 11.5.1 | 割り込み要因と優先順位                           | 11-158 |

| 11.5.2 | DTC/DMAC の起動                          | 11-160 |

| 11.5.3 | A/D 変換器の起動                            | 11-160 |

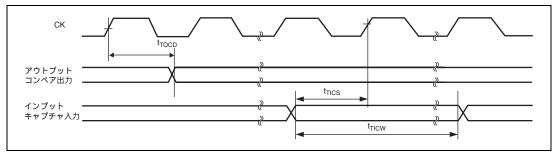

| 11.6   | 動作タイミング                               |        |

| 11.6.1 | 入出力タイミング                              |        |

| 11.6.2 | 割り込み信号タイミング                           | 11-169 |

| 11.7   | 使用上の注意事項                              | 11-175 |

| 11.7.1 | モジュールスタンバイモードの設定                      | 11-175 |

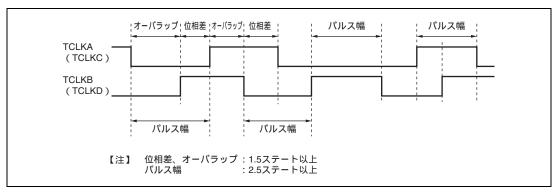

| 11.7.2 | 入力クロックの制限事項                           | 11-175 |

| 11.7.3 | 周期設定上の注意事項                            | 11-175 |

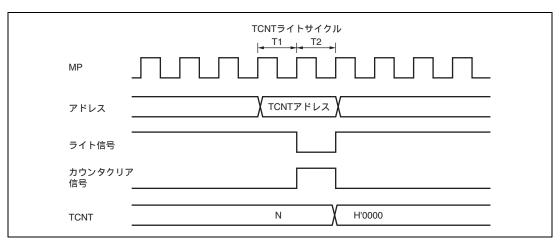

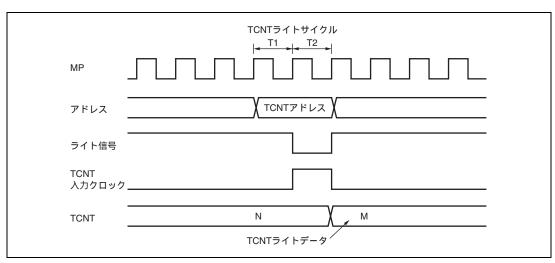

| 11.7.4 | TCNT のライトとクリアの競合                      | 11-176 |

| 11.7.5 | TCNT のライトとカウントアップの競合                  | 11-176 |

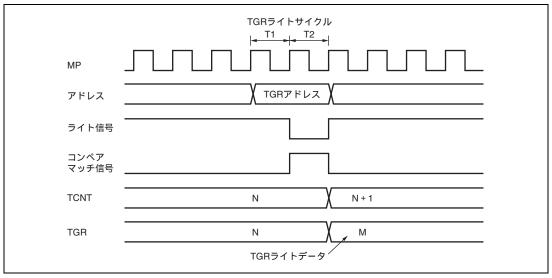

| 11.7.6 | TGR のライトとコンペアマッチの競合                   | 11-177 |

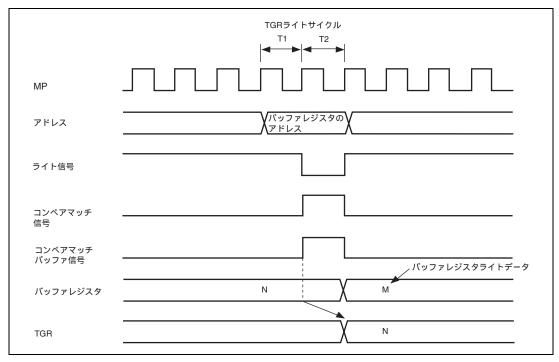

| 11.7.7 | バッファレジスタのライトとコンペアマッチの競合               | 11-178 |

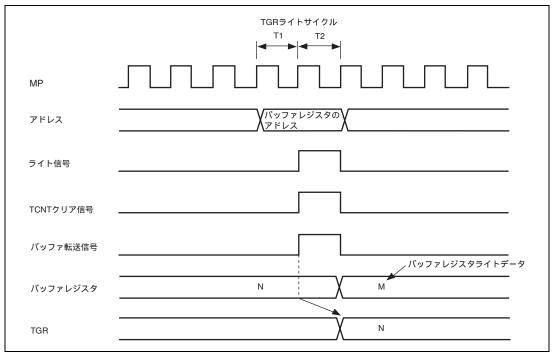

| 11.7.8  | バッファレジスタのライトと TCNT クリアの競合                            | 11-179 |

|---------|------------------------------------------------------|--------|

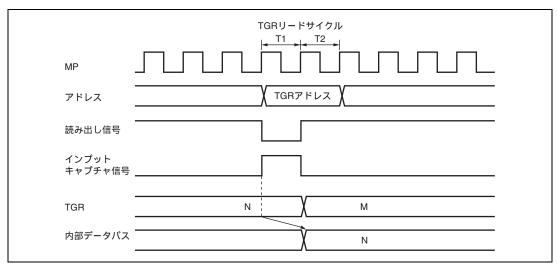

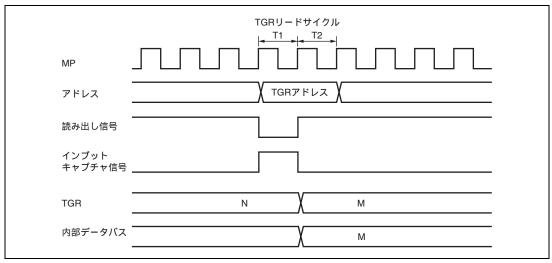

| 11.7.9  | TGR のリードとインプットキャプチャの競合                               | 11-180 |

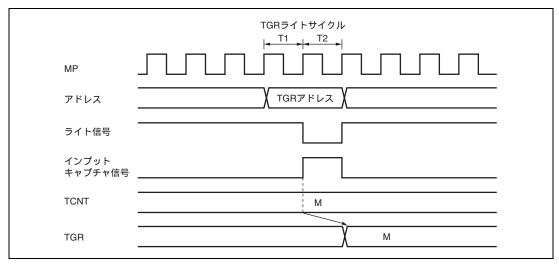

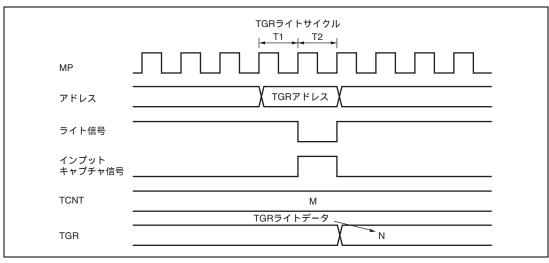

| 11.7.10 | ) TGR のライトとインプットキャプチャの競合                             | 11-181 |

| 11.7.11 | バッファレジスタのライトとインプットキャプチャの競合                           | 11-182 |

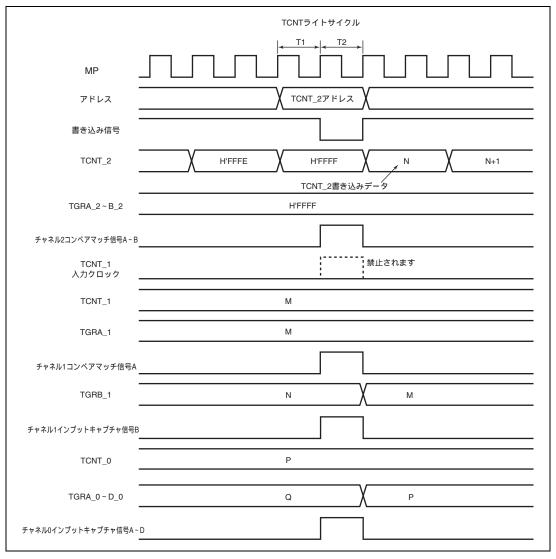

| 11.7.12 | 2 カスケード接続における TCNT_2 のライトとオーバフロー / アンダフローの競合         | 11-182 |

| 11.7.13 | 3 相補 PWM モード停止時のカウンタ値                                | 11-184 |

| 11.7.14 | 4 相補 PWM モードでのバッファ動作の設定                              | 11-184 |

| 11.7.15 | 5 リセット同期 PWM モードのバッファ動作とコンペアマッチフラグ                   | 11-185 |

| 11.7.16 | 5 リセット同期 PWM モードのオーバフローフラグ                           | 11-186 |

| 11.7.17 | 7 オーバフロー / アンダフローとカウンタクリアの競合                         | 11-187 |

| 11.7.18 | 3 TCNT のライトとオーバフロー / アンダフローの競合                       | 11-187 |

| 11.7.19 | ) 通常動作または PWM モード 1 からリセット同期 PWM モードへ遷移する場合の<br>注意事項 | 11-188 |

| 11.7.20 |                                                      |        |

| 11.7.21 |                                                      |        |

| 11.7.22 |                                                      |        |

| 11.7.23 | - ー ー ー ー ー ー ー ー ー ー ー ー ー ー ー ー ー ー ー              | 11-189 |

| 11.7.24 |                                                      |        |

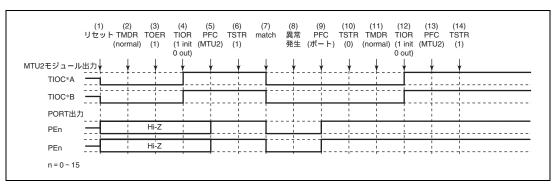

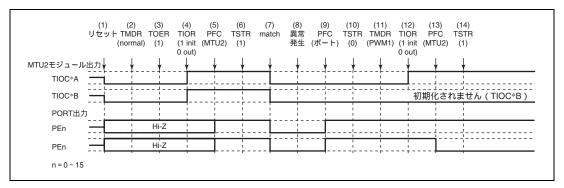

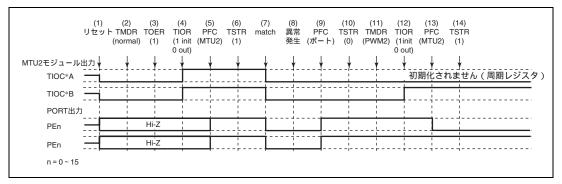

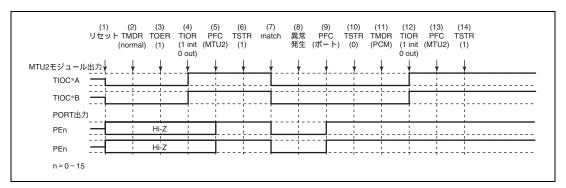

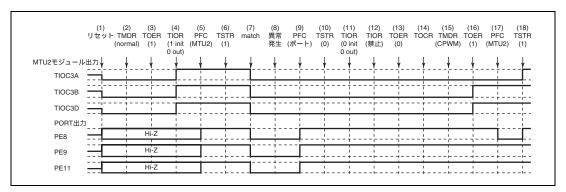

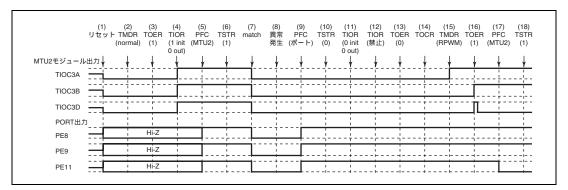

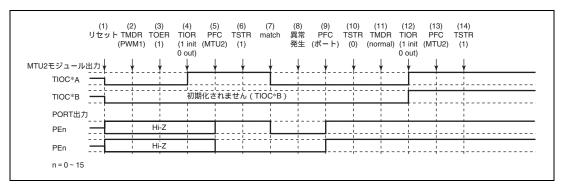

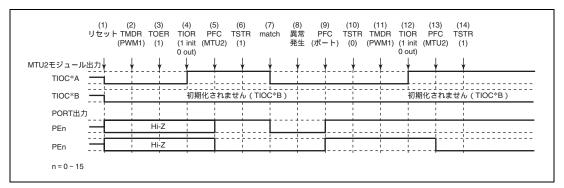

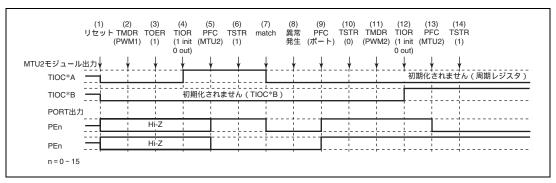

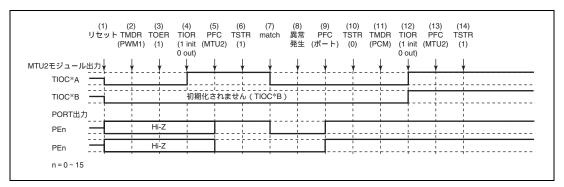

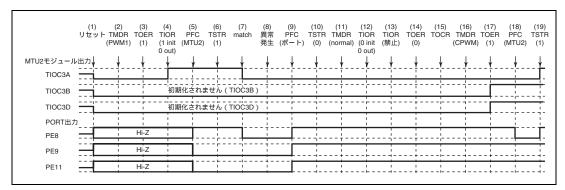

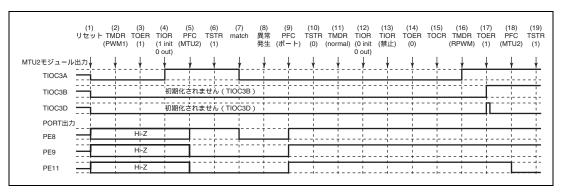

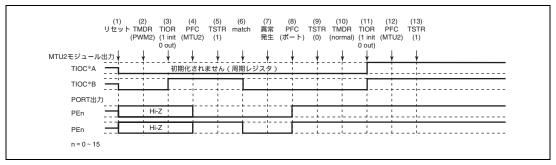

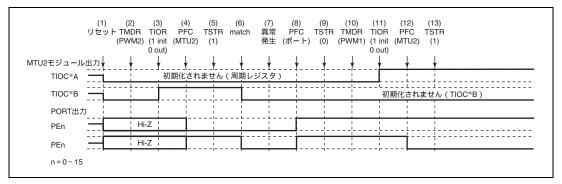

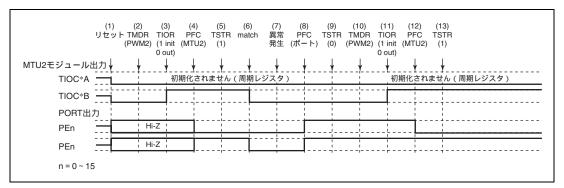

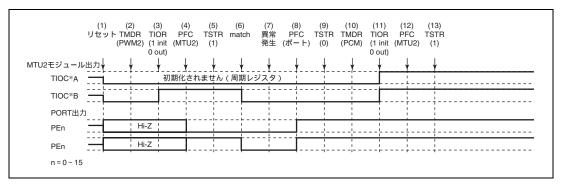

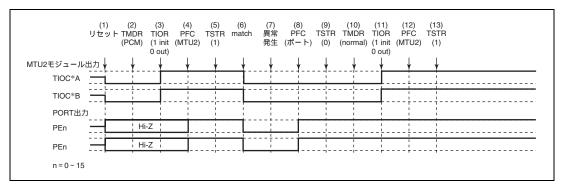

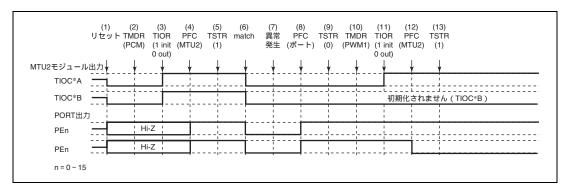

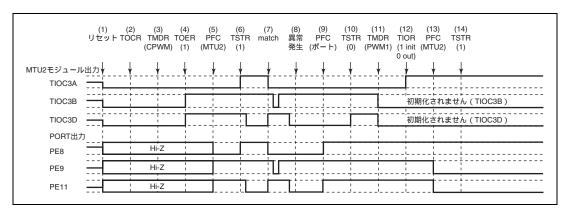

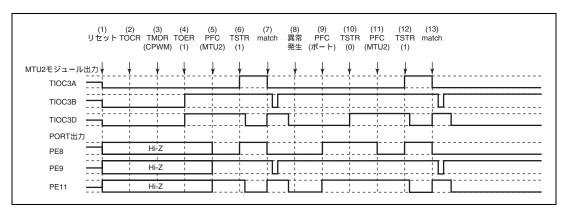

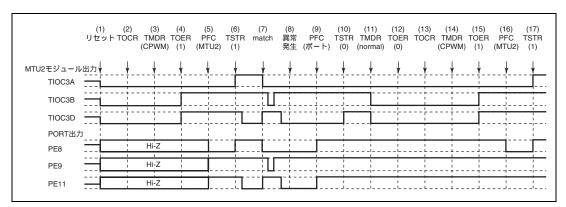

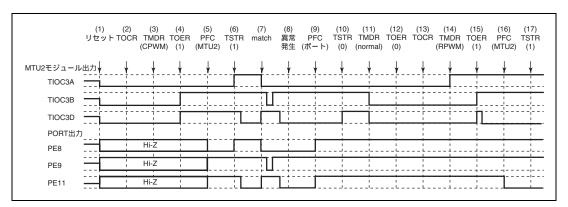

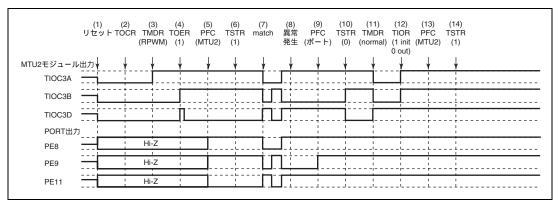

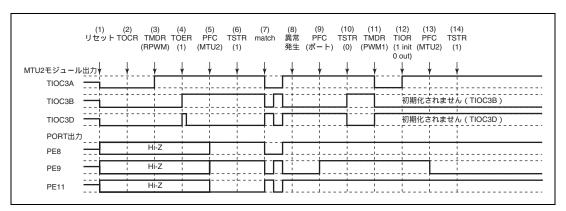

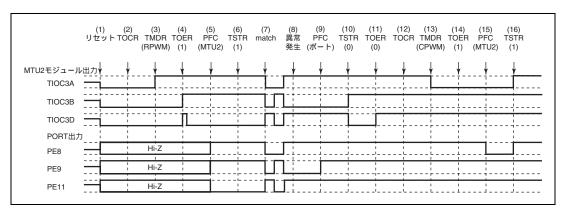

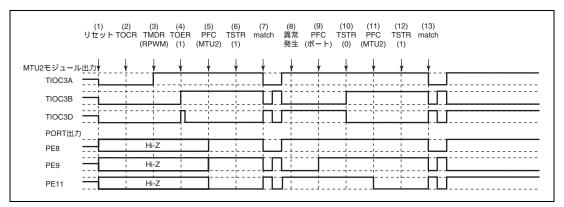

| 11.8    | MTU2出力端子の初期化方法                                       | 11-192 |

| 11.8.1  | 動作モード                                                | 11-192 |

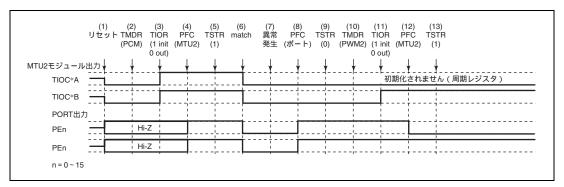

| 11.8.2  | リセットスタート時の動作                                         | 11-192 |

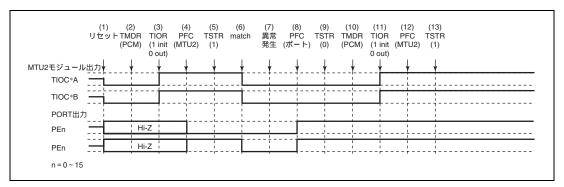

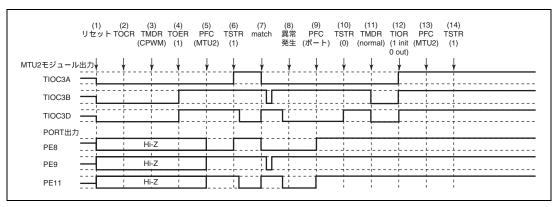

| 11.8.3  | 動作中の異常などによる再設定時の動作                                   | 11-193 |

| 11.8.4  | 動作中の異常などによる端子の初期化手順、モード遷移の概要                         | 11-193 |

| 12. マル  | ・チファンクションタイマパルスユニット 2S(MTU2S)                        | 12-1   |

| 12.1    | 入出力端子                                                | 12-3   |

| 12.2    | レジスタの説明                                              | 12-4   |

|         |                                                      |        |

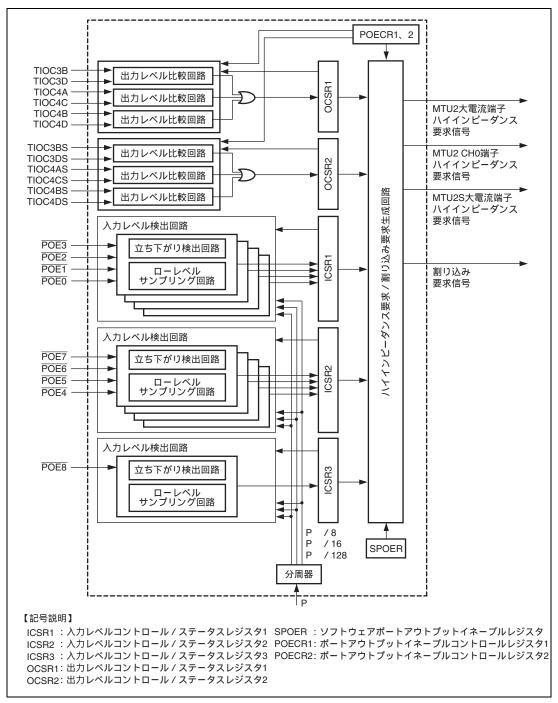

| 13. ポー  | - トアウトプットイネーブル(POE)                                  | 13-1   |

| 13.1    | 特長                                                   | 13-1   |

| 13.2    | 入出力端子                                                | 13-3   |

| 13.3    | レジスタの説明                                              | 13-4   |

| 13.3.1  | 入力レベルコントロール / ステータスレジスタ 1(ICSR1)                     | 13-4   |

| 13.3.2  | 出力レベルコントロール / ステータスレジスタ 1 ( OCSR1 )                  | 13-7   |

| 13.3.3  | 入力レベルコントロール / ステータスレジスタ 2(ICSR2)                     | 13-8   |

| 13.3.4  | 出力レベルコントロール / ステータスレジスタ 2 ( OCSR2 )                  | 13-11  |

| 13.3.5  | 入力レベルコントロール / ステータスレジスタ 3(ICSR3)                     | 13-12  |

| 13.3.6  | ソフトウェアポートアウトプットイネーブルレジスタ ( SPOER )                   | 13-13  |

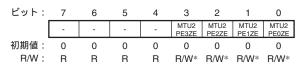

| 13.3.7  | ポートアウトプットイネーブルコントロールレジスタ 1 ( POECR1 )                | 13-14  |

| 13.3.8  | ポートアウトプットイネーブルコントロールレジスタ 2 ( POECR2 )                | 13-15  |

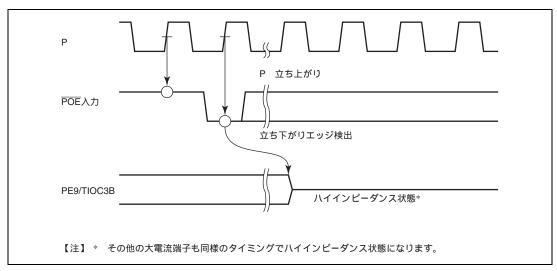

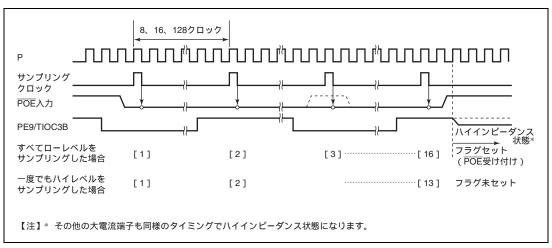

| 13.4    | 動作説明                                                 | 13-19  |

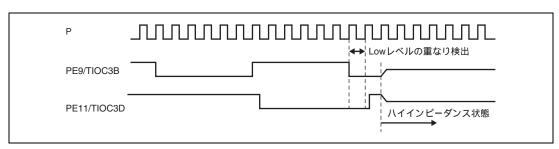

| 13.4.1  | 入力レベル検出動作                           | 13-20 |

|---------|-------------------------------------|-------|

| 13.4.2  | 出力レベル比較動作                           | 13-21 |

| 13.4.3  | ハイインピーダンス状態からの解除                    | 13-22 |

| 13.5    | 割り込み                                | 13-23 |

| 13.6    | 使用上の注意事項                            | 13-24 |

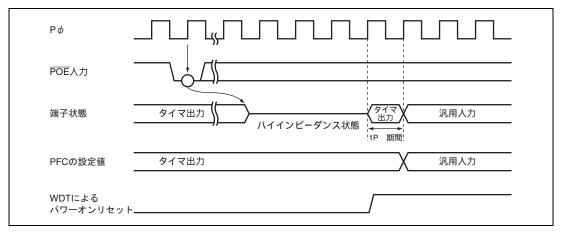

| 13.6.1  | ウォッチドッグタイマからパワーオンリセットが発行されたときの端子状態  | 13-24 |

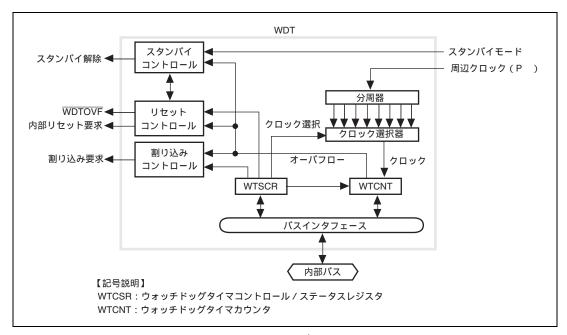

| 14. ウォ  | ・ッチドッグタイマ(WDT)                      | 14-1  |

| 14.1    | 特長                                  | 14-1  |

| 14.2    | 入出力端子                               | 14-3  |

| 14.3    | レジスタの説明                             | 14-4  |

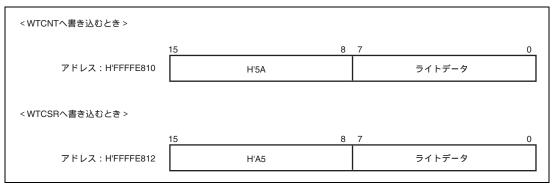

| 14.3.1  | ウォッチドッグタイマカウンタ(WTCNT)               | 14-4  |

| 14.3.2  | ウォッチドッグタイマコントロール / ステータスレジスタ(WTCSR) | 14-5  |

| 14.3.3  | レジスタアクセス時の注意                        | 14-7  |

| 14.4    | 動作説明                                | 14-8  |

| 14.4.1  | ソフトウェアスタンバイ解除の手順                    | 14-8  |

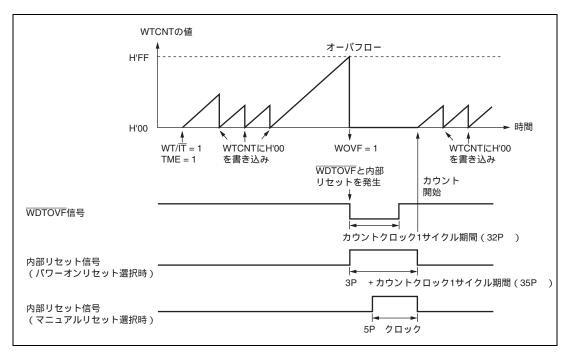

| 14.4.2  | ウォッチドッグタイマモードの使用法                   | 14-8  |

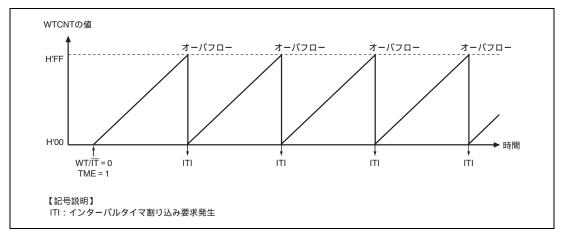

| 14.4.3  | インターバルタイマモードの使用法                    | 14-10 |

| 14.5    | 割り込み要因                              | 14-11 |

| 14.6    | 使用上の注意事項                            | 14-11 |

| 14.6.1  | WTCNT の設定値                          | 14-11 |

| 14.6.2  | タイマ誤差                               | 14-11 |

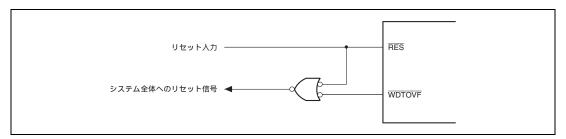

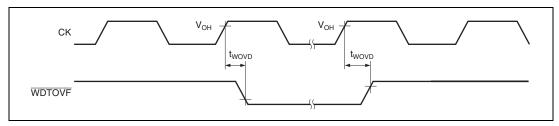

| 14.6.3  | WDTOVF 信号によるシステムリセット                | 14-11 |

| 14.6.4  | ウォッチドッグタイマモードのマニュアルリセット             | 14-12 |

| 14.6.5  | ウォッチドッグタイマモードでの内部リセット               | 14-12 |

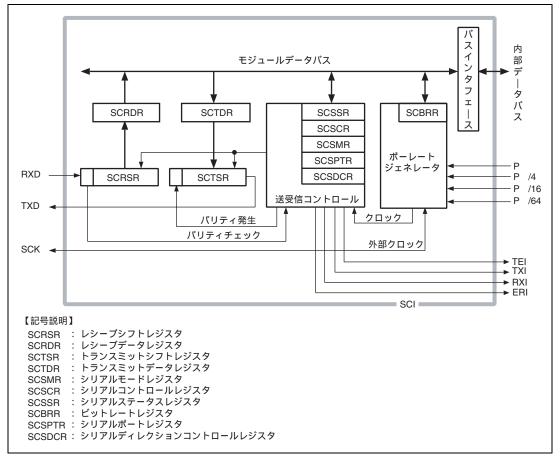

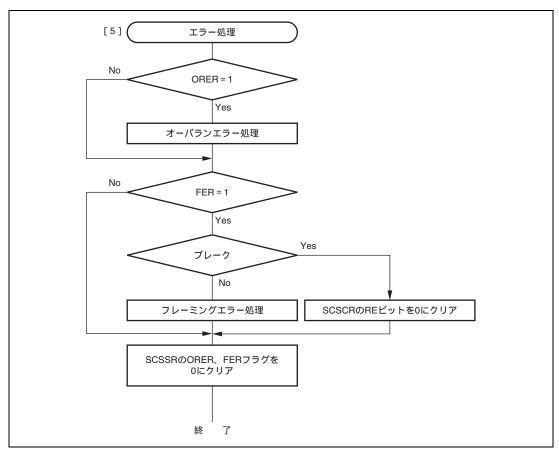

| 15. シリ  | アルコミュニケーションインタフェース (SCI)            | 15-1  |

| 15.1    | 特長                                  | 15-1  |

| 15.2    | 入出力端子                               | 15-4  |

| 15.3    | レジスタの説明                             | 15-5  |

| 15.3.1  | レシープシフトレジスタ ( SCRSR )               | 15-6  |

| 15.3.2  | レシープデータレジスタ(SCRDR)                  | 15-6  |

| 15.3.3  | トランスミットシフトレジスタ(SCTSR)               | 15-6  |

| 15.3.4  | トランスミットデータレジスタ(SCTDR)               | 15-7  |

| 15.3.5  | シリアルモードレジスタ ( SCSMR )               | 15-7  |

| 15.3.6  | シリアルコントロールレジスタ ( SCSCR )            | 15-9  |

| 15.3.7  | シリアルステータスレジスタ(SCSSR)                | 15-12 |

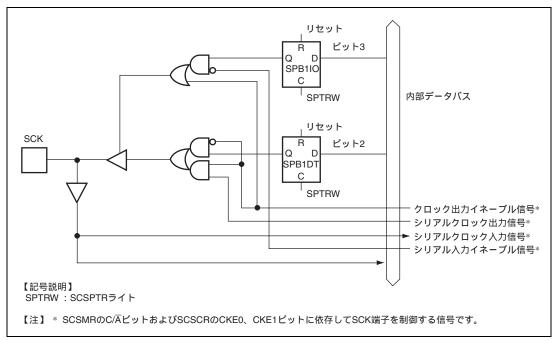

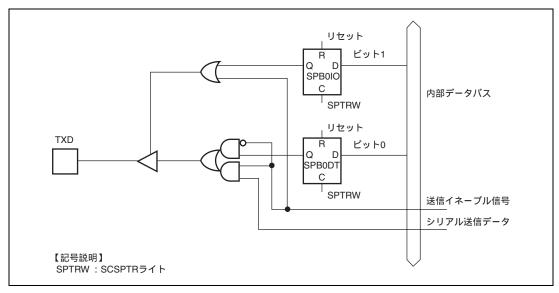

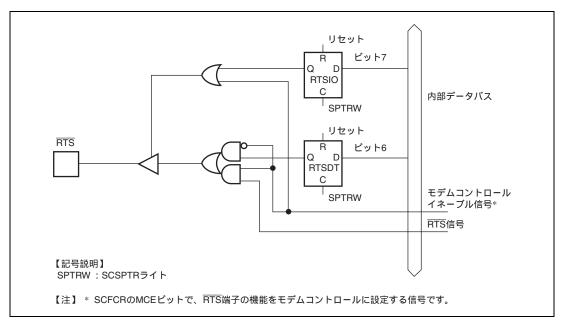

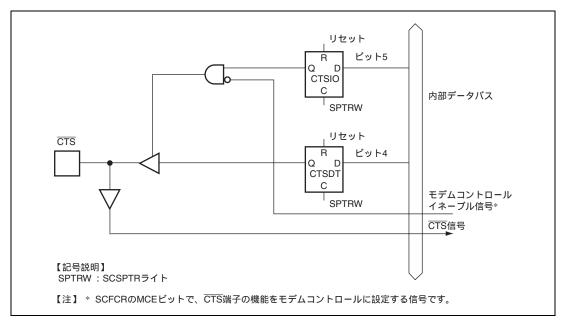

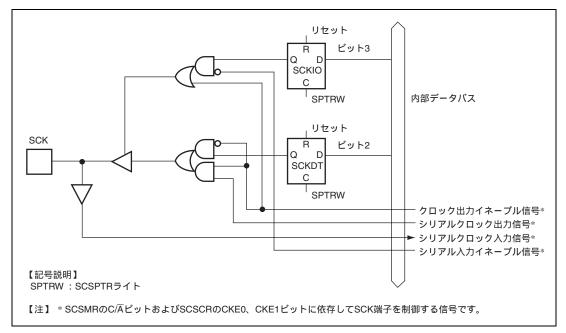

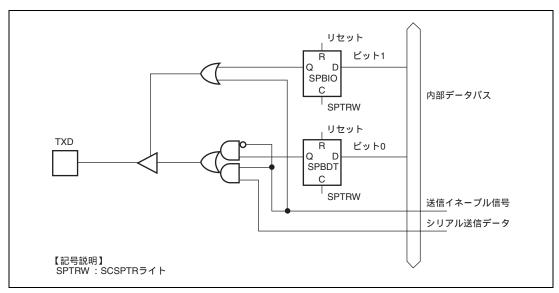

| 15.3.8  | シリアルポートレジスタ(SCSPTR)                 | 15-16 |

| 15.3.9  | シリアルディレクションコントロールレジスタ(SCSDCR)       | 15-17 |

| 15.3.10 | ) ビットレートレジスタ ( SCBRR )              | 15-18 |

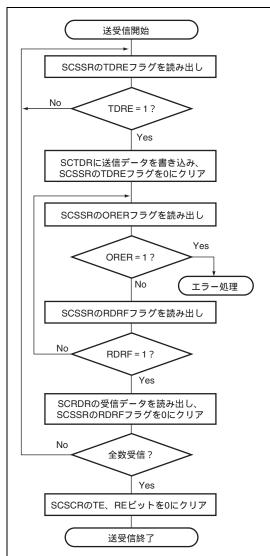

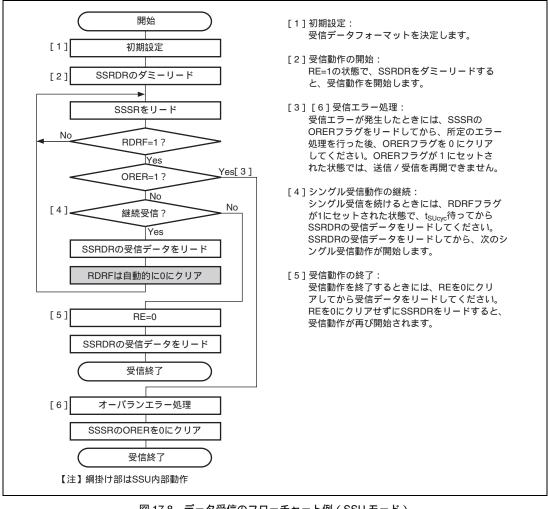

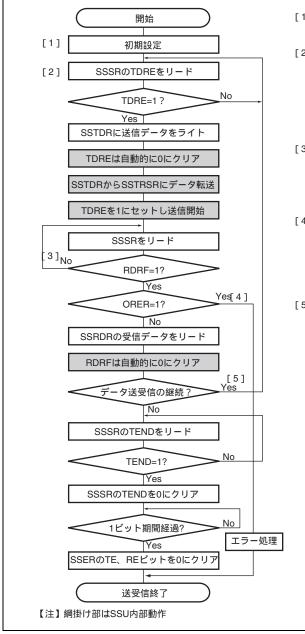

| 15.4    | 動作説明                                | 15-27 |

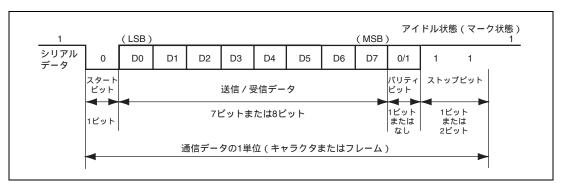

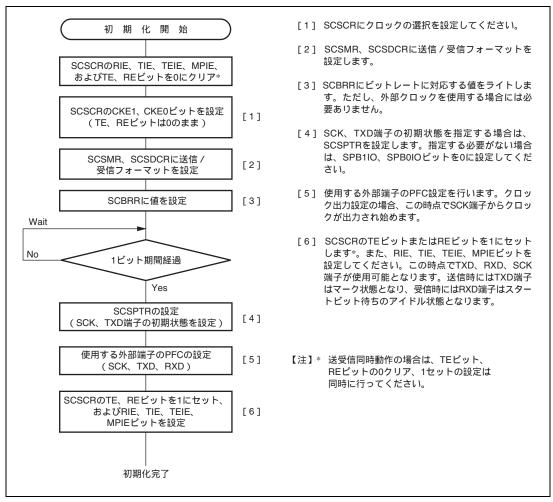

| 15.4.1           | 概要                                                  | 15-27 |

|------------------|-----------------------------------------------------|-------|

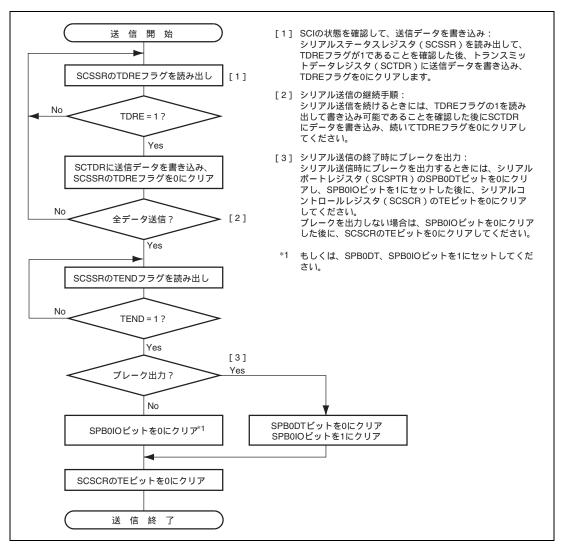

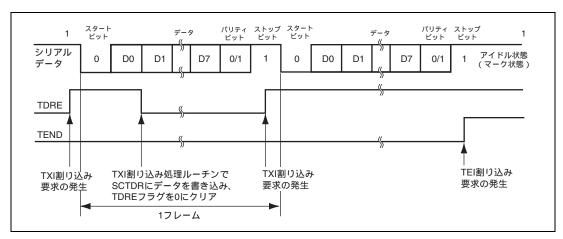

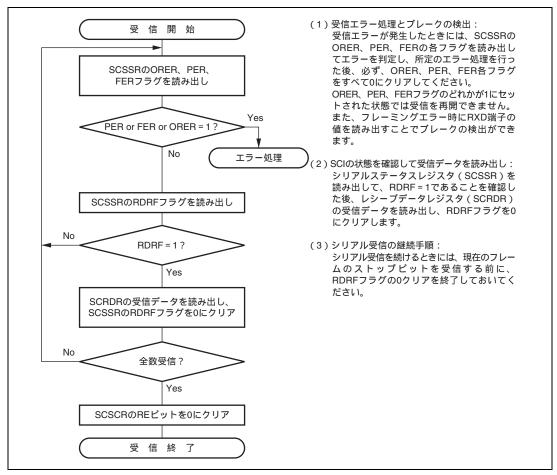

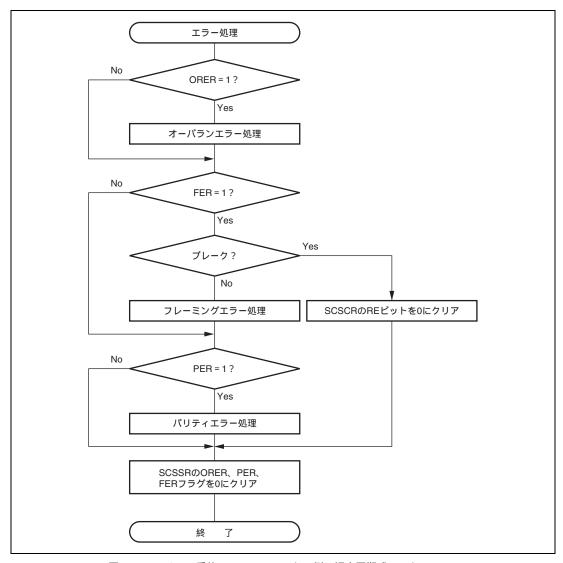

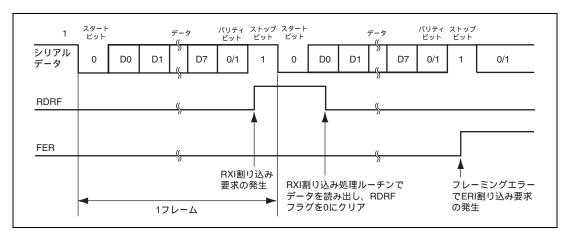

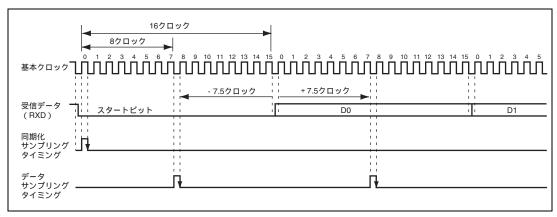

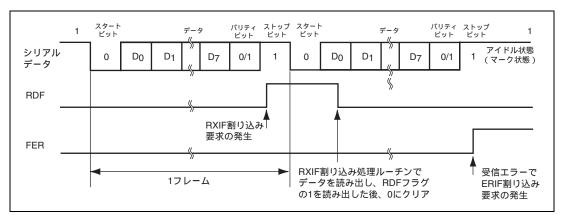

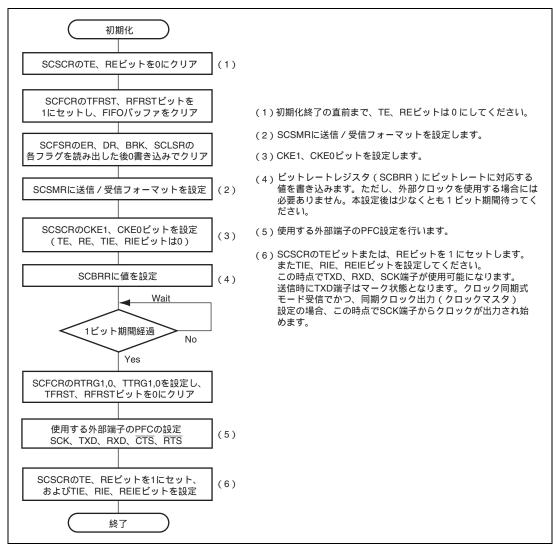

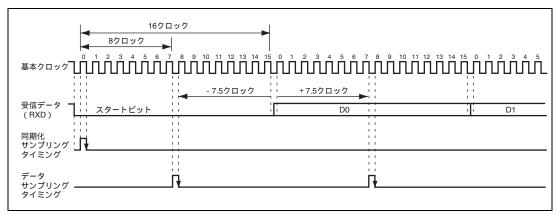

| 15.4.2           | 調歩同期式モード時の動作                                        | 15-29 |

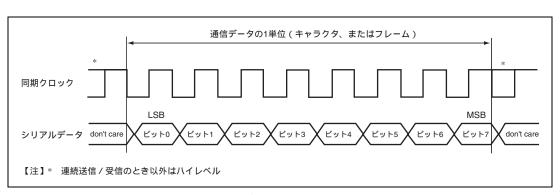

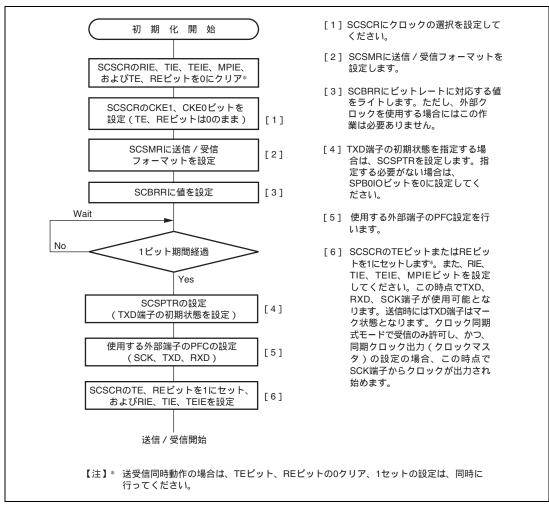

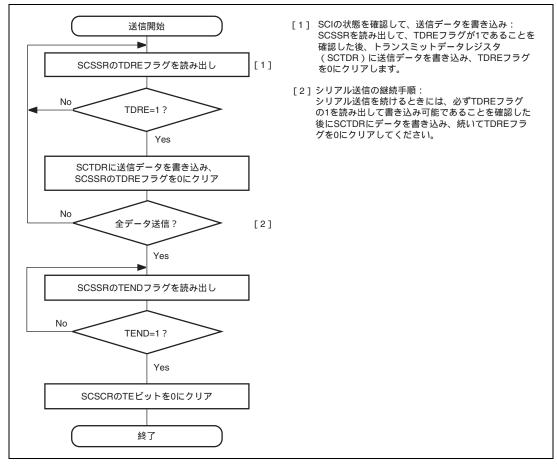

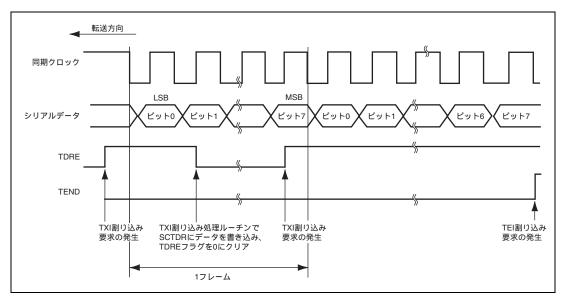

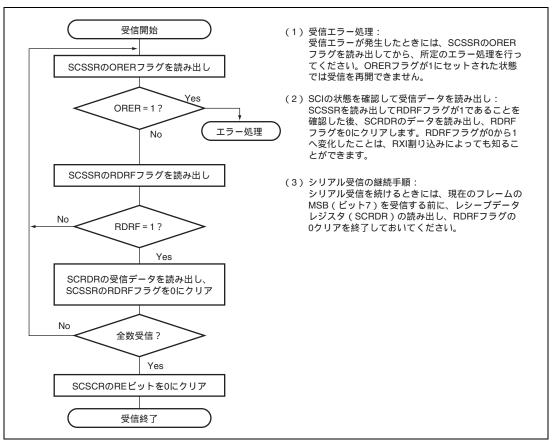

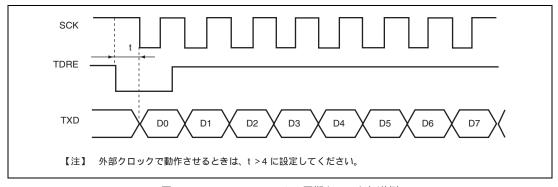

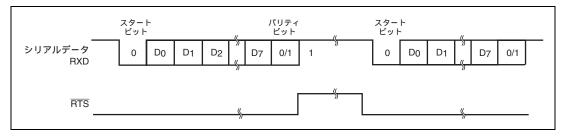

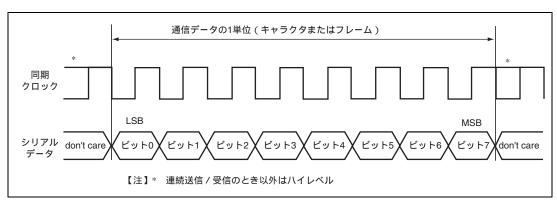

| 15.4.3           | クロック同期式モード時の動作                                      | 15-38 |

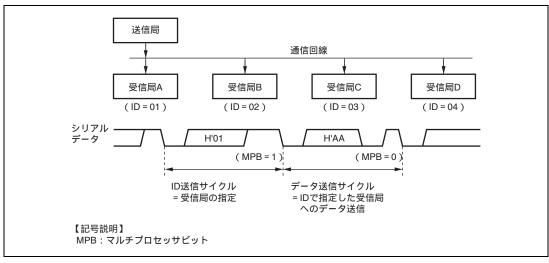

| 15.4.4           | マルチプロセッサ通信機能                                        | 15-47 |

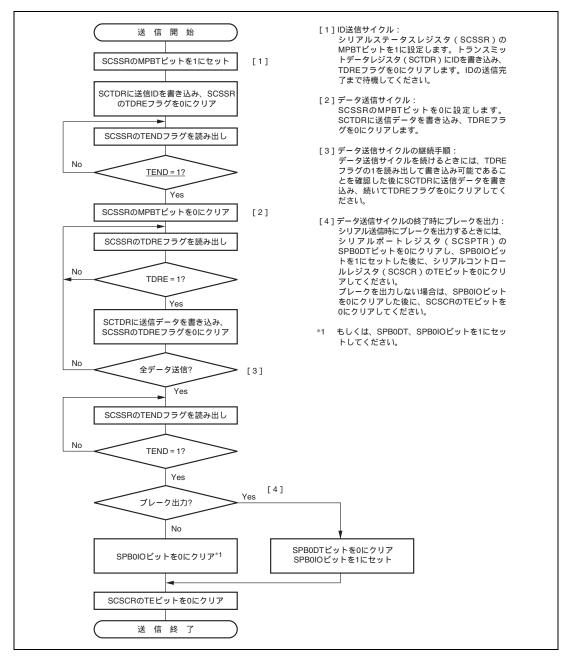

| 15.4.5           | マルチプロセッサシリアルデータ送信                                   | 15-48 |

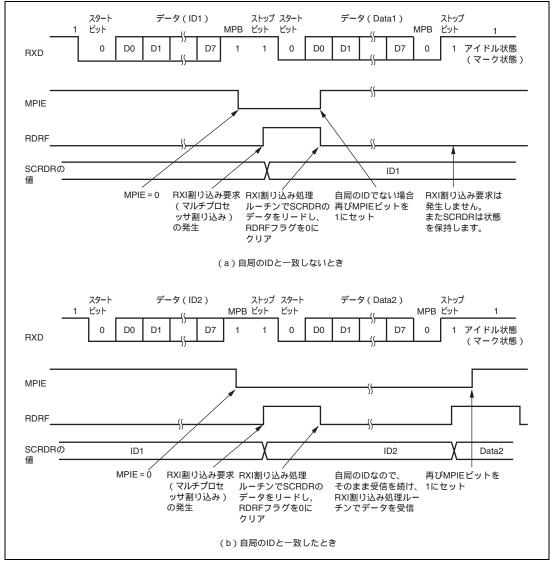

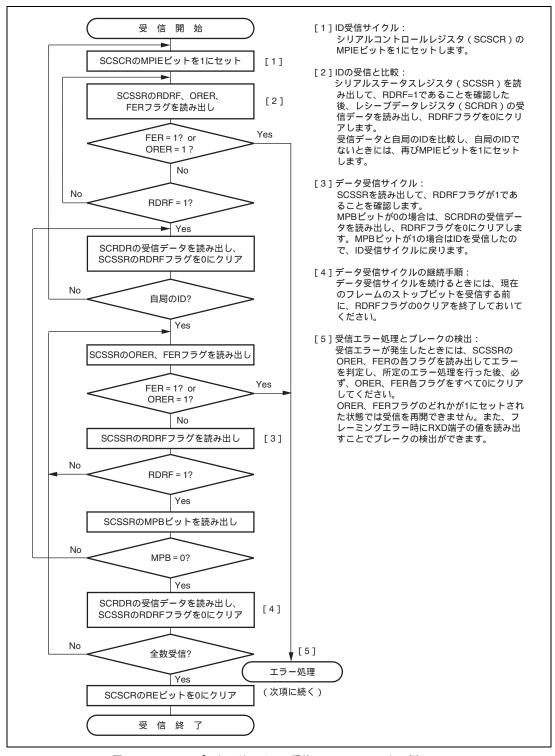

| 15.4.6           | マルチプロセッサシリアルデータ受信                                   | 15-49 |

| 15.5             | 割り込み要因とDMAC/DTC                                     | 15-52 |

| 15.6             | シリアルポートレジスタ (SCSPTR) とSCI端子との関係                     | 15-54 |

| 15.7             | 使用上の注意事項                                            | 15-55 |

| 15.7.1           | SCTDR への書き込みと TDRE フラグの関係について                       | 15-55 |

| 15.7.2           | 複数の受信エラーが同時に発生した場合の動作について                           | 15-55 |

| 15.7.3           | ブレークの検出と処理について                                      | 15-56 |

| 15.7.4           | ブレークの送り出し                                           | 15-56 |

| 15.7.5           | 調歩同期式モードの受信データサンプリングタイミングと受信マージン                    | 15-56 |

| 15.7.6           | DMAC/DTC 使用上の注意事項                                   | 15-57 |

| 15.7.7           | クロック同期外部クロックモード時の注意事項                               | 15-58 |

| 15.7.8           | モジュールスタンバイモードの設定                                    | 15-58 |

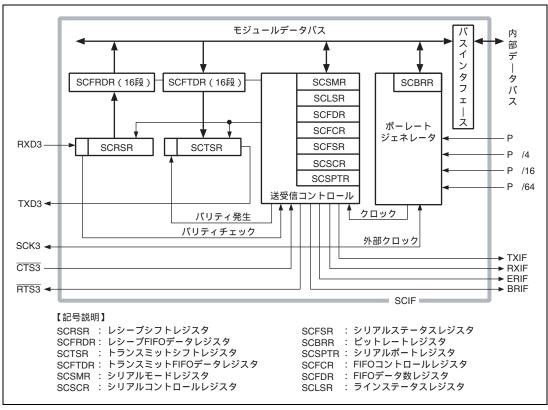

| 16 EIE           | O付きシリアルコミュニケーション インタフェース(SCIF)                      | 16-1  |

|                  |                                                     |       |

| 16.1             | 特長                                                  |       |

| 16.2             | 入出力端子                                               |       |

| 16.3             | レジスタの説明                                             |       |

| 16.3.1           | レシープシフトレジスタ (SCRSR)                                 |       |

| 16.3.2           | レシープ FIFO データレジスタ(SCFRDR)                           |       |

| 16.3.3           | トランスミットシフトレジスタ(SCTSR)                               |       |

| 16.3.4           | トランスミット FIFO データレジスタ ( SCFTDR )                     |       |

| 16.3.5           | シリアルモードレジスタ(SCSMR)シリアルコントロールレジスタ(SCSCR)             |       |

| 16.3.6<br>16.3.7 | シリアルコントロールレシスタ ( SCSCR )<br>シリアルステータスレジスタ ( SCFSR ) |       |

| 16.3.8           | ビットレートレジスタ ( SCBRR )                                |       |

| 16.3.9           | FIFO コントロールレジスタ ( SCFCR )                           |       |

| 16.3.10          |                                                     |       |

| 16.3.11          |                                                     |       |

| 16.3.12          |                                                     |       |

| 16.4             | 動作説明                                                |       |

| 16.4.1           | 概要                                                  |       |

| 16.4.2           | 調歩同期式モード時の動作                                        |       |

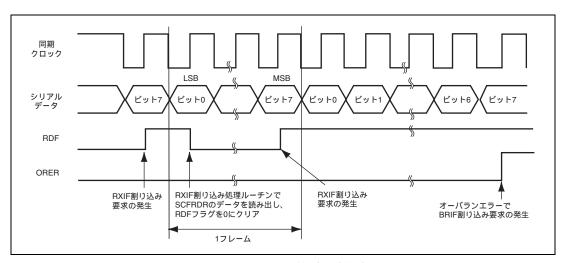

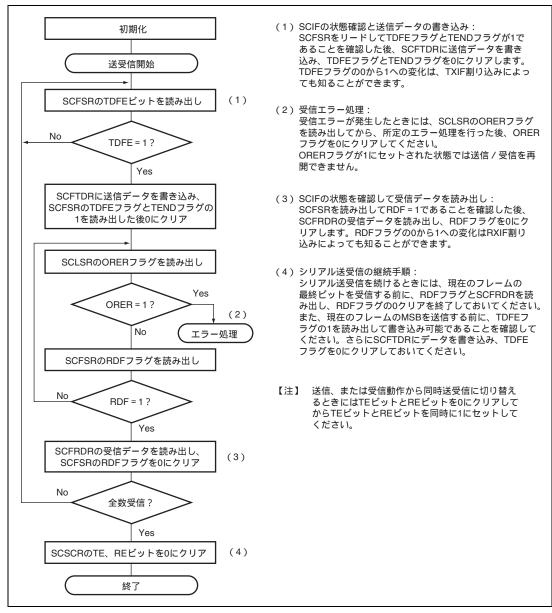

| 16.4.3           | クロック同期式モード時の動作                                      |       |

| 16.5             | SCIFの割り込み要因とDTC                                     |       |

| 16.6             | シリアルポートレジスタ ( SCSPTR ) とSCIF端子との関係                  |       |

| 16.7             | 使用上の注意事項                                            |       |

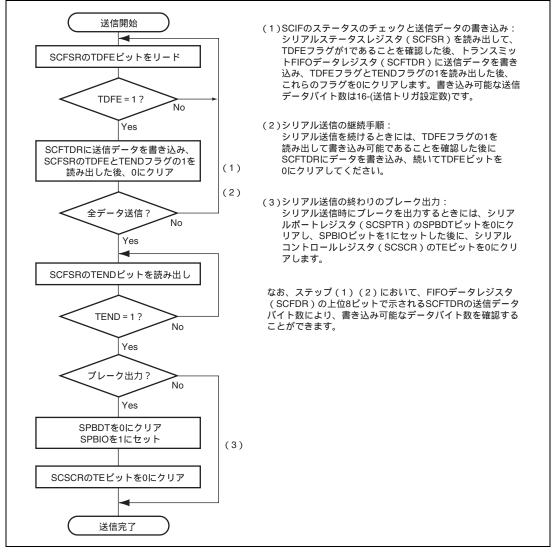

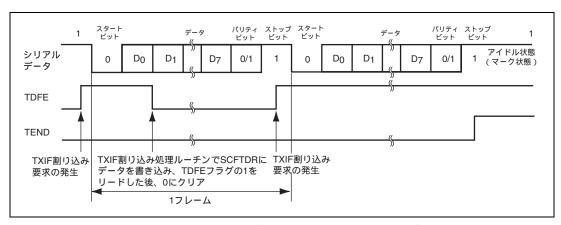

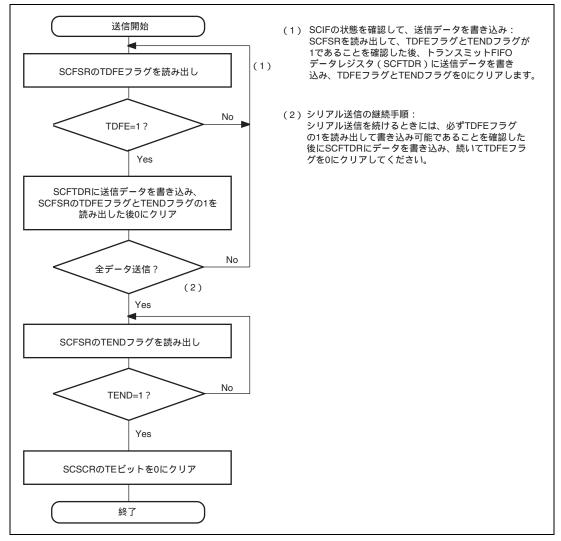

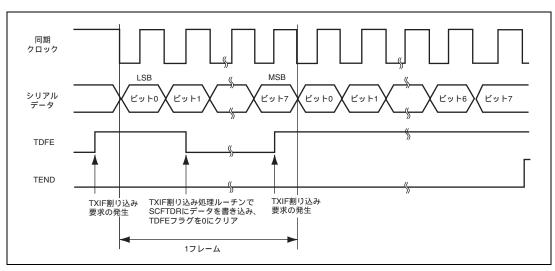

| 16.7.1               | SCFTDR への書き込みと TDFE フラグについて                  | 16-52 |

|----------------------|----------------------------------------------|-------|

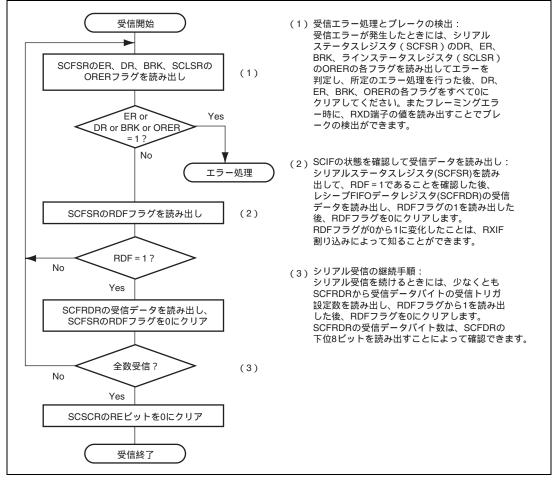

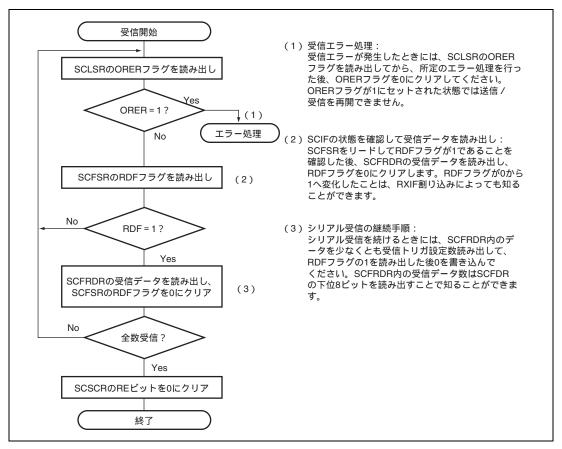

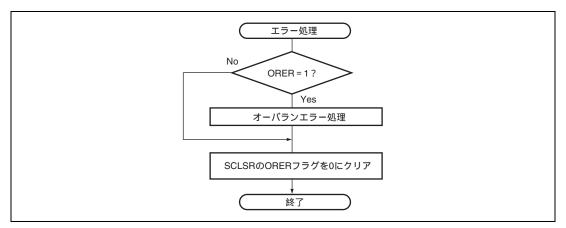

| 16.7.2               | SCFRDR の読み出しと RDF フラグについて                    | 16-52 |

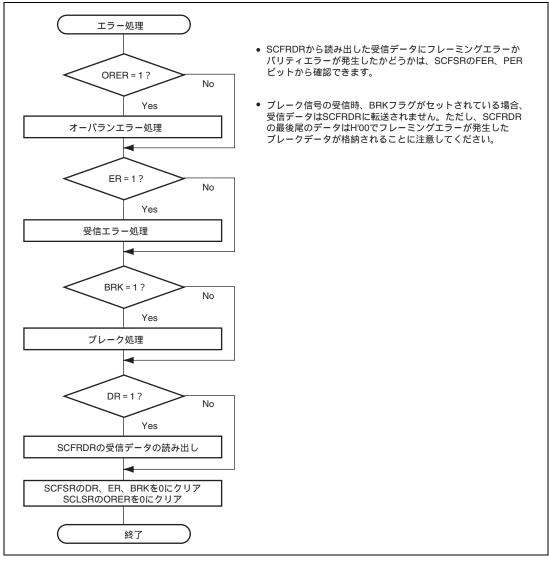

| 16.7.3               | ブレークの検出と処理について                               | 16-52 |

| 16.7.4               | ブレークの送り出し                                    | 16-53 |

| 16.7.5               | 調歩同期式モードの受信データサンプリングタイミングと受信マージン             | 16-53 |

| 16.7.6               | モジュールスタンバイモードの設定                             | 16-54 |

| 16.7.7               | DTC 使用上の注意事項                                 | 16-54 |

| 16.7.8               | シリアルステータスレジスタ(SCFSR)の FER フラグおよび PER フラグについて | 16-54 |

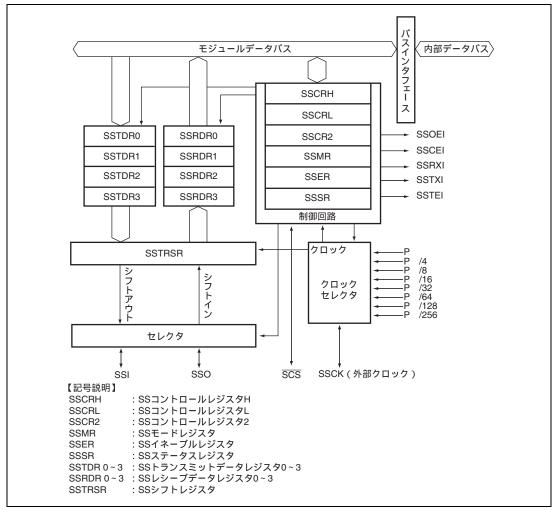

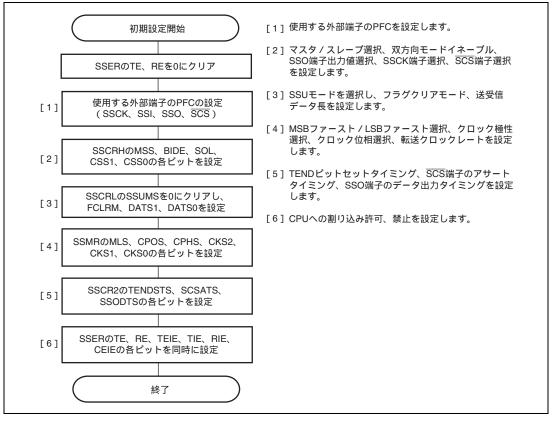

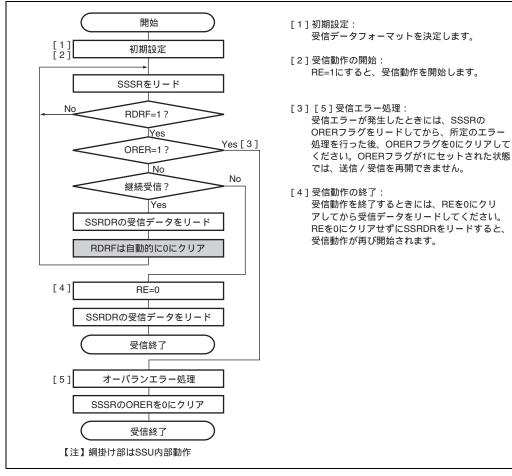

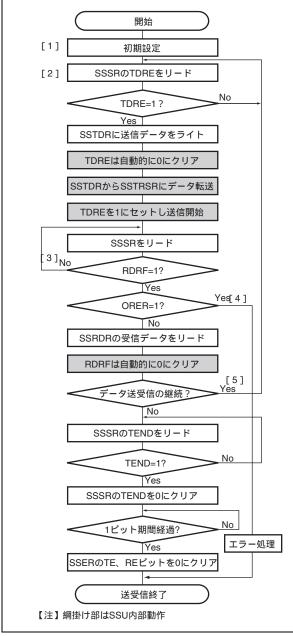

| 17. シン               | ノクロナスシリアルコミュニケーション ユニット(SSU)                 | 17-1  |

| 17.1                 | 特長                                           | 17-1  |

| 17.2                 | 入出力端子                                        | 17-3  |

| 17.3                 | レジスタの説明                                      | 17-4  |

| 17.3.1               | SS コントロールレジスタ H ( SSCRH )                    | 17-5  |

| 17.3.2               | SS コントロールレジスタL ( SSCRL )                     | 17-6  |

| 17.3.3               | SS モードレジスタ ( SSMR )                          | 17-7  |

| 17.3.4               | SS イネーブルレジスタ ( SSER )                        | 17-8  |

| 17.3.5               | SS ステータスレジスタ ( SSSR )                        | 17-9  |

| 17.3.6               | SS コントロールレジスタ 2 ( SSCR2 )                    | 17-12 |

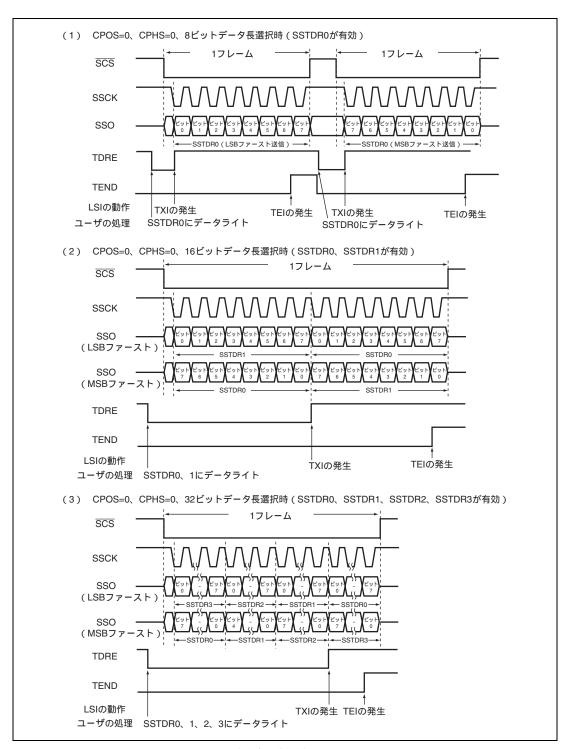

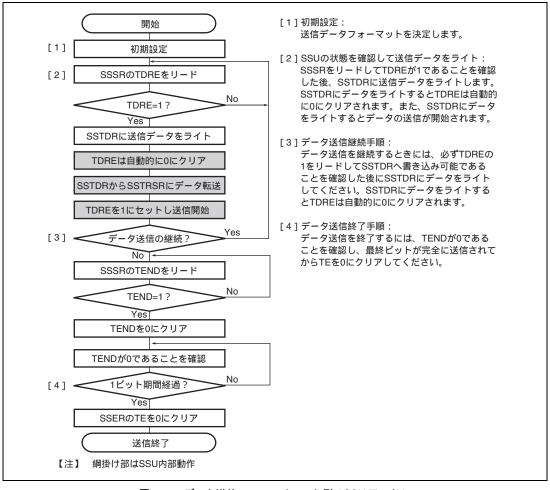

| 17.3.7               | SS トランスミットデータレジスタ 0~3 ( SSTDR0~SSTDR3 )      | 17-13 |

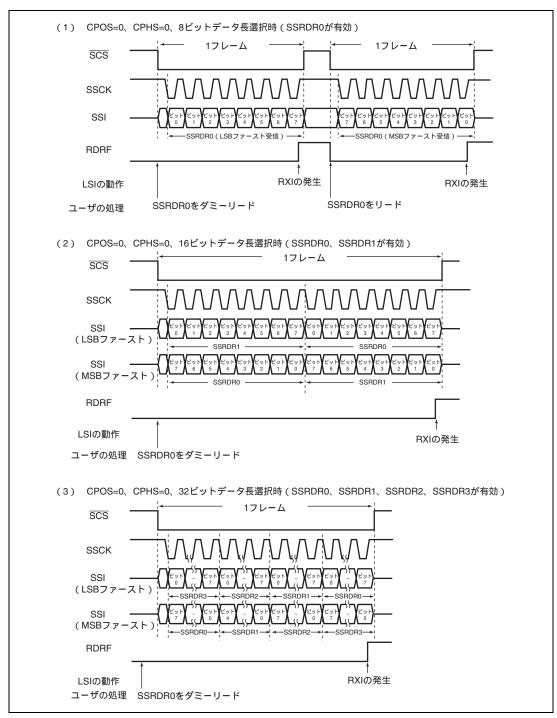

| 17.3.8               | SS レシープデータレジスタ 0~3 ( SSRDR0~SSRDR3 )         | 17-14 |

| 17.3.9               | SS シフトレジスタ ( SSTRSR )                        | 17-15 |

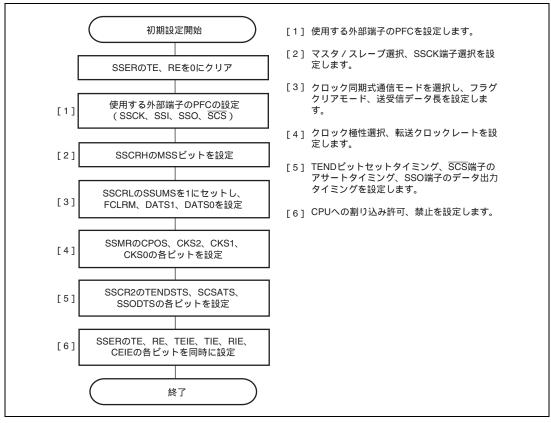

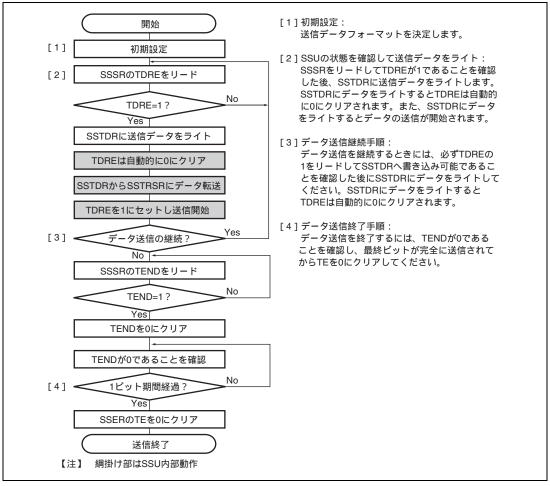

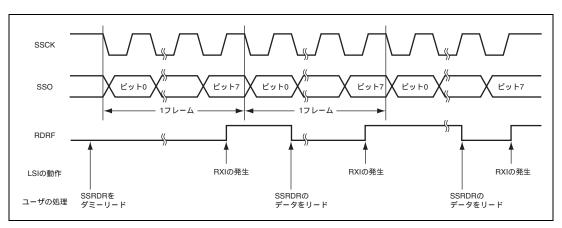

| 17.4                 | 動作説明                                         | 17-16 |

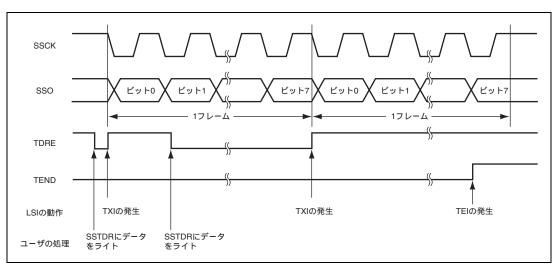

| 17.4.1               | 転送クロック                                       | 17-16 |

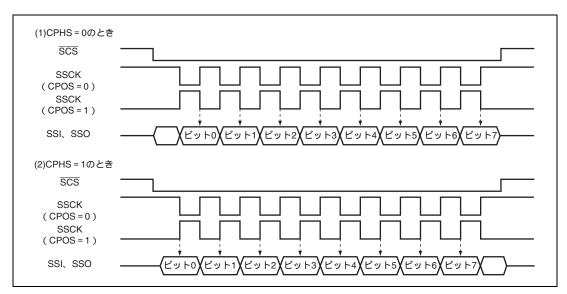

| 17.4.2               | クロックの位相、極性とデータの関係                            | 17-16 |

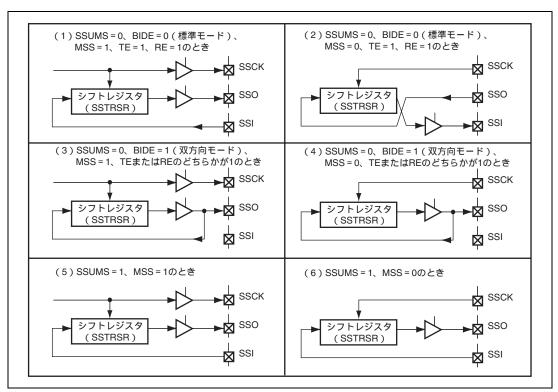

| 17.4.3               | データ入出力端子とシフトレジスタの関係                          | 17-17 |

| 17.4.4               | 各通信モードと端子機能                                  | 17-18 |

| 17.4.5               | SSU モード                                      | 17-19 |

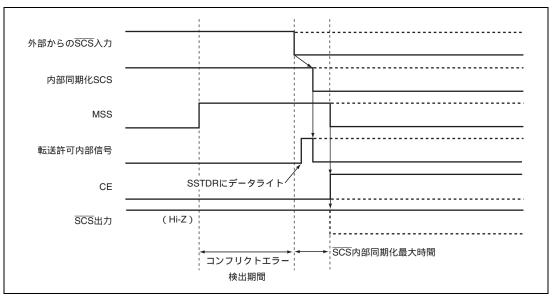

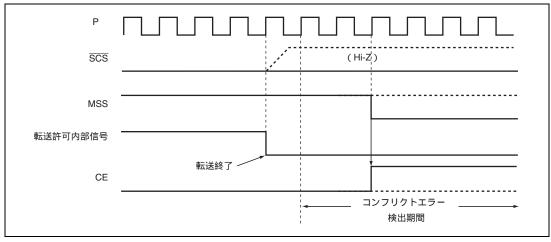

| 17.4.6               | SCS 端子制御とコンフリクトエラー                           | 17-27 |

| 17.4.7               | クロック同期式通信モード                                 | 17-28 |

| 17.5                 | SSUの割り込み要因とDTC                               | 17-34 |

| 17.6                 | 使用上の注意事項                                     | 17-35 |

| 17.6.1               | モジュールスタンバイモードの設定                             | 17-35 |

| 17.6.2               | SSTDR、SSRDR レジスタのアクセス                        | 17-35 |

| 17.6.3               | SSU スレーブモードにおける連続送受信時の注意事項                   | 17-35 |

| 17.6.4               | SSU モードでのスレーブ受信動作時の注意事項                      | 17-35 |

| 17.6.5               | SSU モードでのマスタ送信、マスタ送受信の注意事項                   | 17-35 |

| 17.6.6               | DTC 転送を行うときの注意事項                             | 17-36 |

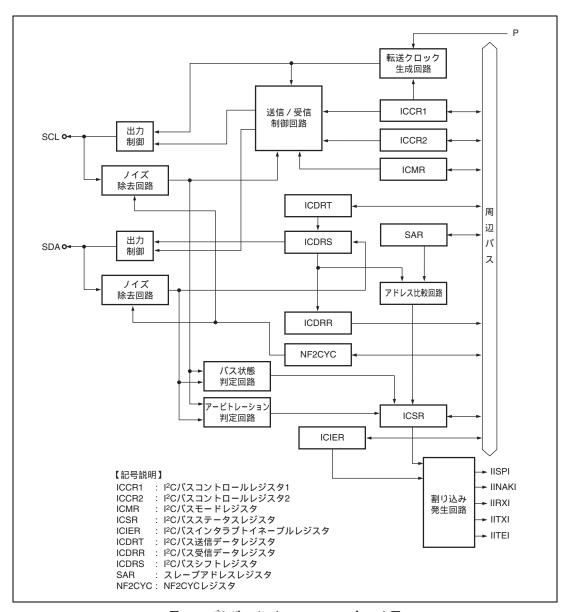

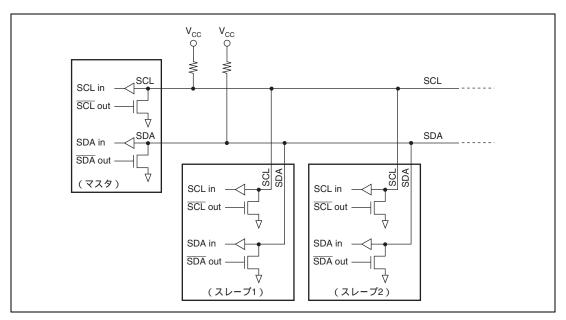

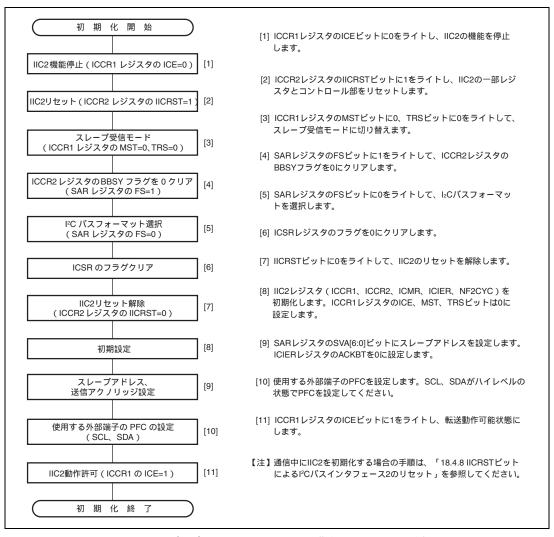

| 18. I <sup>2</sup> C | バスインタフェース 2(IIC2)                            | 18-1  |

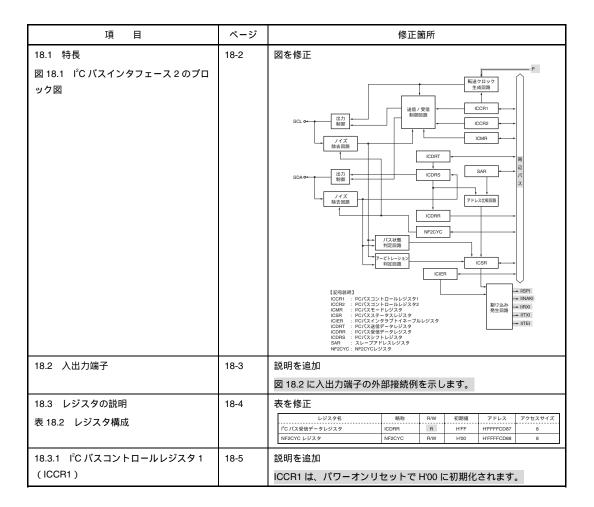

| 18.1                 | 特長                                           | 18-1  |

| 18.2    | 入出力端子                                                 | 18-3  |

|---------|-------------------------------------------------------|-------|

| 18.3    | レジスタの説明                                               |       |

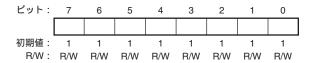

| 18.3.1  | I <sup>2</sup> C バスコントロールレジスタ 1(ICCR1)                |       |

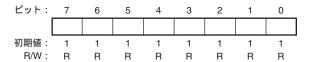

| 18.3.2  | I <sup>2</sup> C バスコントロールレジスタ 2 ( ICCR2 )             | 18-7  |

| 18.3.3  | I <sup>2</sup> C バスモードレジスタ(ICMR)                      | 18-9  |

| 18.3.4  | I <sup>2</sup> C バスインタラプトイネーブルレジスタ(ICIER)             | 18-11 |

| 18.3.5  | I <sup>2</sup> C バスステータスレジスタ(ICSR)                    | 18-13 |

| 18.3.6  | スレープアドレスレジスタ(SAR)                                     | 18-15 |

| 18.3.7  | I <sup>2</sup> C バス送信データレジスタ(ICDRT)                   | 18-16 |

| 18.3.8  | I <sup>2</sup> C バス受信データレジスタ(ICDRR)                   | 18-16 |

| 18.3.9  | I <sup>2</sup> C バスシフトレジスタ(ICDRS)                     | 18-16 |

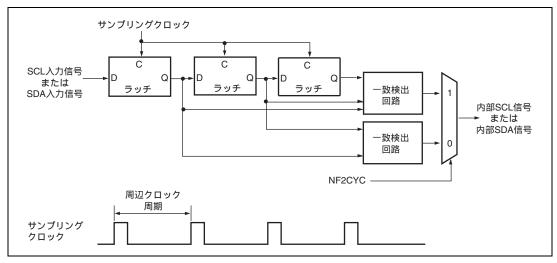

| 18.3.10 | NF2CYC レジスタ (NF2CYC)                                  | 18-17 |

| 18.4    | 動作説明                                                  | 18-18 |

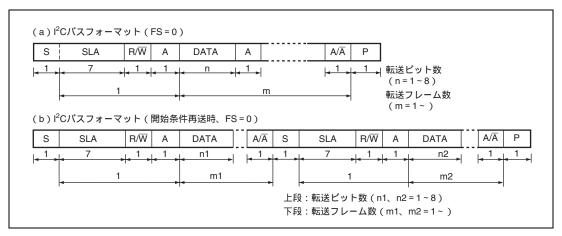

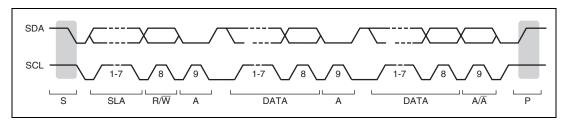

| 18.4.1  | I <sup>2</sup> C バスフォーマット                             | 18-18 |

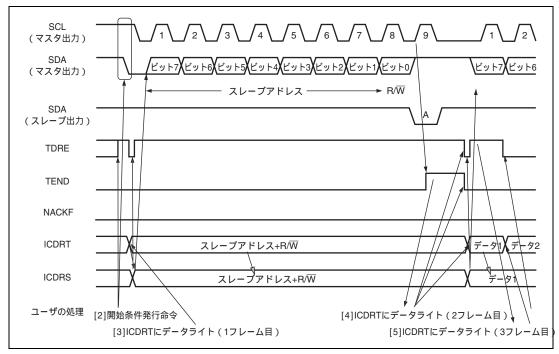

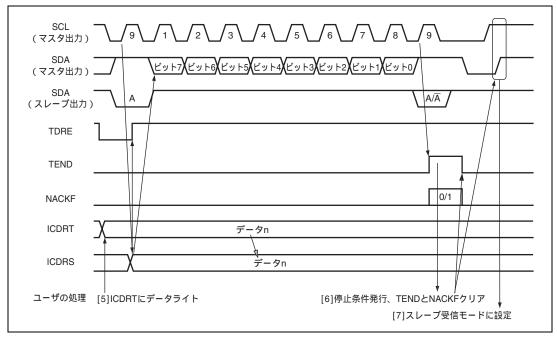

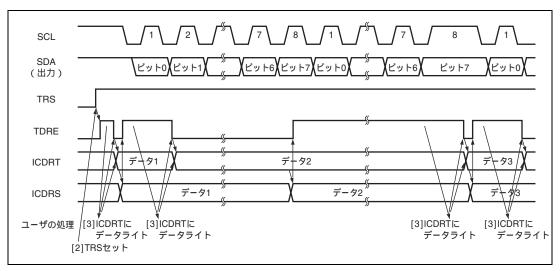

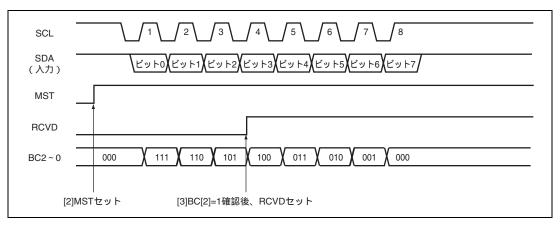

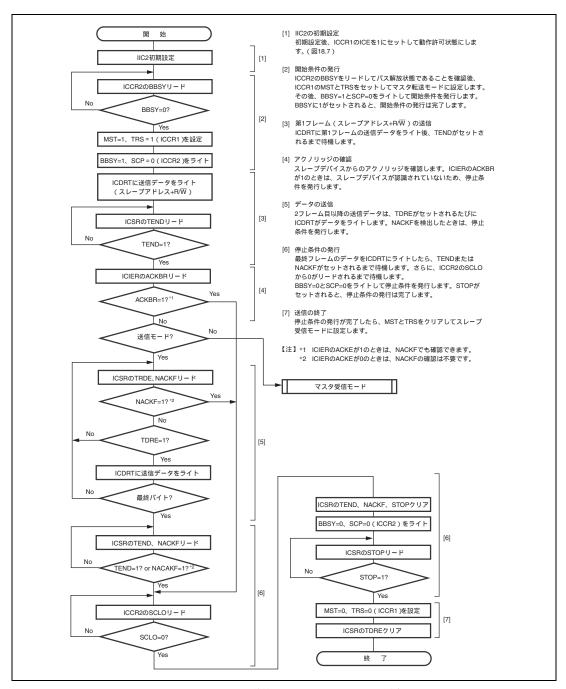

| 18.4.2  | マスタ送信動作                                               | 18-19 |

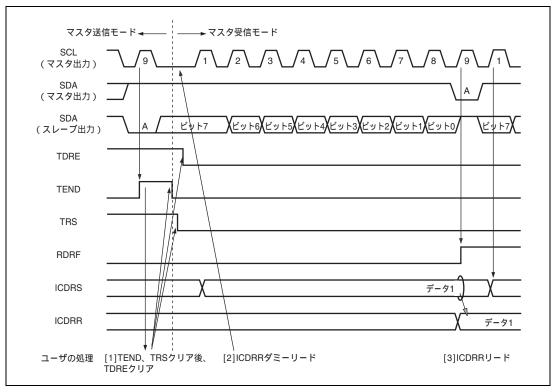

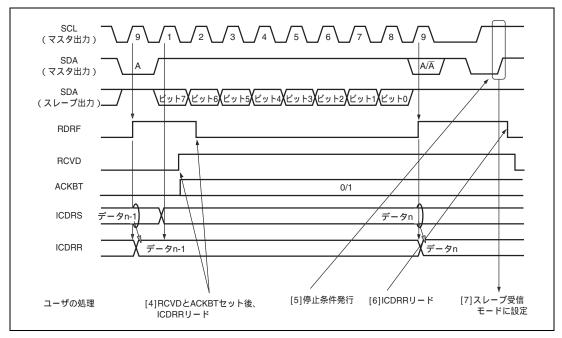

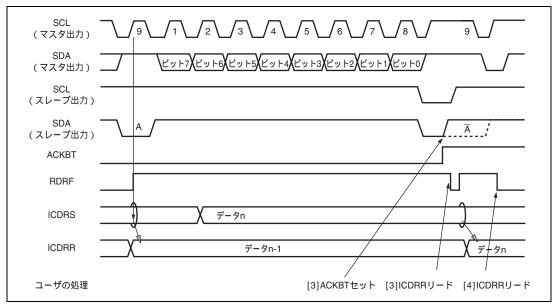

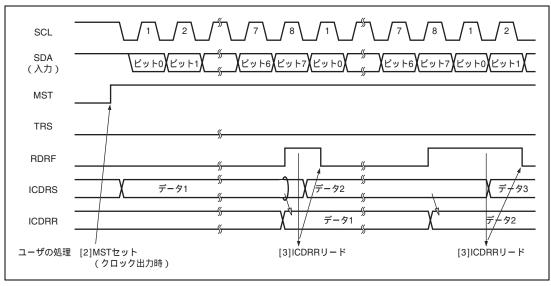

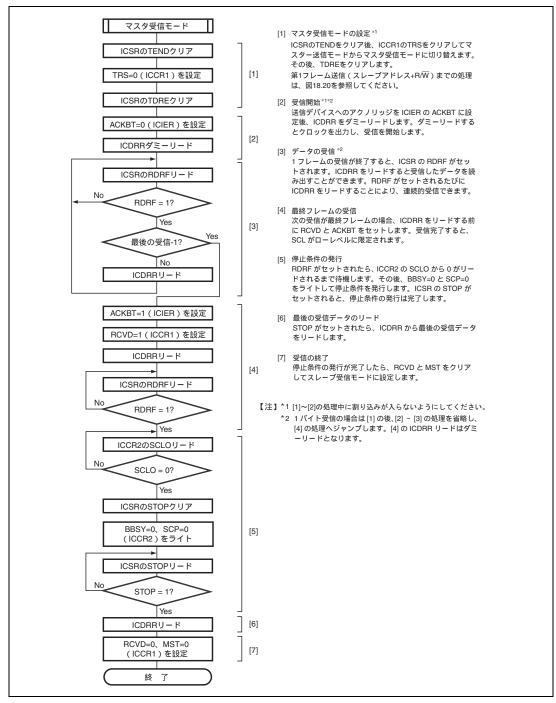

| 18.4.3  | マスタ受信動作                                               | 18-22 |

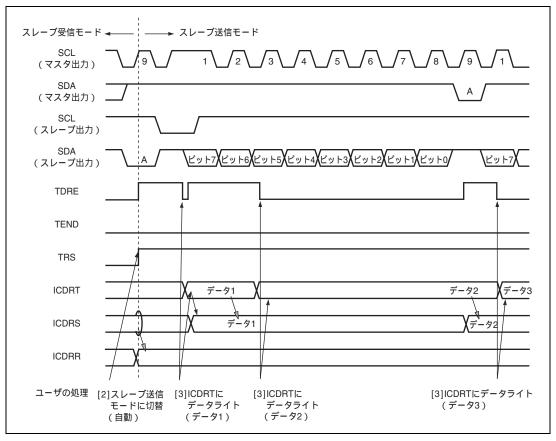

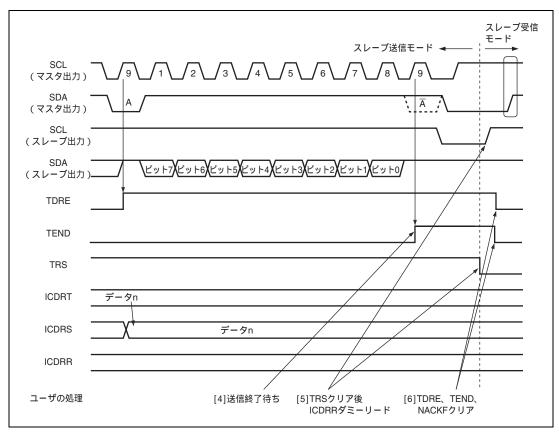

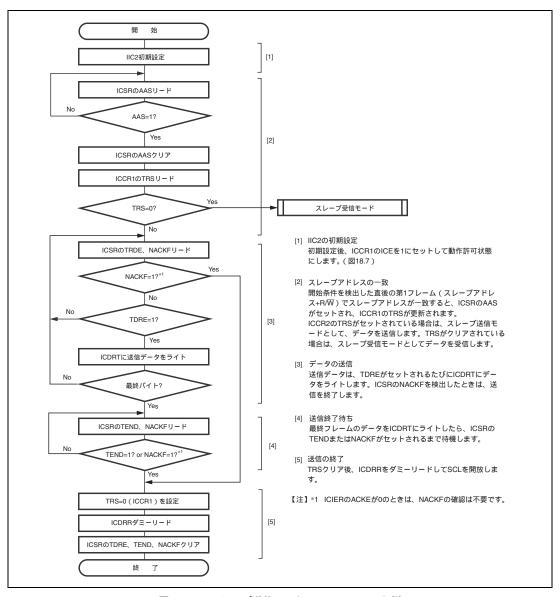

| 18.4.4  | スレーブ送信動作                                              | 18-24 |

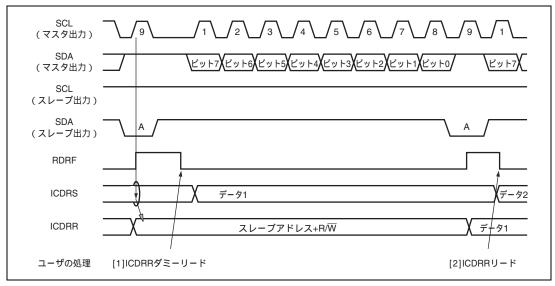

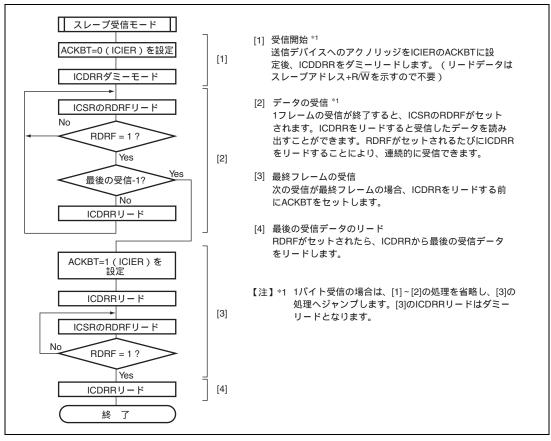

| 18.4.5  | スレーブ受信動作                                              | 18-27 |

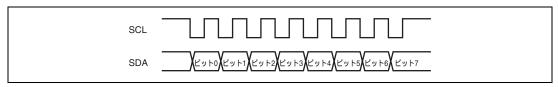

| 18.4.6  | クロック同期式シリアルフォーマット                                     | 18-28 |

| 18.4.7  | ノイズ除去回路                                               | 18-31 |

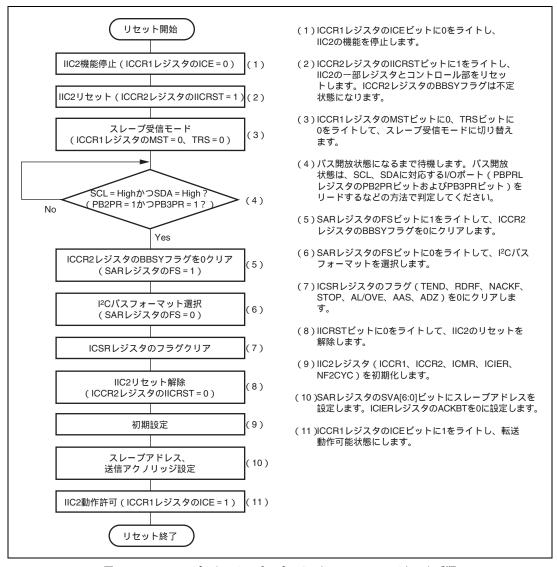

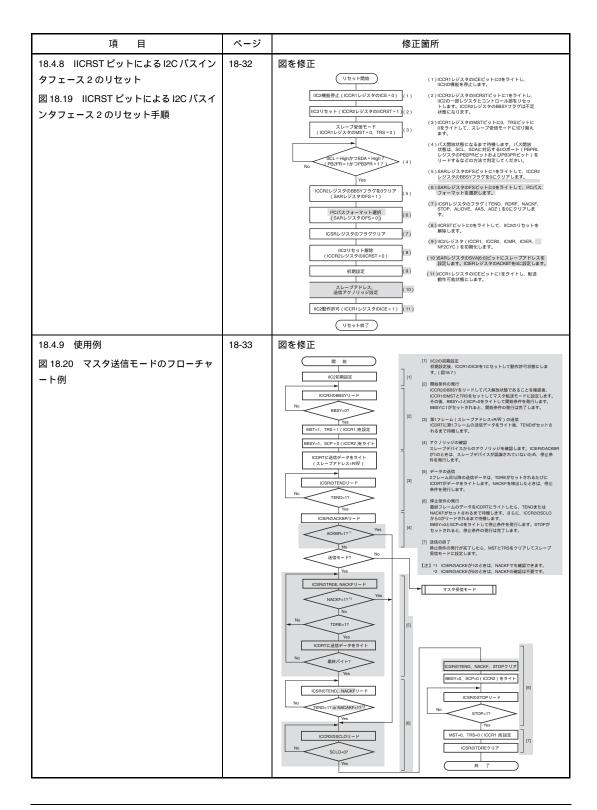

| 18.4.8  | IICRST ビットによる f'C バスインタフェース 2 のリセット                   | 18-32 |

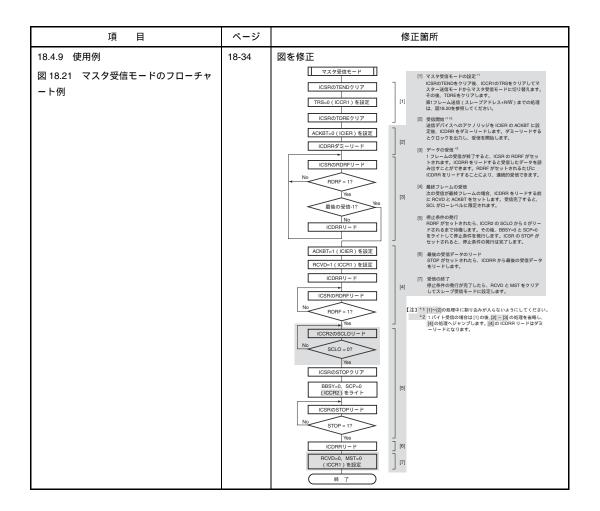

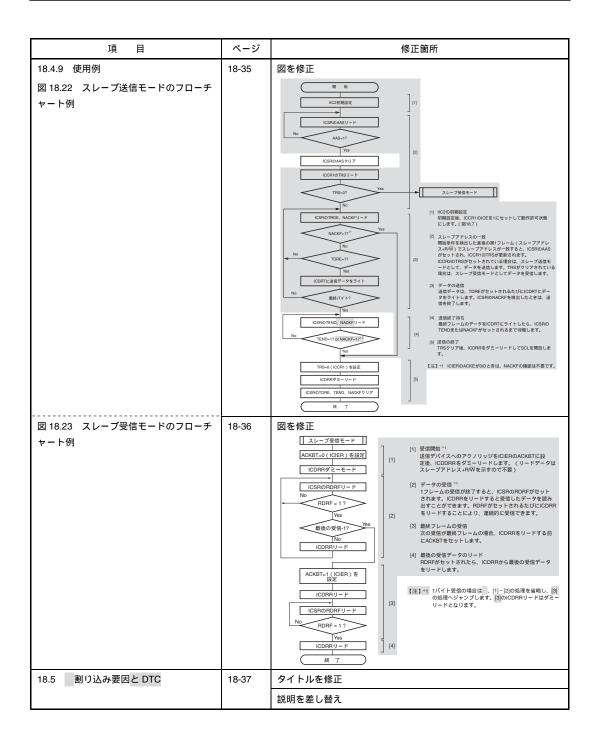

| 18.4.9  | 使用例                                                   | 18-33 |

| 18.5    | 割り込み要因とDTC                                            | 18-37 |

| 18.6    | DTCによる動作                                              | 18-39 |

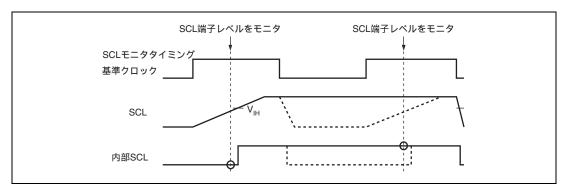

| 18.7    | ビット同期回路                                               | 18-40 |

| 18.8    | 使用上の注意事項                                              | 18-41 |

| 18.8.1  | モジュールスタンバイモードの設定                                      | 18-41 |

| 18.8.2  | 停止条件の発行および開始条件(再送)の発行                                 | 18-41 |

| 18.8.3  | 開始条件と停止条件の連続発行                                        | 18-41 |

| 18.8.4  | マルチマスタ使用時の設定について                                      | 18-41 |

| 18.8.5  | マスタ受信モードにおける ICDRR のリード                               |       |

| 18.8.6  | I <sup>2</sup> C バス動作中における ICE ビットおよび IICRST ビットのアクセス | 18-42 |

| 18.8.7  | IICRST ビットによるレジスタ初期化                                  | 18-42 |

| 18.8.8  | ICE = 0 における I <sup>2</sup> C バスインタフェース 2 の動作         | 18-43 |

| 18.8.9  | マスタ受信モード切り替え時の注意事項について                                | 18-43 |

| 18.8.10 | ) IIRXI 割り込みを要因とした DTC 転送について                         |       |

| 18.8.11 | IITXI 割り込みを要因とした DTC 転送について                           | 18-44 |

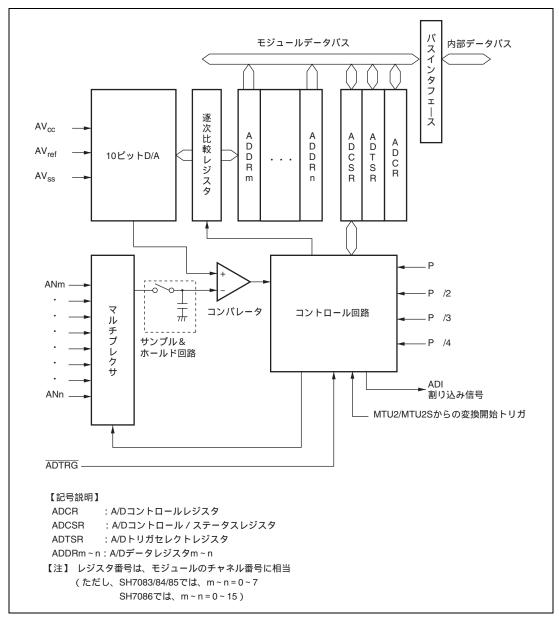

| 19. A/D | 变换器(ADC)                                              | 19-1  |

| 19.1    | 特長                                                    | 19-1  |

| 19.2    | 入出力端子                                                 | 19-3  |

| 19.3   | レジスタの説明                                  | 19-4  |

|--------|------------------------------------------|-------|

| 19.3.1 | A/D データレジスタ 0~15 ( ADDR0~ADDR15 )        | 19-5  |

| 19.3.2 | A/D コントロール / ステータスレジスタ_0~2 ( ADCSR_0~2 ) | 19-5  |

| 19.3.3 | A/D コントロールレジスタ_0~2 ( ADCR_0~2 )          | 19-7  |

| 19.3.4 | A/D トリガセレクトレジスタ_0、1 ( ADTSR_0、1 )        | 19-10 |

| 19.4   | 動作説明                                     | 19-15 |

| 19.4.1 | シングルモード                                  | 19-15 |

| 19.4.2 | 連続スキャンモード                                | 19-15 |

| 19.4.3 | 1 サイクルスキャンモード                            | 19-16 |

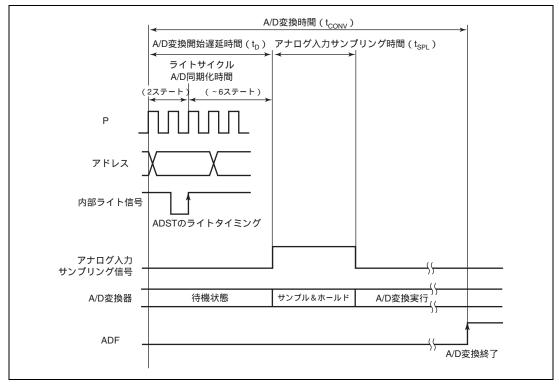

| 19.4.4 | 入力サンプリングと A/D 変換時間                       | 19-17 |

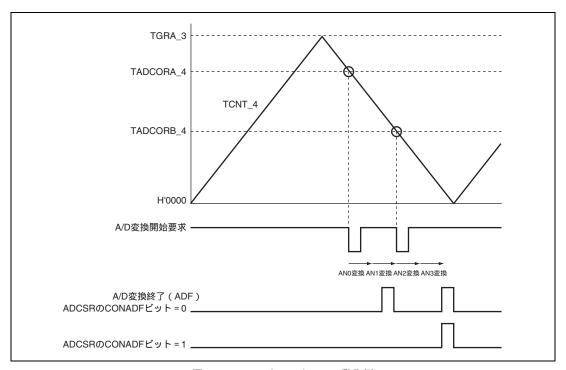

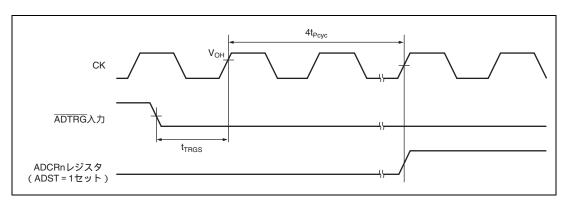

| 19.4.5 | MTU2、MTU2S による A/D 変換器の起動                | 19-19 |

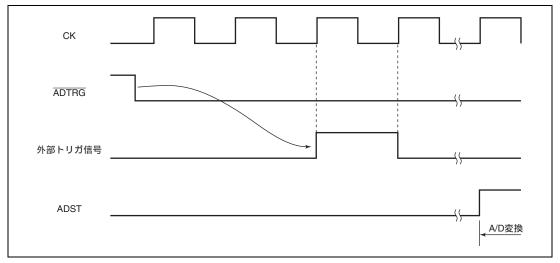

| 19.4.6 | 外部トリガ入力タイミング                             | 19-19 |

| 19.4.7 | 2 チャネルスキャン                               | 19-20 |

| 19.5   | 割り込み要因とDMAC/DTC転送要求                      | 19-21 |

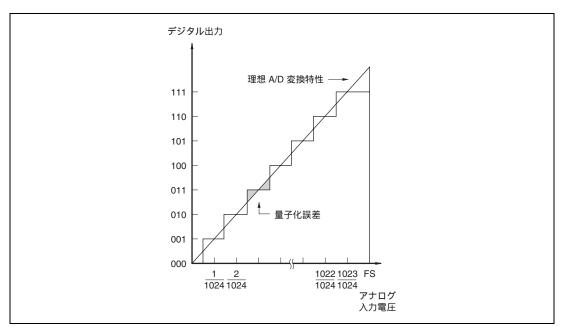

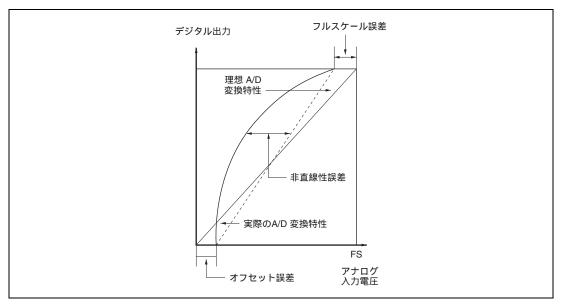

| 19.6   | A/D変換精度の定義                               | 19-22 |

| 19.7   | 使用上の注意事項                                 | 19-24 |

| 19.7.1 | モジュールスタンバイモードの設定                         | 19-24 |

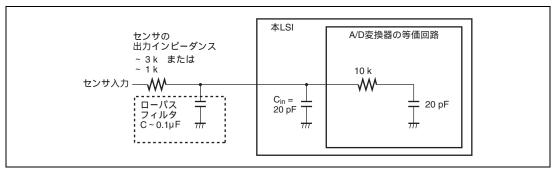

| 19.7.2 | 許容信号源インピーダンスについて                         | 19-24 |

| 19.7.3 | 絶対精度への影響                                 | 19-24 |

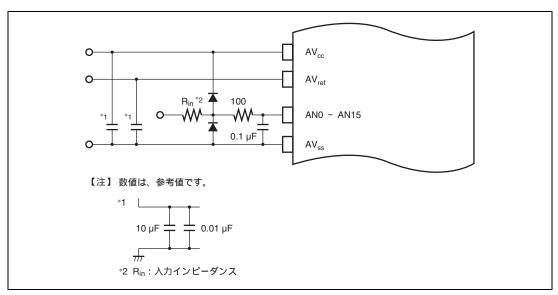

| 19.7.4 | アナログ電源端子などの設定範囲                          | 19-25 |

| 19.7.5 | ボード設計上の注意事項                              | 19-25 |

| 19.7.6 | ノイズ対策上の注意事項                              | 19-25 |

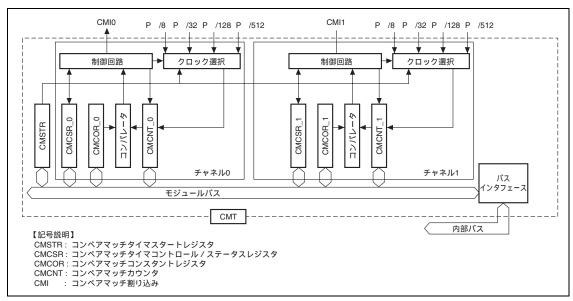

| 20. コン | パペアマッチタイマ(CMT)                           | 20-1  |

| 20.1   | 特長                                       | 20-1  |

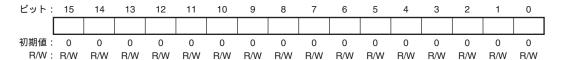

| 20.2   | レジスタの説明                                  |       |

| 20.2.1 | コンペアマッチタイマスタートレジスタ (CMSTR)               |       |

| 20.2.2 | コンペアマッチタイマコントロール / ステータスレジスタ (CMCSR)     |       |

| 20.2.3 | コンペアマッチカウンタ ( CMCNT )                    |       |

| 20.2.4 | コンペアマッチコンスタントレジスタ(CMCOR)                 |       |

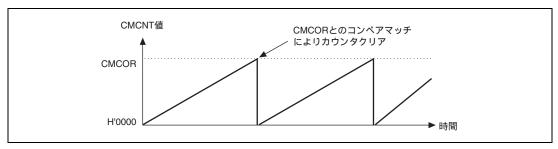

| 20.3   | 動作説明                                     |       |

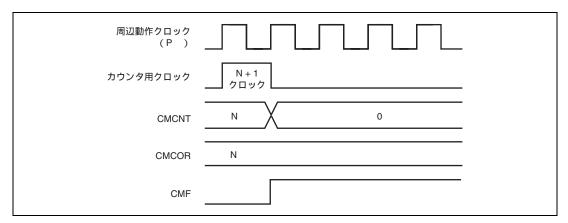

| 20.3.1 | 期間カウント動作                                 |       |

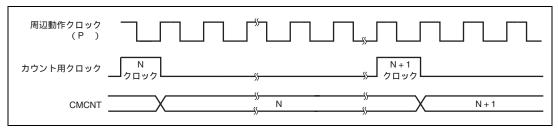

| 20.3.2 | CMCNT カウントタイミング                          |       |

| 20.4   | 割り込み                                     | 20-6  |

| 20.4.1 | ョウン かました DTC 転送要求                        |       |

| 20.4.2 | コンペアマッチフラグのセットタイミング                      |       |

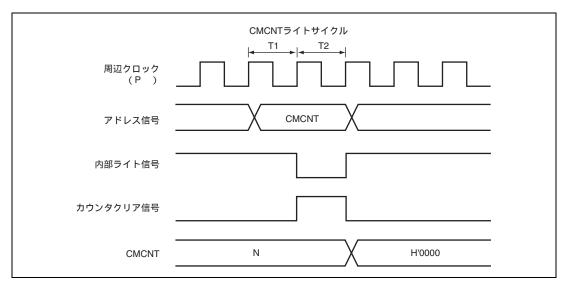

| 20.4.3 | コンペアマッチフラグのクリアタイミング                      |       |

| 20.5   | 使用上の注意事項                                 |       |

| 20.5.1 | モジュールスタンバイモードの設定                         |       |

| 20.5.2 | CMCNT の書き込みとコンペアマッチの競合                   |       |

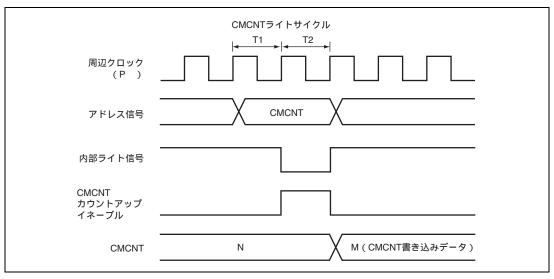

| 20.5.3 | CMCNT のワード書き込みとカウントアップの競合                |       |

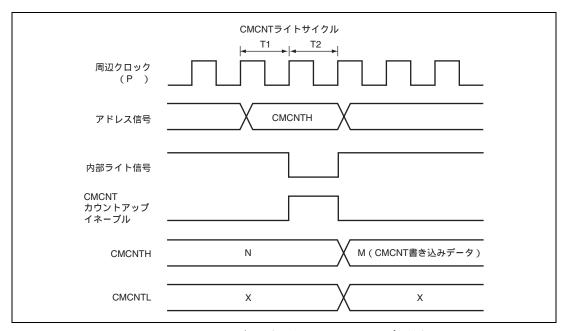

| 20.5.4         | CMCNT のバイト書き込みとカウントアップの競合                   | 20-10  |

|----------------|---------------------------------------------|--------|

| 20.5.5         | CMCNT と CMCOR のコンペアマッチ                      | 20-10  |

|                |                                             |        |

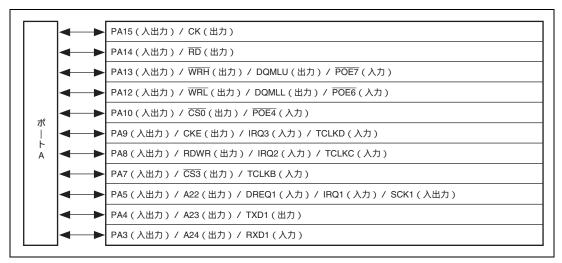

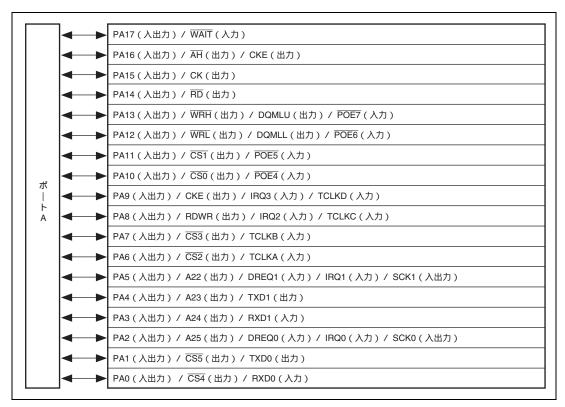

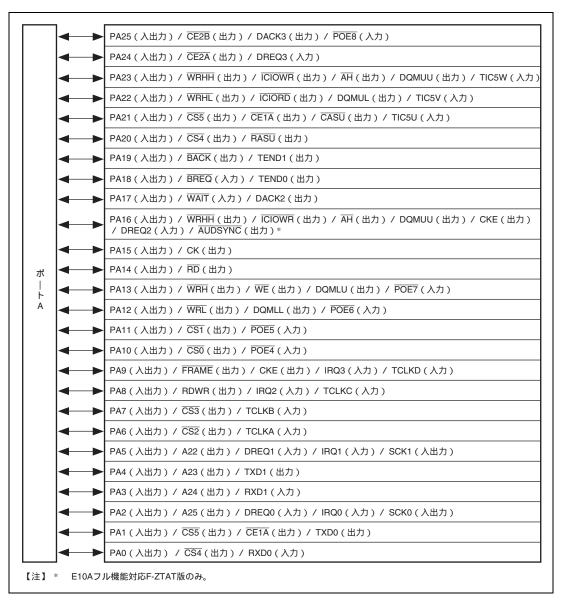

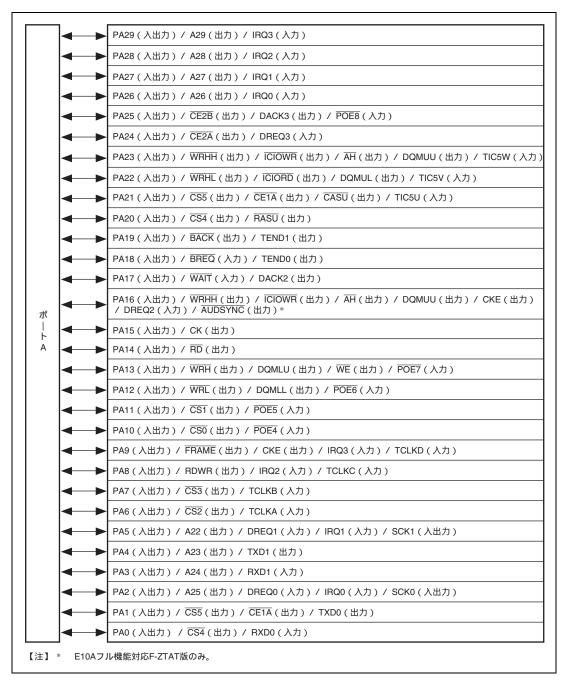

| 21. ピン         | プアンクションコントローラ(PFC)                          | 21-1   |

| 21.1           | レジスタの説明                                     | 21-43  |

| 21.1.1         | ポートA・IO レジスタL、H(PAIORL、PAIORH)              | 21-44  |

| 21.1.2         | ポート A コントロールレジスタ L1~L4、H1~H4                |        |

|                | (PACRL1~PACRL4, PACRH1~PACRH4)              | 21-45  |

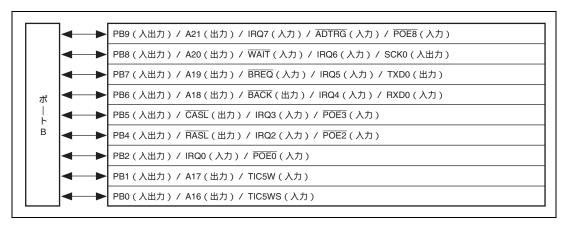

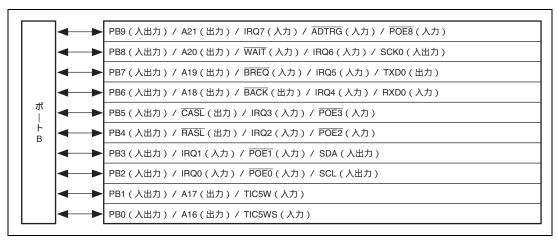

| 21.1.3         | ポート B・IO レジスタ L ( PBIORL )                  | 21-73  |

| 21.1.4         | ポートB コントロールレジスタ L1 ~ L3 ( PBCRL1 ~ PBCRL3 ) | 21-73  |

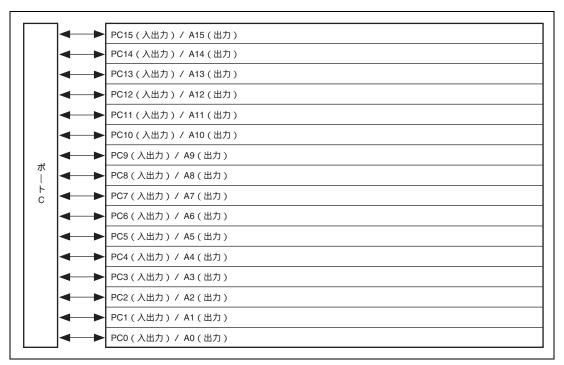

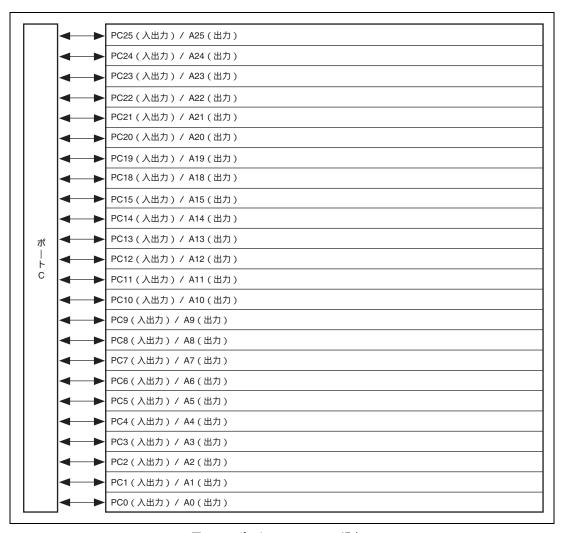

| 21.1.5         | ポート C・IO レジスタ L、H(PCIORL、PCIORH)            | 21-80  |

| 21.1.6         | ポート C コントロールレジスタ L1 ~ L4、H1 ~ H3            |        |

|                | ( PCCRL1 ~ PCCRL4、 PCCRH1 ~ PCCRH3 )        | 21-81  |

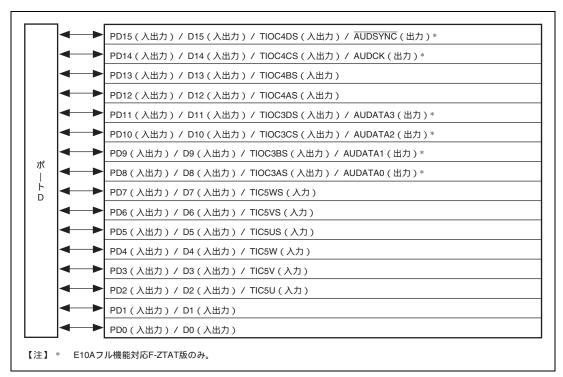

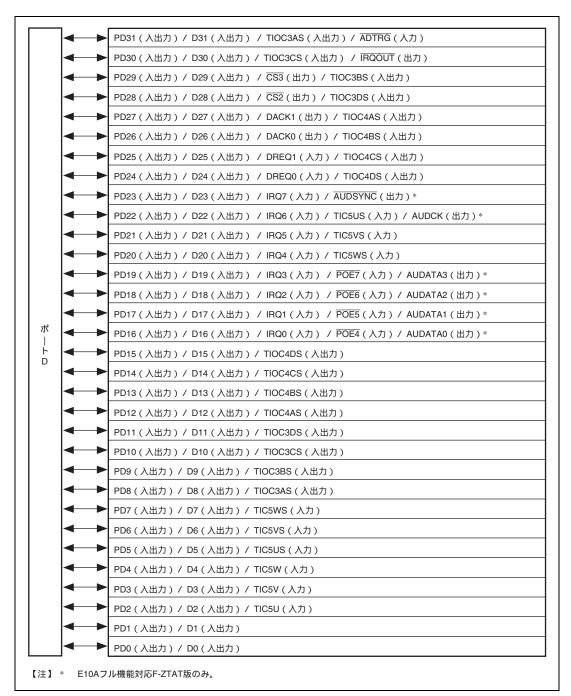

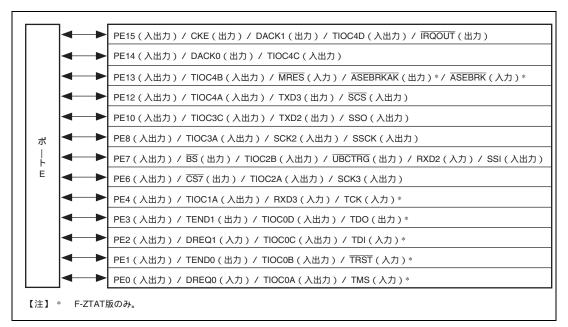

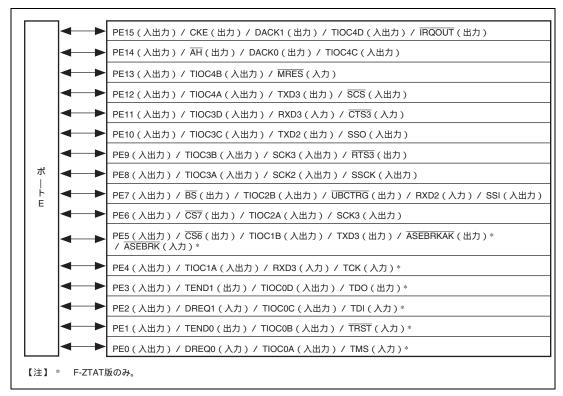

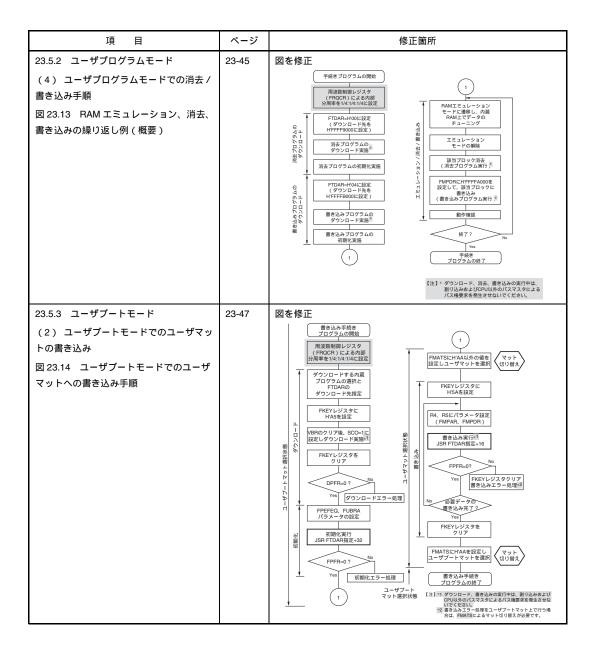

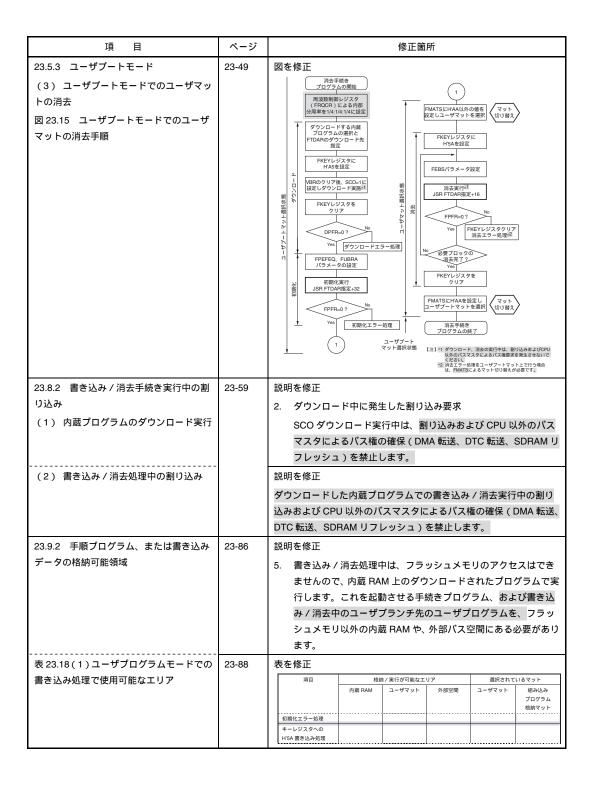

| 21.1.7         | ポートD・IO レジスタL、H(PDIORL、PDIORH)              | 21-92  |