# RENESAS Timing Commander<sup>™</sup> Software for VersaClock<sup>®</sup> 3S - 5P3502x

# Glossary

**IDT Timing Commander Software** – Executable file that will execute a personality, connect to a timing chip on an evaluation board, and read or write Settings files.

**Personality** – Encrypted file with an extension .tcp. Used by IDT Timing Commander Software to determine the characteristics for a specific family of timing devices. A personality file may refer to a single device or an entire family of similar devices. Please contact IDT to obtain the most current version of a personality file for the devices of interest.

**Settings File** – Text file with extension .tcs. Written or read by IDT Timing Commander Software to save or restore a particular setup for a specific version of a device personality and version of IDT Timing Commander Software. Settings files created with newer versions of IDT Timing Commander Software or a device personality may not be compatible when read into older version of IDT Timing Commander Software, or, if an older version of the personality is installed. Forward compatibility (older settings files read by newer software and/or personality) will be maintained.

**Bit Set** – A single variable stored within the registers of the device. A bit set may use only part of a register or many span multiple registers, but is thought of as a single field. For example, a 20-bit output divider ratio may be defined as a single bit set of length 20-bits, but may be stored in Register 0x4A, bits [3:0], Register 0x4B, bits [7:0] and Register 0x4c, bits [7:0].

**Metadata** – Variable used within the personality, but not stored directly in device registers. For example, an output frequency is generally not stored anywhere in a device's registers, but must be known to calculate register settings for the device with which we achieve those frequencies.

**Tooltip** – Context-sensitive pop-up that appears briefly as the mouse pointer hovers over an icon or element on the screen. These are intended to provide useful information about the specific item being pointed to.

Value – When referring to any field that the user can edit, Value means the current internally-represented value of that field.

**Default Value** – When referring to any field that the user can edit, *Default Value* means the value recommended by the personality for that field, taking into account the settings in other fields in the device. Changes of other fields may result in a change to the Default Value. Whenever a field is unlocked, Default Value = Value. Only by locking a field can a user set a field to a Value other than the Default Value or prevent a field's Value from changing if Default Value changes.

**Display Value** – A field may be controlled by a personality to display its *Value* or *Default Value* in a more meaningful way. For example, if the Value is defined in MHz, but the actual value is 0.008MHz, the personality may choose to display this to the user as 8KHz. In another example, if a bit set represents a divider ratio that can only be an even number and so does not implement the Least Significant bit, the personality may choose to show a divider ratio of 2 when the bit set value is 1 (i.e., 1 increment of divide-by-2).

# **Getting Started**

Follow the steps below to start a new setting or open an existing Settings File and configure the device to meet your timing requirements.

Note: Ensure to install latest Timing Commander version before proceeding with next step.

1. Launching Timing Commander GUI software for the first time, you will see the following window:

## Figure 1. Launching Timing Commander for the First Time

| New Settings File Open Settings File | © IDT.<br>IDT Timing Commander<br>Nour Timing Tree |

|--------------------------------------|----------------------------------------------------|

|                                      | New Settings File Open Settings File               |

A settings file (.tcs) is a text file where the device input and output requirements are stored. From this window, an existing setting file can be opened to restore a configuration, or a new setting file can be created.

**2. Clicking on "New Setting File" button**, a personality file (.tcp) will be requested and can be opened by browsing to the folder where a personality file is stored. Once the personality file is opened (click OK), the following page will be displayed, where the correct VC3S product can be selected (see Figure 2). As soon as the product is selected, then the configuration window for the selected product will appear as in Figure 4.

## Figure 2. Choose Correct VersaClock 3S Part Number

| Description           | VersaClock3S          |

|-----------------------|-----------------------|

| 3-Output VersaClock3S |                       |

| 6-Output VersaClock3S | 5P35023               |

|                       | 6-Output VersaClock3S |

|                       | 6-Output VersaClock3S |

|                       |                       |

|                       | 3-Output VersaClock3S |

# Figure 3. Launching the User Interface

# Areas of the Screen for the Summary View

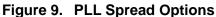

A block diagram is displayed when a Settings File is loaded with a personality of a device (5P35023). There are differential areas in the block diagram as shown in Figure 4 along with detailed explanations of the labels in Table 1.

Figure 4. Summary View Description of 5P35023

# Table 1: 5P35023 Summary View Labels Description

| Label # | Timing Commander<br>Label | Description                                                                              |

|---------|---------------------------|------------------------------------------------------------------------------------------|

| 0       | IDT5P35023                | The detailed block diagram of the device                                                 |

| 1       | PIN out                   | 5P35023 pinout                                                                           |

| 2       | 5P35023 v1.0              | Personality revision                                                                     |

| 3       | Search Box                | This is used to search for items on the screen                                           |

| 4       | 5P25023                   | Part number corresponding to the personality being used                                  |

| 5       | Save                      | Enable to save the current configuration as a .tcs file                                  |

| 6       | Diagram                   | Default tab                                                                              |

| 7       | Bit Sets                  | Tab that shows all bit set used in this personality for 5P35023                          |

| 8       | Registers                 | Register table tab shows all register bits settings and address                          |

| 9       | Enable check box          | If checked it enables the corresponding Outputs                                          |

| 10      | Source                    | Selects the frequency source either as Crystal or input Clock                            |

| 11      | Output Frequency          | Field to enter the output frequencies                                                    |

| 12      | Input Frequency           | Field to enter the input frequency                                                       |

| 13      | Signal Type               | Drop down button to enter the output type                                                |

| 14      | VDDO                      | Drop down button to enter the voltage for each output                                    |

| 15      | Spread Spectrum           | Enable or disable the spread spectrum feature on the selected outputs                    |

| 16      | + -                       | Enable to zoom in or zoom out the tab                                                    |

| 17      | i                         | Display information about timing commander                                               |

| 18      | Connect                   | Enable the Connection to the Evaluation Board                                            |

| 19      | Settings                  | Setting window for I2C connection                                                        |

| 20      | Calculate                 | Execute calculation of the entered frequency combination when disconnected from the DUT. |

| 21      | Optimization Options      | Open Optimization box for PCIe and phase jitter performance                              |

| 22      | Reset*                    | Writes null value to the chip                                                            |

| 23      | Restore to Default        | Restore the values to Factory Default                                                    |

\* Do not burn the part with Reset button enabled.

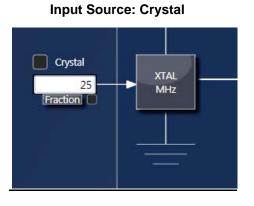

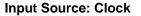

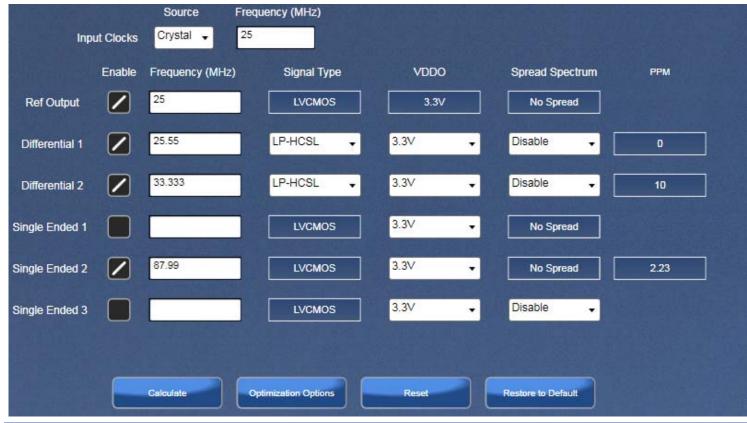

# 1 Input Clock Selection

Input source can be selected between a crystal and an external reference clock. The frequency can be entered besides the Dropdown under "Source". There are two options to select Source – Crystal and Clock. The maximum input frequency the crystal supports is 40 MHz, and Maximum input frequency from clock should be 125 MHz.

Figure 5. Input Clock Reference Selection (From Crystal)

Figure 6. Input Clock Reference Selection (From External Clock)

# 2 **Optimization Options**

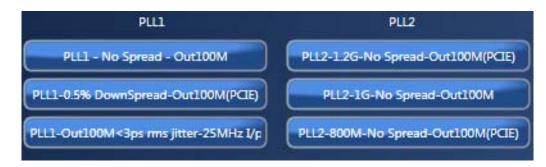

The 5P35023 GUI provides multiple options for optimizing the PLL1 and PLL2 settings for PCIe on DIFF-1 and DIFF-2 depending on the desired performance.

| PLLX | Description                                                                                                                                                                                                                                                                                                            |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLL1 | <ul> <li>PLL1-No Spread: optimizes 100MHz PCIe on DIFF1 and DIFF2 from PLL1</li> <li>PLL1-0.5% Down spread: optimizes 100MHz PCIe on DIFF1 and DIFF2 from PLL1 with 0.5% Down Spread</li> <li>PLL1-Out100M: optimizes 100MHz on DIFF1 and DIFF2 from PLL1 for 25 MHz Input that provides &lt;3ps RMS Jitter</li> </ul> |

| PLL2 | <ul> <li>PLL2-1.2G-No Spread: optimizes 100MHz PCIe on DIFF1 and DIFF2 from PLL2</li> <li>PLL2-1G-No Spread: optimizes Provides 100MHz PCIe on DIFF1 and DIFF2 from PLL2</li> <li>PLL2-800M-No Spread: optimizes 100MHz PCIe on DIFF1 and DIFF2 from PLL2</li> </ul>                                                   |

# Figure 7. Optimization Options

# 3 Output Selection and Configuration

There are 6 outputs in 5P35023, out of which two are differential pairs outputs, and four are single-ended outputs.

# Table 2: Output – Signal Type

| Signal Type | # of Outputs | Output Type                                       |

|-------------|--------------|---------------------------------------------------|

| LVCMOS      | 1            | Single-Ended for SE_1, SE_2, SE_3 & Ref.          |

| LVCMOS1     | 1            | Single-Ended Output                               |

| LVCMOSX2    | 2            | Two copies of the True terminal from Differential |

| LVPECL      | 2            | Differential                                      |

| LVDS        | 2            | Differential                                      |

| LP-HCSL     | 2            | Differential                                      |

# Table 3: Output – VDDO

| VDDO (V) | Available for                                                                              |

|----------|--------------------------------------------------------------------------------------------|

| 1.8      | Single-Ended 1; Single-Ended 2; Single-Ended 3                                             |

| 2.5      | Differential 1; Differential 2; Single-Ended 1; Single-Ended 2; Single-Ended 3             |

| 3.3      | Ref Output; Differential 1; Differential 2; Single-Ended 1; Single-Ended 2; Single-Ended 3 |

## 4 Restore to Default

This button erases the values entered by the user, and sets the window to factory default as per the table below.

## Table 4:Output Type

| Output Type    | Frequency (MHz) | Signal Type | VDDO (V) |

|----------------|-----------------|-------------|----------|

| Ref Output     | 25              | LVCMOS      | 3.3      |

| Differential 1 | 100             | LP-HCSL     | 3.3      |

| Differential 2 | 100             | LP-HCSL     | 3.3      |

| Single-Ended 1 | OFF             | LVCMOS      | 3.3      |

| Single-Ended 2 | 48              | LVCMOS      | 3.3      |

| Single-Ended 3 | 60              | LVCMOS      | 3.3      |

# 5 Spread Spectrum

This button will enable or disable the Spread Spectrum as required by the user (see Figure 8). Note that the spread spectrum is only available for Differential 1, Differential 2, and Single-Ended 3.

| Inp            | ut Clocks | Source Free<br>Crystal - 25 | quency (MHz)         |                                                       |                              |

|----------------|-----------|-----------------------------|----------------------|-------------------------------------------------------|------------------------------|

|                | Enable    | Frequency (MHz)             | Signal Type          | VDDO                                                  | Spread Spectrur              |

| Ref Output     |           | 25                          | LVCMOS               | 3.3V                                                  | No Spread                    |

| Differential 1 |           | 100                         | LP-HCSL 🗸            | 3.3V 🗸                                                | Disable                      |

| Differential 2 |           | 100                         | LP-HCSL 🗸            | 3.3∨ →                                                | Disable<br>Enable<br>Disable |

| Single Ended 1 |           | 0.032768                    | LVCMOS               | 3.3V →                                                | No Spread                    |

| Single Ended 2 |           | 48                          | LVCMOS               | <mark>3.3∨ →</mark>                                   | No Spread                    |

| Single Ended 3 |           | 60                          | LVCMOS               | <mark>3.3∨                                    </mark> | Disable                      |

|                |           | Calculate                   | Optimization Options | Reset                                                 | Restore to Default           |

## Figure 8. Enable/Disable Spread Spectrum

Once the Spread Spectrum is enabled, click the Calculate button to enable the PLL Spread Options as shown below to configure the Spread Spectrum as needed.

# Figure 10. Spread Spectrum

|                                | Enable Spread         | SS KHz                   |                  | 8 <mark>1.5</mark> | Real SS KHz (Obtained) |

|--------------------------------|-----------------------|--------------------------|------------------|--------------------|------------------------|

| Enable Spread Post Divide by 2 | Post Divide by 2 or 3 | Total Spread %<br>SS Dir | 0.5%<br>- spread | •                  | ss fb div              |

|                                |                       |                          |                  |                    |                        |

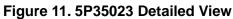

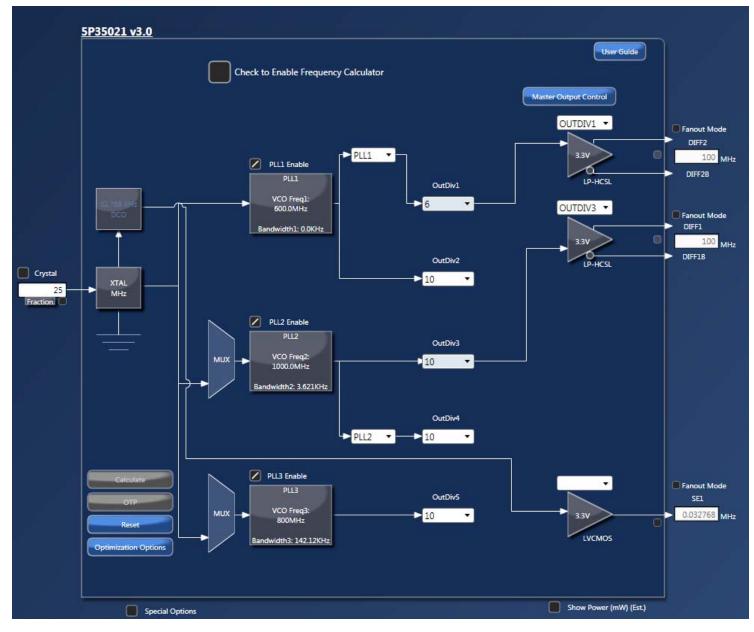

# Areas of the Screen for Detailed View

The Detailed view provides a full block diagram to the user and flexibility to change PLL settings, outputs and other. It reflects what has been entered in the summary view. Table 5 below describes all the labels mentioned in Figure 11.

## Table 5: Detailed View Label Description of 5P35023

| Serial | Timing Commander Label | Description                                                                  |

|--------|------------------------|------------------------------------------------------------------------------|

| 0      | Special Options        | Enables added functionalities                                                |

| 1      | Optimization Options   | Opens Optimization box for PCIe and phase jitter performance                 |

| 2      | Reset*                 | Writes null value to the Interface(GUI)                                      |

| 3      | OTP                    | Program the OTP                                                              |

| 4      | Calculate Values       | Execute calculation of the entered frequency combination in Calculation mode |

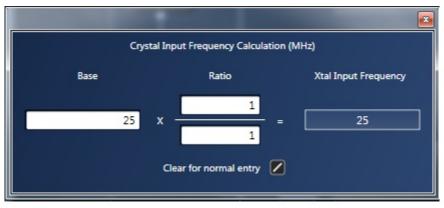

| 5      | XTAL MHz               | Opens the XTAL Configuration                                                 |

| 6      | Fraction Box           | Opens a fraction calculation window                                          |

| Serial | Timing Commander Label                                  | Description                                                                                                                                    |

|--------|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 7      | Crystal Frequency (Input Clock Selection)               | This signifies the Crystal Input Frequency                                                                                                     |

| 8      | 32.768 KHz DCO                                          | Opens the 32.768 KHz DCO Configuration output                                                                                                  |

| 9      | 5P35023 v0.27                                           | Personality revision                                                                                                                           |

| 10     | PLL1 Block                                              | Opens PLL1 block diagram                                                                                                                       |

| 11     | MUX                                                     | Provision for customized PLL cascading at Factory                                                                                              |

| 12     | PLL1 Enable                                             | Check box enable/disable the PLL                                                                                                               |

| 13     | Source Selector                                         | This would select the Source for the Output Divider 1 and 4                                                                                    |

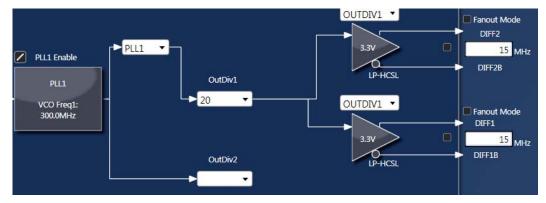

| 14     | OutDiv1                                                 | This is used to configure the value of Output Divider                                                                                          |

| 15     | Driver                                                  | Opens the configuration window for the given driver output                                                                                     |

| 16     | Output Divider                                          | Selects the Output Divider                                                                                                                     |

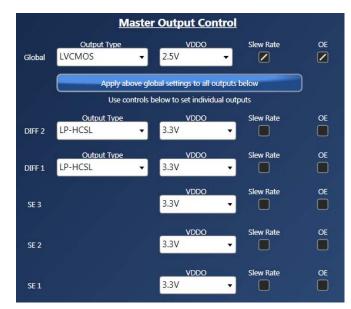

| 17     | Master Output Control                                   | Open the Master output control window                                                                                                          |

| 18     | User Guide                                              | Link to the user guide                                                                                                                         |

| 19     | Stop Ref                                                | Enables the output when checked. Disables the output when unchecked                                                                            |

| 20     | Fanout Mode                                             | Enables the buffer mode                                                                                                                        |

| 21     | Fraction Enable/Disable (Fraction Box)                  | Sets the Fractional part of the Output Frequency                                                                                               |

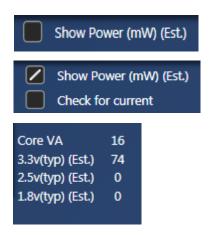

| 22     | Show Power (mW) (Est.) (Estimated<br>Power Consumption) | Shows estimate number for current consumption                                                                                                  |

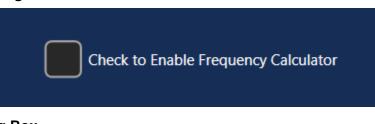

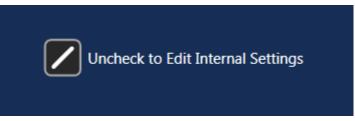

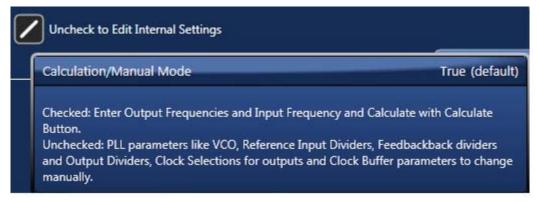

| 23     | Calculation/Manual Mode                                 | Check to Enable Frequency Calculator<br>Uncheck to Edit Internal Settings - Manual Mode<br>Frequency Calculator is disabled during Manual Mode |

\* Do not burn the part with Reset.

# 6 PLL1 Block

By clicking on the PLL1 block, the user can get access to the Reference Divider, Voltage Controlled Oscillator and the Spread Spectrum for the given PLL (refer to Figure 12 below). The VCO block specifies the minimum, and the maximum frequency that can be configured.

# Figure 12. Internal Block of PLL1

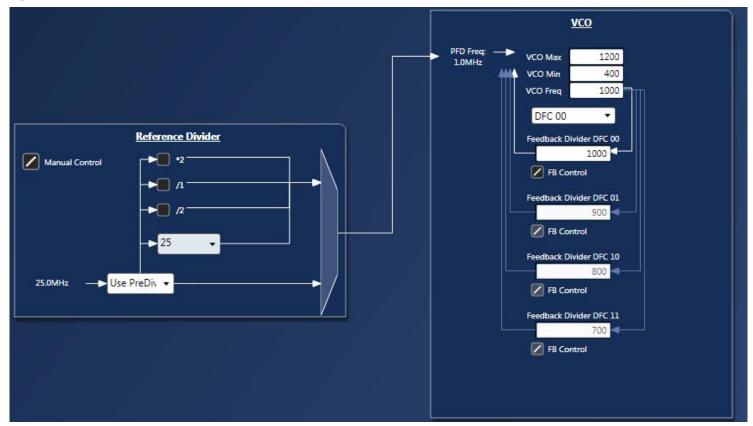

## a. Reference Divider

By clicking PLL block the user can get access to the Reference Divider diagram, in which the divider settings can be adjusted by the given manual check box. By default, Timing Commander bypasses the pre-divider for wider PFD frequency that improves performance.

#### Figure 13. Reference Divider

|                | Reference Divider |     |

|----------------|-------------------|-----|

| Manual Control | *2                | i N |

| Max PFD MHz    | → <b>□</b> /1     | ┝━► |

| 150            | → <b>1</b> 2      |     |

| 1              | ▶ 25 -            |     |

| 25.0MHz — Вур  | ass Pre 👻         |     |

## b. Spread Spectrum

The 5P35023 and 5P35021 supports Spread Spectrum clocks from PLL1 and PLL2; the PLL1 built-in with Analog spread spectrum and PLL2 has Digital spread spectrum. Please note that the primary spread amount used is down spread -0.5%.

#### Figure 14. Spread Spectrum (PLL1)

| Enable Spread         | SS KHz                   | ( s    | 31.5 | Real SS KHz (Obtained) |

|-----------------------|--------------------------|--------|------|------------------------|

| Post Divide by 2 or 3 | Total Spread %<br>SS Dir | 0.5%   | •    | ss fb div              |

|                       |                          | spiced |      |                        |

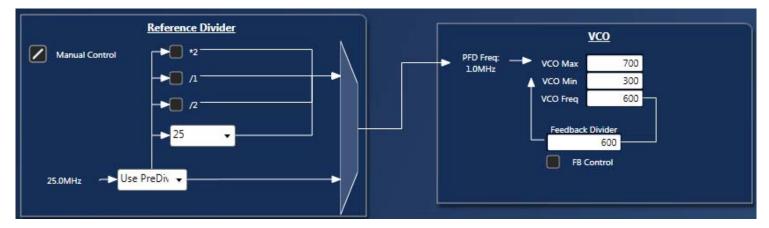

# 7 PLL2 Block

By clicking on the PLL2 block, the user can get access to Reference Divider and the Voltage Controlled Oscillator. The VCO block specifies the minimum, and the maximum frequencies. **Note:** The Reference divider for PLL2 can only be an integer between 1 and 31.

#### Figure 15. Phase Locked Loop (PLL2)

VC3S can either be programmed with its digital frequency control (DFC) mode enabled or with a single frequency configuration (DFC 00). In DFC mode, 4 different feedback divider values can be programmed and subsequently selected for 4 different frequency options. In Non-DFC mode, only DFC 00 is used.

When DFC mode is used, FB control for DFC00 must be checked. This will ensure to preserve the divider value DFC 00 while changing the remaining others. Not doing so, would replace DFC 00 value with the newly selected DFC divider value. All other DFC's by default have FB Control locked, so you can shift your DFC modes easily.

After you program different DFC's for different frequencies, you should come back to DFC 00 and then can proceed to OTP Burn. When you Readback, make sure the DFC 00 FB Control is checked in (enable), otherwise, the DFC Feedback divider values would not be shown.

#### Illustrating Example of DFC use in GUI:

• DFC 00: For example, 1000

If you wish to use other DFC's then CHECK the FB CONTROL for DFC 00. Change selection - DFC 00 to DFC 01 as shown in Figure 15.

• DFC 01: For example, 900

FB Control for DFC 01 is CHECKED by default (If not, check it). Change selection - DFC 01 to DFC 10 as shown in Figure 15.

• DFC 10: For example, 800

FB Control for DFC 10 is CHECKED by default (If not, check it). Change selection - DFC 10 to DFC 11 as shown in Figure 15.

#### • DFC 11: For example, 700:

FB Control for DFC 11 is CHECKED by default (If not, check it). Change selection - DFC 11 to DFC 00 after you program your DFC's and keep the FB Control for DFC 00 CHECKED.

#### Readback for DFC:

If the Part if burned with DFC's other than DFC 00(which is not part of regular DFC Mode), then the moment part is connected to Timing Commander, then a Green Light indicating DFC mode is shown (if the part is burned). If there is no indication or the green light has not been shown, then the part isn't burned with DFC 01, 10, 11 in use.

Once the Green Light indicates that the VC3S Chip is burned with DFC, then Open the internal settings and go to PLL2 DFC Options, and CHECK the FB Control for DFC 00 before Reading Back the part - otherwise, DFC 01, 10, 11 divider values would not be shown and replaced by DFC 00 divider values. If any of the DFC 01, 10, or 11's FB Controls are not checked-in before Reading Back, then your Readback values for DFC Feedback dividers may be not correct. So, always keep checked (enable) the feedback divider values inside PLL2 for a DFC Readback.

## DCO

It is disabled and represents the DCO settings which are factory reserved settings

#### 8 PLL3 Block

By clicking on the PLL3 block, the user can get access to Reference divider, and the voltage controlled oscillator. The VCO block specifies the minimum, and the maximum frequencies, different from one PLL to another. PLL3 does not support Spread Spectrum Clocking (SSC) functionality. **Note:** The Reference divider for PLL2 can only be an integer between 1 and 63.

#### Figure 16. Phase Locked Loop (PLL3)

## 9 Input Clock Selection

Input source can be set to crystal or an external reference clock, using the check box as shown in the figure below. When using the crystal, uncheck the box and the XTAL MHz block will be activated. In this case the crystal input frequency can go up to 40MHz and the internal load capacitors can be used.

When using the external clock, check the box and the XTAL MHz block will gray out indicating that CLKIN path is enable. The specified external clock input frequency can go up to 125MHz.

# Figure 17. Input Clock Selection

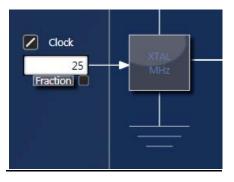

**a.Internal Capacitance Configuration** - VC3S Personality has built in capacitance for crystal load capacitance tuning. In XTAL Configuration window (Figure 18), X1 and X2 represent the capacitance the device can add to each leg of the crystal. The user can enter the value of the XTAL CL indicated by the Xtal manufacturer. Timing Commander will calculate the necessary values for the internal capacitors.

XTAL[3:0] = (XTAL CL - 5pF) \* 2

The parallel tuning capacitance can be set between 5pF to 12.5pF with a resolution of 0.5pF.

More device programming details can be found in the VC3S Register programming guide.

When the X1 is overdriven, Timing Commander sets the load capacitances to their minimum values.

## Figure 18. XTAL Capacitance Value Configuration

# **10 Fraction Box**

The user is encouraged to enter fractional frequency values as in fractional format shown below. This is done by checking the Fraction box checkbox. The calculate button causes the final frequency to be displayed.

# Figure 19. Input and Output Frequency Fraction Box

# **11 Output Dividers**

Upon clicking the Output Divider window, The OutDivx drop down box provides various integer values, which can be used to generate a particular frequency. For example, The VCO in PLL1 is limited from 300 MHz to 700 MHz, and if output frequency needs to be 15 MHz, then the VCO Frequency has to be set at 300 MHz with the OutDiv of 20. Timing Commander also provides flexibility with the ability to choose between multiple Output Dividers for different output frequencies.

# Figure 20. Output Divider

# **12 Output Configuration**

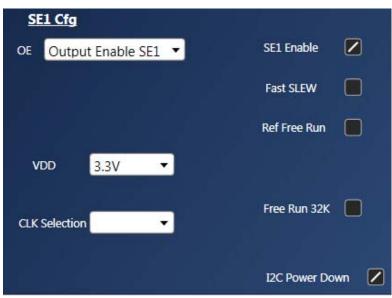

Upon clicking the driver sign, Timing Commander opens the window as shown in figure 23 and 24 which can be used to do further configuration for the respective outputs. The outputs types are further described in the summary view chapter. Refer to Table 2 and Table 3 for further configuration.

Figure 21. Differential Output – 2 (Diff-2)

| <u>Diff2 Cfg</u>  |              |           | D1FF2 Enable                 |  |

|-------------------|--------------|-----------|------------------------------|--|

| Output Type       | LP-HCSL      | •         | Fast CMOS SLEW<br>Flip CMOS2 |  |

| VDDO 2            | 3.3V         | •         |                              |  |

| CLK Selection     | OUTDIV1      | •         |                              |  |

| Amplitude Control | LVPECL:710mV | •         |                              |  |

|                   |              | Power Dov | vn DIFFx Outputs             |  |

# Figure 22. Single-ended Ouput – 1

# **13 Master Output Control Window**

This window allows defining global settings that can be applied to all the outputs at once with the single click. For the slew rate, the check button selects between the two available settings: Fast (checked), Slow (Unchecked).

Figure 23. Master Output Control Window

# **14 Estimated Power Consumption**

Checking the box called Show Power will show an estimated current consumption for every output and the core current consumption in mA (see Figure 24).

## Figure 24. Power Estimator Box

# **15 Special Options**

By checking the special option box in the left bottom corner, "Current Regs to Clipboard", "Restore Defaults" and "PCiE Opt" buttons will appear in active status.

# Figure 25. Special Options

Restore Defaults button enable to restore the default values into the device.

The **Current Regs to Clipboard** button copies all the current register values from one configuration to the clipboard. A message will pop up to confirm that the specific configuration register has been copied to the clip board. It consists of one line of string

containing register values in hexadecimal.

# 16 Calculation/Manual Mode

Checked: Frequency can be Calculated by Entering Output Frequencies.

**Unchecked**: Internal Settings can be edited like PLL Parameters - VCO, Feedback dividers, Reference Dividers, and Output Dividers and there selections to Outputs.

#### Figure 26. Unchecked Dialog Box

## Figure 27. Checked Dialog Box

#### Figure 28. Calculation/Manual Mode Dialog Box

# **17 Enter Project Details**

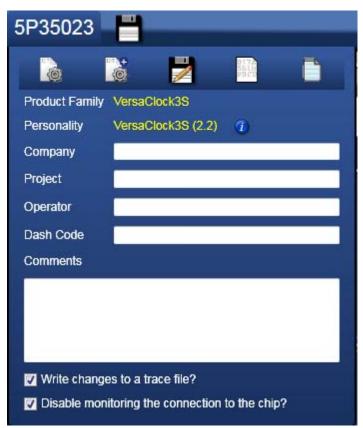

By clicking on the Versaclock3S part number, a window will pop up where many things can be done like open settings file, new settings file, save as, and also enter project details. These should be filled out for proper documentation.

# Figure 29. Project Details Information and File Tools

|                    |                        | Save as Button                   |                                                    |

|--------------------|------------------------|----------------------------------|----------------------------------------------------|

|                    | Save Button            | Dump register values into a text |                                                    |

| New Settings file  | 5P35023 💾              |                                  |                                                    |

| Open Settings file |                        |                                  | Summary File – Displays<br>Input & Output settings |

|                    | Product Family Versa   |                                  |                                                    |

|                    | Personality<br>Company | 0                                |                                                    |

|                    | Project                |                                  |                                                    |

|                    | Operator               |                                  |                                                    |

|                    | Dash Code<br>Comments  |                                  |                                                    |

|                    |                        |                                  |                                                    |

|                    |                        |                                  |                                                    |

|                    | Vrite changes to a t   |                                  |                                                    |

|                    | Disable monitoring t   | he connection to the chip?       |                                                    |

# 18 Save the Settings File

After the configuration is complete, click on the disk symbol at the upper left corner to save the setting file, as shown below.

# Figure 30. Save the Settings File

| JIDT Timing Commander | PRODUCT DATABASE BUT I NAME |

|-----------------------|-----------------------------|

| 5P35023               |                             |

|                       | Save Settings File Diagram  |

|                       | Q                           |

# **19 Connecting to the Chip**

If a VersaClock 3S evaluation board is connected, the settings can be written to the chip registers through I2C interface. In GUI software, the connection to the chip can be made by clicking on the round button at upper right corner of the GUI, as shown in Figure 31.

Connection Settings

Cancel

OK

Connection Interface

Onboard USB (I2C)

•

I2C Slave Address

D4,D0

Figure 31. Connection Settings for Connecting to the Chip

Use the default values in Connection Settings window and click OK to close it. Then click the chip symbol in the corner to bring out read/write command. When the connection is functioning, the area will turn green with "read" or "write" indicators. See Figure 32. The arrow pointing out of the chip means "reading from the chip"; the arrow pointing into the chip means "writing to the chip".

#### Figure 32. Read from or Writing to Device Registers

If the TC session is a used one, then a Reset (Reset from main page option) is needed before reading back the chip. If the chip is DFC Burned, then the FB Control of the DFC 00 in PLL2 has to be checked in to observe different DFC Values.

# 20 OTP Programming

When a configuration is ready for programming, the chip can be programmed right within the Timing Commander GUI software. Clicking on the OTP button will bring up OTP programming window in which the user can select the OTP Burn either on Evaluation board or on Programming board. Figure 34 shows the OTP programming window.

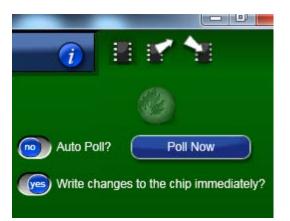

Steps to program a device:

- 1. Enter Output Frequencies

- 2. Calculate

- 3. Connect

4.Recommended Setting: Check (Enable) "Disable Monitoring the connection to the chip" - Figure 35 for reference

- 5.Recommended Setting: Set Auto Poll to "NO" Figure 36 for reference

- 6. Write All

- 7. Proceed to OTP Burn to burn the chip (cannot be reverted back)

- 8. Disconnect

- 9. Next Set of Output Frequencies can be entered and calculated

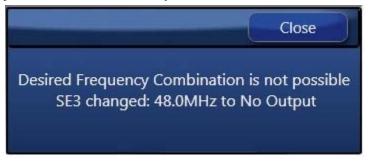

If the Desired Frequency combination is not possible, a pop-up would display that particular Output Frequency has turned to No Output.

## Figure 33. Output Frequency has Turned to No Output Window

# Figure 34. OTP Programming within Timing Commander GUI

|                            |   | OTP Burn                                     |                                   |

|----------------------------|---|----------------------------------------------|-----------------------------------|

| DFC 00 Mode                |   |                                              |                                   |

| DFC 01 Mode                |   | Click for OTP Burn on Eval Board             | Click for OTP - Eval Board        |

| DFC 10 Mode                |   | Click for OTP Burn on Programming Board      | Click for OTP - Programming Board |

| DFC 11 Mode                | _ |                                              |                                   |

| DFC All Modes              |   |                                              |                                   |

|                            |   |                                              |                                   |

|                            |   |                                              |                                   |

|                            |   | OTP Burn                                     |                                   |

| DFC 00 Mode                |   | <u>OTP Burn</u>                              |                                   |

| DFC 00 Mode<br>DFC 01 Mode |   | OTP Burn<br>Click for OTP Burn on Eval Board | Click for OTP - Eval Board        |

|                            |   |                                              |                                   |

| DFC 01 Mode                |   | Click for OTP Burn on Eval Board             |                                   |

Check for different DFC's that needs to be programmed/burned.

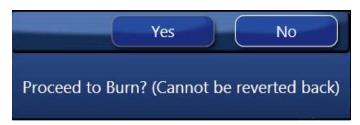

Upon clicking, "Click for OTP - Eval board", or "Click for OTP - Programming board", a confirmation window will pop up, Once the user selects "Yes", the Burn is permanent and cannot be reverted back. Figure 35 shows the confirmation window.

## Figure 35. Disable Monitoring the Connection to the Chip

Figure 36. Set Auto Poll to "No"

## Figure 37. Burn Confirmation Window

Please, note that the user needs to apply a +6.5V on VPROG (VPP) in order to burn the part. Without a +6.5V the part cannot be burned. Use the following figures to locate the VPROG (VPP) on the Evaluation board.

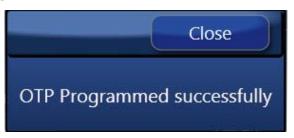

## Figure 38. Confirmation Message after OTP Burn

Note: Refer the Programming board manual for the OTP burn (for programming board)

# 21 PPM

PPM values are calculated and displayed as shown in the Figure 39.

# 22 Summary File

A Summary file can be generated to maintain a record of information for a future used. To generate a summary file click on the 5P35023 button, and clicking on the notepad button will generate the summary file for 5P35023.

#### Figure 40. Generating the Summary File

| 🔓 Tin | ning Commander (                                                             | Internal)                                            |          | and B from                    | ·C              |        |

|-------|------------------------------------------------------------------------------|------------------------------------------------------|----------|-------------------------------|-----------------|--------|

|       | 5P35023                                                                      | -                                                    |          |                               |                 |        |

|       | Product Family<br>Personality<br>Company<br>Project<br>Operator<br>Dash Code | VersaClock3S<br>VersaClock3S (0.21*)                 | 0        | Bit Se<br>y summary           | of the sett     | ings   |

|       |                                                                              | ges to a trace file?<br>nitoring the connection to t | he chip? | S<br>E<br>3<br>19<br>18<br>17 | DIFF1<br>DIFF1B | 100 MH |

## Figure 41. Summary File Example

| IDT Timing Commander Settings<br>Personality/Version: 5P35023 v1<br>Created: 2016-05-27 08:49:55                         |                                                                  |                                                                                        |                                                                                                        |                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| Part: 5P35023<br>Product Family: VersaClock 3S<br>Company name:<br>Project Name<br>Oper ator:<br>Dash Code:<br>Comments: |                                                                  |                                                                                        |                                                                                                        |                                                                                                        |

| Device I2C address: D0                                                                                                   |                                                                  |                                                                                        |                                                                                                        |                                                                                                        |

| Configuration<br>Input frequency:25.0 MHz<br>Input Source: Crystal                                                       |                                                                  |                                                                                        |                                                                                                        |                                                                                                        |

| CLKS OUTput Frequencies<br>Diff1 100.000000<br>Diff1 100.000000<br>5E3 60.00000<br>SE2 48.000000<br>5E1 0.032768         | OUTPUT Types<br>LP-HCSL<br>LP-HCSL<br>LVCMOS<br>LVCMOS<br>LVCMOS | Vddo(V) Slew PLL<br>3.3 PLL1<br>3.3 PLL2<br>3.3 Slow PLL1<br>3.3 Slow PLL3<br>3.3 Slow | VC0(MHZ) OUTDIV<br>600.000000 OUTDIV<br>1000.000000 OUTDIV<br>600.000000 OUTDIV2<br>480.000000 OUTDIV5 | spread                                                                                                 |

| OE1: Output Enable for SE1<br>OE2: Output Enable for SE2<br>OE3: Output Enable for SE3                                   |                                                                  |                                                                                        |                                                                                                        |                                                                                                        |

|                                                                                                                          |                                                                  |                                                                                        |                                                                                                        | A 18 1C 1D 1E 1F 20 21 22 23 24 25 26 27 28 29 2A<br>9 37 3F 30 10 86 80 80 F0 70 84 7D 69 E1 00 00 00 |

# **VersaClock 3S Derivative Parts**

Additional Derivative VersaClock3S parts are now available; to program them they can be selected from the drop down menu. To the right, you can find a description of the part.

Figure 42. Drop Down Menu to Select Derivative Parts and Description of Part

## Figure 43. Main Block of 5P35021

As shown in Figure 43, the 5P35021 device Timing Commander window looks a lot like the 5P35023 device window, all buttons and functionality are identical - the only difference is the output and number of outputs.

## Figure 44. Internal Block of 5P35021

# **Getting Further Help**

IDT Timing Commander Software is designed to be used interactively. Context-sensitive "tooltips" will appear when the mouse pointer is hovered-over any icon or entry box on the screen. These tooltips will provide information on what function the icon performs and/or limits on values that can be entered into the field. Figure 45 shows an example of such a tooltip indicating an output frequency field when the mouse pointer is hovering over it.

Figure 45. Tooltip Appears when the Mouse Pointer is Hovering Over any Block in the Window

|                  |   |                          | 100.0       | ) MHz            |                     |                     |           |              | Inp            | ut Clocks | Source<br>Crystal 🗸 | Frequency (M | (Hz)     |       |                               |        |

|------------------|---|--------------------------|-------------|------------------|---------------------|---------------------|-----------|--------------|----------------|-----------|---------------------|--------------|----------|-------|-------------------------------|--------|

|                  |   | D                        | D           |                  | D                   | D                   |           |              |                | Enable    | Frequency (MH:      | z) Sig       | nal Type | VDDO  | Spread Spectru                | IM РРМ |

|                  |   | D<br>VI<br>SF<br>SF<br>2 | F<br>F<br>2 | F<br>2<br>B      | VI<br>DF<br>DF<br>2 | D<br>VI<br>SF<br>SF |           |              | Differential 1 |           | 100                 | LP-H         | CSL 🗸    | 3.3V  | Disable                       | • 0    |

|                  | 0 | 20                       | 2<br>19     | 18               | 2<br>17             | 1<br>16             |           |              | Differential 2 |           | 100                 | LP-H         | CSL 🗸    | 3.3V  | - Disable                     | • 0    |

| 1004             |   |                          |             |                  |                     |                     |           |              | Single Ended 1 |           | 0.032768            |              | VCMOS    | 3.3V  | <ul> <li>No Spread</li> </ul> | 0      |

| VDDA             |   |                          | _           |                  |                     |                     |           | — 100.0 MHz  |                |           | Calculate           | Optimization | Options  | Reset | Restore to Default            | ٦      |

| SDA/DFC0         |   |                          |             | T5P3502          |                     |                     | 14 DIFF1B |              |                |           |                     |              |          |       |                               |        |

| SEL_DFC/SCL_DFC1 |   |                          |             |                  |                     |                     | 13 VDDDI  |              |                |           |                     |              |          |       |                               |        |

| CLKINB/X2        | 4 |                          |             |                  |                     |                     | 12 OE1 as | SE1          |                |           |                     |              |          |       |                               |        |

| CLKIN/X1         | 5 |                          |             |                  |                     |                     | 11 SE1    | 0.032768 MHz |                |           |                     |              |          |       |                               |        |

|                  |   | 6                        | 7           | 8                | 9                   | 10                  |           |              |                |           |                     |              |          |       |                               |        |

|                  |   | V<br>B<br>A<br>T         | > s<br>s    | V<br>D<br>3<br>3 | VS<br>SE<br>S1      | VS<br>DE<br>D1      |           |              |                |           |                     |              |          |       |                               |        |

The **About** icon on the top-right corner of the screen (blue button with a letter "i") can be used to generate an E-mail to IDT for assistance (See Figure 46), including the option to attach a log file that provides IDT with information on the sequence of operations performed by the user in this session to assist in resolving the user's concern.

## Figure 46. From About icon, an E-mail can be Generated to IDT with Option of Attaching a Log File

| About |                                                                                                          |                   | Close |

|-------|----------------------------------------------------------------------------------------------------------|-------------------|-------|

|       | IDT Timing Comman<br>Software Version 1.7<br>Build date: 06/10/2016 14:17:<br>Contact IDT: TimingCommand | 40                |       |

|       | Personality: VersaClock3S [V                                                                             | C3S1] version 3.0 |       |

| XX.   | C C C C C C C C C C C C C C C C C C C                                                                    |                   | ×     |

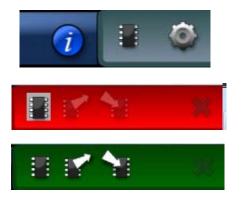

# **Icons Descriptions**

## Main Screen Icons

**About** – This icon allows the user to see the version numbers of the IDT Timing Commander Software and the personality currently in use. It also allows the user to contact IDT via Email, with or without attaching a log file to assist in resolution of any issues.

**Error Tab** – Indicates one or more errors are present. Click on this icon to open the Error/Warning Panel if it is not open.

**Warning Tab** – Indicates one or more errors are present. Click on this icon to open the Error/Warning Panel if it is not open.

Connection Setup – Clicking on this icon will allow setup of Chip Connect parameters.

**Chip Connect** – Clicking on this icon will cause an attempt to establish a connection with a device in a USB-attached evaluation board (EVB). The device will be tested to determine if it is the device referred to in this personality or not.

**Write to Chip** – Clicking on this icon when located in the top-right corner of the screen will write all registers values to the chip. Clicking on this icon beside a register in Register View will write out only that register to the connected chip.

**Read from Chip** – Clicking on this icon when located in the top-right corner of the screen will read all register values from the chip and replace the internal bit set Values with them, even if they are locked. Clicking on the icon beside a register in Register View will read only this register's Value.

# Icons Associated with Data Entry Boxes

Error – There is an error associated with the field this icon is attached to. Hovering over the field with the mouse will bring up a tooltip with more details on the error. The error can also be viewed via the Error/Warning Panel portion of the screen (Error/Warning Panel may need to be expanded by clicking on the Error or Warning tab). Note that a Settings file may not be saved while there are unsolved errors.

**Warning** – There is a warning associated with the field this icon is attached to. Hovering over the field with the mouse will bring up a tooltip with more details on the warning. The warning can also be viewed via the Error/Warning Panel portion of the screen (Error/Warning Panel may need to be expanded by clicking on the Error or Warning tab). Warnings do not prevent saving of a Settings file.

**Modified** – Alerts the user that the value in this field has been modified, either by the user or by the personality from its original value. Clicking on this icon will return the Value to the previous setting and remove the alert.

Revert - When this icon is clicked the state will revert back to the previous setting or value entered in the field.

## **Types of Data Entry Boxes**

Check Box – This data entry format is used for binary values that may only be set to 0 (box cleared) or 1 (box checked).

000010000

**Bit-by-bit** – This data entry format is used when it makes most sense to set each bit individually. Each bit may be set to 1 or 0 only.

Cfg 1 🔹

2

**Combo Box** – This data entry format provides a drop-down menu of selections. Selection values may be fixed or may be adjusted by the personality in response to other fields changing.

**Text Entry** – This data entry format allows direct keyboard entry of values. Values will be checked against the programmed data type for the field as they are typed.

**Read-Only** – This field is read-only. It may not be accessible to the user at all or may have a writable version at another (single) location in the diagram or bit set views.

# Notice

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information.

- Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall be responsible for determining what licenses are required from any third parties, and obtaining such licenses for the lawful import, export, manufacture, sales, utilization, distribution or other disposal of any products incorporating Renesas Electronics products, if required.

- 5. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- 6. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 7. No semiconductor product is absolutely secure. Notwithstanding any security measures or features that may be implemented in Renesas Electronics hardware or software products, Renesas Electronics shall have absolutely no liability arising out of any vulnerability or security breach, including but not limited to any unauthorized access to or use of a Renesas Electronics product or a system that uses a Renesas Electronics product. RENESAS ELECTRONICS DOES NOT WARRANT OR GUARANTEE THAT RENESAS ELECTRONICS PRODUCTS, OR ANY SYSTEMS CREATED USING RENESAS ELECTRONICS PRODUCTS WILL BE INVULNERABLE OR FREE FROM CORRUPTION, ATTACK, VIRUSES, INTERFERENCE, HACKING, DATA LOSS OR THEFT, OR OTHER SECURITY INTRUSION ("Vulnerability Issues"). RENESAS ELECTRONICS DISCLAIMS ANY AND ALL RESPONSIBILITY OR LIABILITY ARISING FROM OR RELATED TO ANY VULNERABILITY ISSUES. FURTHERMORE, TO THE EXTENT PERMITTED BY APPLICABLE LAW, RENESAS ELECTRONICS DISCLAIMS ANY AND ALL WARRANTIES, EXPRESS OR IMPLIED, WITH RESPECT TO THIS DOCUMENT AND ANY RELATED OR ACCOMPANYING SOFTWARE OR HARDWARE, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY, OR FITNESS FOR A PARTICULAR PURPOSE.

- 8. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for systems manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions.

- 12. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 13. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 14. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

- (Note1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries.

- (Note2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Disclaimer Rev.5.0-1 October 2020)

# **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

# Contact Information

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: <a href="http://www.renesas.com/contact/">www.renesas.com/contact/</a>

# Trademarks

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.