#### 2 OUTPUT PCIE GEN1/2/3 SYNTHESIZER

5V41235

#### **Recommended Applications**

2 Output synthesizer for PCIe Gen1/2/3 and Ethernet

# **General Description**

The 5V41235 is a PCIe Gen2/3 compliant spread spectrum capable clock generator. The device has 2 differential HCSL outputs and can be used in communication or embedded systems to substantially reduce electro-magnetic interference (EMI). The spread amount and output frequency are selectable via select pins. The 5V41235 can also supply 25 MHz, 125 MHz and 200 MHz outputs for applications such as Ethernet.

## **Output Features**

2 - 0.7V current mode differential HCSL output pairs

#### Features/Benefits

- 16-pin TSSOP and QFN packages; small board footprint

- Spread-spectrum capable; reduces EMI

- Outputs can be terminated to LVDS; can drive a wider variety of devices

- TSSOP package: 25MHz, 100MHz, 125MHz and 200MHz output frequencies.

- QFN package: 100MHz and 200MHz output frequencies.

- OE control pin; greater system power management

- Spread% and frequency pin selection; no software required to configure device

- Industrial temperature range available; supports demanding embedded applications

## **Key Specifications**

- Cycle-to-cycle jitter < 100 ps

- Output-to-output skew < 50 ps

- PCIe Gen2 phase jitter < 3.0ps RMS

- PCle Gen3 phase jitter <1.0ps RMS

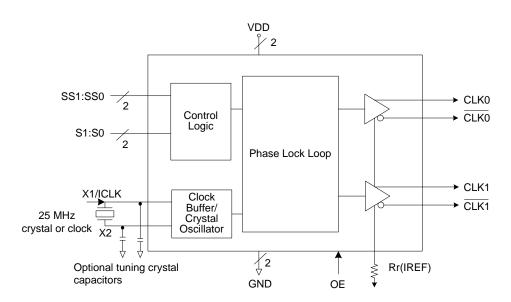

# **Block Diagram**

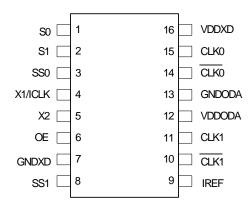

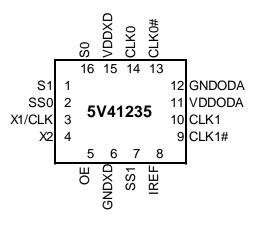

# **Pin Assignments**

16-pin (173 mil) TSSOP

#### Output Select Table 1 (MHz) - TSSOP Only

| S1 | S0 | CLK(1:0), CLK(1:0) |

|----|----|--------------------|

| 0  | 0  | 25M                |

| 0  | 1  | 100M               |

| 1  | 0  | 125M               |

| 1  | 1  | 200M               |

#### **Spread Selection Table 2 - TSSOP Only**

| SS1 | SS0 | Spread%    |

|-----|-----|------------|

| 0   | 0   | No Spread  |

| 0   | 1   | Down -0.5  |

| 1   | 0   | Down -0.75 |

| 1   | 1   | No Spread  |

16-pin QFN

#### **Output/Spread Select Table 3 - QFN Only**

| S1 | S0 | SS1 | SS0 | Output           | Spread%   |  |

|----|----|-----|-----|------------------|-----------|--|

| 0  | 0  | 0   | 0   | 100MHz           | -0.5      |  |

| 0  | 0  | 0   | 1   | 200MHz           | -0.5      |  |

| 0  | 0  | 1   | 0   | 100MHz           | No spread |  |

| 0  | 0  | 1   | 1   | Res              | served    |  |

| 0  | 1  | 0   | 0   | 100MHz           | -1        |  |

| 0  | 1  | 0   | 1   | 200MHz           | -1        |  |

| 0  | 1  | 1   | 0   | Reserved         |           |  |

| 0  | 1  | 1   | 1   | Reserved         |           |  |

| 1  | 0  | 0   | 0   | 100MHz           | -1.5      |  |

| 1  | 0  | 0   | 1   | 200MHz           | -1.5      |  |

| 1  | 0  | 1   | 0   | Res              | served    |  |

| 1  | 0  | 1   | 1   | Res              | served    |  |

| 1  | 1  | 0   | 0   | Reserved         |           |  |

| 1  | 1  | 0   | 1   | 200MHz No spread |           |  |

| 1  | 1  | 1   | 0   | Reserved         |           |  |

| 1  | 1  | 1   | 1   | Res              | served    |  |

# **Pin Descriptions**

| QFN Pin | TSSOP  | Pin     | Pin    | Pin Description                                                                           |

|---------|--------|---------|--------|-------------------------------------------------------------------------------------------|

| Number  | Pin    | Name    | Type   |                                                                                           |

|         | Number |         |        |                                                                                           |

| 16      | 1      | S0      | Input  | Select pin 0. See Table1. Internal pull-up resistor.                                      |

| 1       | 2      | S1      | Input  | Select pin 1. See Table 1. Internal pull-up resistor.                                     |

| 2       | 3      | SS0     | Input  | Spread Select pin 0. See Table 2. Internal pull-up resistor.                              |

| 3       | 4      | X1/ICLK | Input  | Crystal or clock input. Connect to a 25 MHz crystal or single ended clock.                |

| 4       | 5      | X2      | Output | Crystal connection. Leave unconnected for clock input.                                    |

| 5       | 6      | OE      | Input  | Output enable. Tri-states outputs and device is not shut down. Internal pull-up resistor. |

| 6       | 7      | GNDXD   | Power  | Connect to ground.                                                                        |

| 7       | 8      | SS1     | Input  | Spread Select pin 1. See Table 2. Internal pull-up resistor.                              |

| 8       | 9      | IREF    | Output | Precision resistor attached to this pin is connected to the internal current reference.   |

| 9       | 10     | CLK1    | Output | HCSL complementary clock output 1.                                                        |

| 10      | 11     | CLK1    | Output | HCSL true clock output 1.                                                                 |

| 11      | 12     | VDDODA  | Power  | Connect to voltage supply +3.3 V for output driver and analog circuits                    |

| 12      | 13     | GNDODA  | Power  | Connect to ground.                                                                        |

| 13      | 14     | CLK0    | Output | HCSL complementary clock output 0.                                                        |

| 14      | 15     | CLK0    | Output | HCSL true clock output 0.                                                                 |

| 15      | 16     | VDDXD   | Power  | Connect to voltage supply +3.3 V for crystal oscillator and digital circuit.              |

# **Applications Information**

#### **External Components**

A minimum number of external components are required for proper operation.

#### **Decoupling Capacitors**

Decoupling capacitors of 0.01  $\mu F$  should be connected between each VDD pin and the ground plane, as close to the VDD pin as possible. Do not share ground vias between components. Route power from power source through the capacitor pad and then into ICS pin.

#### Crystal

A 25 MHz fundamental mode parallel resonant crystal should be used. This crystal must have less than 300 ppm of error across temperature in order for the 5V41235 to meet PCI Express specifications.

#### **Crystal Capacitors**

Crystal capacitors are connected from pins X1 to ground and X2 to ground to optimize the accuracy of the output frequency.

C<sub>I</sub> = Crystal's load capacitance in pF

Crystal Capacitors (pF) =  $(C_1 - 7) * 2$

For example, for a crystal with a 8pF load cap, each external crystal cap would be 2pF [(8-7)\*2=2].

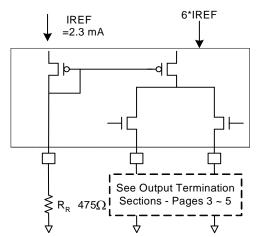

Current Source (Iref) Reference Resistor - RR

If board target trace impedance (Z) is  $50\Omega$ , then  $R_R$  =  $475\Omega$  (1%), providing IREF of 2.32 mA. The output current (I<sub>OH</sub>) is equal to 6\*IREF.

#### **Output Termination**

The PCI-Express differential clock outputs of the 5V41235 are open source drivers and require an external series resistor and a resistor to ground. These resistor values and their allowable locations are shown in detail in the **PCI-Express Layout Guidelines** section.

The 5V41235 can also be configured for LVDS compatible voltage levels. See the **LVDS Compatible Layout Guidelines** section.

## **Output Structures**

#### **General PCB Layout Recommendations**

For optimum device performance and lowest output phase noise, the following guidelines should be observed.

- 1. Each  $0.01\mu F$  decoupling capacitor should be mounted on the component side of the board as close to the VDD pin as possible.

- 2. No vias should be used between decoupling capacitor and VDD pin.

- 3. The PCB trace to VDD pin should be kept as short as possible, as should the PCB trace to the ground via. Distance of the ferrite bead and bulk decoupling from the device is less critical.

- 4. An optimum layout is one with all components on the same side of the board, minimizing vias through other signal layers (any ferrite beads and bulk decoupling capacitors can be mounted on the back). Other signal traces should be routed away from the 5V41235. This includes signal traces just underneath the device, or on layers adjacent to the ground plane layer used by the device.

# **Layout Guidelines**

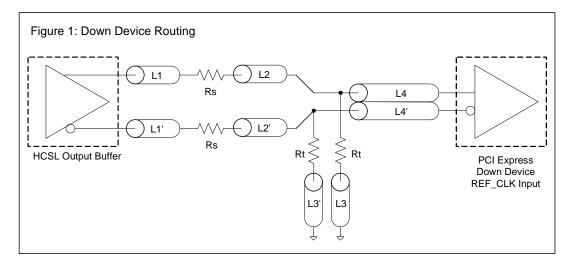

| SRC Reference Clock                             |                    |      |        |  |  |  |  |  |

|-------------------------------------------------|--------------------|------|--------|--|--|--|--|--|

| Common Recommendations for Differential Routing | Dimension or Value | Unit | Figure |  |  |  |  |  |

| L1 length, route as non-coupled 50ohm trace     | 0.5 max            | inch | 1      |  |  |  |  |  |

| L2 length, route as non-coupled 50ohm trace     | 0.2 max            | inch | 1      |  |  |  |  |  |

| L3 length, route as non-coupled 50ohm trace     | 0.2 max            | inch | 1      |  |  |  |  |  |

| Rs                                              | 33                 | ohm  | 1      |  |  |  |  |  |

| Rt                                              | 49.9               | ohm  | 1      |  |  |  |  |  |

| Down Device Differential Routing                                 |                     |      |   |

|------------------------------------------------------------------|---------------------|------|---|

| L4 length, route as coupled microstrip 100ohm differential trace | 2 min to 16 max     | inch | 1 |

| L4 length, route as coupled stripline 100ohm differential trace  | 1.8 min to 14.4 max | inch | 1 |

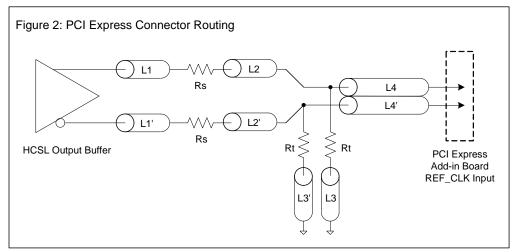

| Differential Routing to PCI Express Connector                    |                       |      |   |

|------------------------------------------------------------------|-----------------------|------|---|

| L4 length, route as coupled microstrip 100ohm differential trace | 0.25 to 14 max        | inch | 2 |

| L4 length, route as coupled stripline 100ohm differential trace  | 0.225 min to 12.6 max | inch | 2 |

5

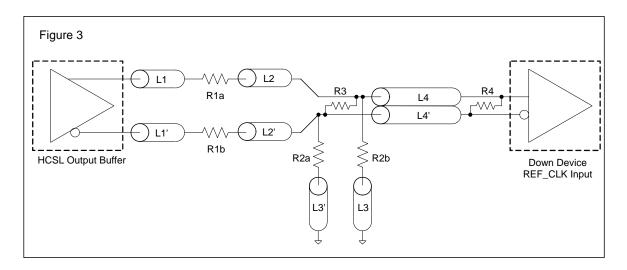

|                                 | Alternative Termination for LVDS and other Common Differential Signals (figure 3) |      |    |      |      |     |                                |  |  |

|---------------------------------|-----------------------------------------------------------------------------------|------|----|------|------|-----|--------------------------------|--|--|

| Vdiff Vp-p Vcm R1 R2 R3 R4 Note |                                                                                   |      |    |      |      |     | Note                           |  |  |

| 0.45 v                          | 0.22v                                                                             | 1.08 | 33 | 150  | 100  | 100 |                                |  |  |

| 0.58                            | 0.28                                                                              | 0.6  | 33 | 78.7 | 137  | 100 |                                |  |  |

| 0.80                            | 0.40                                                                              | 0.6  | 33 | 78.7 | none | 100 | ICS874003i-02 input compatible |  |  |

| 0.60                            | 0.3                                                                               | 1.2  | 33 | 174  | 140  | 100 | Standard LVDS                  |  |  |

R1a = R1b = R1R2a = R2b = R2

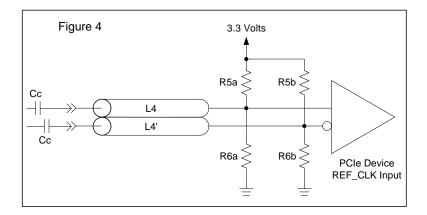

| Cable Connecte | Cable Connected AC Coupled Application (figure 4) |      |  |  |  |  |  |

|----------------|---------------------------------------------------|------|--|--|--|--|--|

| Component      | Value                                             | Note |  |  |  |  |  |

| R5a, R5b       | 8.2K 5%                                           |      |  |  |  |  |  |

| R6a, R6b       | 1K 5%                                             |      |  |  |  |  |  |

| Сс             | 0.1 μF                                            |      |  |  |  |  |  |

| Vcm            | 0.350 volts                                       |      |  |  |  |  |  |

6

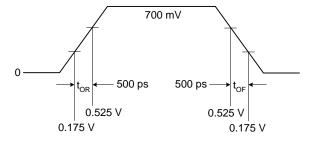

# Typical PCI-Express (HCSL) Waveform

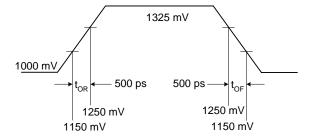

# **Typical LVDS Waveform**

# **Absolute Maximum Ratings**

Stresses above the ratings listed below can cause permanent damage to the 5V41235. These ratings are stress ratings only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods can affect product reliability. Electrical parameters are guaranteed only over the recommended operating temperature range.

| Item                                       | Rating              |

|--------------------------------------------|---------------------|

| Supply Voltage, VDDXD, VDDODA              | 4.6 V               |

| All Inputs and Outputs                     | -0.5 V to VDD+0.5 V |

| Ambient Operating Temperature (commercial) | 0 to +70°C          |

| Ambient Operating Temperature (industrial) | -40 to +85°C        |

| Storage Temperature                        | -65 to +150°C       |

| Junction Temperature                       | 125°C               |

| Soldering Temperature                      | 260°C               |

| ESD Protection (Input)                     | 2000 V min. (HBM)   |

# **DC Electrical Characteristics**

Unless stated otherwise, VDD = 3.3 V ±5%, Ambient Temperature -40 to +85°C

| Parameter                          | Symbol            | Conditions                                            | Min.    | Тур. | Max.     | Units |

|------------------------------------|-------------------|-------------------------------------------------------|---------|------|----------|-------|

| Supply Voltage                     | V                 |                                                       | 3.135   | 3.3  | 3.465    | V     |

| Input High Voltage <sup>1</sup>    | V <sub>IH</sub>   | S0, S1, OE, ICLK, SS0, SS1                            | 2.2     |      | VDD +0.3 | V     |

| Input Low Voltage <sup>1</sup>     | $V_{IL}$          | S0, S1, OE, ICLK, SS0, SS1                            | VSS-0.3 |      | 0.8      | V     |

| Input Leakage Current <sup>2</sup> | I <sub>IL</sub>   | 0 < Vin < VDD                                         | -5      |      | 5        | μΑ    |

| Operating Supply Current           | I <sub>DD</sub>   | $R_S$ =33 $\Omega$ , $R_P$ =50 $\Omega$ , $C_L$ =2 pF |         | 63   | 85       | mA    |

| @100 MHz                           | I <sub>DDOE</sub> | OE =Low                                               |         | 42   | 50       | mA    |

| Input Capacitance                  | C <sub>IN</sub>   | Input pin capacitance                                 |         |      | 7        | pF    |

| Output Capacitance                 | C <sub>OUT</sub>  | Output pin capacitance                                |         |      | 6        | pF    |

| X1, X2 Capacitance                 | C <sub>INX</sub>  |                                                       |         |      | 5        | pF    |

| Pin Inductance                     | L <sub>PIN</sub>  |                                                       |         |      | 5        | nΗ    |

| Output Impedance                   | Z <sub>O</sub>    | CLK outputs                                           | 3.0     |      |          | kΩ    |

| Pull-up Resistor                   | R <sub>PU</sub>   | S0, S1, OE, SS0, SS1                                  |         | 100  |          | kΩ    |

- 1. Single edge is monotonic when transitioning through region.

- 2. Inputs with pull-ups/-downs are not included.

# AC Electrical Characteristics - CLK0/CLK1, CLK0/CLK1

Unless stated otherwise, VDD=3.3 V ±5%, Ambient Temperature -40 to +85°C

| Parameter                               | Symbol              | Conditions                                       | Min. | Тур. | Max. | Units |

|-----------------------------------------|---------------------|--------------------------------------------------|------|------|------|-------|

| Input Frequency                         |                     |                                                  |      | 25   |      | MHz   |

| Output Frequency                        |                     | HCSL termination                                 | 25   |      | 200  | MHz   |

|                                         |                     | LVDS termination                                 | 25   |      | 100  | MHz   |

| Output High Voltage <sup>1,2</sup>      | V <sub>OH</sub>     | HCSL                                             |      |      | 850  | mV    |

| Output Low Voltage <sup>1,2</sup>       | V <sub>OL</sub>     | HCSL                                             | -150 |      |      | mV    |

| Crossing Point Voltage <sup>1,2</sup>   |                     | Absolute                                         | 250  |      | 550  | mV    |

| Crossing Point Voltage <sup>1,2,4</sup> |                     | Variation over all edges                         |      |      | 140  | mV    |

| Jitter, Cycle-to-Cycle <sup>1,3</sup>   |                     |                                                  |      |      | 100  | ps    |

| Frequency Synthesis Error               |                     | All outputs                                      |      | 0    |      | ppm   |

| Modulation Frequency                    |                     | Spread spectrum                                  | 30   | 32.9 | 33   | kHz   |

| Rise Time <sup>1,2</sup>                | t <sub>OR</sub>     | From 0.175 V to 0.525 V                          | 175  |      | 700  | ps    |

| Fall Time <sup>1,2</sup>                | t <sub>OF</sub>     | From 0.525 V to 0.175 V                          | 175  |      | 700  | ps    |

| Rise/Fall Time Variation <sup>1,2</sup> |                     |                                                  |      |      | 125  | ps    |

| Output to Output Skew                   |                     |                                                  |      |      | 50   | ps    |

| Duty Cycle <sup>1,3</sup>               |                     |                                                  | 45   |      | 55   | %     |

| Output Enable Time <sup>5</sup>         |                     | All outputs                                      |      | 50   | 100  | ns    |

| Output Disable Time <sup>5</sup>        |                     | All outputs                                      |      | 50   | 100  | ns    |

| Stabilization Time                      | t <sub>STABLE</sub> | From power-up VDD=3.3 V                          |      |      | 1.8  | ms    |

| Spread Spectrum Transition<br>Time      | t <sub>SPREAD</sub> | Stabilization time after spread spectrum changes | 7    |      | 30   | ms    |

- Note 1: Test setup is  $R_S=33\Omega$ ,  $R_P=50\Omega$  with  $C_I=2$  pF,  $R_I=475\Omega$  (1%).

- Note 2: Measurement taken from a single-ended waveform.

- Note 3: Measurement taken from a differential waveform.

- Note 4: Measured at the crossing point where instantaneous voltages of both CLK and CLK are equal.

- Note 5: CLK pins are tri-stated when OE is low asserted. CLK is driven differential when OE is high.

#### **Electrical Characteristics - Differential Phase Jitter Parameters**

| T <sub>A</sub> = Commercial and Indust | rial, Supply V            | SPEC                                       |     |      |     |             |       |  |

|----------------------------------------|---------------------------|--------------------------------------------|-----|------|-----|-------------|-------|--|

| PARAMETER                              | Symbol                    | Conditions                                 | Min | Тур  | Max | Units       | Notes |  |

|                                        | t <sub>jphaseG1</sub>     | PCIe Gen 1                                 |     | 28   | 86  | ps (p-p)    | 1,2,3 |  |

| Jitter, Phase                          | t <sub>jphaseG2Lo</sub>   | PCIe Gen 2<br>10kHz < f < 1.5MHz           |     | 0.7  | 3   | ps<br>(RMS) | 1,2,3 |  |

|                                        | t <sub>jphaseG2High</sub> | PCIe Gen 2<br>1.5MHz < f < Nyquist (50MHz) |     | 1.8  | 3.1 | ps<br>(RMS) | 1,2,3 |  |

|                                        | t <sub>jphaseG3</sub>     | PCIe Gen 3                                 |     | 0.48 | 1   | ps<br>(RMS) | 1,2,3 |  |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>&</sup>lt;sup>2</sup>See http://www.pcisig.com for complete specs

<sup>&</sup>lt;sup>3</sup>Applies to 100MHz, spread off and 0.5% down spread only.

# **Thermal Characteristics (16TSSOP)**

| Parameter                           | Symbol            | Conditions     | Min. | Тур. | Max. | Units |

|-------------------------------------|-------------------|----------------|------|------|------|-------|

| Thermal Resistance Junction to      | $\theta_{\sf JA}$ | Still air      |      | 78   |      | °C/W  |

| Ambient                             | $\theta_{\sf JA}$ | 1 m/s air flow |      | 70   |      | °C/W  |

|                                     | $\theta_{\sf JA}$ | 3 m/s air flow |      | 68   |      | °C/W  |

| Thermal Resistance Junction to Case | $\theta_{\sf JC}$ |                |      | 37   |      | °C/W  |

# **Thermal Characteristics (16QFN)**

| Parameter                           | Symbol            | Conditions     | Min. | Тур. | Max. | Units |

|-------------------------------------|-------------------|----------------|------|------|------|-------|

| Thermal Resistance Junction to      | $\theta_{\sf JA}$ | Still air      |      | 63.2 |      | °C/W  |

| Ambient                             | $\theta_{\sf JA}$ | 1 m/s air flow |      | 55.9 |      | °C/W  |

|                                     | $\theta_{\sf JA}$ | 3 m/s air flow |      | 51.4 |      | °C/W  |

| Thermal Resistance Junction to Case | $\theta_{\sf JC}$ |                |      | 65.8 |      | °C/W  |

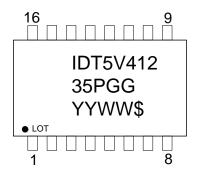

# Marking Diagram (5V41235PGG)

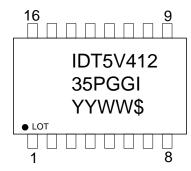

# Marking Diagram (5V41235PGGI)

#### Notes:

- 1. Line 1 and 2: IDT part number.

- 2. Line 3: YYWW Date code; \$ Assembly location.

- 3. "G" after the two-letter package code designates RoHS compliant package.

- 4. "I" at the end of part number indicates industrial temperature range.

- 5. Bottom marking: country of origin if not USA.

## Marking Diagram (5V41235NLGI)

# **Marking Diagram (5V41235NLGI)**

#### Notes:

- 1. Line 1: Lot number.

- 2. Line 2: YWW Date code; \$ Assembly location.

- 3. "G" designates RoHS compliant package.

- 4. "I" at the end of part number indicates industrial temperature range.

- 5. Bottom marking: country of origin if not USA.

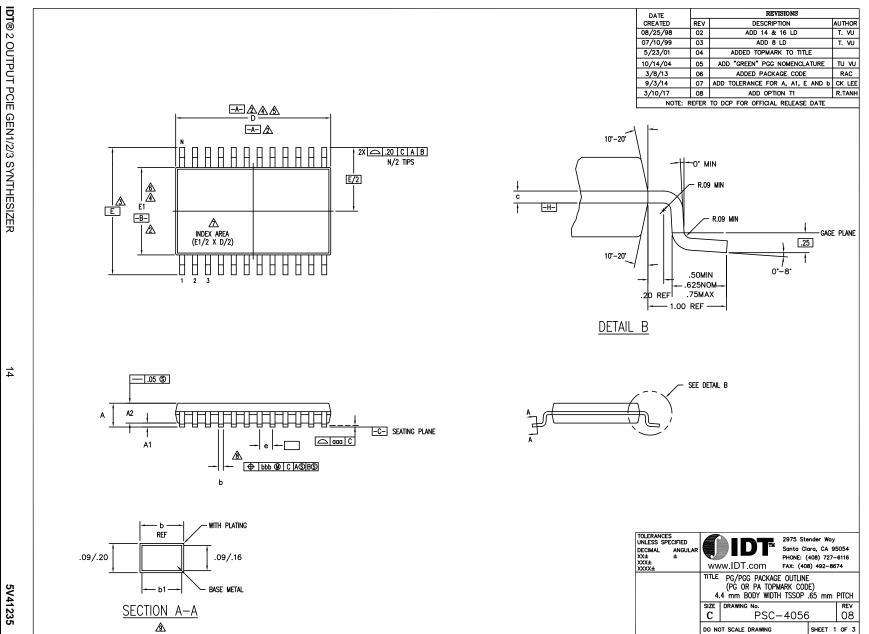

Package Outline and Package Dimensions (3)

×

ယ

mm 16-QFN)

IDT® 2 OUTPUT PCIE GEN1/2/3 SYNTHESIZER

#### REVISIONS DESCRIPTION DATE APPROVED 10/15/08 RC 00 INITIAL RELEASE COMBINE POD & LAND PATTERN 9/17/13 KS PIN #1 IDENTIFICATION 1.700±0.10 Exp. DAP Pin 1 Dot - 3.000±0.1 -By Marking 0.400±0.10 0.500 Bsc 1.700±0.10 Exp. DAP 3.000±0.10 0.23<u>0±0.05</u>0 0.400±0.050 1.500 Ref. TOP VIEW DM VIEW -0.900±0.10 0.20 REF 0.000-0.050 TOP VIEW 16LD QFN 3X3 (0.5MM PITCH) TOLERANCES UNLESS SPECIFIED 6024 Silver Creek Valley Road San Jose, CA 95138 ANGULAR ± DECIMAL ® PHONE: (408) 284-8200 XX± XXX± www.IDT.com FAX: (408) 284-8591 TITLE NL/NLG16 PACKAGE OUTLINE APPROVALS DATE DRAWN RAC 10/15/08 3.0 x 3.0 mm BODY CHECKED 0.5 mm PITCH QFN DRAWING No. C PSC-4169 01 DO NOT SCALE DRAWING SHEET 1 OF 2

IDT® 2 OUTPUT PCIE GEN1/2/3 SYNTHESIZER

#### Package Outline and Package Dimensions (3) REVISIONS APPROVED RC REV DESCRIPTION DATE 00 INITIAL RELEASE 10/15/08 COMBINE POD & LAND PATTERN 9/17/13 KS 01 3.80 2.20 .50 - .80 → .25 3.80 2.20 1.80 .50 .80 × 1.80 ယ mm 16-QFN), cont. NOTES: 1. ALL DIMENSION ARE IN mm. ANGLES IN DEGREES. 2. TOP DOWN VIEW. AS VIEWED ON PCB. 3. COMPONENT OUTLINE SHOW FOR REFERENCE IN GREEN. 4. LAND PATTERN IN BLUE. NSMD PATTERN ASSUMED. TOLERANCES UNLESS SPECIFIED 6024 Silver Creek Valley Road 5. LAND PATTERN RECOMMENDATION PER IPC-7351B GENERIC REQUIREMENT San Jose, CA 95138 ® PHONE: (408) 284-8200 DECIMAL XX± XXX± XXXX± ANGULAR FOR SURFACE MOUNT DESIGN AND LAND PATTERN. www.IDT.com FAX: (408) 284-8591 APPROVALS DATE DRAWN &AC 10/15/08 CHECKED TITLE NL/NLG16 PACKAGE OUTLINE 3.0 x 3.0 mm BODY 0.5 mm PITCH QFN SIZE DRAWING No. С PSC-4169 01 DO NOT SCALE DRAWING SHEET 2 OF 2

MAY 5, 2017

| DATE     |       | REVISIONS                        |        |  |  |  |  |  |  |  |

|----------|-------|----------------------------------|--------|--|--|--|--|--|--|--|

| CREATED  | REV   | DESCRIPTION                      | AUTHOF |  |  |  |  |  |  |  |

| 08/25/98 | 02    | ADD 14 & 16 LD                   | T. VU  |  |  |  |  |  |  |  |

| 07/10/99 | 03    | ADD 8 LD                         | T. VU  |  |  |  |  |  |  |  |

| 5/23/01  | 04    | ADDED TOPMARK TO TITLE           |        |  |  |  |  |  |  |  |

| 10/14/04 | 05    | ADD "GREEN" PGG NOMENCLATURE     | TU VU  |  |  |  |  |  |  |  |

| 3/8/13   | 06    | ADDED PACKAGE CODE               | RAC    |  |  |  |  |  |  |  |

| 9/3/14   | 07    | ADD TOLERANCE FOR A, A1, E AND b | CK LEE |  |  |  |  |  |  |  |

| 3/10/17  | 08    | ADD OPTION T1                    | R.TANH |  |  |  |  |  |  |  |

| NOTE: F  | REFER | TO DCP FOR OFFICIAL RELEASE DATE |        |  |  |  |  |  |  |  |

**Package**

Outline

and

**Package**

Dimensions (4.4

mm 16-TSSOP), cont.

2 OUTPUT PCIE GEN1/2/3 SYNTHESIZER

|             |      | PG/P     | GG8  |     |      | PG/PGG14 |      | PG/PGG16 |      |          | PG/PGG20 |     |      |          | PG/P | GG24 |      |          | PG/P | GG28 |      |          |      |     |

|-------------|------|----------|------|-----|------|----------|------|----------|------|----------|----------|-----|------|----------|------|------|------|----------|------|------|------|----------|------|-----|

| S<br>Y<br>M | JEDE | C VARIAT | ION  | 02  | JEDE | C VARIAT | ION  | N D      | JEDE | C VARIAT | ION      | N   | JEDE | C VARIAT | ION  | N    | JEDE | C VARIAT | ION  | N    | JEDE | C VARIAT | ION  | oz  |

| Ě           | MIN  | NOM      | MAX  | Ē   | MIN  | NOM      | MAX  | Ę        | MIN  | NOM      | MAX      | Ē   | MIN  | NOM      | MAX  | Ē    | MIN  | NOM      | MAX  | Ē    | MIN  | NOM      | MAX  | Ē   |

| Α           | .85  | 1.10     | 1.20 |     | .85  | 1.10     | 1.20 |          | .85  | 1.10     | 1.20     |     | .85  | 1.10     | 1.20 |      | .85  | 1.10     | 1.20 |      | .85  | 1.10     | 1.20 |     |

| A1          | .05  | .10      | .15  |     | .05  | .10      | .15  |          | .05  | .10      | .15      |     | .05  | .10      | .15  |      | .05  | .10      | .15  |      | .05  | .10      | .15  |     |

| A2          | .80  | 1.00     | 1.05 |     | .80  | 1.00     | 1.05 |          | .80  | 1.00     | 1.05     |     | .80  | 1.00     | 1.05 |      | .80  | 1.00     | 1.05 |      | .80  | 1.00     | 1.05 |     |

| D           | 2.90 | 3.00     | 3.10 | 4,5 | 4.90 | 5.00     | 5.10 | 4,5      | 4.90 | 5.00     | 5.10     | 4,5 | 6.40 | 6.50     | 6.60 | 4,5  | 7.70 | 7.80     | 7.90 | 4,5  | 9.60 | 9.70     | 9.80 | 4,5 |

| Ε           | 6.20 | 6.40     | 6.60 | 3   | 6.20 | 6.40     | 6.60 | 3        | 6.20 | 6.40     | 6.60     | 3   | 6.20 | 6.40     | 6.60 | 3    | 6.20 | 6.40     | 6.60 | 3    | 6.20 | 6.40     | 6.60 | 3   |

| E1          | 4.30 | 4.40     | 4.50 | 4,6 | 4.30 | 4.40     | 4.50 | 4,6      | 4.30 | 4.40     | 4.50     | 4,6 | 4.30 | 4.40     | 4.50 | 4,6  | 4.30 | 4.40     | 4.50 | 4,6  | 4.30 | 4.40     | 4.50 | 4,6 |

| е           |      | .65 BSC  |      |     |      | .65 BSC  |      |          |      | .65 BSC  |          |     |      | .65 BSC  |      |      |      | .65 BSC  |      |      |      | .65 BSC  |      |     |

| b           | .19  | .25      | .30  |     | .19  | .25      | .30  |          | .19  | .25      | .30      |     | .19  | .25      | .30  |      | .19  | .25      | .30  |      | .19  | .25      | .30  |     |

| b1          | .19  | .22      | .25  |     | .19  | .22      | .25  |          | .19  | .22      | .25      |     | .19  | .22      | .25  |      | .19  | .22      | .25  |      | .19  | .22      | .25  |     |

| aaa         | -    | _        | .10  |     | -    | _        | .10  |          | -    | -        | .10      |     | _    | -        | .10  |      | _    | -        | .10  |      | _    | -        | .10  |     |

| bbb         | -    | _        | .10  |     | -    | _        | .10  |          | -    | ı        | .10      |     | -    | ı        | .10  |      | -    | ı        | .10  |      | _    | ı        | .10  |     |

| N           |      | 8        |      |     |      | 14       |      |          |      | 16       |          |     |      | 20       |      |      |      | 24       |      |      |      | 28       |      |     |

#### NOTES:

- 1 ALL DIMENSIONING AND TOLERANCING CONFORM TO ASME Y14.5M-1994

- DATUMS —A— AND —B— TO BE DETERMINED AT DATUM PLANE —H—

- DIMENSION E TO BE DETERMINED AT SEATING PLANE \_\_C\_

- DIMENSIONS D AND E1 ARE TO BE DETERMINED AT DATUM PLANE -H-

- DIMENSION D DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED .15 mm PER SIDE

- bimension e1 does not include interlead flash or protrusions. Interlead flash or protrusions shall not exceed .25 mm per side

- DETAIL OF PIN 1 IDENTIFIER IS OPTIONAL BUT MUST BE LOCATED WITHIN THE ZONE INDICATED

- LEAD WIDTH DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION IS .08 mm IN EXCESS OF THE LEAD WIDTH DIMENSION AT MAXIMUM MATERIAL CONDITION. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT

- THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN .10 AND .25 mm FROM THE LEAD TIP

- 10 ALL DIMENSIONS ARE IN MILLIMETERS

- 11 THIS OUTLINE CONFORMS TO JEDEC PUBLICATION 95 REGISTRATION MO-153, VARIATION AA, AB-1, AB, AC, AD & AE

|        |      | OPTIO    | N T1 |             |

|--------|------|----------|------|-------------|

|        |      | PGG14    | 4T1  |             |

| SYMBOL | JEDE | C VARIAT | ION  | N           |

| B      |      | AB-1     |      | N<br>T<br>E |

|        | MIN  | È        |      |             |

| Α      | .90  | 1.10     | 1.20 |             |

| A1     | .05  | .10      | .15  |             |

| A2     | .80  | 1.00     | 1.05 |             |

| D      | 4.90 | 5.00     | 5.10 | 4,5         |

| Ε      | 6.20 | 6.40     | 6.60 | 3           |

| E1     | 4.30 | 4.40     | 4.50 | 4,6         |

| е      |      | .65 BSC  |      |             |

| b      | .19  | .25      | .30  |             |

| b1     | .19  | .22      | .25  |             |

| С      | .09  | -        | .20  |             |

| aaa    | -    | -        | .10  |             |

| bbb    | -    | -        | .10  |             |

| N      |      | 14       |      |             |

| TOLERANCES UNLESS SPECIFIED DECIMAL ANGULAR XX± ± XXXX± XXXX± | W W   | Santa PHONE                                                        | 2975 Stender Way<br>Santa Clara, CA 95054<br>PHONE: (408) 727-6116<br>FAX: (408) 492-8674 |         |           |  |

|---------------------------------------------------------------|-------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------|-----------|--|

|                                                               |       | PG/PGG PACKAGE OUTL<br>(PG OR PA TOPMARK (<br>4 mm BODY WIDTH TSSO | OD                                                                                        | E)      | PITCH     |  |

|                                                               | SIZE  | PSC-40                                                             | 56                                                                                        | 6       | REV<br>08 |  |

|                                                               | DO NO | OT SCALE DRAWING                                                   |                                                                                           | SHEET 2 | OF 3      |  |

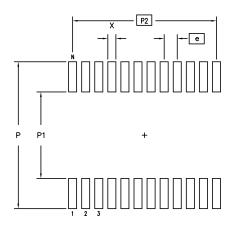

# Package Outline and Package Dimensions (4.4 mm 16-TSSOP), cont.

#### DATE CREATED 08/25/98 REVISIONS AUTHOR T. VU REV DESCRIPTION ADD 14 & 16 LD 02 07/10/99 03 ADD 8 LD T. VU 5/23/01 04 ADDED TOPMARK TO TITLE 10/14/04 05 ADD "GREEN" PGG NOMENCLATURE TU VU 3/8/13 9/3/14 ADDED PACKAGE CODE 07 ADD TOLERANCE FOR A, A1, E AND b CK LEE 3/10/17 08 ADD OPTION T1 NOTE: REFER TO DCP FOR OFFICIAL RELEASE DATE

#### LAND PATTERN DIMENSIONS

|    | MIN   | MAX  | MIN   | MAX   | MIN      | MAX     | MIN      | MAX  | MIN      | MAX  | MIN      | MAX  |  |

|----|-------|------|-------|-------|----------|---------|----------|------|----------|------|----------|------|--|

| Р  | 7.20  | 7.40 | 7.20  | 7.40  | 7.20     | 7.40    | 7.20     | 7.40 | 7.20     | 7.40 | 7.20     | 7.40 |  |

| P1 | 4.20  | 4.40 | 4.20  | 4.40  | 4.20     | 4.40    | 4.20     | 4.40 | 4.20     | 4.40 | 4.20     | 4.40 |  |

| P2 | 1.95  | BSC  | 3.90  | BSC   | 4.55 BSC |         | 5.85 BSC |      | 7.15 BSC |      | 8.45 BSC |      |  |

| Х  | .30   | .50  | .30   | .50   | .30      | .50     | .30      | .50  | .30      | .50  | .30      | .50  |  |

| е  | .65 E | BSC  | .65 E | BSC . | .65 E    | .65 BSC |          | BSC  | .65 BSC  |      | .65 BSC  |      |  |

| N  | 8     | 3    | 1     | 4     | 1        | 16      |          | 20   |          | 24   |          | 28   |  |

| TOLERANCES<br>UNLESS SPECIFIED    |             |                                                     | 2975 Ste | nder Way                             |       |

|-----------------------------------|-------------|-----------------------------------------------------|----------|--------------------------------------|-------|

| DECIMAL ANGULAR XX± ± XXXX± XXXX± | ww          | w.IDT.com                                           | PHONE: ( | ara, CA 9:<br>408) 727-<br>3) 492-86 | 6116  |

|                                   | TITLE<br>4. | PG/PGG PACKAGE<br>(PG OR PA TOPM<br>4 mm BODY WIDTH | IARK COD | E)                                   | PITCH |

|                                   | SIZE        | DRAWING No.                                         |          |                                      | REV   |

|                                   | С           | PSC-                                                | -4056    | 5                                    | 80    |

|                                   | DO NO       | OT SCALE DRAWING                                    |          | SHEET 3                              | OF 3  |

MAY 5, 2017

5V41235

IDT® 2 OUTPUT PCIE GEN1/2/3 SYNTHESIZER

# **Ordering Information**

| Part / Order Number | Marking     | Shipping Packaging | Package      | Temperature   |

|---------------------|-------------|--------------------|--------------|---------------|

| 5V41235PGG          | See Page 10 | Tubes              | 16-pin TSSOP | 0 to +70° C   |

| 5V41235PGG8         |             | Tape and Reel      | 16-pin TSSOP | 0 to +70° C   |

| 5V41235PGGI         |             | Tubes              | 16-pin TSSOP | -40 to +85° C |

| 5V41235PGGI8        |             | Tape and Reel      | 16-pin TSSOP | -40 to +85° C |

| 5V41235NLG          | See Page 10 | Tubes              | 16-pin QFN   | 0 to +70° C   |

| 5V41235NLG8         |             | Tape and Reel      | 16-pin QFN   | 0 to +70° C   |

| 5V41235NLGI         |             | Tubes              | 16-pin QFN   | -40 to +85° C |

| 5V41235NLGI8        |             | Tape and Reel      | 16-pin QFN   | -40 to +85° C |

<sup>&</sup>quot;G" after the two-letter package code are the Pb-Free configuration and are RoHS compliant.

While the information presented herein has been checked for both accuracy and reliability, Integrated Device Technology (IDT) assumes no responsibility for either its use or for the infringement of any patents or other rights of third parties, which would result from its use. No other circuits, patents, or licenses are implied. This product is intended for use in normal commercial applications. Any other applications such as those requiring extended temperature range, high reliability, or other extraordinary environmental requirements are not recommended without additional processing by IDT. IDT reserves the right to change any circuitry or specifications without notice. IDT does not authorize or warrant any IDT product for use in life support devices or critical medical instruments.

# **Revision History**

| Rev. | Originator | Date     | Description of Change                                                                                                                                                                                                                                                                                |

|------|------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Α    | RDW        | 11/02/11 | Initial release.                                                                                                                                                                                                                                                                                     |

| В    | RDW        | 11/22/11 | Changed title to "2 Output PCIe GEN1/2/3 Synthesizer"     Updated Differential Phase Jitter table.                                                                                                                                                                                                   |

| С    | RDW        | 06/06/12 | 1. Updated Features bullet(s) from: "• 25 MHz, 125 MHz and 200 MHz output frequencies; supports Ethernet applications", to: "• 25 MHz, 100MHz, 125 MHz and 200 MHz output frequencies; TSSOP-only • 100MHz output frequency; MLF package". 2. Added table 3, Output/Spread Select table for MLF only |

| D    | S. Sharma  | 10/16/12 | Updated and expanded Output Select table per char review.     Changed crystal capacitance load spec from 16pF to 8pF.                                                                                                                                                                                |

| E    | IH         | 09/09/15 | Corrected typo in Ordering information; NLG and NLGI shipping packaging changed from "Tray" to "Tubes".                                                                                                                                                                                              |

| F    | IH         | 07/08/16 | Updated marking diagrams for TSSOP devices.                                                                                                                                                                                                                                                          |

| G    | RDW        | 10/11/16 | Updated Features bullets for package output frequencies.     Changed all MLF references to QFN.                                                                                                                                                                                                      |

| Н    | B.Shen     | 01/12/17 | Updated 16QFN POD drawing to latest showing chamfered epad.                                                                                                                                                                                                                                          |

| J    | C.P.       | 05/05/17 | Updated PGG16 package outline drawing to latest version.                                                                                                                                                                                                                                             |

#### 5V41235 2 OUTPUT PCIE GEN1/2/3 SYNTHESIZER

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.