## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: <a href="http://www.renesas.com">http://www.renesas.com</a>

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (<a href="http://www.renesas.com">http://www.renesas.com</a>)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# **Power MOS FET**

**Application Note**

#### Keep safety first in your circuit designs!

Renesas Technology Corp. puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage.

Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- These materials are intended as a reference to assist our customers in the selection of the Renesas

Technology Corp. product best suited to the customer's application; they do not convey any license

under any intellectual property rights, or any other rights, belonging to Renesas Technology Corp. or

a third party.

- 2. Renesas Technology Corp. assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corp. without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor for the latest product information before purchasing a product listed herein.

- The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

- Please also pay attention to information published by Renesas Technology Corp. by various means, including the Renesas Technology Corp. Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corp. assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corp. semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- 6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduce in whole or in part these materials.

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

- Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

- 8. Please contact Renesas Technology Corp. for further details on these materials or the products contained therein.

## Index

| 1.  | Electrical Characteristics Definition and Usage Explanation                                        | 1    |

|-----|----------------------------------------------------------------------------------------------------|------|

| 1.1 | Absolute Maximum Ratings and Electrical Characteristics                                            | 1    |

| 1.1 | .1 Absolute Maximum Ratings                                                                        | 1    |

| 1.1 | .2 Electrical Characteristics                                                                      | 2    |

| 1.2 | Relationship between On-Resistance R <sub>DS(on)</sub> and Withstand Voltage V <sub>DSS</sub>      | 3    |

|     | Saturation Voltage V <sub>DS(on)</sub> (= Id × R <sub>DS(on)</sub> ) Gate Drive Voltage Dependence |      |

| 1.3 |                                                                                                    |      |

| 1.4 | Gate Charge Amounts Qg, Qgs, Qgd                                                                   |      |

| 1.4 |                                                                                                    |      |

| 1.5 | Internal Diode Reverse Recovery Time trr Current I <sub>DR</sub> Characteristic                    | 6    |

| 1.6 | Transient Thermal Resistance Characteristic θch-c(t) – Pulse Width PW Characteristic               |      |

| 1.7 | Area of Safe Operation (ASO)                                                                       |      |

| 1.7 |                                                                                                    |      |

| 1.7 |                                                                                                    |      |

| 2.  | Power MOS FET Destruction Mechanisms and Countermeasures                                           | 11   |

| 2.1 | Relationship between Power MOS FET Application Areas and Destruction Modes                         | 11   |

| 2.1 | .1 Relationship between Main Power MOS FET Application Areas and Destruction Modes                 | 11   |

| 2.1 | .2 Power MOS FET Applications and Operating Range                                                  | 13   |

| 2.1 | .3 Power MOS FET Structure                                                                         | 14   |

| 2.2 | Avalanche Destruction                                                                              | 16   |

| 2.2 | 2.1 Explanation of Avalanche Destruction                                                           | 16   |

| 2.2 | 2.2 Avalanche Destruction Resistance Test Circuit and Waveform                                     | 16   |

| 2.2 | 2.3 Avalanche Energy Calculation Method                                                            | 17   |

| 2.2 | 2.4 Classification of Avalanche Destruction Factors                                                | 18   |

| 2.2 | 2.5 Avalanche Destruction Current and Energy Value                                                 | 19   |

| 2.2 | 2.6 Avalanche Destruction Current and dV/dt Resistance                                             | . 20 |

| 2.2 | 2.7 Simple Determination Method for Avalanche Resistance Guaranteed Products                       | . 20 |

| 2.2 | ·                                                                                                  |      |

| 2.3 | ASO Destruction (Heat Radiation Design)                                                            | 22   |

| 2.3 | 8.1 Explanation of ASO Destruction                                                                 | . 22 |

| 2.3 | 3.2 ASO Destruction Countermeasures                                                                | . 22 |

| 2.3 | 8.3 Forward Bias ASO (Area of Safe Operation)                                                      | . 23 |

| 2.3 |                                                                                                    |      |

| 2.3 | •                                                                                                  |      |

| 2.4 | Internal Diode Destruction                                                                         | 29   |

| 2.4 | .1 Explanation of Internal Diode Destruction                                                       | 29   |

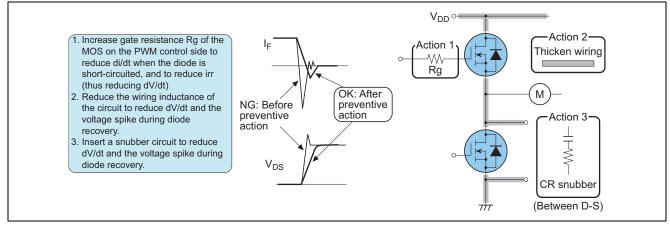

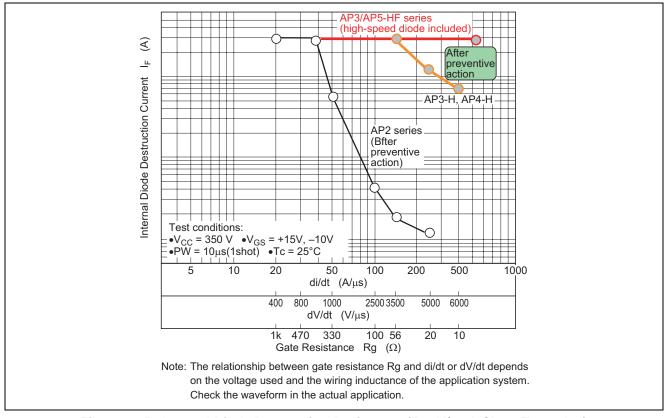

| 2.4 | .2 Example of Internal Diode Destruction Circuit Countermeasures                                   | 31   |

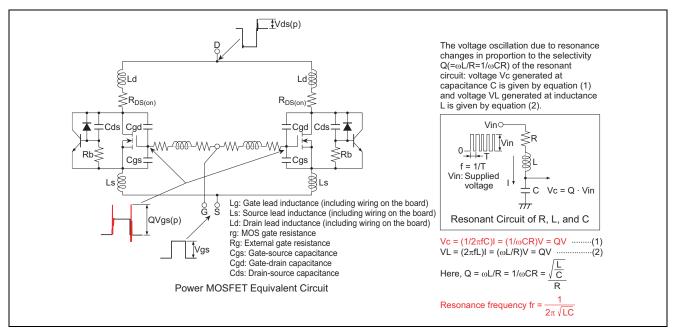

| 2.5 | Destruction Due to Parasitic Oscillation                                                           |      |

| 2.5 | 5.1 Explanation of Destruction Due to Parasitic Oscillation                                        | 32   |

| 2.5 |                                                                                                    |      |

| 2.6 | Notes on Parallel Connection                                                                       |      |

| 2.6 |                                                                                                    |      |

| 2.6 | •                                                                                                  |      |

| 2.7 | Electrostatic Destruction                                                                          |      |

| 2.7 |                                                                                                    |      |

|     |                                                                                                    |      |

| 2.7.2  | Electrostatic Destruction Countermeasures                                             | . 35 |

|--------|---------------------------------------------------------------------------------------|------|

| 2.7.3  | Destruction Progression Modes after Electrostatic Destruction                         | . 36 |

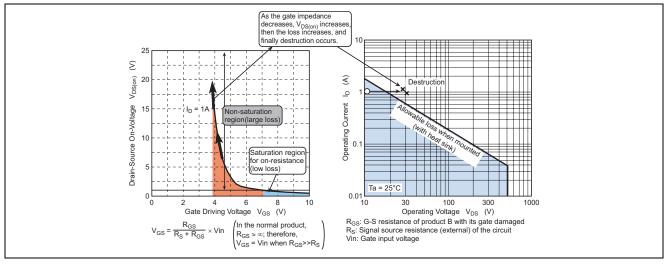

| 2.7.4  | Mechanism whereby Gate Destruction Product B Come to ASO Destruction                  |      |

| 2.8 Us | age Notes                                                                             |      |

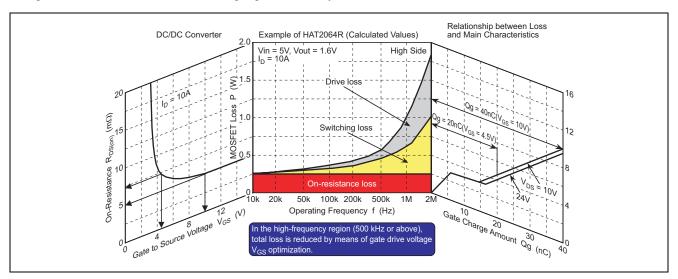

| 2.8.1  | Power MOS FET Main Loss Frequency Dependence and Relationship to Main Characteristics |      |

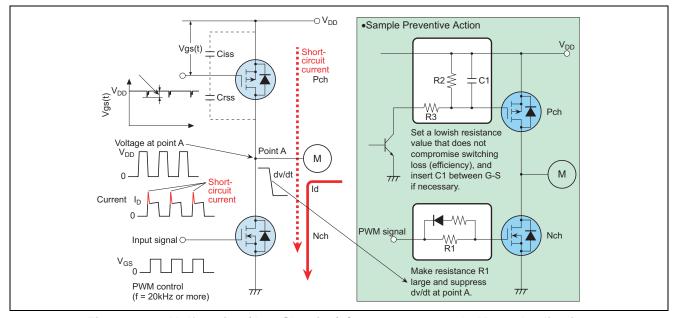

| 2.8.2  | Malfunction (Arm Shorting) Countermeasures in Motor Application                       | . 38 |

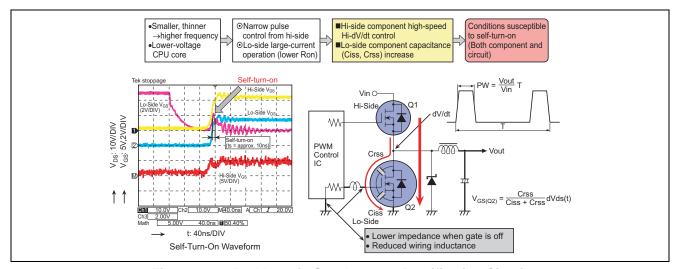

| 2.8.3  | Non-Isolated Synchronous Rectification Converter Low-Side Self-Turn-On Phenomenon     |      |

| 3. Po  | wer MOS FET Applications                                                              | . 41 |

|        | plication Map                                                                         |      |

|        | tomotive Applications                                                                 |      |

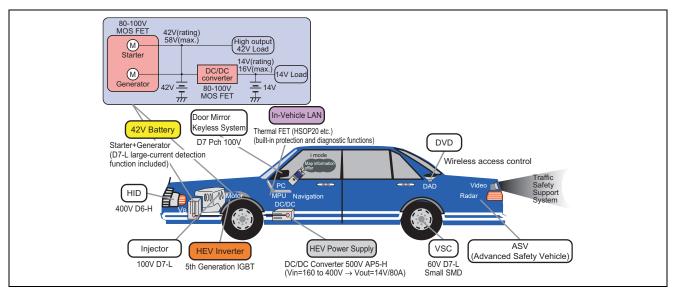

| 3.2.1  | Technological Trends in Automotive Electrical Equipment                               | . 42 |

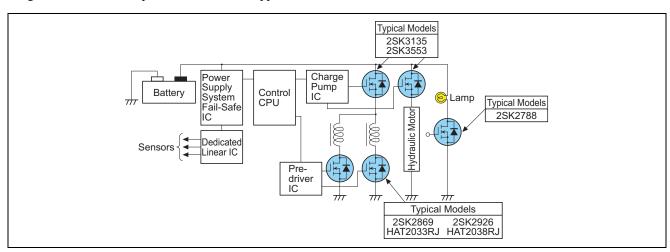

| 3.2.2  | Sample Automobile ABS Application                                                     | . 42 |

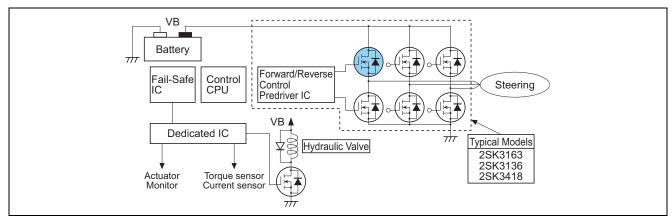

| 3.2.3  | Sample Automobile Power Steering Application                                          | . 43 |

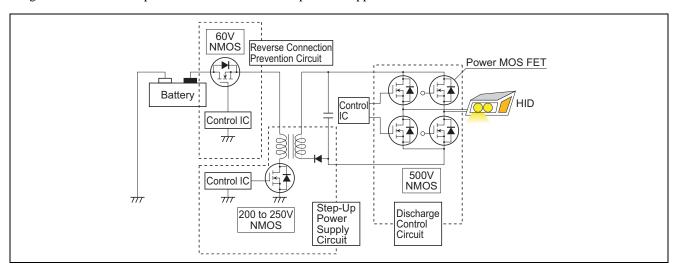

| 3.2.4  | Sample Automobile HID Headlamp Control Application                                    | . 43 |

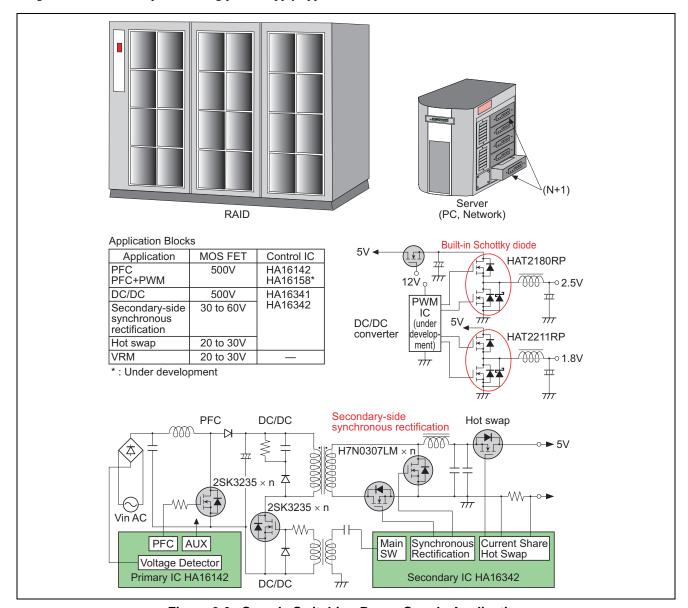

| 3.3 Po | wer Supply Applications                                                               | . 44 |

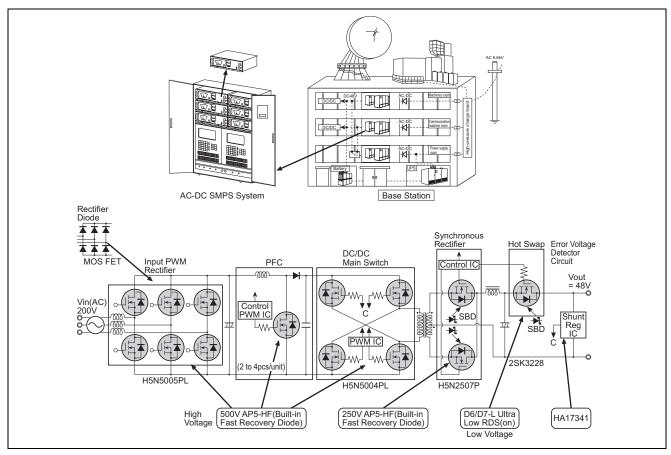

| 3.3.1  | Switching Power Supplies                                                              | . 44 |

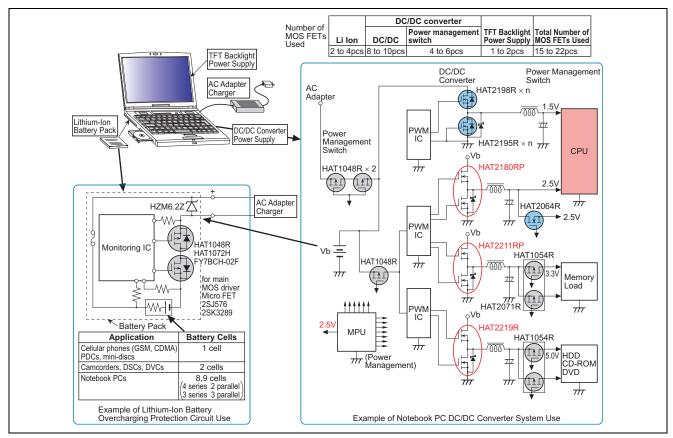

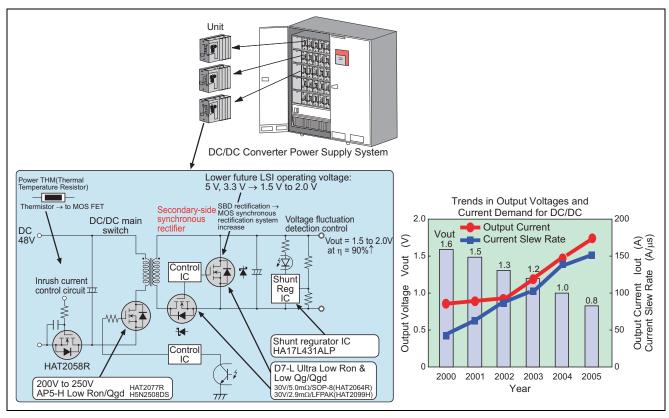

| 3.3.2  | DC/DC Converters                                                                      | . 45 |

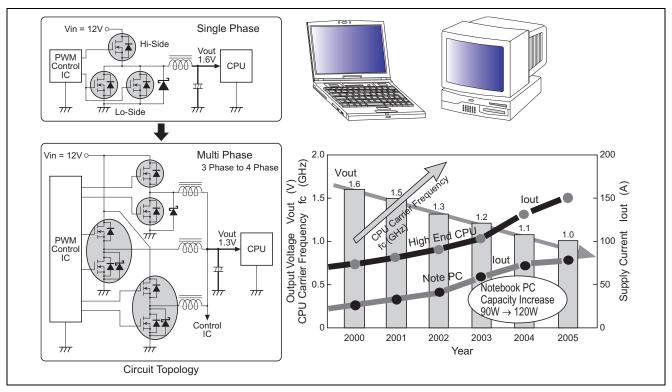

| 3.3.3  | VRM (Voltage Regulator Module)                                                        | . 46 |

| 3.3.4  | Base Station SMPS (Switch-Mode Power Supply)                                          | . 47 |

| 3.3.5  | Communication Equipment DC/DC Converter                                               | . 48 |

| 3.4 Mo | tor Drive Applications                                                                |      |

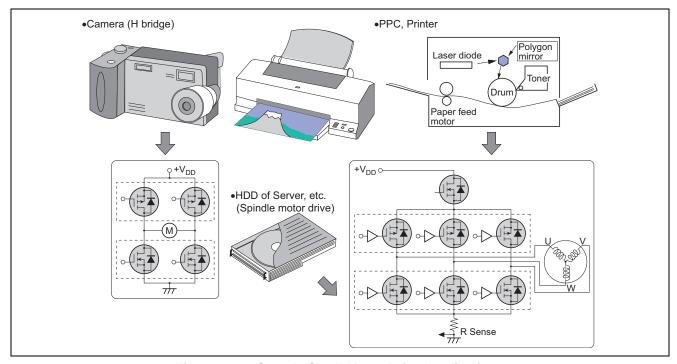

| 3.4.1  | Small Motor Drive                                                                     | . 49 |

## **Power MOS FET**

## **Application Note**

### **Electrical Characteristics Definition and Usage Explanation**

#### **Absolute Maximum Ratings and Electrical Characteristics** 1.1

#### **Absolute Maximum Ratings** 1.1.1

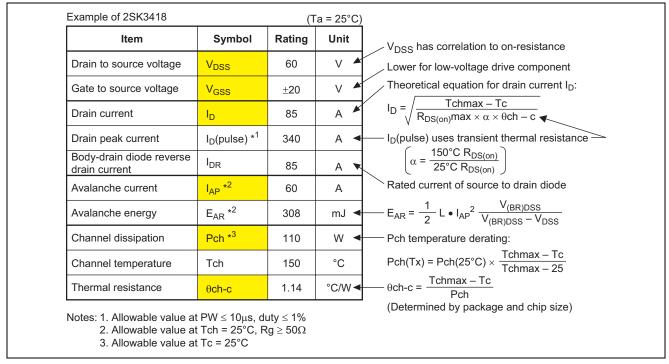

Figure 1.1 shows the meaning of power MOSFET absolute maximum ratings.

Figure 1 Power MOS FET Absolute Maximum Ratings

RENESAS

#### 1.1.2 Electrical Characteristics

Table 1.1 shows the meaning of power MOSFET electrical characteristics.

Table 1.1 Power MOS FET Electrical Characteristics

$(Ta = 25^{\circ}C)$

|                                              |                      | Ratings |      |      |                                                    |      |                        |                                                                                                                                                 |  |  |

|----------------------------------------------|----------------------|---------|------|------|----------------------------------------------------|------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Item                                         | Symbol               | Min     | Тур  | Max  | Test<br>Conditions                                 | Unit | Temperature Dependence | Design Notes                                                                                                                                    |  |  |

| Drain to source breakdown voltage            | V <sub>(BR)DSS</sub> | 60      | _    | _    | $I_D = 10 \text{mA},$<br>$V_{GS} = 0$              | V    | •                      | Correlation to on-resistance                                                                                                                    |  |  |

| Zero gate voltage drain current              | I <sub>DSS</sub>     | _       | _    | 10   | $V_{DS} = 60V,$<br>$V_{GS} = 0$                    | μА   | •                      | Thermal dependence is high, but low in terms of loss                                                                                            |  |  |

| Gate to source<br>leakage current            | I <sub>GSS</sub>     | _       | _    | ±0.1 | $V_{GS} = \pm 20V,$ $V_{DS} = 0$                   | μА   | _                      | For products with on-chip protective diode, several tens of nA to several µA, guaranteed value of ±10 µA                                        |  |  |

| Gate to source cutoff voltage                | $V_{GS(off)}$        | 1.0     | _    | 2.5  | $V_{DS} = 10V$ ,<br>$I_D = 1mA$                    | V    | 0                      | Affects switching operation noise and switching time tr, tf                                                                                     |  |  |

| Forward transfer admittance                  | Yfs                  | 55      | 90   | _    | $I_D = 45A,$ $V_{DS} = 10V$                        | s    | 0                      |                                                                                                                                                 |  |  |

| Static drain to source on state resistance 1 | R <sub>DS(on)1</sub> | —       | 4.3  | 5.5  | $I_D = 45A,$ $V_{GS} = 10V$                        | mΩ   | •                      | Most important parameters in determining on-loss. Note that these rise together with                                                            |  |  |

| Static drain to source on state resistance 2 | R <sub>DS(on)2</sub> | _       | 6.0  | 9.0  | $I_D = 45A$ , $V_{GS} = 4V$                        | mΩ   | •                      | temperature.                                                                                                                                    |  |  |

| Input capacitance                            | Ciss                 | _       | 9770 | _    | $V_{DS} = 10V,$<br>$V_{GS} = 0,$                   | pF   | _                      | V <sub>DS</sub> dependent. Drive loss indicator in analog operation                                                                             |  |  |

| Output capacitance                           | Coss                 | _       | 1340 | _    | f = 1MHz                                           | pF   | _                      | V <sub>DS</sub> dependent. Affects fall time tf under light load.                                                                               |  |  |

| Reverse transfer capacitance                 | Crss                 | _       | 470  | _    |                                                    | pF   | _                      | V <sub>DS</sub> dependent. Influences switching time tr, tf.                                                                                    |  |  |

| Total gate charge                            | Qg                   | _       | 180  | _    | $V_{DD} = 50V,$ $V_{GS} = 10V,$ $I_{D} = 85A$      | nC   | _                      | Characteristic that determines drive loss. Greatly dependent on gate drive voltage.                                                             |  |  |

| Gate to source charge                        | Qgs                  | _       | 32   | _    | 1                                                  | nC   | _                      |                                                                                                                                                 |  |  |

| Gate to drain charge                         | Qgd                  | _       | 36   | _    |                                                    | nC   | _                      | Characteristic that determines switching time tr, tf. Dependent on power supply voltage V <sub>DD</sub> (increases when V <sub>DD</sub> rises). |  |  |

| Turn-on delay time                           | td(on)               | _       | 53   | _    | $V_{GS} = 10V$ ,                                   | ns   | _                      | Determined by Rg, Qgd, and gate                                                                                                                 |  |  |

| Rise time                                    | tr                   | _       | 320  | _    | $I_D = 45A,$ $R_L = 0.67\Omega,$                   | ns   | _                      | drive voltage. Influence diode onloss in inverter use.                                                                                          |  |  |

| Turn-off delay time                          | td(off)              |         | 700  | _    | $Rg = 50\Omega$                                    | ns   | _                      | Determined by Rg, Qgd, and Vth.                                                                                                                 |  |  |

| Fall time                                    | tf                   | _       | 380  | _    |                                                    | ns   | _                      | Influence surge voltage (noise) when switching off.                                                                                             |  |  |

| Body-drain diode forward voltage             | V <sub>DF</sub>      | _       | 1.0  | _    | $I_F = 85A,$ $V_{GS} = 0$                          | V    | 0                      | Becomes same characteristic as on-resistance when positive bias is applied to $V_{\rm GS}$ .                                                    |  |  |

| Body-drain diode reverse recovery time       | trr                  | _       | 70   | _    | $I_F = 85A,$ $V_{GS} = 0,$ $di/dt = 50\mu A/\mu s$ | ns   | •                      | Short-circuit current: lowers di/dt to suppress noise.                                                                                          |  |  |

Note: ●: Has positive temperature coefficient, O: Has negative temperature coefficient

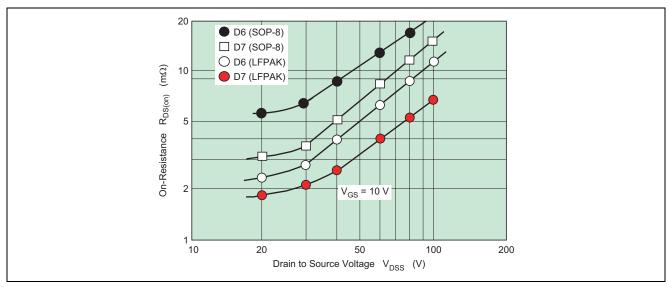

## 1.2 Relationship between On-Resistance R<sub>DS(on)</sub> and Withstand Voltage V<sub>DSS</sub>

Figure 1.2 shows the relationship between a withstand voltage  $V_{DSS} = 20$  to 100 V rated component and on-resistance  $R_{DS(on)}$ . When selecting the withstand voltage of an component, a margin should be left in the settings with respect to circuit operation conditions power supply voltage  $V_{DD}$  and surge voltage  $V_{DS(peak)}$  generated when switching off. As  $V_{DSS}$  has a positive temperature characteristic with respect to temperature, the minimum temperature environment conditions for use of the component must be taken into consideration.

Figure 1.2 R<sub>DS(on)</sub> – V<sub>DSS</sub> Relationship

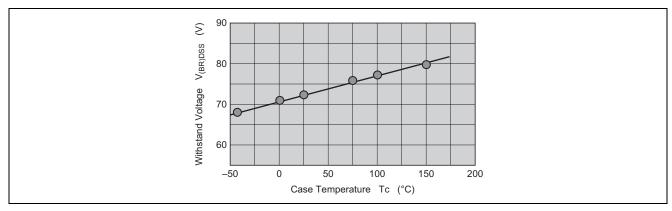

Figure 1.3 shows the  $V_{(BR)DSS}$  temperature characteristic (taking the example of the 2SK3418). In this case, making the withstand voltage margin larger than necessary is inadvisable as it will result in higher on-resistance and greater steady-state loss. Recently, components have appeared that can handle guaranteed avalanche resistance in order to reduce this margin as much as possible and provide the benefit of lower loss.

Figure 1.3 V<sub>(BR)DSS</sub> – Tc Characteristics (2SK3418)

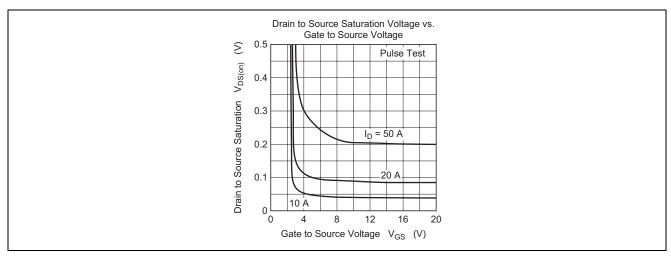

## 1.3 Saturation Voltage $V_{DS(on)}$ (= Id × $R_{DS(on)}$ ) Gate Drive Voltage Dependence

This characteristic is a characteristic curve for designing at what gate drive voltage the  $V_{DS(on)}$  area (on-resistance area) is effected in the case of a predetermined operating current Id.

In the case of power MOS FETs, 10 V drive components, 4 V drive components, 4 V drive (or lower) components are produced according to the gate drive operating current. The means of achieving low-voltage drive is generally to use a thin gate oxide film (whereby the gate-source withstand voltage  $V_{GSS}$  rating is reduced) to attain a lower  $V_{GS(off)}$  value.

$V_{GS(off)}$  has an approximately -5 mV/°C negative temperature coefficient (characteristic that falls approximately 0.5 V with a 100°C rise).

When selecting the type of component in terms of drive voltage, it is necessary to consider the application (for example, selection of a 10 V drive component with a high  $V_{GS(off)}$  value to cope with noise in switching power supply or motor drive applications) and the specifications of the gate drive IC or LSI to be used (such as a low-level voltage that keeps the MOS FET off).

Recently, therefore, a distinction may be made between the use of 4 V drive components and 10 V drive components according to the conditions of use and application even in automotive electrical equipment.

Figure 1.4 V<sub>DS(on)</sub> - V<sub>GS</sub> Characteristics (2SK3418)

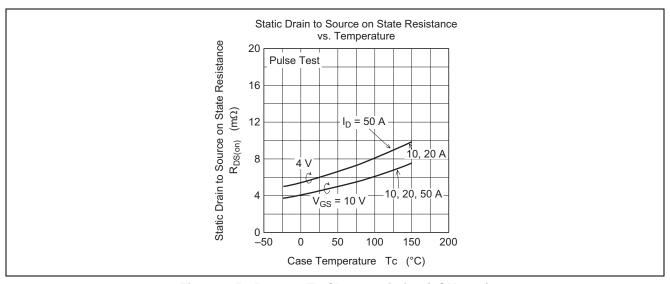

#### 1.3.1 On-Resistance R<sub>DS(on)</sub> Temperature Dependence

Figure 1.5 shows temperature dependence of on-resistance  $R_{DS(on)}$ . Power MOS FET on-resistance  $R_{DS(on)}$  has a positive temperature characteristic.

If the ratio between channel temperature rating Tch(max.) of  $150^{\circ}$ C and room temperature of  $25^{\circ}$ C ( $150^{\circ}$ CRon/ $25^{\circ}$ CRon) is designated  $\alpha$ , the value is approximately 1.7 to 1.8 times for an component with a withstand voltage of 100 V or less, and approximately 2.4 to 2.5 times for an component with a withstand voltage of 500 V. It should also be noted that, as shown in the figure,  $R_{DS(on)}$  does not rise linearly with a rise in temperature, but increases in a curvilinear shape.

What this means is that, when ambient temperature  $Ta = 100^{\circ}C$ , for example, if the channel temperature calculation result is that  $Tch = 130^{\circ}C$ , and Ta is made  $120^{\circ}C$  (a  $20^{\circ}C$  rise), Tch does not simply rise by  $20^{\circ}C$  to become  $150^{\circ}C$ , but rises above that temperature.

Therefore, when an component is used in a high-temperature environment such as automotive electrical equipment, this temperature characteristic must be carefully considered in heat radiation design. For details, refer to the power MOS FET heat radiation design example.

Figure 1.5 R<sub>DS(on)</sub> – Tc Characteristics (2SK3418)

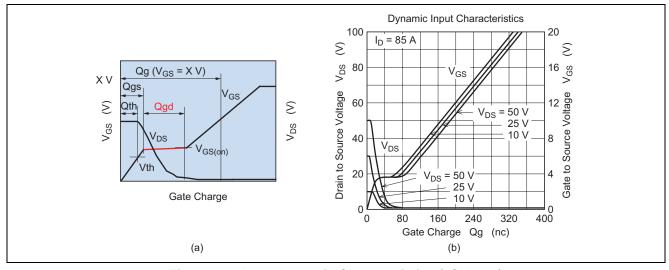

#### 1.4 Gate Charge Amounts Qg, Qgs, Qgd

In figure 1.6(a), the point up to prescribed drive voltage  $V_{GS}$  (=XV) is total charge amount Qg. This is the characteristic parameter that determines gate peak current ig(peak) for driving the gate and drive loss P(drive loss).

$$lg(peak) = Qg/t$$

....(1)

$P(drive loss) = f \cdot Qg \cdot V_{GS}$  .....(2)

Qgd corresponds to mirror capacitance Crss, and depends on power supply voltage  $V_{DS}$ . It is also a parameter that influences switching characteristics.

$$tf \cong \frac{(Rs + rg) \cdot Qgd}{Vgs(on) - Vth} \log \frac{Vgs(on)}{Vth} \dots (3)$$

Fall time tf that controls L load switching loss is expressed by equation (3). Qg and Qgd are important items in designing high-frequency operation loss. In high-frequency (f = 100 kHz or above) applications, it can be said that the smaller the Ron-Qg or Ron-Qgd product, the higher is the performance of the component.

Figure 1.6 Input Dynamic Characteristics (2SK3418)

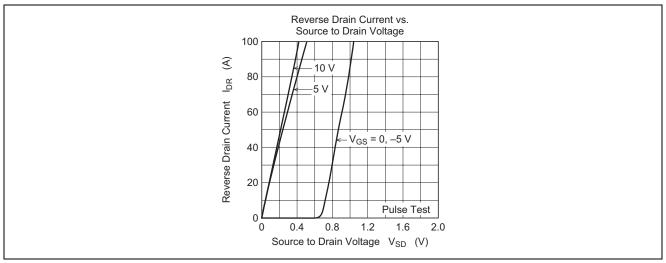

#### 1.4.1 Characteristics of Internal Diode between Source and Drain

In a power MOSFET, a parasitic diode is provided between the source and drain. Rated current  $I_{DR}$  of this diode is the same value as forward drain current rating  $I_D$ .

The characteristics of this diode show the same forward voltage characteristics as an ordinary diode in the case of zero bias of the gate drive voltage ( $V_{GS} = 0$ ). If the gate drive voltage is given positive bias (in the Nch case), as shown in Figure 1.7 there is a voltage drop determined by on-resistance  $R_{DS(on)}$  ( $V_{SD} = Id \times R_{DS(on)}$ ) that is the same as in the forward direction, and a much lower forward voltage can be obtained even than with an SBD (Schottky barrier diode).

Figure 1.7 I<sub>DR</sub> - V<sub>SD</sub> Characteristics (2SK3418)

The benefits of such reverse-direction characteristics are actively applied in the following kinds of uses.

- Load switches for preventing battery reverse connection

- Switching power supply (n+1) redundant-type hot swap circuits

- Motor drive circuit external diode replacement

- Switching power supply secondary-side drive rectification circuits, etc.

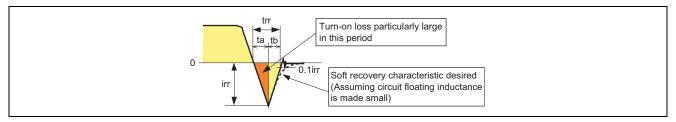

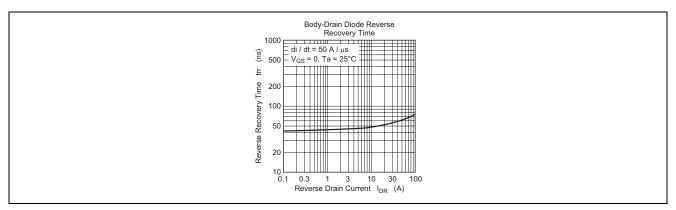

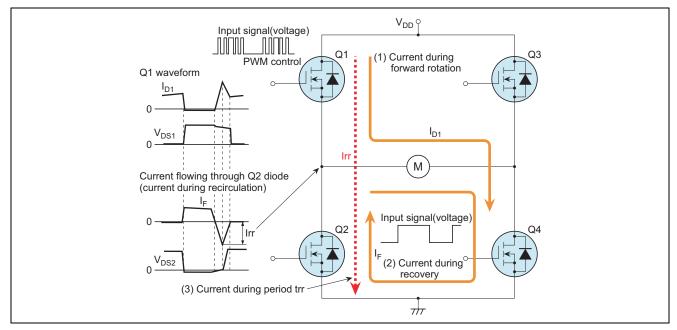

#### 1.5 Internal Diode Reverse Recovery Time trr Current I<sub>DR</sub> Characteristic

In motor drive (power steering, starter generators, etc. in the case of electrical equipment) and switching power supply synchronous rectification applications that make positive use of a power MOSFET internal diode, there is a requirement for this reverse recovery time trr to be fast. In these applications, operationally upper arm/lower arm shorting and excess turn-on loss occur in this trr period. Generally, therefore, in the control circuitry, a dead time (longer than trr) is provided that turns off the gate signal at the time of upper/lower component switching.

Figure 1.8 Reverse Recovery Time trr Waveform

This reverse recovery time trr shows a tendency to increase as the temperature rises. Also, the steeper di/dt at the time of recovery (area tb in figure 1.9), the more likely is the occurrence of noise, and therefore a soft recovery characteristic is desirable. Reverse recovery time trr differs greatly according to the withstand voltage of the component. In the case of a withstand voltage of 60 V or less, it is comparatively fast at a value of 40 to 60 ns. It is around 100 ns in the 100 V class, and around 300 to 600 ns in the 250 to 500 V high-withstand-voltage class. Therefore, in the high-withstand-voltage class of 250 V and above, products have been developed that have been speeded up to around 100 ns by means of lifetime control technology.

Figure 1.9 trr - IDR Characteristics (2SK3418)

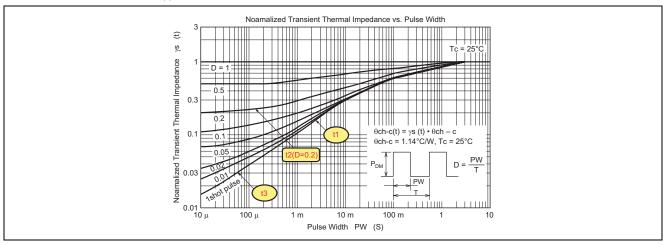

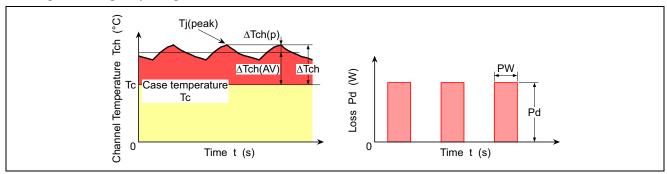

# 1.6 Transient Thermal Resistance Characteristic θch-c(t) – Pulse Width PW Characteristic

Figure 1.10 shows the  $\theta$ ch-c(t)—pulse width PW characteristic. This is a characteristic for calculating channel temperature Tch in the component operating state. Pulse width PW on the horizontal axis is the operating time, and 1 Shot Single Pulse repeat operation conditions are shown.

For example, PW = 1 ms, D = 0.2 (duty cycle = 20%) means that the repetition frequency is 200 Hz (repetition cycle T = 5 ms).

Generally, when channel temperature rise  $\Delta T$ ch is calculated with duty cycle = 20% (D = 0,2), PW = 10 ms, and current dissipation Pd = 60 W, the following equation may be used, but since error arises as shown below, the transient thermal resistance characteristic should be used.

Tch =

$$(0.2 \times Pd) \times \theta$$

ch-c =  $(0.2 \times 60) \times 1.14 = 13.7$ °C

When the transient thermal resistance characteristic is used, 16.5°C error arises as shown below.

Tch = Pd ×

$$\theta$$

ch-c(t) = 60 × 0.44 × 1.14 = 30.2°C

Figure 1.10 θch-c(t) – Pulse Width PW Characteristics (2SK3418)

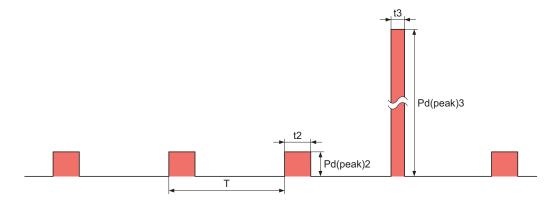

Examples of channel temperature Tch calculation (2SK3418) using transient thermal resistance are shown below.

#### • Example 1

To calculate channel temperature Tch under the following conditions: when case temperature  $Tc = 85^{\circ}C$ , peak power Pd(peak)1 = 50 W, application time ts = 10 ms, 1 shot single pulse

Tch1 = Tc + (Pd(peak)1)

$$\times$$

0ch-c(t1) = 85 + (50  $\times$  0.3  $\times$  1.14) = 102.1°C

#### • Example 2

To calculate channel temperature Tch under the following conditions: when case temperature  $Tc=85^{\circ}C$ , operating frequency f=2 kHz, repeat operation with duty cycle = 20%, applied power Pd(peak)2 = 50 W

From the above operation, application time  $t2 = 100~\mu s$ , repetition cycle  $T = 500~\mu s$ , and D = t2/T = 0.2. Therefore:

Tch2 = Tc + (Pd(peak)2)

$$\times \theta$$

ch-c(t2/T) = 85 + (50  $\times$  0.22  $\times$  1.14) = 97.54°C

#### Example 3

To calculate peak channel temperature Tch(peak) when peak power Pd(peak)3 = 500 W is further applied for a period of t3 = 60 µs by another circuit control system during the operation in Example 2

Tch2 = Tc + (Pd(peak)2) ×

$$\theta$$

ch-c(t2/T) + {(Pd(peak)3 - Pd(peak)2 × t2/T)} ×  $\theta$ ch-c(t3) = 85 + (50 × 0.22 × 1.14) + (500 - 50 × 0.2) × 0.031 × 1.14) = 85 + 12.54 + 17.32 = 114.86°C

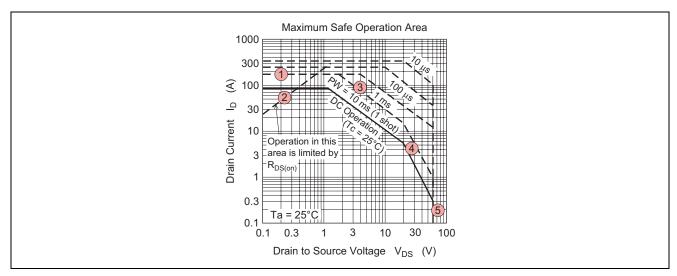

#### 1.7 Area of Safe Operation (ASO)

#### 1.7.1 Area of Safe Operation (ASO) Diagram

Figure 1.11 shows an area of safe operation (ASO) diagram for the 2SK3418.

The ASO limited area is divided into the following 5 areas.

Area (1) is an area limited by maximum rated currents I<sub>DC</sub>, I<sub>D(pulse)</sub>max.

Area (2) is an area limited by on-resistance  $R_{DS(on)}max\ [I_D=V_{DS}/R_{DS(on)}]$ . Generally, this area is divided separately from the ASO area.

Area (3) is an area limited by channel loss.

Area (4) is the same kind of secondary breakdown area as in a bipolar transistor that appears under conditions of continuous operation or opened with a comparatively long pulse width (several ms or more). This is because, when the operating voltage increases in the same applied power line, the operating current naturally decreases, but in this small current area the output transfer characteristic (Vgs-Id characteristic) is a negative temperature characteristic. When the area becomes a large current area that entails a change to a positive temperature characteristic, this phenomenon disappears. The current value at which the temperature characteristic changes from negative to positive differs from product to product, and with products of several amperes or less this phenomenon is unlikely to occur, and this can be guaranteed with a so-called constant power line with no secondary breakdown.

Area (5) is an area limited by withstand voltage  $V_{DSS}$ max.

Figure 1.11 ASO Diagram (2SK3418)

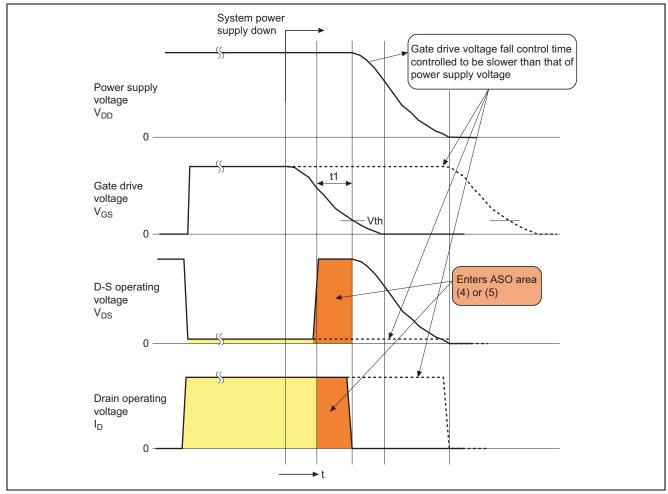

#### 1.7.2 Notes on ASO in Circuit Control System

As power MOS FETs are generally used in switching applications, in normal operation they are usually used in limited area (2). A point requiring attention in circuit design is the control system sequence.

Figure 1.12 shows an example of the power supply voltage and gate drive voltage sequence for a terminal electronic device when the system's source power supply is cut. As shown by the solid lines in the figure, if the fall time until power supply voltage  $V_{DD}$  is turned off is longer than that for gate drive voltage  $V_{GS}$ ,  $V_{GS}$  is in an underdrive state in period t1 in the figure, and enters ASO limited area (4) or (5), making it necessary to confirm whether it is in an area of safe operation. An effective means of avoiding such an operation area is to perform sequence control so that the fall time of gate drive voltage  $V_{GS}$  is delayed beyond supply voltage  $V_{DD}$  as shown by the dotted lines.

Figure 12 Example of Terminal Electronic Device System Power Supply Voltage and Gate Drive Voltage Sequence

## **Power MOS FET**

## **Application Note**

# 2. Power MOS FET Destruction Mechanisms and Countermeasures Introduction

As power MOS FETs are often used in the final output circuitry of electronic device application circuits, and are used under a wide range of conditions, circuit designers frequently have to confront the problem of unexpected component destruction.

The purpose of this section is to carry out electronic circuit design with a good understanding of the mechanisms behind such destruction, and produce as far as possible problems involving heat radiation, destruction, and so forth, in mass production and in the market after design is completed, in order to use power MOS FETs effectively.

# 2.1 Relationship between Power MOS FET Application Areas and Destruction Modes

## 2.1.1 Relationship between Main Power MOS FET Application Areas and Destruction Modes

Table 2.1 shows the relationship between main power MOSFET application areas and destruction modes. Power MOS FET destruction modes can be broadly be divided into the five modes shown below.

Table 2.1 Relationship between Power MOSFET Application Areas and Destruction Modes

|   | Application Field                                                                         |                   |                                                                              |                           |                                                                                                                                                                      |                |                                                |                         |                                        |             |          |                                   | Automobile (electronic components) |                     | Motor Drive   |            |

|---|-------------------------------------------------------------------------------------------|-------------------|------------------------------------------------------------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------------------------------------|-------------------------|----------------------------------------|-------------|----------|-----------------------------------|------------------------------------|---------------------|---------------|------------|

|   |                                                                                           |                   |                                                                              | AC/DC(OA, Server)         |                                                                                                                                                                      |                |                                                |                         |                                        | Machine     | Motor    | Valve,<br>solenoid                | Low<br>voltage                     | High<br>voltage     |               |            |

| D |                                                                                           |                   |                                                                              | Forward<br>conver-<br>ter | Reso-<br>nance<br>method                                                                                                                                             | Bridge circuit | Large-<br>power<br>parallel<br>connec-<br>tion | DC-DC<br>conver-<br>ter | Synch-<br>ronous<br>rectifi-<br>cation | UPS<br>(DC- | dischar- | EPS<br>start-up<br>genera-<br>tor |                                    | OA<br>(PPC,<br>HDD) | FA<br>(servo) | Audio amp. |

| 1 | Avala                                                                                     | nche c            | lestruction                                                                  | 0                         | 0                                                                                                                                                                    | 0              | 0                                              | 0                       | 0                                      | 0           | 0        | 0                                 | 0                                  | 0                   | 0             | _          |

| 2 | ASO                                                                                       | Forwa             | ard-bias ASO                                                                 | _                         | _                                                                                                                                                                    | _              | _                                              | _                       |                                        | _           | _        | _                                 | _                                  | _                   | _             | 0          |

|   | dest-<br>ructi-<br>on                                                                     | Loss<br>↓<br>Heat | ASO with short-circuit of load (Short-circuit between upper and lower sides) | _                         | 0                                                                                                                                                                    | 0              | _                                              | _                       | 0                                      | <b>©</b>    | _        | 0                                 | _                                  | 0                   | <b>©</b>      | _          |

|   |                                                                                           |                   | R <sub>DS(on)</sub>                                                          | 0                         | 0                                                                                                                                                                    | 0              | 0                                              | 0                       | 0                                      | 0           | 0        | 0                                 | 0                                  | 0                   | 0             | _          |

|   |                                                                                           |                   | Switching                                                                    | 0                         | 0                                                                                                                                                                    | 0              | 0                                              | 0                       | 0                                      | 0           | 0        | 0                                 | 0                                  | 0                   | 0             | _          |

|   |                                                                                           |                   | Built-in Di trr                                                              | _                         | 0                                                                                                                                                                    | 0              | _                                              | _                       | 0                                      | 0           | _        | 0                                 | _                                  | 0                   | 0             | _          |

| 3 | 3 Built-in diode destruction                                                              |                   | _                                                                            | 0                         | 0                                                                                                                                                                    | _              | _                                              | 0                       | 0                                      | _           | 0        | _                                 | 0                                  | 0                   | _             |            |

| 4 | 4 Destruction by parasitic oscillation when operating with MOS FETs connected in parallel |                   |                                                                              | _                         | _                                                                                                                                                                    | 0              | 0                                              | _                       |                                        | 0           | 0        | _                                 | _                                  | _                   | _             | 0          |

| 5 | 5 Gate surge or electrostatic destruction                                                 |                   |                                                                              |                           | Guard against static electricity during handling (including electrostatic charges on the mounting equipment), and against external surges that reach to the circuit. |                |                                                |                         |                                        |             |          |                                   |                                    |                     |               |            |

#### Power MOS FET 2. Power MOS FET Destruction Mechanisms and Countermeasures

#### (1) Avalanche destruction mode

A phenomenon whereby destruction occurs if a surge voltage exceeding the rated  $V_{DSS}$  of the component is applied between the drain and source, destruction voltage  $V_{(BR)DSS}$  (whose value differs according to the destruction current) is reached, and a certain energy level or higher is attained. This destruction energy differs according to the individual product and operating conditions.

#### (2) ASO (Area of Safe Operation) destruction

Mostly caused by heat caused by exceeding the so-called Area of Safe Operation, in which component maximum rating drain current Id, drain-source voltage  $V_{DSS}$ , or allowable channel dissipation Pth(W) is exceeded. Main causes of heat radiation are classified as a continuous or transient factors.

1. Continuous factors: Heat radiation due to DCASO (loss caused by DC power application)

: On-resistance  $R_{DS(on)}$  loss ( $R_{DS(on)}$  increases at high temperatures)

: Loss due to leakage current I<sub>DSS</sub> (extremely small compared with other loss)

2. Transient factors : Pulse ASO (1 shot pulse application)

: Load shorting ASO

: Switching loss (turn-on, turn-off)\*

: Internal diode trr loss (Upper/lower arm shorting loss)\*

All are temperature-dependent. Asterisked items also depend on operating frequency f.

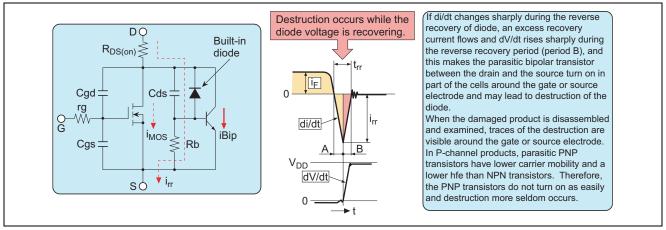

#### (3) Internal diode destruction

This is a mode in which, when a parasitic diode configured between the source and drain operates, a power MOSFET parasitic bipolar transistor operates and breaks down in reverse recovery of that diode. (For details, see section 2.4, Internal Diode Destruction.)

(4) Destruction due to parasitic oscillation

This destruction mode is prone to occur in the case of parallel connection. (For details, see section 2.5, Destruction Due to Parasitic Oscillation, and section 2.6, Notes on Parallel Connection.)

(5) Gate surge, electrostatic destruction

Main types are gate overvoltage destruction caused by surge application between the gate and source from external circuitry, and gate destruction ESD (electrostatic discharge) caused by static electricity due to handling (including a charge from mounting or measuring equipment).

Table 2.1 shows the importance of the above five modes in various devices and applications, and taking these points into account when designing circuits and selecting components is an effective means of preventing various problems.

From this standpoint, the following considerations are important.

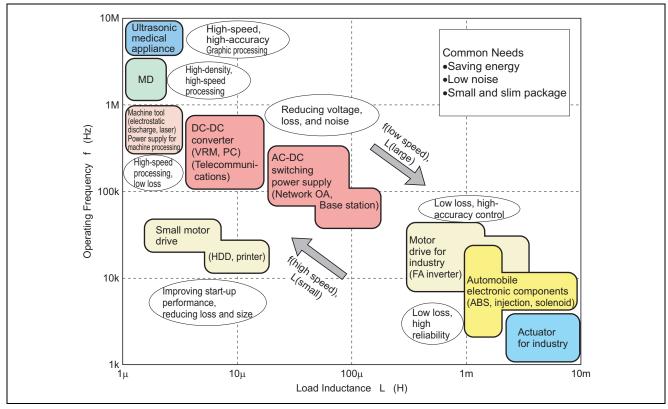

#### 2.1.2 Power MOS FET Applications and Operating Range

Figure 2.1 shows the kind of operating conditions in which power MOS FET applications are used, with load inductance and operating frequency as parameters.

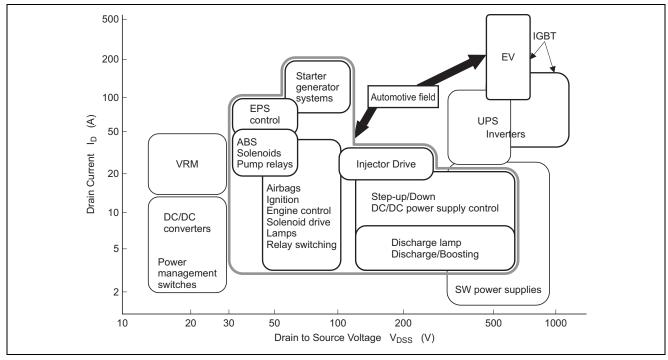

Figure 2.1 Power MOS FET Applications

Market requirements are (1) improved energy saving, (2) lower noise (environmental considerations), (3) smaller, thinner design.

With regard to the characteristics demanded of power MOS FETs, the most important characteristics and specifications naturally differ according to the field and application concerned.

Consequently, a demand has recently arisen for products specific to particular applications.

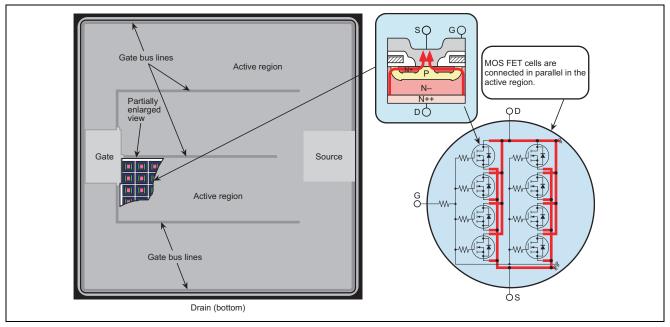

#### 2.1.3 Power MOS FET Structure

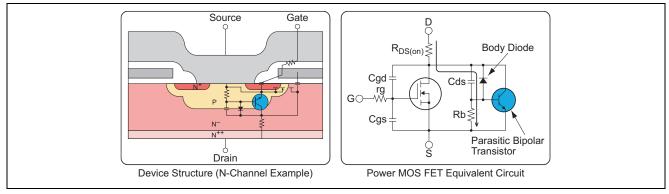

Figure 2.2 shows an N-channel power MOS FET chip and its internal structure.

As shown in the figure, the internal structure of an N-channel power MOS FET chip comprises a large number of cells connected in parallel. As shown in the enlarged cell diagram, current flows in the source  $\rightarrow$  drain direction (the reverse is true in a P-channel type).

Figure 2.2 N-Channel Power MOS FET Chip and Internal Structure

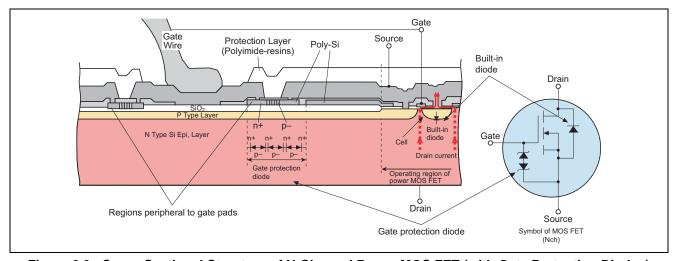

Figure 2.3 shows the cross-sectional structure of an N-channel power MOS FET (with gate protection diodes).

Figure 2.3 Cross-Sectional Structure of N-Channel Power MOS FET (with Gate Protection Diodes)

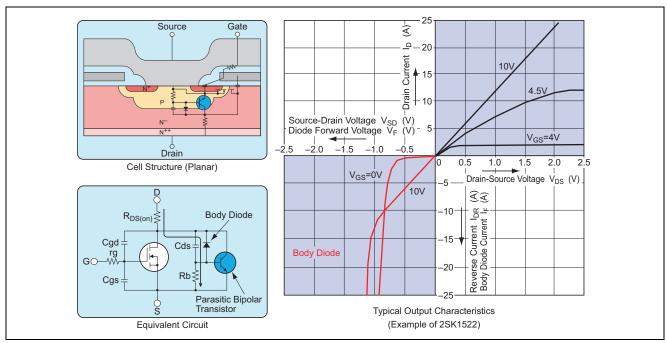

Figure 2.4 shows the output static characteristics and diode characteristics of a high-withstand-voltage power MOS FET (2SK1522). When a power MOS FET is used in a monitor drive, UPS (uninterruptible power supply), or similar application, the internal diode characteristics can be used effectively. The cell cross-sectional structure of a general power MOS FET plate structure is shown, together with an equivalent circuit diagram. A power MOS FET has a structure in which bipolar transistors are connected in parallel between drain and source. These transistors operate at the time of transitions, and are designed so that Rb is made small, for example, so as not to affect the MOS FET destruction tolerance.

Figure 2.4 Output Static Characteristics and Diode Characteristics (High Withstand Voltage)

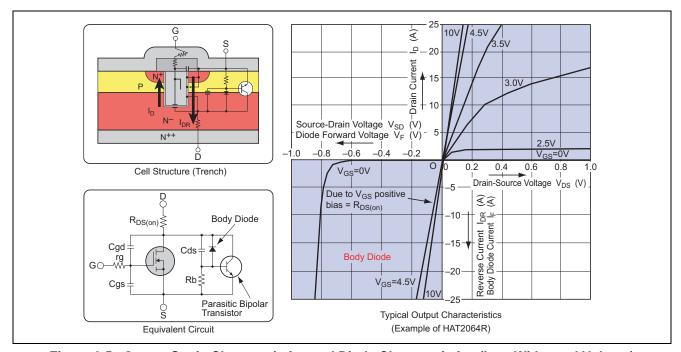

Figure 2.5 shows the output static characteristics and diode characteristics of a low-withstand-voltage power MOS FET (HAT2064R) in the same way as in the previous section. Low-withstand-voltage power MOS FETs attain an ultra-low on-resistance characteristic on the order of several m $\Omega$  or less, and are therefore much smaller than a rectification Schottky barrier diode (SBD) low-V<sub>F</sub> component (V<sub>F</sub> = 0.4 to 0.5 V), and are widely used as MOS synchronous rectification components for the purpose of achieving higher efficiency of low-voltage power supplies (Vout = 3.3 V or less).

Figure 2.5 Output Static Characteristics and Diode Characteristics (Low Withstand Voltage)

#### 2.2 Avalanche Destruction

#### 2.2.1 Explanation of Avalanche Destruction

Avalanche destruction is a mode in which a flyback voltage generated when dielectric load switching operation is turned off, or a spike voltage due to leakage inductance, exceeds the power MOS FET drain rated withstand voltage, entered in a destruction area, and destruction occurs.

#### 2.2.2 Avalanche Destruction Resistance Test Circuit and Waveform

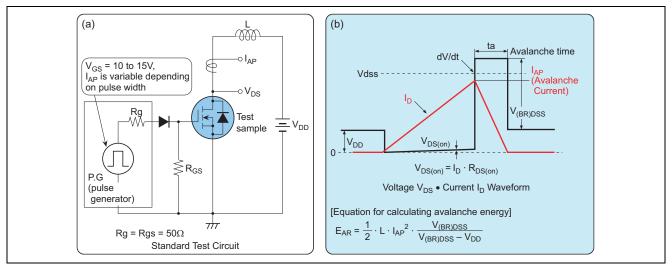

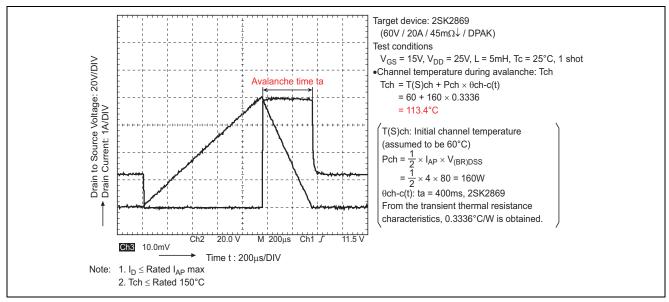

Figure 2.6 shows an avalanche destruction resistance standard test circuit (a) and its operational waveform (b).

Figure 2.6 Avalanche Destruction Resistance Test Circuit and Waveform

Period ta in the waveform in (b) is defined as the avalanche time. The range in which drain-source peak voltage Vds(p) satisfies the condition  $Vdss \leq Vds(p) < V_{(BR)DSS}$  is an area in which the so-called rated voltage is exceeded but avalanche destruction has not been reached. In this kind of operation area, the avalanche area may or may not actually be entered depending on actual withstand voltage  $V_{(BR)DSS}$  of the component, but it is advisable to select a product with guaranteed avalanche resistance. Avalanche resistance guaranteed products are all subjected to final screening by the standard circuit shown in (a). For avalanche resistance guaranteed products, avalanche current rated value  $I_{AP}(A)$  and avalanche energy value  $E_{AR}(J)$  are stipulated.  $E_{AR}$  is expressed by equation (1).

$$E_{AR} = Pd \cdot t = \frac{1}{2} V_{(BR)DSS} \cdot I_{AP} \cdot ta = \frac{1}{2} \cdot L \cdot I_{AP}^2 \cdot \frac{V_{(BR)DSS}}{V_{(BR)DSS} - V_{DD}}$$

(J) .....(1)

Also, with regard to peak channel temperature Tch(peak) in the avalanche operation state, use within rating channel temperature Tch  $\leq 150^{\circ}$ C is necessary. An example of calculation of this channel temperature is given in another section.

#### 2.2.3 Avalanche Energy Calculation Method

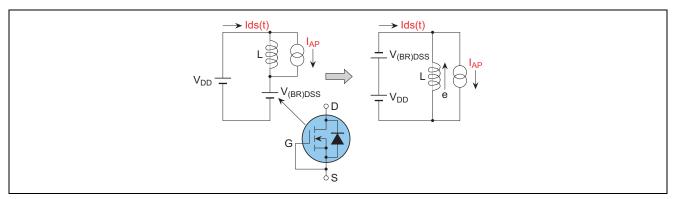

Figure 2.7 shows an avalanche test equivalent circuit.

Figure 2.7 Avalanche Test Equivalent Circuit

Avalanche energy value  $E_{AR}$  in the equivalent circuit is expressed by equation (1).

Vds(t) and Id(t) are as follows:

$$Vds(t) = V_{(BR)DSS}$$

.....(2)

$$Id(t) = I_{AP} - \frac{I_{AP}}{ta} t \qquad (3)$$

$$ta = \frac{L \cdot I_{AP}}{V_{(BR)DSS} - V_{DD}} \qquad (4)$$

Substituting (2) and (3) in equation (1):

$$\begin{split} E_{AR} &= \int_0^{ta} V_{(BR)DSS} \bigg( I_{AP} - \frac{I_{AP}}{ta} \ t \bigg) dt = \int_0^{ta} \bigg( V_{(BR)DSS} \cdot I_{AP} - \frac{V_{(BR)DSS} \cdot I_{AP} \cdot t}{ta} \bigg) dt \\ &= \bigg[ V_{(BR)DSS} \cdot I_{AP} \cdot t - \frac{V_{(BR)DSS} \cdot I_{AP} \cdot t^2}{2ta} \bigg]_0^{ta} = \frac{1}{2} \cdot V_{(BR)DSS} \cdot I_{AP} \cdot ta \end{split}$$

Substituting ta of equation (4) in the above equation:

$$\therefore E_{AR} = \frac{1}{2} \cdot L \cdot I_{AP}^2 \cdot \frac{V_{(BR)DSS}}{V_{(BR)DSS} - V_{DD}}$$

#### 2.2.4 Classification of Avalanche Destruction Factors

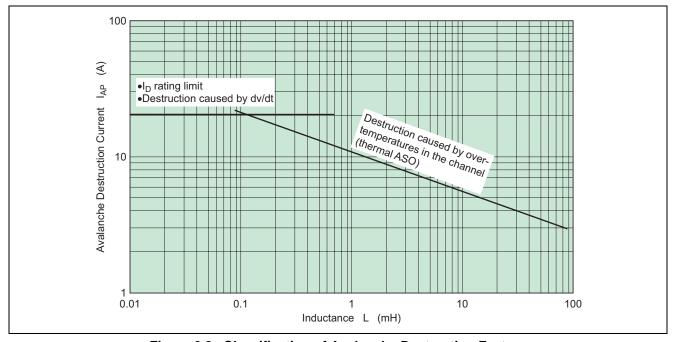

The following three factors, illustrated in figure 2.8, affect the avalanche destruction resistance value.

- (1) Limitation due to drain current Id rating

- (2) Limitation due to excessive channel temperature in avalanche

- (3) Decline of destruction resistance due to dV/dt (figure 2.6(b))

Figure 2.8 Classification of Avalanche Destruction Factors

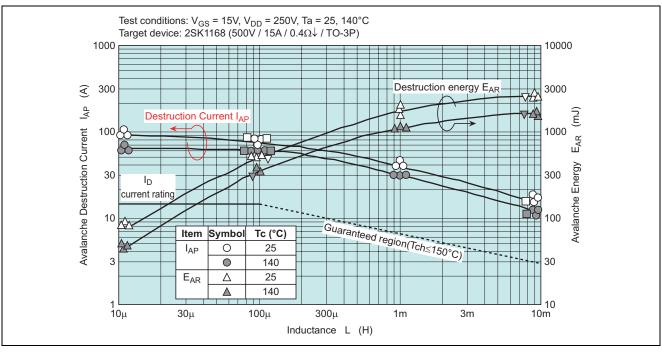

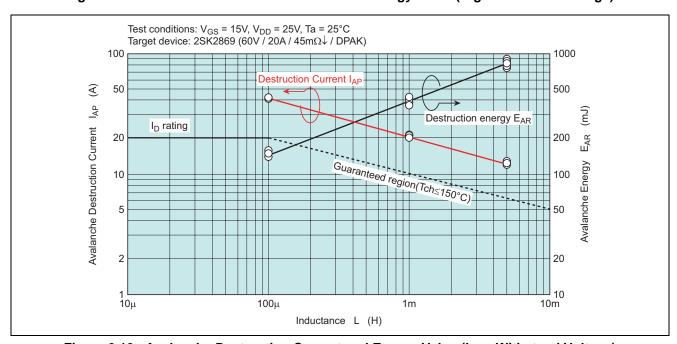

#### 2.2.5 Avalanche Destruction Current and Energy Value

Figures 2.9 and 2.10 show actual data show how avalanche destruction current  $I_{AP}$  and avalanche destruction energy  $E_{AR}$  vary with the inductance L value for a high-withstand-voltage 500 V class component and low-withstand-voltage 60 V class component, respectively. The graphs show that as the inductance L value increases, destruction current  $I_{AP}$  tends to fall, but the destruction energy  $E_{AR}$  value tends to increase. Therefore, to see the variations in avalanche resistance, it is necessary to consider both destruction current  $I_{AP}$  and energy value  $E_{AR}$ . In general, it can probably be stated that an component with a small inductance value L and large destruction energy value  $E_{AR}$  has good avalanche resistance.

Figure 2.9 Avalanche Destruction Current and Energy Value (High Withstand Voltage)

Figure 2.10 Avalanche Destruction Current and Energy Value (Low Withstand Voltage)

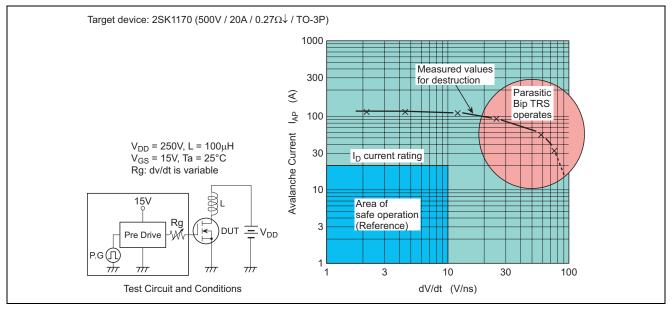

#### 2.2.6 Avalanche Destruction Current and dV/dt Resistance

The third factor, the relationship between avalanche destruction resistance and dV/dt, will now be considered. Figure 2.11 shows measured values for avalanche destruction current  $I_{AP}$  dependence on dV/dt resistance. In a power MOS FET, as explained before, a parasitic bipolar transistor is formed between the drain and source in the structure shown in figure 2.4. As dV/dt is made steeper, a transient current flows through capacitance Cds, and this transistor is turned on, leading to a drop in destruction resistance. In the example in figure 2.11, the area in which  $dV/dt \le 10 \ V/\mu s$  can be called a safe area. This value differs according to the particular component.

Figure 2.11 Avalanche Destruction Current and dV/dt Resistance

#### 2.2.7 Simple Determination Method for Avalanche Resistance Guaranteed Products

A simple determination method for avalanche resistance guaranteed products is described here. The description is based on the avalanche operation waveform (1 shot period) in figure 2.12, taking the example of a 2SK2869 (60 V/20 A, 45 m $\Omega$  $\downarrow$ , DPAK package) avalanche guaranteed product as the tested device.

Figure 2.12 Avalanche Time and Drain-Source Voltage (Drain Current)

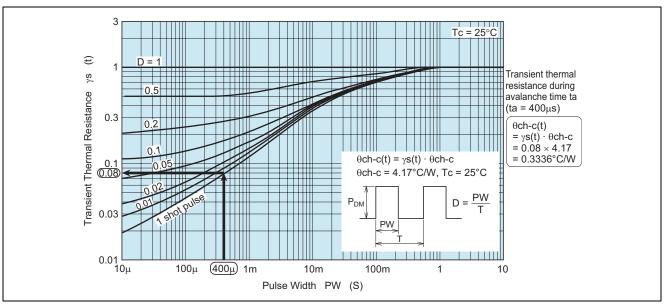

Figure 2.13 2SK2869 Transient Thermal Resistance Characteristics (Data Sheet)

Trial calculations have been carried out assuming that start channel temperature  $T(s)ch = 60^{\circ}C$  before avalanche operation (due to the channel temperature rise caused by on-resistance  $R_{DS(on)}$  and switching loss). For dV/dt, a range of safe operation was assumed. Therefore, the following two checkpoints should be confirmed.

- (1) Whether avalanche current  $I_{AP}$  is within avalanche guarantee value current rating  $I_{AP}$ max (For 2SK2869 avalanche guaranteed current  $I_{AP}$ , when L = 5 mH,  $I_{AP}$ max = 6.2 A (figure 2.10))

- (2) Whether channel temperature Tch in avalanche operation is within the range Tchmax  $\leq 150^{\circ}$ C First, as avalanche current  $I_{AP}$  in (1) is 4 A from the waveform, it can be confirmed that it is within avalanche rated current +  $I_{AP}$ max  $\leq 6.2$  A.

Next, channel temperature Tch in avalanche operation in (2) is expressed by equation (1).

$$\begin{aligned} & Tch = T(s)ch + Pch \times \theta ch - c(t) \\ & = T(s)ch + \left(\frac{1}{2} \times I_{AP} \times V_{(BR)DSS}\right) \times \theta ch - c(t) \end{aligned} \qquad .....(1)$$

Here,  $\theta$ ch-c(t) is transient thermal resistance, and is calculated from the 2SK2869 data sheet transient thermal resistance characteristics in figure 2.13.  $\theta$ ch-c(t = 400  $\mu$ s) when avalanche opened time ta = 400  $\mu$ s can be calculated from the graph as shown below.

$$\theta ch - c(t = 400 \mu s) = \gamma(t) \times \theta ch - c$$

= 0.08 × 4.17

= 0.3336°C/W

Therefore, substituting numeric values in equation (1) gives:

Tch = T(s)ch +

$$\left(\frac{1}{2} \times I_{AP} \times V_{(BR)DSS}\right) \times \theta ch - c(t)$$

=  $60 + \left(\frac{1}{2} \times 4 \times 80\right) \times 0.3336$

and it can be confirmed that Tch is within the Tchmax  $\leq 150^{\circ}$ C rating.

Thus, it is determined that the value is within the avalanche guarantee range.

When more complex conditions or components are involved, individual measures should be taken.

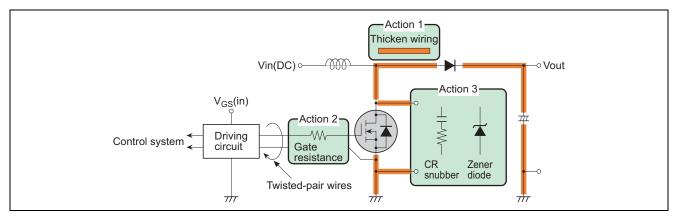

#### 2.2.8 Avalanche Destruction Countermeasures

Figure 2.14 shows avalanche destruction countermeasures (methods of suppressing surge voltages).

Figure 2.14 Avalanche Destruction Countermeasures

In avalanche destruction, destruction is caused by a counter voltage due to floating inductance (inductance load). As a characteristic after destruction, electrodes are shorted.

There are three countermeasures for avalanche destruction, as follows.

- (1) Make large-current path wiring as short and thick as possible to reduce floating inductance.

- (2) Insert a gate series resistance Rg, and suppress dV/dt. As a surge voltage occurs when switching off, surge voltages are suppressed by making the value of turn-off constant Rg large, but if the value is made too large, switching loss will increase. This should be considered when deciding on the circuit constant.

- (3) Insertion of CR snubber and Zener diode

When a surge absorption snubber, etc., is inserted, the wiring should be made short and thick, and connection

should be made directly to the power MOS FET drain and source terminals.

### 2.3 ASO Destruction (Heat Radiation Design)

#### 2.3.1 Explanation of ASO Destruction

ASO destruction refers to a mode in which heat radiation is caused instantaneously and locally, and destruction occurs, when an overcurrent and the used voltage are applied simultaneously due to load shorting, etc., that does not occur in normal operation. It also refers to a mode in which the channel temperature rises excessively due to continuous heat radiation, thermal runaway occurs, and destruction results, when chip heat radiation is not performed properly due to thermal mismatching or a high repetition frequency.

#### 2.3.2 ASO Destruction Countermeasures

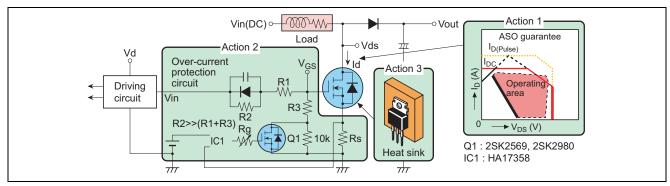

Figure 2.15 illustrates ASO destruction and countermeasures.

Figure 2.15 ASO Destruction (Heat Radiation Design) and Countermeasures

There are three countermeasures, as follows.

- (1) Check inclusion within the forward bias ASO (Area of Safe Operation) guarantee, and that the temperature derating is adequate.

- (2) If load shorting is predicted, insert an overcurrent protection circuit.

If the designed drain load current is exceeded, the voltage arose on Rs is detected, MOS FET Q1 is turned on, shorting occurs between G-S of the main power MOS FET via R3, and it is turned off. In this case the value of R3 is made larger than R1 determined as a normal switching off time constant, and is made a constant that prevents the occurrence of surge at the time of overcurrent (cutoff) protection. Alternatively, it is possible to perform cutoff control of speed at the time of cutoff in a list by means of Q1 gate resistance Rg. MOS FET gate-source drive voltage V<sub>GS</sub> in normal operation is expressed by equation (1).

$$V_{GS} = Vin \times \frac{R3 + 10k\Omega}{(R3 + 10k\Omega) + (R1 + R2)}$$

....(1)

$V_{GS}$  is set to a value ( $V_{GS}$  = approx. 10 V) at which a power MOS FET operates fully in the on-resistance region. Gate retention voltage  $V_{GS}$ (cut) at the time of overcurrent cutoff is expressed by equation (2).

$$V_{GS(cut)} = Vin \times \frac{R3}{R1 + R2 + R3} \qquad (2)$$

$V_{GS}(cut)$  must be set to a value smaller than power MOS FET gate-source cutoff voltage  $V_{GS(off)}$ . The  $V_{GS(off)}$  temperature characteristic ( $\alpha = -5$  mV to -7 mV/ $^{\circ}$ C) is also taken into consideration.

(3) Carry out radiation design allowing a sufficient margin. This is covered in the practical example of radiation design.

#### 2.3.3 Forward Bias ASO (Area of Safe Operation)

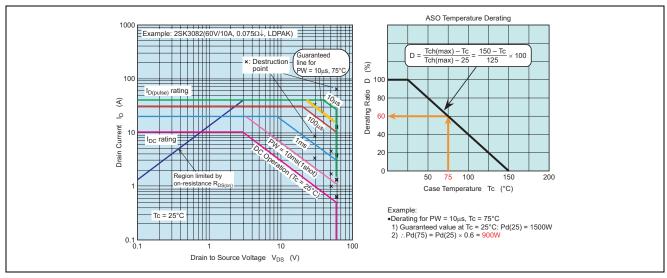

Figure 2.16 shows a forward bias ASO graph (2SK3082) and the corresponding temperature derating method. (For information on an Area of Safe Operation (ASO), refer to the description of the use of power MOS FET characteristics described earlier.)

Figure 2.16 Forward Bias ASO Diagram (Area of Safe Operation)

With regard to the ASO temperature derating method, PW =  $10 \mu s$ , Tc =  $75^{\circ}$ C derating will be described as an example.

First, regarding PW = 10  $\mu$ s and Tc = 25°C guarantee values, this ASO diagram gives a Pd(25) = 1500 W (= Vds  $\times$  I<sub>D</sub> = 50 V  $\times$  30 A) power line. Then, as Tc = 75°C derating ratio D = 60%,

$$Pd(75) = Pd(25) \times 0.6$$

= 1500 × 0.6

= 900W

In the ASO diagram, this is the area indicated by the PW =  $10 \mu s$ ,  $Tc = 75^{\circ}C$  line in figure 2.16.

#### 2.3.4 Load Shorting Resistance and Countermeasures

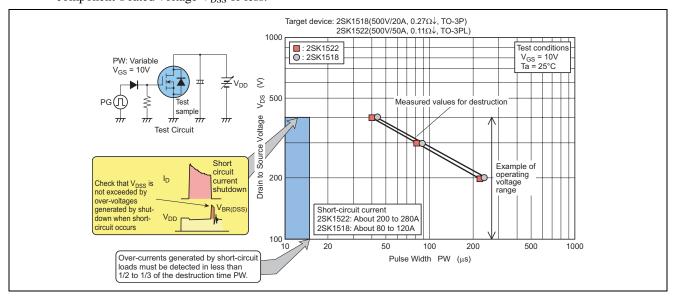

Figure 2.17 shows power MOS FET load shorting resistance (examples of the 2SK1518 and 2SK1522). When a power MOS FET is used in a motor drive application, if the load should short, it is necessary to be able to withstand the conditions without breaking down until the overcurrent protection circuit operates.

- 1. As shown in figure 2.17, this load shorting resistance is dependent on the power supply voltage  $V_{DD}$  ( $\approx V_{DS}$ ) used, with destruction occurring in a shorter time the greater the value of  $V_{DS}$  (as the power applied due to load shorting increases). This destruction time differs from product to product, but the overcurrent protection detection time in the event of load shorting should be set to between 1/2 and 1/3 or less of the destruction time. In the case of a power MOS FET, a setting of between 10  $\mu$ s and 15  $\mu$ s or less can be said to be safe.

- 2. Next, when load shorting occurs, as the short-circuit current an overcurrent of around 5 to 10 times the normal operation current flows, and this is cut off.

A point to be noted here is the surge voltage that is generated when this overcurrent is cut off. This is showed as the waveform in figure 2.17. As a current considerably larger than the steady state current flows, it is necessary to set a cutoff turn-on time slower than the steady state on/off speed, and suppress the cutoff surge voltage to the component's rated voltage V<sub>DSS</sub> or less.

Figure 2.17 Power MOS FET Load Shorting Resistance and Countermeasures

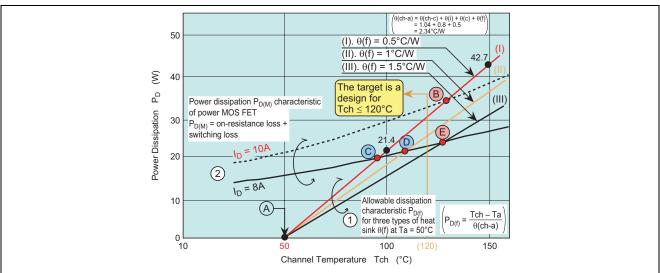

#### 2.3.5 Heat Radiation Design

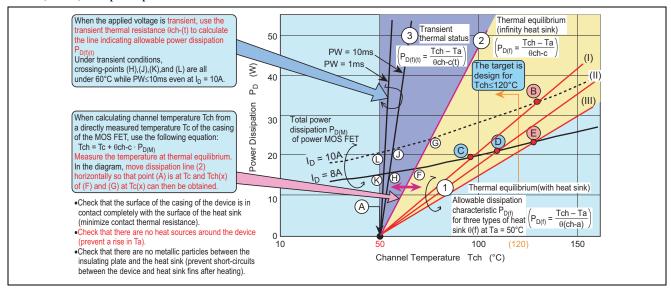

When carrying out mounting design for power devices, it goes without saying that cooling technology — that is, how heat is to be radiated efficiently under various environmental conditions — is an important consideration, but how to perform theoretical heat calculations efficiently is also important. Examples are given here of practical heat radiation design in which the operating channel temperature of a power MOS FET can be calculated theoretically.

- 1. Preconditions when using a 2SK1170 (500 V/20 A, 0.27  $\Omega$ , TO-3P) are shown below.

- (1) Operating conditions

- Ambient temperature  $Ta = 50^{\circ}C$

- Operating current Id = 8A, 10A (2 conditions)

- PW =  $10 \mu s$ , duty = 50% max (f = 50 kHz operation)

- Switching loss P(tf) = 500 W, tf period = 0.2  $\mu$ s (ton loss is omitted here)

Design target: Tch ≤ 120°C

#### Power MOS FET 2. Power MOS FET Destruction Mechanisms and Countermeasures

- (2) Heat sink thermal resistance θf-a: 3 kinds: (I). 0.5°C/W, (II). 1.0°C/W, (III). 1.5°C/W

- (3) Mounting method: Insulating mica used, silicon grease used

$(\theta(i) + \theta(c)) = 0.8^{\circ}C/W$

where  $\theta(i)$ : Insulating mica thermal resistance

$\theta(c)$ : Contact thermal resistance

Table 2.2 Thermal Resistance of Various Transistor Packages

|                      | Thermal Res               | sistance             | DPAK        | TO-220AB           | LDPAK                               | TO-220FM   | TO-3P      | TO-3PFM    | TO-3PL     |

|----------------------|---------------------------|----------------------|-------------|--------------------|-------------------------------------|------------|------------|------------|------------|

| Rth(ch-c) (°C/W)     |                           |                      | Rth(ch-c) = | Tj max – Tc<br>Pch | (See individual catalog for Pch(W)) |            |            |            |            |

| Rth(c-a) *1 (°C/W)   |                           |                      | 178         | 80                 | 83.3                                | 62.5       | 55         | 42         | 45         |

| (Rth(i) +<br>Rth(c)) | No<br>insulation<br>plate | With silicon grease  | 0.3 to 0.6  | 0.3 to 0.5         | 0.3 to 0.5                          | 0.4 to 0.6 | 0.1 to 0.2 | 0.3 to 0.5 | 0.1 to 0.2 |

| (°C/W)               |                           | No<br>silicon grease | 2.0 to 2.5  | 1.5 to 2.0         | 1.5 to 2.0                          | 1.5 to 2.0 | 0.5 to 0.9 | 1.0 to 1.5 | 0.4 to 0.5 |

|                      | Mica insertion            | With silicon grease  | _           | 2.0 to 2.5         | _                                   | _          | 0.5 to 0.8 | _          | 0.5 to 0.7 |

|                      | (t = 50 to<br>100μm)      | No<br>silicon grease | _           | 4.0 to 6.0         | _                                   | _          | 2.0 to 3.0 | _          | 1.2 to 1.5 |

Note: 1. Reference value

Based on these preconditions, a design target channel temperature of Tch ≤ 120°C is set.

2. In this method, allowable power dissipation characteristics under various heat radiation conditions (1) and the power dissipation P<sub>D</sub> characteristic according to a rise in the power MOS FET channel temperature (2) are calculated, and the point of intersection at which functions (1) and (2) overlap is taken as the channel temperature in the saturation state to be found. Results calculated on the basis of the above operating and environmental usage conditions are shown in figure 2.18.

Figure 2.18 Channel Temperature Tch and Power Dissipation Pn

#### Power MOS FET 2. Power MOS FET Destruction Mechanisms and Countermeasures

The procedure to reach figure 2.18 is described below.

- 3. With reference to the contents of the box below, allowable power dissipation characteristics under the aforementioned various heat radiation conditions (1) and the power MOS FET power dissipation characteristic (2) are calculated. In the calculation of power MOS FET power dissipation  $P_D$ , power MOS FET on-resistance temperature coefficient  $\alpha$  (coefficient when Tch = 25°C is taken as 1.0) can be read beforehand from the Ron-Tc characteristic of the individual data sheet, and that value entered on the horizontal axis as in table 2.3. Table 2.3 shows the calculation results.

- Calculate and plot allowable power dissipation straight line  $P_{D(f)}$  under each heat radiation condition ((1) in figure) First, find total thermal resistance  $\theta$ (ch-a) under each heat radiation condition.

$$\theta(\text{ch-a}) = \theta(\text{ch-c}) + (\theta(i) + \theta(c)) + \theta(f) \qquad \dots (1)$$

From equation (1),  $\theta$ (ch-a) when using (I) heat sink is as follows:

$$\theta$$

(ch-a) = 1.04 + 0.8 + 0.5 = 2.34°C/W (Similarly for (II) = 2.84°C/W, (III) = 3.34°C/W)

Allowable power dissipation  $P_{D(f)}$  is expressed by equation (2). Three points can be used for the allowable loss curve.

$$P_{D(f)} = \frac{Tch - Ta}{\theta(ch-a)}$$

(2)

Under condition (I), assuming Tch = 50, 100, 150°C gives 0W, 21.4 W, 42.7 W respectively ( $\approx (150 - 50)/2.34$ ) Calculation can be performed for the 2 conditions (II) and (III) in the same way, and 3 straight lines plotted.

• Calculate and plot power MOS FET power dissipation curve  $P_{D(M)}$  ((2) in figure)

Power MOS FET on-resistance R<sub>DS(on)</sub> has a positive temperature characteristic.

That is to say, there is a curvilinear rise (as shown in individual catalogs) as Tch rises.

When power MOS FET total power dissipation  $P_{D(M)}$  accompanying the temperature rise when  $I_D = 8A$ , 10A is found, taking this point into consideration, 2 curves can be drawn.

Table 2.3 Calculation of Power MOS FET Power Dissipation P<sub>D(M)</sub> (Example of 2SK1170)

| Item Tch(°C)                                                 |                                                                                                | 25                   | 40   | 60   | 80   | 100  | 120  | 140  | 150  | Notes |                                                       |

|--------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------|------|------|------|------|------|------|------|-------|-------------------------------------------------------|

| $R_{DS(on)}$ temperature coefficient $\alpha$ for Tch = 25°C |                                                                                                |                      | 1.0  | 1.09 | 1.27 | 1.5  | 1.73 | 2.0  | 2.27 | 2.41  | See Ron-Tc characteristic in individual data sheet    |

| MOS<br>power                                                 | On-resistance loss $P_{ON} = I_D^2 \cdot R_{DS(on)max}$ $\times \alpha \cdot \frac{t_{ON}}{T}$ | I <sub>D</sub> = 8A  | 8.64 | 9.4  | 11.0 | 13.0 | 14.9 | 17.3 | 19.6 | 20.8  | Note R <sub>DS(on)</sub> temperature dependence       |

| dissipation                                                  |                                                                                                | I <sub>D</sub> = 10A | 13.5 | 14.7 | 17.1 | 20.3 | 23.4 | 27   | 30.6 | 32.5  | aoponaonos                                            |

|                                                              | Switching loss *1 $P_S = \frac{tf}{T} P(tf)$                                                   |                      | 5    | 5    | 5    | 5    | 5    | 5    | 5    | 5     | Note operating frequency dependence                   |

| Total power d                                                | issipation P <sub>D(M)</sub>                                                                   | I <sub>D</sub> = 8A  | 13.6 | 14.4 | 16.0 | 18.0 | 19.9 | 22.3 | 24.6 | 25.8  | See separate section for detailed calculation of R, L |

| . D(W) - 1 ON .                                              |                                                                                                | I <sub>D</sub> = 10A | 18.5 | 19.7 | 22.1 | 25.5 | 28.4 | 32.0 | 35.6 | 37.5  | load Ron loss, SW loss                                |

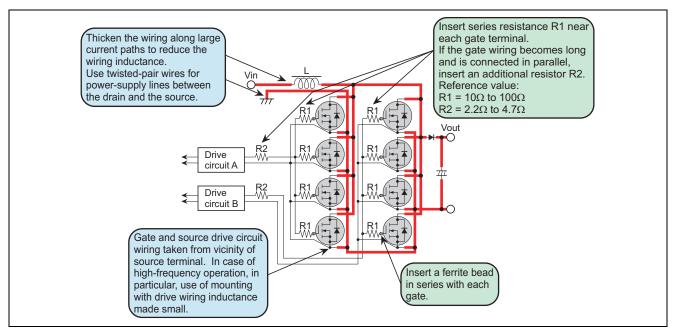

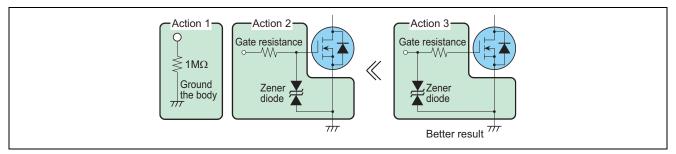

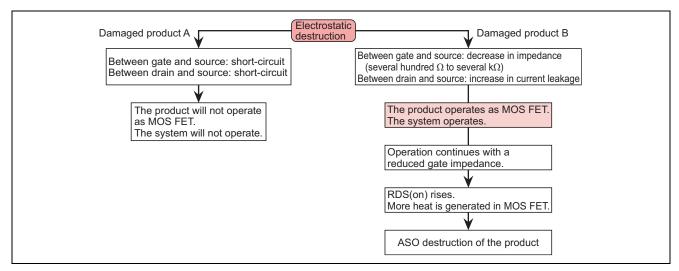

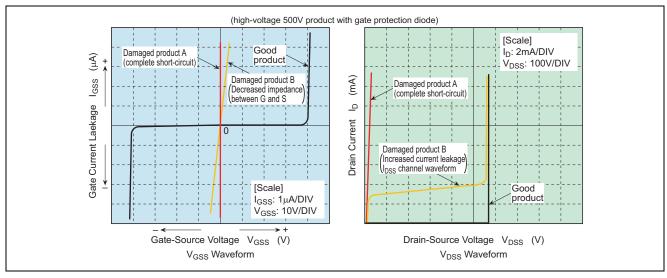

Note: 1. For the sake of simplicity, the same  $P_S$  value is used for both  $I_D$  = 8 A and 10 A.