#### 1.0 Features

- Isolated AC/DC offline 100V<sub>AC</sub>/230V<sub>AC</sub> LED driver

- Line frequency ranges from 45Hz to 66Hz

- Intelligent wall dimmer detection

- » Leading-edge dimmer

- » Trailing-edge dimmer

- » No-dimmer detected

- » Unsupported dimmer

- Hybrid dimming scheme

- Wide dimming range from 1% up to 100%

- No visible flicker

- Resonant control to achieve high efficiency, 85% without dimmer

- Temperature compensated LED current

- Small size design

- » Small size input bulk capacitor

- » Small size output capacitor

- » Small transformer

- Primary-side sensing eliminates the need for optoisolator feedback and simplifies design

- Tight LED current regulation ± 5%

- Fast start-up, typically 10µA start-up current

- Hot-plug LED module support

- Multiple protection features:

- » LED open circuit protection

- » Single-fault protection

- » Over-current protection

- » LED short circuit protection

- » Current sense resistor short circuit protection

- » Over-temperature protection

- » Input over-voltage protection

- Up to 10W output power

#### 2.0 Description

The iW3602 is a high performance AC/DC offline power supply controller for dimmable LED luminaires, which uses advanced digital control technology to detect the dimmer type and phase. The dimmer conduction phase controls the LED brightness. The LED brightness is modulated by PWM-dimming. The iW3602's unique digital control technology eliminates visible flicker.

The iW3602 can operate with all dimmer schemes including: leading-edge dimmer, trailing-edge dimmer, as well as other dimmer configurations such as R-type, R-C type or R-L type. When a dimmer is not present, the controller can automatically detect that there is no dimmer.

The iW3602 operates in a quasi-resonant mode to provide high efficiency. The iW3602 provides a number of key built-in features. The iW3602 uses advanced primary-side sensing technology to achieve excellent line and load regulation without secondary feedback circuitry. In addition, the iW3602's pulse-by-pulse waveform analysis technology allows accurate LED current regulation. The iW3602 maintains stability over all operating conditions without the need for loop compensation components. Therefore, the iW3602 minimizes external component count, simplifies EMI design and lowers overall bill of materials cost.

# 3.0 Applications

- Dimmable LED luminaires

- Optimized for 3W to 10W output power

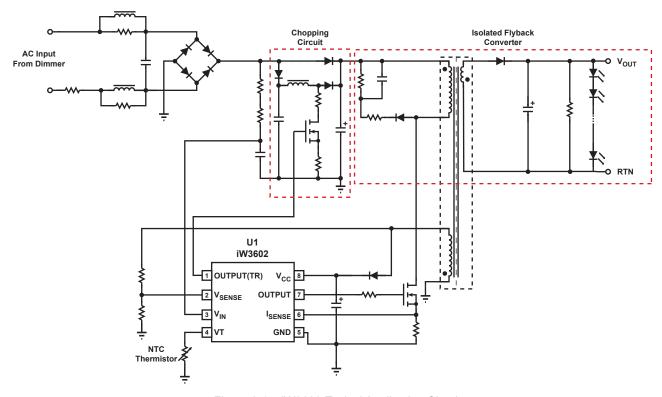

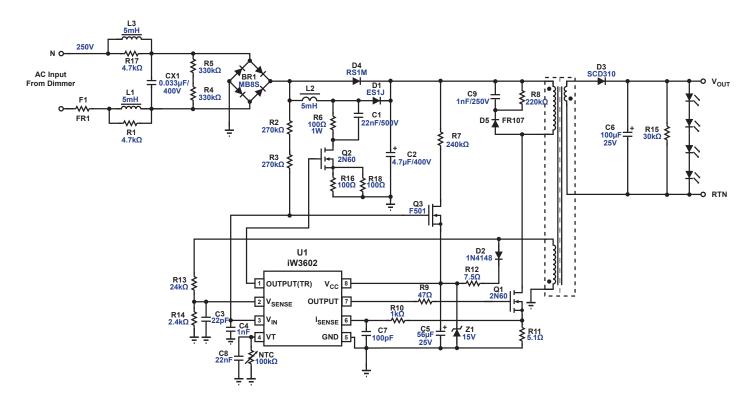

Figure 3.1: iW3602 Typical Application Circuit

### **4.0 Pinout Description**

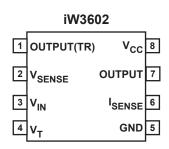

Figure 4.1: 8 Lead SOIC-8 Package

| Pin # | Name               | Type         | Pin Description                                                                 |

|-------|--------------------|--------------|---------------------------------------------------------------------------------|

| 1     | OUTPUT(TR)         | Output       | Gate drive for chopping MOSFET switch.                                          |

| 2     | V <sub>SENSE</sub> | Analog Input | Auxiliary voltage sense (used for primary side regulation and ZVS).             |

| 3     | V <sub>IN</sub>    | Analog Input | Rectified AC line voltage sense.                                                |

| 4     | V <sub>T</sub>     | Analog Input | External power limit and shutdown control.                                      |

| 5     | GND                | Ground       | Ground.                                                                         |

| 6     | I <sub>SENSE</sub> | Analog Input | Primary current sense (used for cycle-by-cycle peak current control and limit). |

| 7     | OUTPUT             | Output       | Gate drive for main MOSFET switch.                                              |

| 8     | V <sub>cc</sub>    | Power Input  | Power supply for control logic and voltage sense for power-on reset circuitry.  |

Datasheet Rev. 1.2 31-May-2022

# **5.0 Absolute Maximum Ratings**

Absolute maximum ratings are the parameter values or ranges which can cause permanent damage if exceeded. For maximum safe operating conditions, refer to Electrical Characteristics in Section 6.0.

| Parameter                                                   | Symbol                                     | Value                    | Units       |        |

|-------------------------------------------------------------|--------------------------------------------|--------------------------|-------------|--------|

| DC supply voltage range (pin 8, I <sub>c</sub>              | V <sub>cc</sub>                            | -0.3 to 18               | V           |        |

| DC supply current at V <sub>CC</sub> pin                    |                                            | I <sub>cc</sub>          | 20          | mA     |

| OUTPUT (pin 7)                                              |                                            |                          | -0.3 to 18  | V      |

| OUTPUT(TR) (pin 1)                                          |                                            |                          | -0.3 to 18  | V      |

| V <sub>SENSE</sub> input (pin 2, I <sub>VSENSE</sub> ≤ 10m/ | 4)                                         |                          | -0.7 to 4.0 | V      |

| V <sub>IN</sub> input (pin 3)                               |                                            |                          | -0.3 to 18  | V      |

| I <sub>SENSE</sub> input (pin 6)                            |                                            |                          | -0.3 to 4.0 | V      |

| V <sub>T</sub> input (pin 4)                                |                                            | -0.3 to 4.0              | V           |        |

| Power dissipation at T <sub>A</sub> ≤ 25°C                  | Power dissipation at T <sub>A</sub> ≤ 25°C |                          |             | mW     |

| Maximum junction temperature                                |                                            | $T_{JMAX}$               | 150         | °C     |

| Operating junction temperature                              |                                            | T <sub>JOPT</sub>        | -40 to 150  | °C     |

| Storage temperature                                         | Storage temperature                        |                          |             | °C     |

| Thermal Resistance                                          | Junction-to-PCB Board Surface Temperature  | ψ <sub>JB</sub> (Note 1) | 70          | °C/W   |

| Thomas Nosistano                                            | Junction-to-Ambient [Still Air]            | $\theta_{JA}$            | 160         | O/ V V |

| ESD rating per JEDEC JESD22-A                               |                                            | ±2,000                   | V           |        |

| Latch-up test per JESD78A                                   |                                            | ±100                     | mA          |        |

#### Notes:

Note 1.  $\psi_{JB}$  [Psi Junction to Board] provides an estimation of the die junction temperature relative to the PCB [Board] surface temperature. This data is measured at the ground pin (pin 5) without using any thermal adhesives. For iW3602-01 (with exposed pad),  $\psi_{JB}$  = 70°C/W. See Section 9.13 for more information.

#### **6.0 Electrical Characteristics**

$V_{CC}$  = 12V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C, unless otherwise specified (Note 1)

| Parameter                                     | Symbol                  | Test Conditions                                             | Min   | Тур   | Max   | Unit |

|-----------------------------------------------|-------------------------|-------------------------------------------------------------|-------|-------|-------|------|

| V <sub>IN</sub> SECTION (Pin 3)               |                         |                                                             |       |       |       |      |

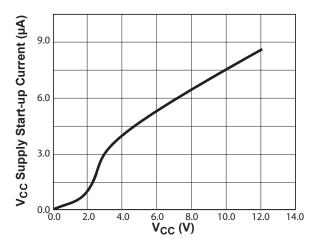

| Start-up current                              | I <sub>INST</sub>       | $V_{IN} = 10V, C_{VCC} = 10\mu F$                           |       | 10    | 15    | μA   |

| Input impedance                               | Z <sub>IN</sub>         | T <sub>A</sub> = 25°C                                       |       | 2.5   |       | kΩ   |

| V <sub>IN</sub> Range                         | V <sub>IN</sub>         |                                                             | 0     |       | 1.8   | V    |

| V <sub>SENSE</sub> SECTION (Pin 2)            |                         |                                                             |       |       |       |      |

| Input leakage current                         | I <sub>IN(Vsense)</sub> | V <sub>SENSE</sub> = 2V                                     |       |       | 1     | μA   |

| Nominal voltage threshold                     | V <sub>SENSE(NOM)</sub> | T <sub>A</sub> = 25°C, negative edge                        | 1.523 | 1.538 | 1.553 | V    |

| Output OVP threshold                          | V <sub>SENSE(MAX)</sub> | T <sub>A</sub> = 25°C, negative edge                        | 1.65  | 1.7   | 1.75  | V    |

| OUTPUT SECTION (Pin 7)                        |                         |                                                             |       |       |       |      |

| Output low level ON-resistance                | R <sub>DS(ON)LO</sub>   | I <sub>SINK</sub> = 5mA                                     |       | 30    |       | Ω    |

| Output high level ON-resistance               | R <sub>DS(ON)HI</sub>   | I <sub>SOURCE</sub> = 5mA                                   |       | 150   |       | Ω    |

| Rise time (Note 2)                            | t <sub>R</sub>          | T <sub>A</sub> = 25°C, C <sub>L</sub> = 330pF<br>10% to 90% |       | 150   |       | ns   |

| Fall time (Note 2)                            | t <sub>F</sub>          | T <sub>A</sub> = 25°C, C <sub>L</sub> = 330 pF<br>90% to 10 |       | 30    |       | ns   |

| Maximum switching frequency (Note 3)          | f <sub>SW(MAX)</sub>    |                                                             |       | 200   |       | kHz  |

| V <sub>CC</sub> SECTION (Pin 8)               |                         |                                                             |       |       |       |      |

| Maximum operating voltage                     | V <sub>CC(MAX)</sub>    |                                                             |       |       | 16    | V    |

| Start-up threshold                            | V <sub>CC(ST)</sub>     | V <sub>CC</sub> rising                                      | 11    | 12    | 13    | V    |

| Undervoltage lockout threshold                | V <sub>CC(UVL)</sub>    | V <sub>CC</sub> falling                                     | 7     | 7.5   | 8     | V    |

| Operating current                             | I <sub>CCQ</sub>        | C <sub>L</sub> = 330pF, V <sub>SENSE</sub> = 1.5V           |       | 4.1   | 4.7   | mA   |

| Zener diode clamp voltage                     | V <sub>Z(CLAMP)</sub>   | $T_A = 25^{\circ}C, I_Z = 5mA$                              | 18.5  | 19    | 20.5  | V    |

| I <sub>SENSE</sub> SECTION (Pin 6)            |                         |                                                             |       |       |       |      |

| Over-current limit threshold                  | V <sub>OCP</sub>        |                                                             | 1.83  | 1.89  | 1.95  | V    |

| I <sub>SENSE</sub> short protection reference | V <sub>RSNS</sub>       |                                                             |       | 0.16  |       | V    |

| CC regulation threshold limit (Note 4)        | $V_{REG-TH}$            |                                                             |       | 1.8   |       | V    |

| V <sub>T</sub> SECTION (Pin 4)                |                         |                                                             |       |       |       |      |

| Power limit high threshold (Note 4)           | V <sub>P-LIM(HI)</sub>  |                                                             |       | 0.56  |       | V    |

| Power limit low threshold (Note 4)            | V <sub>P-LIM(LO)</sub>  |                                                             |       | 0.44  |       | V    |

Datasheet Rev. 1.2 31-May-2022

# 6.0 Electrical Characteristics (cont.)

$V_{CC}$  = 12V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C, unless otherwise specified (Note 1)

| Parameter                       | Symbol                   | Test Conditions           | Min | Тур  | Max | Unit |

|---------------------------------|--------------------------|---------------------------|-----|------|-----|------|

| Shutdown threshold (Note 4)     | V <sub>SH-TH</sub>       |                           |     | 0.22 |     | V    |

| Input leakage current           | I <sub>IN(VT)</sub>      | V <sub>T</sub> = 1.0V     |     |      | 1   | μA   |

| Pull-up current source          | I <sub>VT</sub>          |                           | 90  | 100  | 110 | μA   |

| OUTPUT(TR) SECTION (Pin 1)      |                          |                           |     | ,    |     | •    |

| Output low level ON-resistance  | R <sub>DS-TR(ON)LO</sub> | I <sub>SINK</sub> = 5mA   |     | 100  |     | Ω    |

| Output high level ON-resistance | R <sub>DS-TR(ON)HI</sub> | I <sub>SOURCE</sub> = 5mA |     | 200  |     | Ω    |

#### Notes:

- Note 1. Adjust  $V_{CC}$  above the start-up threshold before setting at 12V.

- Note 2. These parameters are not 100% tested. They are guaranteed by design and characterization.

- Note 3. Operating frequency varies based on the line and load conditions, see Theory of Operation for more details.

- Note 4. These parameters refer to digital preset values, and they are not 100% tested.

# 7.0 Typical Performance Characteristics

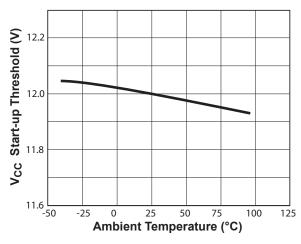

Figure 7.1 : V<sub>CC</sub> vs. V<sub>CC</sub> Supply Start-up Current

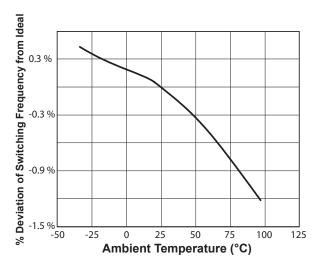

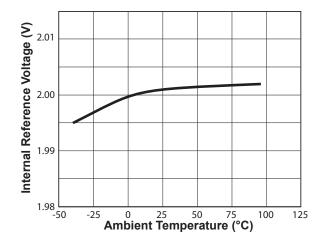

Figure 7.3: % Deviation of Switching Frequency to Ideal Switching Frequency vs. Temperature

Figure 7.2: Start-Up Threshold vs. Temperature

Figure 7.4: Internal Reference vs. Temperature

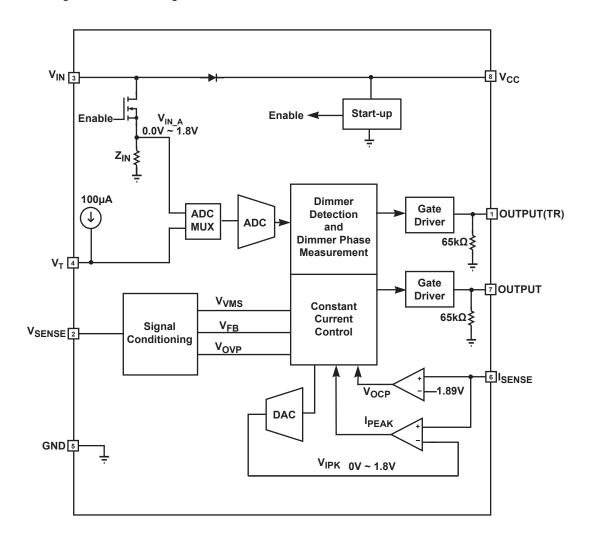

### 8.0 Functional Block Diagram

The iW3602 combines two functions: 1) wall dimmer type detection and dimmer phase measurement; and 2) output LED light dimming. It uses digital control technology, which consists of: 1) chopping circuit, which helps to increase the power factor and serves as a dynamic impedance to load the dimmer; 2) primary side controlled isolated flyback converter. The iW3602 provides a low cost dimming solution which enables LED bulb to be used with most of the common wall dimmers. This allows LED bulbs to directly replace conventional incandescent bulbs with ease. The iW3602 can detect and operate with leading-edge, and trailing-edge dimmers as well as no-dimmer. The controller operates in critical discontinuous conduction mode (CDCM) to achieve high power efficiency and minimum EMI. It incorporates proprietary primary-feedback constant current control technology to achieve tight LED current regulation.

Figure 3.1 shows a typical iW3602 application schematic. Figure 8.1 shows the functional block diagram. The advanced digital control mechanism reduces system design time and improves reliability. The start-up algorithm makes sure the  $V_{CC}$  supply voltage is ready before powering up the IC.

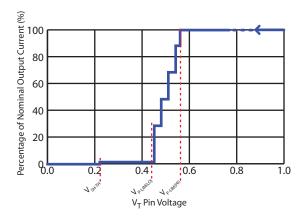

The iW3602 provides multiple protection features for current limit, over-voltage protection, and over temperature protection. The  $V_{\mathsf{T}}$  function can provide over-temperature compensation for the LED. The external NTC senses the LED temperature. If the  $V_{\mathsf{T}}$  pin voltage is below  $V_{\mathsf{P-LIM}(\mathsf{HI})}$ , the controller reduces the LED current. If the  $V_{\mathsf{T}}$  pin voltage is below  $V_{\mathsf{SH-TH}}$  then the controller turns off.

Figure 8.1: iW3602 Functional Block Diagram

#### 9.0 Theory of Operation

The iW3602 is a high performance AC/DC off-line power supply controller for dimmable LED luminaires, which uses advanced digital control technology to detect the dimmer type and dimmer phase to control the LED brightness. A PWM-dimming scheme is used to modulate the LED current with a dimming frequency of 900Hz at low dimming levels. The iW3602 can work with all types of wall dimmers including leading-edge dimmer, trailing-edge dimmer, as well as dimmer configurations such as R-type, R-C type or R-L type without visible flicker. The controller can also work when no dimmer is connected.

The iW3602 operates in quasi-resonant mode to provide high efficiency and simplify EMI design. In addition, the iW3602 includes a number of key built-in protection features. Using the state-of-the-art primary-feedback technology, the iW3602 removes the need for secondary feedback circuitry while achieving excellent line and load regulation. The iW3602 also eliminates the need for loop compensation components while maintaining stability over all operating conditions. Pulse-by-pulse waveform analysis allows for accurate LED current regulation. Hence, the iW3602 can provide high performance dimming solutions, with minimal external component count and low bill of materials cost.

#### 9.1 Pin Detail

#### Pin 1 - OUTPUT(TR)

Gate drive for the chopping circuit MOSFET switch.

#### Pin 2 - V<sub>SENSE</sub>

Sense signal input from auxiliary winding. This pin provides secondary voltage feedback used for output regulation.

#### Pin 3 - VIN

Sense signal input from the rectified line voltage.  $V_{\text{IN}}$  is used for dimmer phase detection. The input line voltage is scaled down using a resistor network. It is used for input under-voltage and over-voltage protection. This pin also provides the supply current to the IC during start-up.

#### **Pin 4 - V<sub>T</sub>**

External power limit and shutdown control. If the shutdown control is not used, this pin should be connected to GND via a resistor.

#### Pin 5 - GND

Ground.

#### Pin 6 - I<sub>SENSE</sub>

Primary current sense. Used for cycle-by-cycle peak current control.

#### Pin 7 - OUTPUT

Gate drive for the external MOSFET switch.

#### Pin 8 - V<sub>cc</sub>

Power supply for the controller during normal operation. The controller starts up when  $V_{\text{CC}}$  reaches 12V (typical) and shuts down when the  $V_{\text{CC}}$  voltage is below 7.5V (typical).

High-frequency transients and ripples can be easily generated on the  $V_{\rm CC}$  pin due to power supply switching transitions and line and load disturbances. Excess ripples and noises on  $V_{\rm CC}$  may cause the iW3602 to function undesirably, hence a decoupling capacitor must be connected between the  $V_{\rm CC}$  pin and GND. It is suggested that a ceramic capacitor of minimum 0.1uF be connected as close as possible to the  $V_{\rm CC}$  pin.

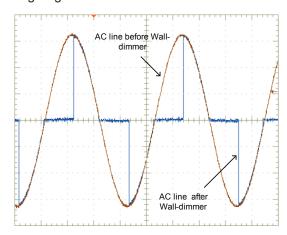

#### 9.2 Wall Dimmer Detections

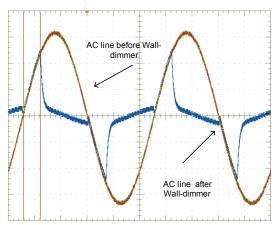

There are two types of wall dimmers: leading-edge dimmer and trailing-edge dimmer.

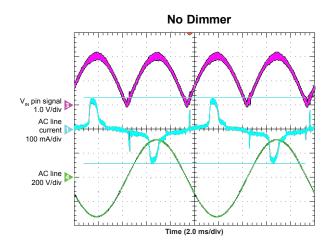

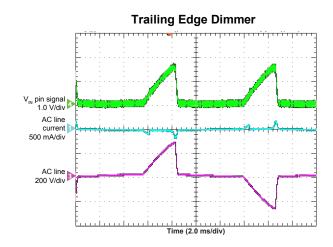

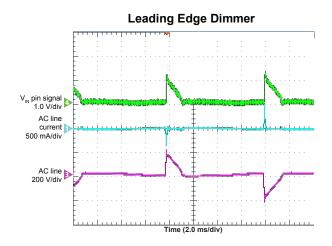

Figure 9.1 : Leading-Edge Wall Dimmer Waveforms

Figure 9.2: Trailing-Edge Wall Dimmer Waveforms

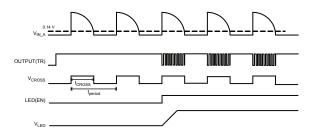

Dimmer detection, or discovery, takes place during the third cycle after start-up. The controller determines whether no dimmer exists, or if there is a leading-edge dimmer or a trailing-edge dimmer.

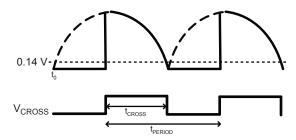

The  $V_{CROSS}$  is internally generated by comparing the digitalized  $V_{IN}$  signal to the threshold of 0.25V during dimming and 0.14V without a dimmer. The  $V_{IN}$  period ( $t_{PERIOD}$ ) is measured between two consecutive rising edge zero-crossings. The  $t_{CROSS}$  is generated by the internal digital block (refer to Figure 9.3); when  $V_{IN\_A}$  is higher than 0.14V,  $t_{CROSS}$  is set to high and when  $V_{IN\_A}$  falls below 0.14V  $t_{CROSS}$  is reset to zero. If  $t_{CROSS}$  is much shorter than the  $V_{IN}$  period then a dimmer is detected. The controller uses the filtered derivatives to decide which type of dimmer is present. A large positive derivative value indicates a leading-edge dimmer. Then the controller enters leading-edge dimmer mode; otherwise it enters trailing-edge dimmer mode.

During the dimmer detection stage, the OUTPUT(TR) keeps high to turn on the switch FET in the chopping circuit. This creates a resistive load for the wall dimmer.

Figure 9.3: Dimmer Detection

# 9.3 Dimmer Tracking and Phase Measurements

The dimmer detection algorithm and the dimmer tracking algorithm both depend on an accurate input voltage period

measurement. The  $V_{\text{IN}}$  period is measured during the second cycle of the dimmer detection process and is latched for use thereafter. Using the measured  $V_{\text{IN}}$  period in subsequent calculations rather than a constant allows for automatic 50/60Hz operation and allows for a 10% frequency variation.

The phase measurement starts when  $V_{IN}$  exceeds the rising threshold until  $V_{IN}$  falls below the falling threshold.

Figure 9.4: Dimmer Phase Measurement

The dimmer phase is calculated as:

Dimmer Phase =

$$\frac{t_{CROSS}}{t_{PERIOD}}$$

(9.1)

The calculated dimmer phase is used to generate the signal  $D_{RATIO}$ , which determines LED current. If the dimmer phase is less than 0.14 then the  $D_{RATIO}$  is clamped at 0.14; if the dimmer phase is greater than 0.7 then  $D_{RATIO}$  is clamped at 1.0; otherwise  $D_{RATIO}$  is calculated by equation 9.2.

$$D_{RATIO} = \text{Dimmer Phase} \times K_1 - K_2 \tag{9.2}$$

Where,  $K_1$  is set to 1.768 and  $K_2$  is set to 0.238.

Using  $V_{\rm Isense(NOM)}$  to represent the nominal 100% LED current, the  $V_{\rm Isense}$ , which modulates the output LED current, is controlled by:

$$V_{Isense} = V_{Isense(NOM)} \times D_{RATIO}$$

(9.3)

When  $D_{RATIO}$  is 1, the converter outputs 100% of nominal power to the LED. If  $D_{RATIO}$  is 0.01, the converter outputs 1% of nominal power to the LED.

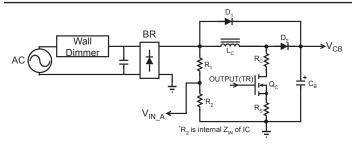

#### 9.4 Chopping Operation

Figure 9.5: Chopping Schematic

Chopping circuit provides the dynamic impedance for the dimmer and builds the energy to the LED power converter. It consists of  $L_C$ ,  $Q_C$ ,  $R_C$ ,  $R_S$ , and  $D_2$ .  $L_C$  is the chopping inductor. During the chopping period,  $L_C$  is used to store the energy when the  $Q_C$  is on, and then release the energy to  $C_B$  when  $Q_C$  is off. The on-time of  $Q_C$  during the chopping period when no dimmer exists is calculated by the following equation:

$$T_{ON(Qc)} = 4\mu s - 2.2 \frac{\mu s}{V} \times V_{IN_A}$$

(9.4)

If a dimmer exists then the on-time of  $Q_{C}$  is determined by equation 9.4. The period of  $Q_{C}$  is calculated by:

$$T_{PERIOD(Qc)} = 12.2 \mu s + 8.8 \frac{\mu s}{V} \times V_{IN\_A}$$

(9.5)

$V_{\text{IN\_A}}$  is the scale voltage of  $V_{\text{IN}}$ .  $V_{\text{CB}}$  is the voltage across  $C_{\text{B}}$ . When  $t_{\text{CROSS}}$  is low,  $Q_{\text{C}}$  is always on. When  $t_{\text{CROSS}}$  is high,  $Q_{\text{C}}$  operates according to equation 9.4 and 9.5.

During the chopping period, the average current of  $L_{\rm C}$  is in phase with the input AC line voltage, so it inherently generates a high power factor.  $D_{\rm 1}$  in the chopping circuit is used to charge  $C_{\rm B}$  when the voltage of  $C_{\rm B}$  is lower than the input line voltage. This helps to reduce the inrush current when the TRIAC is fired.

Figure 9.6: Signals of Chopping Circuit.

#### 9.5 Start-up

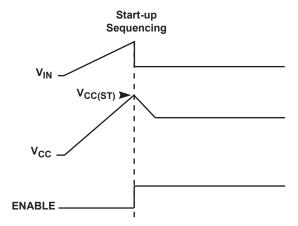

Prior to start-up the  $V_{\text{IN}}$  pin charges up the  $V_{\text{CC}}$  capacitor through a diode between  $V_{\text{IN}}$  and  $V_{\text{CC}}$ . When  $V_{\text{CC}}$  is fully charged to a voltage higher than the start-up threshold  $V_{\text{CC(ST)}}$ , the ENABLE signal becomes active and enables the control logic, shown by Figure 9.7. When the control logic is enabled, the controller enters normal operation mode. During the first 3 half AC cycles, OUTPUT(TR) keeps high. After the dimmer type and AC line period are measured, the constant current stage is enabled and the output voltage starts to ramp up. When the output voltage is above the forward voltage of the LED, the controller begins to operate in constant current mode.

An adaptive soft-start control algorithm is applied during the start-up state, where the initial output pulses are short and gradually get wider until the full pulse width is achieved. The peak current is limited cycle by cycle by the I<sub>PEAK</sub> comparator.

Figure 9.7 : Start-up Sequencing Diagram

#### 9.6 Understanding Primary Feedback

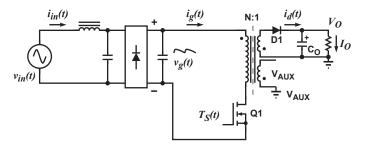

Figure 9.8 illustrates a simplified flyback converter. When the switch  $Q_1$  conducts during  $t_{ON}(t)$ , the current  $i_g(t)$  is directly drawn from rectified  $v_g(t)$ . The energy  $E_g(t)$  is stored in the magnetizing inductance  $L_M$ . The rectifying diode  $D_1$  is reversely biased and the load current  $I_0$  is supplied by the secondary capacitor  $C_0$ . When  $Q_1$  turns off,  $D_1$  conducts and the stored energy  $E_g(t)$  is delivered to the output.

Figure 9.8: Simplified Flyback Converter

In order to tightly regulate the output voltage, the information about the output voltage and load current must be accurately sensed. In the DCM flyback converter, this information can be read via the auxiliary winding or the primary magnetizing inductance ( $L_{\rm M}$ ). During the  $Q_{\rm 1}$  on-time, the load current is supplied from the output filter capacitor  $C_{\rm O}$ . The voltage across  $L_{\rm M}$  is  $v_g(t)$ , assuming the voltage dropped across  $Q_{\rm 1}$  is zero. The current in  $Q_{\rm 1}$  ramps up linearly at a rate of:

$$\frac{di_g(t)}{dt} = \frac{v_g(t)}{L_M} \tag{9.6}$$

At the end of on-time, the current ramps up to:

$$i_{g_peak}(t) = \frac{v_g(t) \times t_{ON}}{L_M}$$

(9.7)

This current represents a stored energy of:

$$E_g = \frac{L_M}{2} \times i_{g\_peak}(t)^2 \tag{9.8}$$

When  $Q_1$  turns off,  $i_g(t)$  in  $L_M$  forces a reversal of polarities on all windings. Ignoring the communication-time caused by the leakage inductance  $L_K$  at the instant of turn-off, the primary current transfers to the secondary at a peak amplitude of:

$$i_d(t) = \frac{N_P}{N_S} \times i_{g_peak}(t)$$

(9.9)

Assuming the secondary winding is master and the auxiliary winding is slave.

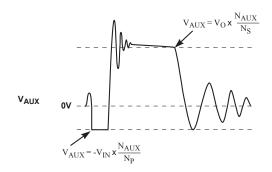

Figure 9.9: Auxiliary Voltage Waveforms

The auxiliary voltage is given by:

$$V_{AUX} = \frac{N_{AUX}}{N_S} (V_O + \Delta V) \tag{9.10}$$

and reflects the output voltage as shown in Figure 9.9.

The voltage at the load differs from the secondary voltage by a diode drop and IR losses. The diode drop is a function of current, as are IR losses. Thus, if the secondary voltage is always read at a constant secondary current, the difference between the output voltage and the secondary voltage is a fixed  $\Delta V$ . If the voltage can be read when the secondary current is small, for example, at the knee of the auxiliary waveform (see Figure 9.9), then  $\Delta V$  is also small. With the iW3602,  $\Delta V$  can be ignored.

The real-time waveform analyzer in the iW3602 reads the auxiliary waveform information cycle by cycle. The part then generates a feedback voltage  $V_{FB}$ . The  $V_{FB}$  signal precisely represents the output voltage and is used to regulate the output voltage.

#### 9.7 Valley Mode Switching

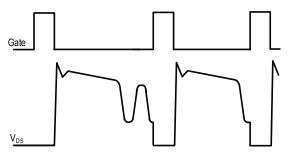

In order to reduce switching losses in the MOSFET and EMI, the iW3602 employs valley mode switching during constant output current operation. In valley mode switching, the MOSFET switch is turned on at the point where the resonant voltage across the drain and source of the MOSFET is at its lowest point (see Figure 9.10). By switching at the lowest  $V_{\text{DS}}$ , the switching loss is minimized.

Figure 9.10: Valley Mode Switching

Turning on at the lowest  $V_{DS}$  generates the lowest dV/dt, thus valley mode switching can also reduce EMI. To limit the switching frequency range, the iW3602 can skip valleys (seen the first cycle in Figure 9.10) when the switching frequency is greater than  $f_{SW(MAX)}$ .

At each of the switching cycles, the falling edge of  $V_{\text{SENSE}}$  is checked. If the falling edge of  $V_{\text{SENSE}}$  is not detected, the off-time is extended until the falling edge of  $V_{\text{SENSE}}$  is detected.

#### 9.8 LED Current Regulation

The iW3602 incorporates a patented primary-side only constant current regulation technology. The iW3602 regulates the output current at a constant level regardless of the output voltage, while avoiding a continuous conduction mode. To achieve this regulation the iW3602 senses the load current indirectly through the primary current. The primary current is detected by the  $I_{\text{SENSE}}$  pin through a resistor from the MOSFET source to ground.

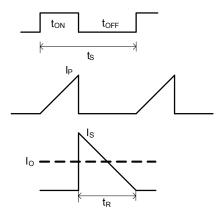

Figure 9.11: Constant LED Current Regulation

The  $I_{\text{SENSE}}$  resistor determines the maximum current output of the power supply. The output current of the power supply is determined by:

$$I_{OUT} = \frac{1}{2} \times N_{PS} \times \frac{V_{REG-TH}}{R_{SENSE}} \times \frac{t_R}{t_S}$$

(9.11)

where  $N_{PS}$  is the turns ratio of the primary and secondary windings and  $R_{SENSE}$  is the  $I_{SENSE}$  resistor.

#### 9.9 V<sub>IN</sub> Resistors

$V_{\text{IN}}$  resistors are chosen primarily to scale down the input voltage for the IC. The scale factor for the input voltage in the IC is 0.0043 for high line, and 0.0086 for low line; if the internal impedance of this pin is selected to be 2.5k $\Omega$ . Then for high line, the  $V_{\text{IN}}$  resistors should equate to:

$$R_{Vin} = \frac{2.5k\Omega}{0.0043} - 2.5k\Omega = 579k\Omega \tag{9.12}$$

#### 9.10 Voltage Protection Functions

The iW3602 includes a function that protects against an input over-voltage ( $V_{IN}$  OVP) and output over-voltage (OVP).

The input voltage is monitored by  $V_{\text{IN\_A}}$ , as shown in Figure 8.1. If this voltage exceeds 1.8 V for 15 continuous half AC cycles the iW3602 considers  $V_{\text{IN}}$  to be over-voltage. Output voltage is monitored by the  $V_{\text{SENSE}}$  pin. If the voltage at this pin exceeds  $V_{\text{SENSE}(\text{MAX})}$  for two continuous switching cycles the iW3602 considers the output voltage to be over-voltage.

In both input over-voltage and output over-voltage cases, the IC remains biased, which discharges the  $V_{CC}$  supply. In order to prevent overcharging the output voltage or overcharging the bulk voltage, the iW3602 employs an extended discharge time before restart. Initially if  $V_{CC}$  drops below the UVLO threshold, the controller resets itself and then initiates a new soft-start cycle.

Under a fault condition, the controller tries to start-up for three consecutive times. If all three start-up attempts fail, the controller enters an inactive mode, during which the controller does not respond to  $V_{\text{CC}}$  power-on requests. The controller is activated again after it sees 29 start-up attempts. The controller can also be reset to the initial condition if  $V_{\text{CC}}$  is discharged. Typically, this extended discharge time is around 3 to 5 seconds.

This extended discharge time allows the iW3602 to support hot-plug LED modules without causing dangerously high output voltages while maintaining a quick recovery.

#### 9.11 PCL, OC and SRS Protection

Peak-current limit (PCL), over-current protection (OCP) and sense-resistor short protection (SRSP) are features built-into the iW3602. With the  $I_{SENSE}$  pin the iW3602 is able to monitor the primary peak current. This allows for cycle by cycle peak current control and limit. When the primary peak current multiplied by the  $I_{SENSE}$  sense resistor is greater

than  $V_{\text{OCP}}$  over-current protection is engaged and the IC immediately turns off the gate drive until the next cycle. The output driver continues to send out switching pulses; the IC immediately turns off the gate drive if the OCP threshold is reached again.

If the  $I_{\text{SENSE}}$  sense resistor is shorted there is a potential danger of the over-current condition not being detected. Thus the IC is designed to detect this sense-resistor-short fault after the start-up, and shut down immediately. The  $V_{\text{CC}}$  is discharged since the IC remains biased. In order to prevent overcharging the output voltage, the iW3602 employs an extended discharge time before restart, similar to the discharge time described in section 9.10.

#### 9.12 Over-Temperature Protection

If an NTC thermistor is connected from the  $V_T$  pin to GND then, the iW3602 is able to detect and protect against an over temperature event (OTP).

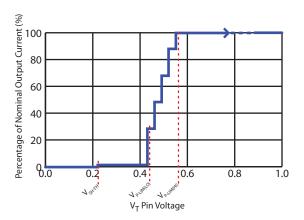

The iW3602 provides a current ( $I_{VT}$ ) to the  $V_T$  pin and detects the voltage on the pin. Based on this voltage the iW3602 can monitor the temperature on the NTC thermistor. As the  $V_T$  pin voltage reduces, the iW3602 reduces the amount of chopping and the output current according to Figure 9.12. There is a hysteresis of 84mV on  $V_T$  pin voltage for each power limiting step.

Figure 9.12 :  $V_T$  Pin Voltage vs. % of Nominal Output Current  $V_T$  from 1.0V to 0.0V

Figure 9.13 :  $V_T$  Pin Voltage vs. % of Nominal Output Current  $V_T$  from 0.0V to 1.0V

When the  $V_T$  pin voltage reaches  $V_{P\text{-}LIM(HI)}$  the output current begins to reduce as shown in Figure 9.12. At  $V_{P\text{-}LIM(LO)}$  the output current reduces to 1%. The device can be placed in shutdown mode by pulling the  $V_T$  pin to ground or below  $V_{SH\text{-}TH}$ .

#### 9.13 Thermal Design

**Note:** This section only applies to iW3602-01.

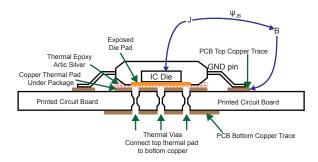

The iW3602 is typically installed inside a small enclosure, where space and air volumes are constrained. Under these circumstances  $\theta_{\text{JA}}$  (thermal resistance, junction to ambient) measurements do not provide useful information for this type of application. Instead we have provided  $\psi_{\text{JB}}$  which estimates the increase in die junction temperature relative to the PCB surface temperature. Figure 9.14 shows the PCB surface temperature is measured at the IC's GND pin pad.

Figure 9.14: Ways to Improve Thermal Resistance

Using  $\psi_{JB}$  the junction temperature (T<sub>J</sub>) of the IC can be found using the equation below.

$$T_J = T_B + P_H \cdot \Psi_{JB} \tag{9.13}$$

where,  $T_B$  is the PCB surface temperature and  $P_H$  is the power applied to the chip or the product of  $V_{CC}$  and  $I_{CCQ}$ .

Datasheet Rev. 1.2 31-May-2022

The iW3602 uses an exposed pad package to reduce the thermal resistance of the package. Although just by using an exposed package can provide some thermal resistance improvement, more significant improvements can be obtained with simple PCB layout and design. Figure 9.13 demonstrates some recommended techniques to improve thermal resistance, which are also highlighted below.

#### **Ways to Improve Thermal Resistance**

- Increase PCB area and associated amount of copper interconnect.

- Use thermal adhesive to attach the package to a thermal pad on PCB.

- Connect PCB thermal pad to additional copper on PCB using thermal vias.

| Environment                                   | Ψјв     |

|-----------------------------------------------|---------|

| No adhesive                                   | 70 °C/W |

| Use thermal adhesive to pad                   | 63 °C/W |

| Use thermal adhesive to pad with thermal vias | 49 °C/W |

Table 9.1: Improvements in  $\psi_{JB}$  Based on Limited Experimentation

**Effect of Thermal Resistance Improvements**

# 85 75 65 Ψ<sub>JB</sub> (°C/Watt) 55 45 35

A: without thermal adhesive and thermal vias B: with thermal adhesive and thermal vias

PCB Area (cm<sup>2</sup>)

15

25

Figure 9.15: Effect of Thermal Resistance Improvements

20

Figure 9.15 shows improvement of approximately 30% in

thermal resistance across different PCB sizes when the exposed pad is attached to PCB using a thermal adhesive and thermal vias connect the pad to a larger plate on the opposing side of the PCB.

#### **10.0 Performance Characteristics**

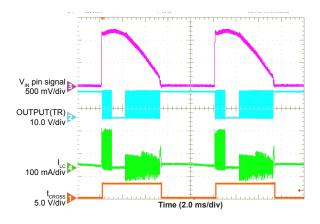

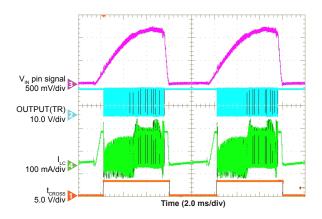

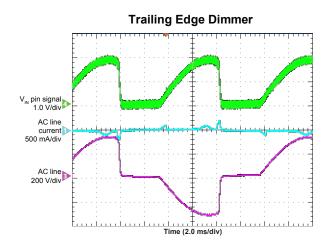

Figure 10.1 : Trailing Edge Dimmer

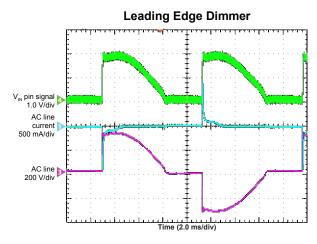

Figure 10.3 : Leading Edge Dimmer

Figure 10.5: No Dimmer

Figure 10.2 : Trailing Edge Dimmer 2

Figure 10.4 : Leading Edge Dimmer 2

# 11.0 Typical Application Schematic

Figure 11.1: iW3602 Typical Application Schematic

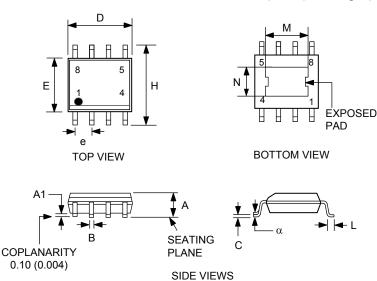

### **12.0 Physical Dimensions**

#### 8-Lead Small Outline (SOIC) Package (Exposed Pad)

| Symbol | Inc    | hes    | Millimeters |       |  |

|--------|--------|--------|-------------|-------|--|

| Syr    | MIN    | MAX    | MIN         | MAX   |  |

| Α      | 0.051  | 0.067  | 1.30        | 1.70  |  |

| A1     | 0.0020 | 0.0060 | 0.05        | 0.150 |  |

| В      | 0.014  | 0.019  | 0.36        | 0.48  |  |

| С      | 0.007  | 0.010  | 0.18        | 0.25  |  |

| D      | 0.189  | 0.197  | 4.80        | 5.00  |  |

| Е      | 0.150  | 0.157  | 3.81        | 3.99  |  |

| е      | 0.050  | ) BSC  | 1.27 BSC    |       |  |

| Н      | 0.228  | 0.244  | 5.79        | 6.20  |  |

| N      | 0.086  | 0.094  | 2.18        | 2.39  |  |

| М      | 0.118  | 0.126  | 3.00        | 3.20  |  |

| L      | 0.016  | 0.050  | 0.41        | 1.27  |  |

| α      | 0°     | 8°     |             | ·     |  |

Compliant to JEDEC Standard MS12F

Controlling dimensions are in inches; millimeter dimensions are for reference only

This product is RoHS compliant and Halide free.

Soldering Temperature Resistance:

- [a] Package is IPC/JEDEC Std 020D Moisture Sensitivity Level 3

- [b] Package exceeds JEDEC Std No. 22-A111 for Solder Immersion Resistance; package can withstand 10 s immersion < 260°C

Dimension D does not include mold flash, protrusions or gate burrs. Mold flash, protrusions or gate burrs shall not exceed 0.15 mm per end. Dimension E does not include interlead flash or protrusion. Interlead flash or protrusion shall not exceed 0.25 mm per side.

The package top may be smaller than the package bottom. Dimensions D and E are determined at the outermost extremes of the plastic body exclusive of mold flash, tie bar burrs, gate burrs and interlead flash, but including any mismatch between the top and bottom of the plastic body.

# 13.0 Ordering Information

| Part Number | Options                                                    | Package                | Description  |

|-------------|------------------------------------------------------------|------------------------|--------------|

| iW3602-01   | Optimized for 230V <sub>AC</sub> Applications <sup>2</sup> | SOIC-8-EP <sup>3</sup> | Tape & Reel¹ |

- Note 1: Tape & Reel packing quantity is 2,500/reel. Minimum ordering quantity is 2,500.

- Note 2: Refer to Section 9.4 Chopping Operation for more information.

- Note 3: For the exposed pad package, refer to Section 9.13 Thermal Design.

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

© 2022 Renesas Electronics Corporation. All rights reserved.

#### **RoHS Compliance**

Dialog Semiconductor's suppliers certify that its products are in compliance with the requirements of Directive 2011/65/EU of the European Parliament on the restriction of the use of certain hazardous substances in electrical and electronic equipment. RoHS certificates from our suppliers are available on request.

(Rev.1.0 Mar 2020)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: www.renesas.com/contact/