## RL78 FAMILY HARDWARE MANUAL GUIDE - ELECTRICAL CHARACTERISTICS EDITION

JULY 2023 RENESAS ELECTRONICS CORPORATION

# ABSOLUTE MAXIMUM RATINGS 1

| Supply voltage         | VDD<br>EVDD0, EVDD1<br>EVSS0, EVSS1 | EVDD0 = EVDD1<br>EVSS0 = EVSS1                                                                                                                                                       | -0.5 to +6.5<br>-0.5 to +6.5                                                                                                                                                                                                                                                                 | V<br>V                                                                                                                                                                                                                                                                                                                                          |

|------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REGC pin input voltage | EVsso, EVss1                        |                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                              | V                                                                                                                                                                                                                                                                                                                                               |

| REGC pin input voltage |                                     | EVss0 = EVss1                                                                                                                                                                        | 0 E to 10 2                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                 |

| REGC pin input voltage |                                     |                                                                                                                                                                                      | -0.5 to +0.3                                                                                                                                                                                                                                                                                 | V                                                                                                                                                                                                                                                                                                                                               |

|                        | VIREGC                              | REGC                                                                                                                                                                                 | -0.3 to +2.1<br>and -0.3 to V <sub>DD</sub> + 0.3 <sup>Note 1</sup>                                                                                                                                                                                                                          | V                                                                                                                                                                                                                                                                                                                                               |

| Input voltage          | VI1                                 | P00 to P07, P10 to P17, P30 to P37,<br>P40 to P47, P50 to P57, P64 to P67,<br>P70 to P77, P80 to P87, P90 to P97,<br>P100 to P106, P110 to P117, P120,<br>P125 to P127, P140 to P147 | -0.3 to EVDD0 + 0.3<br>and -0.3 to VDD + 0.3Note 2                                                                                                                                                                                                                                           | V                                                                                                                                                                                                                                                                                                                                               |

|                        | VI2                                 | P60 to P63 (N-ch open-drain)                                                                                                                                                         | -0.3 to +6.5                                                                                                                                                                                                                                                                                 | V                                                                                                                                                                                                                                                                                                                                               |

|                        | VI3                                 | P20 to P27, P121 to P124, P137,<br>P150 to P156, EXCLK, EXCLKS, RESET                                                                                                                | -0.3 to VDD + 0.3Note 2                                                                                                                                                                                                                                                                      | V                                                                                                                                                                                                                                                                                                                                               |

|                        |                                     | V12<br>V13                                                                                                                                                                           | P40 to P47, P50 to P57, P64 to P67,<br>P70 to P77, P80 to P87, P90 to P97,<br>P100 to P106, P110 to P117, P120,<br>P125 to P127, P140 to P147           Vi2         P60 to P63 (N-ch open-drain)           Vi3         P20 to P27, P121 to P124, P137,<br>P150 to P156, EXCLK, EXCLKS, RESET | P40 to P47, P50 to P57, P64 to P67,<br>P70 to P77, P80 to P87, P90 to P97,<br>P100 to P106, P110 to P117, P120,<br>P125 to P127, P140 to P147         and -0.3 to VDD + 0.3Note 2           VI2         P60 to P63 (N-ch open-drain)         -0.3 to +6.5           VI3         P20 to P27, P121 to P124, P137,         -0.3 to VDD + 0.3Note 2 |

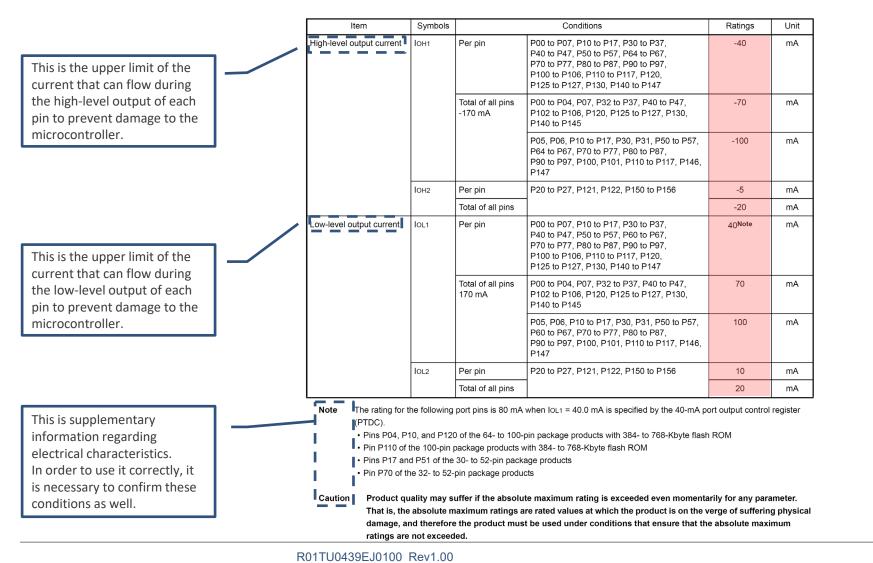

information regarding electrical characteristics. In order to use it correctly, it is necessary to confirm these conditions as well.

**Caution** Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameter. That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded.

Guaranteed values of characteristics and values that users should adhere to

Guaranteed value of characteristics

# $\textbf{ABSOLUTE MAXIMUM RATINGS} \ \textbf{(2)}$

| This is the output voltage                                                                                                                                                | _ | Item                          | Symbols                                                     | Conditions                                                                                                                                                                                                      | Ratings                                                                | Unit     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|----------|

| range for each pin that will<br>not damage the<br>microcontroller.                                                                                                        |   | Output voltage                | Vo1                                                         | P00 to P07, P10 to P17, P30 to P37,<br>P40 to P47, P50 to P57, P60 to P67,<br>P70 to P77, P80 to P87, P90 to P97,<br>P100 to P106, P110 to P117, P120,<br>P125 to P127, P130, P140 to P147                      | -0.3 to EVDD0 + 0.3<br>and -0.3 to VDD + 0.3Note 2                     | V        |

| This is the input voltage range                                                                                                                                           |   |                               | Vo2                                                         | P20 to P27, P121, P122, P150 to P156                                                                                                                                                                            | -0.3 to VDD + 0.3Note 2                                                | V        |

| for the analog pin that will not damage the microcontroller.                                                                                                              |   | Analog input voltage          | VAI1                                                        | ANI16 to ANI26                                                                                                                                                                                                  | -0.3 to EVDD0 + 0.3<br>and -0.3 to AVREFP + 0.3<br>Notes 2, 3          | V        |

|                                                                                                                                                                           |   |                               | VAI2                                                        | ANI0 to ANI14                                                                                                                                                                                                   | -0.3 to VDD + 0.3<br>and -0.3 to AVREFP + 0.3<br>Notes 2, 3            | V        |

| This is supplementary<br>information regarding<br>electrical characteristics.<br>In order to use it correctly, it<br>is necessary to confirm these<br>conditions as well. |   | Caution Product<br>That is, t | on a pin in use for<br>quality may suffe<br>he absolute max | r than 6.5 V.<br>A/D conversion must not exceed AVREFP + 0.3.<br>It if the absolute maximum rating is exceeded<br>imum ratings are rated values at which the pro<br>e product must be used under conditions tha | d even momentarily for any paran<br>oduct is on the verge of suffering | physical |

ratings are not exceeded.

Guaranteed values of characteristics and values that users should adhere to

Guaranteed value of characteristics

Explanation subject

# ABSOLUTE MAXIMUM RATINGS ③

### RENESAS

#### © 2023 Renesas Electronics Corporation. All rights reserved. Jul. 20. 2023

# ABSOLUTE MAXIMUM RATINGS (4)

| Item                | Symbols | Condition                        | S                           | Ratings     | Unit |

|---------------------|---------|----------------------------------|-----------------------------|-------------|------|

| Ambient operating   | Та      | In normal operation mode         | 3C: Industrial applications | -40 to +105 | °C   |

| temperature         |         |                                  | -40 to +85                  |             |      |

|                     |         | In flash memory programming mode | 3C: Industrial applications | -40 to +105 |      |

|                     |         |                                  | 2D: Consumer applications   | -40 to +85  |      |

| Storage temperature | Tstg    |                                  | •                           | -65 to +150 | °C   |

**Caution** Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameter. That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded.

This is supplementary information regarding electrical characteristics. In order to use it correctly, it is necessary to confirm these conditions as well.

This is the temperature range for storage without operating

the microcontroller.

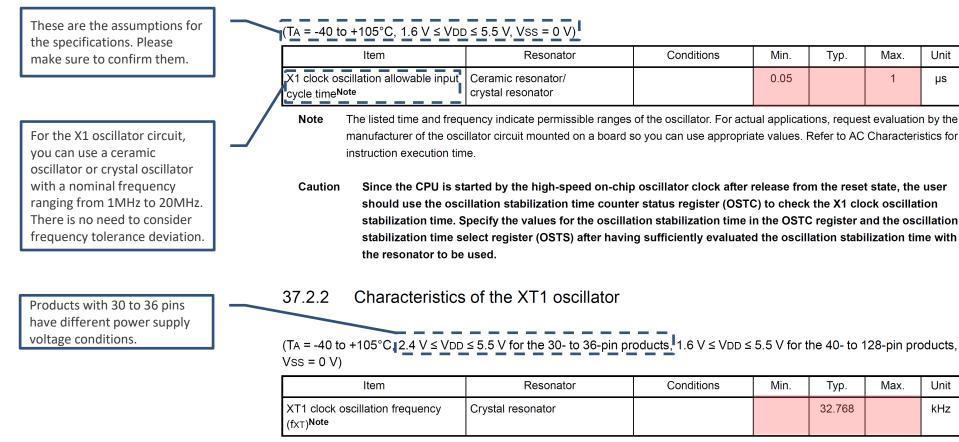

# CHARACTERISTICS OF THE OSCILLATORS

### CHARACTERISTICS OF X1 AND XT1 OSCILLATORS

37.2.1 Characteristics of the X1 oscillator

The listed time and frequency indicate permissible ranges of the oscillator. For actual applications, request evaluation by the Note manufacturer of the oscillator circuit mounted on a board so you can use appropriate values. Refer to AC Characteristics for instruction execution time.

Min.

0.05

Min.

Typ.

32.768

Max.

Unit

kHz

Typ.

Max.

Unit

μs

Guaranteed values of characteristics and values that users should adhere to Guaranteed value of characteristics

# CHARACTERISTICS OF THE OSCILLATORS

### **CHARACTERISTICS OF THE ON-CHIP OSCILLATORS**

37.2.3 Characteristics of the On-chip Oscillators

|                                                                                             | Item                                                             | Symbol        |                   | Condition         | S                                                          | Min. | Тур. | Max. | Unit       |

|---------------------------------------------------------------------------------------------|------------------------------------------------------------------|---------------|-------------------|-------------------|------------------------------------------------------------|------|------|------|------------|

|                                                                                             | High-speed on-chip<br>oscillator clock frequency                 | fін           |                   |                   |                                                            | 1    |      | 32   | MHz        |

| This is the accuracy range of                                                               | High-speed on-chip                                               |               | HIPREC = 1        | +85 to +105°C     | 1.8 V ≤ VDD ≤ 5.5 V                                        | -2.0 |      | +2.0 | %          |

| the clock frequency for the<br>high-speed on-chip oscillator.                               | oscillator clock frequency<br>accuracy <sup>Note</sup> 1         |               |                   |                   | 1.6 V ≤ VDD ≤ 5.5 V                                        | -6.0 |      | +6.0 | %          |

| The operation of the CPU and                                                                |                                                                  |               |                   | -20 to +85°C      | 1.8 V ≤ VDD ≤ 5.5 V                                        | -1.0 |      | +1.0 | %          |

| peripheral functions depends<br>on the accuracy of the<br>selected operating clock.         |                                                                  |               |                   |                   | 1.6 V ≤ VDD ≤ 5.5 V                                        | -5.0 |      | +5.0 | %          |

|                                                                                             |                                                                  |               |                   | -40 to -20°C      | $1.8 \text{ V} \leq \text{VDD} \leq 5.5 \text{ V}$         | -1.5 |      | +1.5 | %          |

|                                                                                             |                                                                  |               |                   |                   | $1.6 \text{ V} \le \text{V}_{\text{DD}} \le 5.5 \text{ V}$ | -5.5 |      | +5.5 | %          |

| By adjusting the High-Speed                                                                 |                                                                  |               | HIPREC = 0N       | lote 4            |                                                            | -15  |      | 0    | %          |

| On-Chip Oscillator Trimming<br>Register (HIOTRM), fIH can be<br>corrected. It indicates the | High-speed on-chip<br>loscillator clock correction<br>resolution |               |                   |                   |                                                            |      | 0.05 |      | %          |

| frequency accuracy that                                                                     | Note 1. The accuracy va                                          | alues were ob | tained in testing | n of this product |                                                            |      |      |      | . <u> </u> |

$(TA = -40 \text{ to } +105^{\circ}\text{C}, 1.6 \text{ V} \le \text{VDD} \le 5.5 \text{ V}, \text{Vss} = 0 \text{ V})$

- Note 1. The accuracy values were obtained in testing of this product.

- Note 2. The listed values only indicate the characteristics of the oscillators. Refer to AC Characteristics for instruction execution time.

Note 3. Guaranteed by characterization results.

**Note 4.** The listed condition applies when the setting of the FRQSEL3 bit is 1.

RENESAS

1.

changes when the setting

value of HIOTRM is varied by

## **DC CHARACTERISTICS PIN CHARACTERISTICS** ①

| This is the upper limit of the                                                                                                                         | <br>Item                                     | Symbol | Conditions                                                                                                                                                                                                      |                                                              | Min.   | Тур. | Max.             | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--------|------|------------------|------|

| current that can flow during<br>the high-level output of each<br>oin. Please limit the current<br>with external circuitry to not<br>exceed this value. | Allowable high-level<br>output currentNote 1 | IOH1   | Per pin for P00 to P07,<br>P10 to P17, P30 to P37,<br>P40 to P47, P50 to P57,<br>P64 to P67, P70 to P77,<br>P80 to P87, P90 to P97,<br>P100 to P106, P110 to P117,<br>P120, P125 to P127, P130,<br>P140 to P147 | 1.6 V ≤ EVDD0 ≤ 5.5 V                                        | WIIII. | iyp. | -10.0<br>Note 2  | mA   |

| urrent that can flow per pin.                                                                                                                          |                                              |        | Total of P00 to P04, P07,<br>P32 to P37, P40 to P47,                                                                                                                                                            | 4.0 V ≤ EVDD0 ≤ 5.5 V                                        |        |      | -55.0<br>Note 4  | mA   |

|                                                                                                                                                        |                                              | Τ      | P102 to P106, P120,<br>P125 to P127, P130,                                                                                                                                                                      | 2.7 V ≤ EVDD0 < 4.0 V                                        |        |      | -10.0            | mA   |

| This is the total upper limit of                                                                                                                       |                                              |        | P140 to P145                                                                                                                                                                                                    | 1.8 V ≤ EVDD0 < 2.7 V                                        |        |      | -5.0             | mA   |

| he current that can flow                                                                                                                               |                                              |        | (when duty ≤ 70% <b>Note 3</b> )                                                                                                                                                                                | 1.6 V ≤ EVDD0 < 1.8 V                                        |        |      | -2.5             | mA   |

| through the relevant pins.<br>'Duty ≤ 70%" indicates the<br>percentage of time during                                                                  |                                              |        | Total of P05, P06, P10 to P17,<br>P30, P31, P50 to P57, P64 to P67,                                                                                                                                             | $4.0 \text{ V} \le \text{EV}_{\text{DD0}} \le 5.5 \text{ V}$ |        |      | -80.0<br>Note 5  | mA   |

| which the current can flow.                                                                                                                            |                                              |        | P70 to P77, P80 to P87,<br>P90 to P97, P100, P101,                                                                                                                                                              | 2.7 V ≤ EVDD0 < 4.0 V                                        |        |      | -19.0            | mA   |

|                                                                                                                                                        |                                              |        | P110 to P117, P146, P147                                                                                                                                                                                        | 1.8 V ≤ EVDD0 < 2.7 V                                        |        |      | -10.0            | mA   |

|                                                                                                                                                        |                                              |        | (when duty ≤ 70% <sup>Note 3</sup> )                                                                                                                                                                            | 1.6 V ≤ EVDD0 < 1.8 V                                        |        |      | -5.0             | mA   |

|                                                                                                                                                        |                                              |        | Total of all pins<br>(when duty ≤ 70% <sup>Note 3</sup> )                                                                                                                                                       | 1.6 V ≤ EVDD0 ≤ 5.5 V                                        |        |      | -135.0<br>Note 6 | mA   |

(Notes, Caution, and Remark continue on the next page.)

haracteristics and values that sers should adhere to Guaranteed value of characteristics

# DC CHARACTERISTICS 2

|                                                             | Item                                      | Symbo       | Conditi                                                                       | ons                                   | Min.          | Тур.        | Max.           | Unit      |                                                           |

|-------------------------------------------------------------|-------------------------------------------|-------------|-------------------------------------------------------------------------------|---------------------------------------|---------------|-------------|----------------|-----------|-----------------------------------------------------------|

|                                                             | Allowable high-level output currentNote 1 | Іон2        | Per pin for P20 to P27, P121,<br>P122, P150 to P156                           | 4.0 V ≤ VDD ≤ 5.5 V                   |               |             | -3.0<br>Note 2 | mA        |                                                           |

|                                                             |                                           |             |                                                                               | 2.7 V ≤ V <sub>DD</sub> < 4.0 V       |               |             | -1.0<br>Note 2 | mA        |                                                           |

|                                                             |                                           |             |                                                                               | 1.8 V ≤ VDD < 2.7 V                   |               |             | -1.0<br>Note 2 | mA        |                                                           |

|                                                             |                                           |             |                                                                               | 1.6 V ≤ VDD < 1.8 V                   |               |             | -0.5<br>Note 2 | mA        |                                                           |

| The current value that can                                  |                                           |             | Total of all pins                                                             | 4.0 V ≤ VDD ≤ 5.5 V                   |               |             | -20.0          | mA        |                                                           |

| flow depends on the                                         |                                           |             | (when duty ≤ 70% <sup>Note 3</sup> )                                          | 2.7 V ≤ VDD < 4.0 V                   |               |             | -10.0          | mA        |                                                           |

| conditions of VDD.                                          |                                           |             |                                                                               | 1.8 V ≤ VDD < 2.7 V                   |               |             | -5.0           | mA        |                                                           |

|                                                             |                                           |             |                                                                               | 1.6 V ≤ VDD < 1.8 V                   |               |             | -5.0           | mA        |                                                           |

|                                                             | output pin.                               |             | uaranteed at the listed currents ev                                           |                                       |               |             | VDD pin t      | o an      |                                                           |

| When using with a duty > 70%                                |                                           |             | hese and other pins must also not<br>oply when the duty cycle is no grea      |                                       |               |             | ate the ou     | tput      |                                                           |

| condition, the current value that can flow becomes smaller. | current wh                                | en the dut  | y cycle is greater than 70%, where                                            | n is the duty cycle.                  |               |             |                |           |                                                           |

| The average current that can                                |                                           | •           | It from the listed pins = $(IOH \times 0.7)/$<br>: 80% and IOH = -10.0 mA     | (n × 0.01)                            |               |             |                |           |                                                           |

| flow remains unchanged.                                     |                                           | •           | It from the listed pins = $(-10.0 \times 0.7)$                                | , , , , , , , , , , , , , , , , , , , |               |             |                |           |                                                           |

|                                                             |                                           |             | cycle has no effect on the current to<br>n rating must not flow into a single |                                       | single pin.   | A current h | igher thar     | n the     |                                                           |

|                                                             |                                           |             | is -30 mA in the products for indus                                           |                                       | x3Cxx) wit    | h an ambie  | ent operat     | ing       |                                                           |

| The current value is different                              | temperatur                                | e range of  | f 85°C to 105°C.                                                              |                                       |               |             |                |           |                                                           |

| when products for industrial                                |                                           |             | is -50 mA in the products for indus<br>f 85°C to 105°C.                       | trial applications (R7F100Gx          | x3Cxx) wit    | h an ambie  | ent operat     | ing       | : Guaranteed values of                                    |

| applications are used in the                                |                                           |             | are respectively -100 mA and -60                                              | mA in the products for indust         | trial applica | tions (R7F  | 100Gxx30       | Cxx) with | characteristics and values that<br>users should adhere to |

| temperature range of -40°C to 105°C.                        | L 💻 🚽 an ambien                           | t operating | temperature range of -40°C to 85                                              | °C and of 85°C to 105°C.              |               |             |                |           | : Guaranteed value of characterist                        |

|                                                             |                                           | 02 to P04,  | ns are not capable of the output<br>P10 to P15, P17, P34, P42 to P4           |                                       | -             |             |                | , and     | Explanation subject                                       |

RENESAS

## **DC CHARACTERISTICS PIN CHARACTERISTICS** ③

|                                                                                                                                                                                           | Item                                     | Symbol | Conditions                                                                                                                                                                                                      |                                                                | Min. | Тур. | Max.               | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------|------|--------------------|------|

| This is the upper limit of the<br>current that can flow during<br>the low-level output of each<br>pin. Please limit the current<br>with external circuitry to meet<br>this specification. | Allowable low-level output currentNote 1 | IOL1   | Per pin for P00 to P07,<br>P10 to P17, P30 to P37,<br>P40 to P47, P50 to P57,<br>P64 to P67, P70 to P77,<br>P80 to P87, P90 to P97,<br>P100 to P106, P110 to P117,<br>P120, P125 to P127, P130,<br>P140 to P147 |                                                                |      |      | 20.0<br>Notes 2, 3 | mA   |

|                                                                                                                                                                                           |                                          |        | Per pin for P60 to P63                                                                                                                                                                                          |                                                                |      |      | 15.0<br>Note 2     | mA   |

| This is the upper limit of the current that can flow per pin.                                                                                                                             |                                          |        | Total of P00 to P04, P07,<br>P32 to P37, P40 to P47,                                                                                                                                                            | $4.0 \text{ V} \leq \text{EV}_{\text{DD0}} \leq 5.5 \text{ V}$ |      |      | 70.0<br>Note 5     | mA   |

|                                                                                                                                                                                           |                                          | 1      | P102 to P106, P120,<br>P125 to P127, P130,                                                                                                                                                                      | 2.7 V ≤ EVDD0 < 4.0 V                                          |      |      | 15.0               | mA   |

|                                                                                                                                                                                           |                                          |        | P140 to P145                                                                                                                                                                                                    | 1.8 V ≤ EVDD0 < 2.7 V                                          |      |      | 9.0                | mA   |

| his is the total upper limit of                                                                                                                                                           |                                          |        | (when duty ≤ 70% <sup>Note 4</sup> )                                                                                                                                                                            | 1.6 V ≤ EVDD0 < 1.8 V                                          |      |      | 4.5                | mA   |

| he current that can flow<br>hrough the relevant pins.<br>Duty ≤ 70%" indicates the                                                                                                        |                                          |        | Total of P05, P06, P10 to P17,<br>P30, P31, P50 to P57, P60 to P67,                                                                                                                                             | $4.0 \text{ V} \leq \text{EV}_{\text{DD0}} \leq 5.5 \text{ V}$ |      |      | 80.0<br>Note 5     | mA   |

| bercentage of time during                                                                                                                                                                 |                                          |        | P70 to P77, P80 to P87,<br>P90 to P97, P100, P101,                                                                                                                                                              | 2.7 V ≤ EVDD0 < 4.0 V                                          |      |      | 35.0               | mA   |

| which the current can flow.                                                                                                                                                               |                                          |        | P110 to P117, P146, P147<br>(when duty ≤ 70% <sup>Note 4</sup> )                                                                                                                                                | 1.8 V ≤ EVDD0 < 2.7 V                                          |      |      | 20.0               | mA   |

|                                                                                                                                                                                           |                                          |        |                                                                                                                                                                                                                 | 1.6 V ≤ EVDD0 < 1.8 V                                          |      |      | 10.0               | mA   |

|                                                                                                                                                                                           |                                          |        | Total of all pins<br>(when duty ≤ 70% <b>Note 4</b> )                                                                                                                                                           |                                                                |      |      | 150.0<br>Note 6    | mA   |

40 to + 400% 40 c V < 50% - 50% - 50% - 50%/**T**.

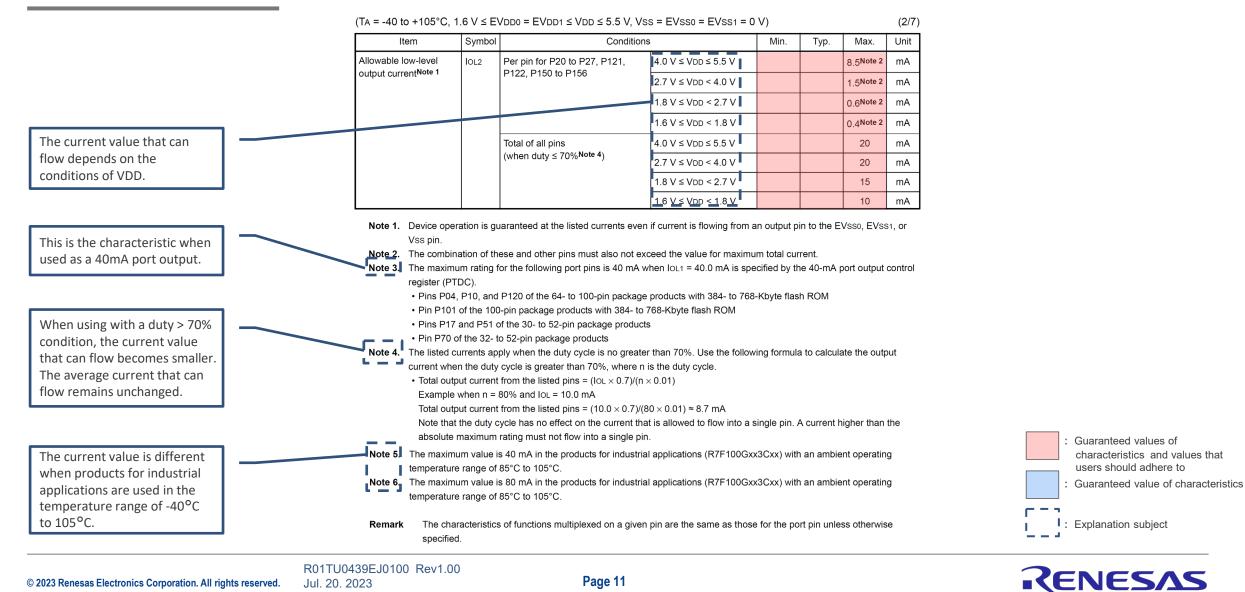

(2/7)

Guaranteed values of characteristics and values that users should adhere to

: Guaranteed value of characteristics

: Explanation subject

(Notes and Remark continue on the next page.)

## DC CHARACTERISTICS **PIN CHARACTERISTICS** (4)

## **DC CHARACTERISTICS PIN CHARACTERISTICS** (5)

| This is the weltage range in                               |               | (TA = -40 to +105°C, | 1.6 V ≤ E' | $VDD0 = EVDD1 \le VDD \le 5.5 \text{ V}, $                                                                                                                                                 | /ss = EVss0 = EVss1 =                     | 0 V)      |      |       | (3/7) |

|------------------------------------------------------------|---------------|----------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----------|------|-------|-------|

| This is the voltage range in which the read value of the   | $\overline{}$ | Item                 | Symbol     | Conditior                                                                                                                                                                                  | าร                                        | Min.      | Тур. | Max.  | Unit  |

| port register reliably becomes<br>"1".                     |               | Input voltage, high  | VIH1       | P00 to P07, P10 to P17,<br>P30 to P37, P40 to P47,<br>P50 to P57, P64 to P67,<br>P70 to P77, P80 to P87,<br>P90 to P97, P100 to P106,<br>P110 to P117, P120,<br>P125 to P127, P140 to P147 | Normal input buffer                       | 0.8 EVDD0 |      | EVDD0 | V     |

|                                                            |               |                      | VIH2       | P01, P03, P04, P10, P11,<br>P13 to P17, P43, P44,                                                                                                                                          | TTL input buffer<br>4.0 V ≤ EVDD0 ≤ 5.5 V | 2.2       |      | EVDD0 | V     |

| The characteristics change when set as a TTL input buffer. |               |                      |            | P53 to P55, P80, P81, P142,<br>P143                                                                                                                                                        | TTL input buffer<br>3.3 V ≤ EVDD0 < 4.0 V | 2.0       |      | EVDD0 | V     |

|                                                            |               |                      |            |                                                                                                                                                                                            | TTL input buffer<br>1.6 V ≤ EVDD0 < 3.3 V | 1.5       |      | EVDD0 | V     |

| P60-P63 are pins with a                                    |               |                      | Vінз       | P20 to P27, P150 to P156                                                                                                                                                                   |                                           | 0.7 Vdd   |      | Vdd   | V     |

| voltage withstand capability<br>of 6V.                     |               |                      | VIH4       | P60 to P63                                                                                                                                                                                 |                                           | 0.7 EVDD0 |      | 6.0   | V     |

|                                                            |               |                      | VIH5       | P121 to P124, P137, EXCLK, EX                                                                                                                                                              | , P137, EXCLK, EXCLKS, RESET              |           |      | Vdd   | V     |

The maximum value of VIH of pins P00, P02 to P04, P10 to P15, P17, P34, P42 to P45, P50, P52 to P55, P71, P72, Caution P74, P80 to P83, P96, P120, and P142 to P144 is EVDD0, even in the N-ch open-drain mode.

Guaranteed values of characteristics and values that users should adhere to : Guaranteed value of characteristics

# DC CHARACTERISTICS 6

|                                                                       | (1A = -40  to) | $+105^{\circ}C, 1.6 V \le E$ | $VDD0 = EVDD1 \le VDD \le 5.5 V,$                                                                                                                                                          | VSS = EVSS0 = EVSS1 =                     | U V) |      |           | (3/7 |

|-----------------------------------------------------------------------|----------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|------|------|-----------|------|

| This is the voltage range in                                          | Iter           | m Symbol                     | Conditio                                                                                                                                                                                   | ons                                       | Min. | Тур. | Max.      | Unit |

| which the read value of the<br>port register reliably becomes<br>"0". | Input voltage  | a, low VIL1                  | P00 to P07, P10 to P17,<br>P30 to P37, P40 to P47,<br>P50 to P57, P64 to P67,<br>P70 to P77, P80 to P87,<br>P90 to P97, P100 to P106,<br>P110 to P117, P120,<br>P125 to P127, P140 to P147 | Normal input buffer                       | 0    |      | 0.2 EVDD0 | V    |

| The characteristics change<br>when set as a TTL input buffer.         | _              | VIL2                         | VIL2 P01, P03, P04, P10, P11,<br>P13 to P17, P43, P44,<br>P53 to P55, P80, P81, P142,<br>P143                                                                                              | TTL input buffer<br>4.0 V ≤ EVDD0 ≤ 5.5 V | 0    |      | 0.8       | V    |

|                                                                       |                |                              |                                                                                                                                                                                            | TTL input buffer<br>3.3 V ≤ EVDD0 < 4.0 V | 0    |      | 0.5       | V    |

|                                                                       |                |                              |                                                                                                                                                                                            | TTL input buffer<br>1.6 V ≤ EVDD0 < 3.3 V | 0    |      | 0.32      | V    |

|                                                                       |                | VIL3                         | P20 to P27, P150 to P156                                                                                                                                                                   |                                           | 0    |      | 0.3 VDD   | V    |

|                                                                       |                | VIL4                         | P60 to P63                                                                                                                                                                                 |                                           | 0    |      | 0.3 EVDD0 | V    |

|                                                                       |                | VIL5                         | P121 to P124, P137, EXCLK, E                                                                                                                                                               | XCLKS, RESET                              | 0    |      | 0.2 Vdd   | V    |

(TA = -40 to +105°C, 1.6 V ≤ EVDD0 = EVDD1 ≤ VDD ≤ 5.5 V, Vss = EVss0 = EVss1 = 0 V)

(3/7)

Guaranteed values of characteristics and values that users should adhere to

Guaranteed value of characteristics

RENESAS

## **DC CHARACTERISTICS PIN CHARACTERISTICS (7)**

| This is the voltage value                                                                     |  | Item                                                       | Symbol                                   | Conditi                                                                         | ions                                                                            | Min.           | Тур. | Max. | Unit |

|-----------------------------------------------------------------------------------------------|--|------------------------------------------------------------|------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------|----------------|------|------|------|

| output from the pin during<br>high-level output. The voltage<br>value varies depending on the |  | Output voltage, high                                       | Vон1                                     | P00 to P07, P10 to P17,<br>P30 to P37, P40 to P47,                              | 4.0 V ≤ EVDD0 ≤ 5.5 V,<br>IOH1 = -10.0 mA                                       | EVDD0<br>- 1.5 |      |      | V    |

| conditions of IOH.                                                                            |  |                                                            |                                          | P50 to P57, P64 to P67,<br>P70 to P77, P80 to P87,<br>P90 to P97, P100 to P106, | $4.0 \text{ V} \le \text{EV}_{\text{DD0}} \le 5.5 \text{ V},$<br>IOH1 = -3.0 mA | EVDD0<br>- 0.7 |      |      | V    |

|                                                                                               |  | P110 to P117, P120,<br>P125 to P127, P130,<br>P140 to P147 | 2.7 V ≤ EVDD0 ≤ 5.5 V,<br>Іон1 = -2.0 mA | EVDD0<br>- 0.6                                                                  |                                                                                 |                | V    |      |      |

|                                                                                               |  |                                                            |                                          | 1.8 V ≤ EVDD0 ≤ 5.5 V,<br>Іон1 = -1.5 mA                                        | EVDD0<br>- 0.5                                                                  |                |      | V    |      |

|                                                                                               |  |                                                            |                                          | 1.6 V ≤ EVDD0 < 5.5 V,<br>Іон1 = -1.0 mA                                        | EVDD0<br>- 0.5                                                                  |                |      | V    |      |

|                                                                                               |  |                                                            | Vон2                                     | P20 to P27, P121, P122,<br>P150 to P156                                         | 4.0 V ≤ VDD ≤ 5.5 V,<br>IOH2 = -3.0 mA                                          | Vdd<br>- 0.7   |      |      | V    |

|                                                                                               |  |                                                            |                                          | 2.7 V ≤ V <sub>DD</sub> < 4.0 V,<br>IOH2 = -1.0 mA                              | Vdd<br>- 0.5                                                                    |                |      | V    |      |

|                                                                                               |  |                                                            |                                          |                                                                                 | 1.8 V ≤ VDD < 2.7 V,<br>Іон2 = -1.0 mA                                          | Vdd<br>- 0.5   |      |      | V    |

|                                                                                               |  |                                                            |                                          |                                                                                 | $1.6 \text{ V} \le \text{V}_{\text{DD}} < 1.8 \text{ V},$<br>IOH2 = -0.5 mA     | VDD<br>- 0.5   |      |      | V    |

Guaranteed values of characteristics and values that users should adhere to : Guaranteed value of characteristics

Caution P00, P02 to P04, P10 to P15, P17, P34, P42 to P45, P50, P52 to P55, P71, P72, P74, P80 to P83, P96, P120, and P142 to P144 do not output high-level signals in the N-ch open-drain mode.

# DC CHARACTERISTICS ®

$(T_A = -40 \text{ to } +105^{\circ}\text{C}, 1.6 \text{ V} \le \text{EVDD0} = \text{EVDD1} \le \text{VDD} \le 5.5 \text{ V}, \text{Vss} = \text{EVss0} = \text{EVss1} = 0 \text{ V})$

|                                                         |     | Item                     | Symbol       |                                                      | Conditions                                                            |                               | Min. | Тур. | Max. | Unit |

|---------------------------------------------------------|-----|--------------------------|--------------|------------------------------------------------------|-----------------------------------------------------------------------|-------------------------------|------|------|------|------|

| This is the veltage value                               |     | Output voltage, low      | Vol1         | P00 to P07, P10 to P17,                              | $4.0 \text{ V} \le \text{EV}_{\text{DD0}} \le 5.5 \text{ V}$          | IOL1 = 20.0 mA                |      |      | 1.3  | V    |

| This is the voltage value<br>output from the pin during |     |                          |              | P30 to P37, P40 to P47,<br>P50 to P57, P64 to P67,   |                                                                       | IOL1 = 40.0 mANote            |      |      | 1.3  | V    |

| low-level output. The voltage                           |     |                          |              | P70 to P77, P80 to P87,<br>P90 to P97, P100 to P106, | 4.0 V ≤ EVDD0 ≤ 5.5 V                                                 | IOL1 = 8.5 mA                 |      |      | 0.7  | V    |

| value varies depending on the                           |     |                          |              | P110 to P117, P120,<br>P125 to P127, P130,           |                                                                       | IOL1 = 17.0 mANote            |      |      | 0.7  | V    |

| conditions of IOL.                                      |     |                          |              | P140 to P147                                         | 2.7 V ≤ EVDD0 ≤ 5.5 V                                                 | IOL1 = 3.0 mA                 |      |      | 0.6  | V    |

| -                                                       |     |                          |              |                                                      |                                                                       | IOL1 = 6.0 mA <sup>Note</sup> |      |      | 0.6  | V    |

|                                                         |     |                          |              |                                                      | 2.7 V ≤ EVDD0 ≤ 5.5 V                                                 | IOL1 = 1.5 mA                 |      |      | 0.4  | V    |

|                                                         |     |                          |              |                                                      |                                                                       | IOL1 = 3.0 mA <sup>Note</sup> |      |      | 0.4  | V    |

|                                                         |     |                          |              |                                                      | 1.8 V ≤ EVDD0 ≤ 5.5 V                                                 | IOL1 = 0.6 mA                 |      |      | 0.4  | V    |

|                                                         |     |                          |              |                                                      |                                                                       | IOL1 = 1.2 mA <sup>Note</sup> |      |      | 0.4  | V    |

|                                                         |     |                          |              |                                                      | 1.6 V ≤ EVDD0 ≤ 5.5 V                                                 | IOL1 = 0.3 mA                 |      |      | 0.4  | V    |

|                                                         |     |                          |              |                                                      |                                                                       | IOL1 = 0.6 mA <sup>Note</sup> |      |      | 0.4  | V    |

|                                                         |     |                          | Vol2         | P20 to P27, P121, P122,                              | 4.0 V ≤ VDD ≤ 5.5 V, IOL                                              | 2 = 8.5 mA                    |      |      | 0.7  | V    |

|                                                         |     |                          |              | P150 to P156                                         | 2.7 V ≤ VDD < 4.0 V, IOL2 = 1.5 mA                                    |                               |      |      | 0.5  | V    |

|                                                         |     |                          |              |                                                      | 1.8 V ≤ VDD < 2.7 V, IOL                                              | 2 <b>= 0.6 mA</b>             |      |      | 0.4  | V    |

|                                                         |     |                          |              |                                                      | $1.6 \text{ V} \le \text{V}_{\text{DD}} < 1.8 \text{ V}, \text{ IOL}$ | 2 = 0.4 mA                    |      |      | 0.4  | V    |

|                                                         |     |                          | Vol3         |                                                      | 4.0 V ≤ EVDD0 ≤ 5.5 V, I                                              | ol3 = 15.0 mA                 |      |      | 2.0  | V    |

|                                                         |     |                          |              |                                                      | 4.0 V ≤ EVDD0 ≤ 5.5 V, I                                              | ol3 = 5.0 mA                  |      |      | 0.4  | V    |

|                                                         |     |                          |              |                                                      | 2.7 V ≤ EVDD0 ≤ 5.5 V, I                                              | OL3 = 3.0 mA                  |      |      | 0.4  | V    |

|                                                         |     |                          |              |                                                      | 1.8 V ≤ EVDD0 ≤ 5.5 V, I                                              | OL3 = 2.0 mA                  |      |      | 0.4  | V    |

|                                                         | 1.6 | 1.6 V ≤ EVDD0 ≤ 5.5 V, I | OL3 = 1.0 mA |                                                      |                                                                       | 0.4                           | V    |      |      |      |

Note The listed value applies when IoL1 = 40.0 mA is specified for the following port pins by the 40-mA port output control register (PTDC).

• Pins P04, P10, and P120 of the 64- to 100-pin package products with 384- to 768-Kbyte flash ROM

Pin P101 of the 100-pin package products with 384- to 768-Kbyte flash ROM

Pins P17 and P51 of the 30- to 52-pin package products

Pin P70 of the 32- to 52-pin products

: Guaranteed values of characteristics and values that users should adhere to

: Guaranteed value of characteristics

(5/7)

# DC CHARACTERISTICS (9)

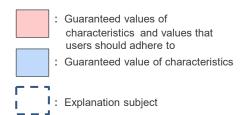

This is the value of the current that can flow when the output current control function is enabled. If an external resistance is connected, the current is limited by the limiting resistor.

|   | (TA = -40 to +105°C, 1         | .6 V ≤ EV0 | $DD0 = EVDD1 \le VDD \le$ | ≦ 5.5 V, Vss = I | EVsso = EVss1 = 0 V)                                     |      |      |      | (6/7) |

|---|--------------------------------|------------|---------------------------|------------------|----------------------------------------------------------|------|------|------|-------|

| [ | Item                           | Symbol     |                           | Conditions       |                                                          | Min. | Тур. | Max. | Unit  |

|   | Output current <sup>Note</sup> | CCDIOL     | P16, P17, P50, P51        | CCSm = 01H       | $4.0 \text{ V} \leq \text{EV}$ DD $0 \leq 5.5 \text{ V}$ | 1.0  | 1.8  | 2.6  | mA    |

|   |                                |            | P60 to P63                |                  | 2.7 V ≤ EVDD0 < 4.0 V                                    | 0.8  | 1.5  | 2.3  | mA    |

|   |                                |            |                           | CCSm = 02H       | $4.0 \text{ V} \leq \text{EVDD0} \leq 5.5 \text{ V}$     | 3.0  | 4.9  | 6.5  | mA    |

|   |                                |            |                           |                  | 3.0 V ≤ EVDD0 < 4.0 V                                    | 2.7  | 4.3  | 5.9  | mA    |

|   |                                |            |                           | CCSm = 03H       | $4.0 \text{ V} \leq \text{EVDD0} \leq 5.5 \text{ V}$     | 6.6  | 10.0 | 13.2 | mA    |

|   |                                |            |                           |                  | 3.3 V ≤ EVDD0 < 4.0 V                                    | 6.0  | 9.1  | 12.1 | mA    |

|   |                                |            | P60 to P63                | CCSm = 04H       | $4.0 \text{ V} \leq \text{EVDD0} \leq 5.5 \text{ V}$     | 10.2 | 15.0 | 19.8 | mA    |

|   |                                |            |                           |                  | 3.3 V ≤ EVDD0 < 4.0 V                                    | 9.4  | 13.8 | 18.2 | mA    |

Note The listed currents apply when the output current control function is enabled.

# DC CHARACTERISTICS

## **DC CHARACTERISTICS SUPPLY CURRENT CHARACTERISTICS** ①

| This is the total current flowing through VDD and     | $\overline{}$ |                      |                |              | products with 96- to $EVDD0 \le VDD \le 5.5$ V | /, Vss = EVsso = 0 V) |           |             |      |      |      | (1/4) | )                                                            |

|-------------------------------------------------------|---------------|----------------------|----------------|--------------|------------------------------------------------|-----------------------|-----------|-------------|------|------|------|-------|--------------------------------------------------------------|

| EVDD.                                                 |               | Item                 | Symbol         |              |                                                | Conditions            |           |             | Min. | Тур. | Max. | Unit  |                                                              |

|                                                       |               | Supply               | IDD1           | Operating    |                                                | fiH = 32 MHzNote 2    | Basic     | VDD = 5.0 V |      | 1.3  | —    | mA    |                                                              |

|                                                       |               | Current              |                | mode         | (high-speed main)<br>mode                      |                       | operation | VDD = 1.8 V |      | 1.3  | _    |       |                                                              |

|                                                       |               |                      |                |              | 1                                              |                       | Normal    | VDD = 5.0 V |      | 3.0  | 5.0  | mA    |                                                              |

|                                                       |               | ſ                    |                |              |                                                |                       | operation | VDD = 1.8 V |      | 3.0  | 5.0  |       |                                                              |

| he operating mode indicates he CPU's operating state. |               |                      |                |              | 18                                             | fiH = 24 MHzNote 2    | Normal    | VDD = 5.0 V |      | 2.3  | 3.8  | mA    |                                                              |

|                                                       |               |                      |                |              | (low-speed main)<br>mode                       |                       | operation | VDD = 1.8 V |      | 2.3  | 3.8  |       |                                                              |

|                                                       |               |                      |                |              |                                                | fiH = 16 MHzNote 2    | Normal    | VDD = 5.0 V |      | 1.7  | 2.7  | mA    |                                                              |

| The value of the current                              | $\checkmark$  |                      |                |              | i :                                            |                       | operation | VDD = 1.8 V |      | 1.7  | 2.7  |       |                                                              |

| flowing through the CPU                               |               |                      |                |              | 1 i                                            | fIM = 4 MHzNote 3     | Normal    | VDD = 5.0 V |      | 0.4  | 0.7  | mA    |                                                              |

| varies depending on its processing.                   |               |                      |                |              | 1 1                                            |                       | operation | VDD = 1.6 V |      | 0.4  | 0.7  |       |                                                              |

| processing.                                           |               |                      |                |              | LP                                             | fim = 2 MHzNote 3     | Normal    | VDD = 5.0 V |      | 200  | 325  | μA    |                                                              |

|                                                       |               |                      |                |              | (low-power main)<br>mode                       |                       | operation | VDD = 1.6 V |      | 200  | 325  |       |                                                              |

| The current value flowing                             |               |                      |                |              |                                                | fim = 1 MHzNote 3     | Normal    | VDD = 5.0 V |      | 112  | 178  | μA    |                                                              |

| through depends on the flash                          |               |                      |                |              |                                                |                       | operation | VDD = 1.6 V |      | 111  | 176  |       | : Guaranteed values of characteristics and values that       |

| operating mode.                                       |               |                      |                |              | HS                                             | fMX = 20 MHzNote 4,   | Normal    | VDD = 5.0 V |      | 1.9  | 3.2  | mA    | users should adhere to<br>: Guaranteed value of characterist |

|                                                       |               |                      |                |              | (high-speed main)<br>mode                      | Square wave input     | operation | VDD = 1.8 V |      | 1.9  | 3.2  |       |                                                              |

|                                                       |               | (Rema                | Irks are liste | ed on the ne |                                                |                       |           |             |      |      |      |       | L I: Explanation subject                                     |

| 2023 Renesas Electronics Corporation. All righ        | nts reserved. | R01TU0<br>Jul. 20. 3 | 439EJ010       | ) Rev1.00    |                                                | Page 18               |           |             |      |      |      |       | RENESAS                                                      |

## **DC CHARACTERISTICS** SUPPLY CURRENT CHARACTERISTICS 2

|                                                              | (TA = -40         | ) to +105°(  | C, 1.6 V ≤ E                 | EVDD0 ≤ VDD ≤ 5.5 '      | V, Vss = EVsso = 0 V)                                  |                      |                  |            |           |           | (1/4)    |                                                           |

|--------------------------------------------------------------|-------------------|--------------|------------------------------|--------------------------|--------------------------------------------------------|----------------------|------------------|------------|-----------|-----------|----------|-----------------------------------------------------------|

|                                                              | Item              | Symbol       |                              |                          | Conditions                                             |                      |                  | Min.       | Тур.      | Max.      | Unit     |                                                           |

|                                                              | Supply            | IDD1         | Operating                    |                          | f <sub>MX</sub> = 20 MHz <sup>Note 4</sup> ,           | Normal               | VDD = 5.0 V      |            | 1.8       | 3.0       | mA       |                                                           |

|                                                              | current<br>Note 1 |              | mode                         | (low-speed main)<br>mode | Square wave input                                      | operation            | VDD = 1.8 V      |            | 1.7       | 3.0       |          |                                                           |

|                                                              |                   |              |                              |                          | fMX = 20 MHzNote 4,                                    | Normal               | VDD = 5.0 V      |            | 1.9       | 3.2       | mA       |                                                           |

|                                                              |                   |              |                              |                          | Resonator connection                                   | operation            | VDD = 1.8 V      |            | 1.9       | 3.2       |          |                                                           |

| The value of the current                                     |                   | Τ            |                              |                          | fMX = 10 MHzNote 4,                                    | Normal               | VDD = 5.0 V      |            | 0.9       | 1.6       | mA       |                                                           |

| flowing varies depending on                                  |                   |              |                              |                          | Square wave input                                      | operation            | VDD = 1.8 V      |            | 0.9       | 1.6       |          |                                                           |

| the CPU clock used.                                          |                   |              |                              |                          | fmx = 10 MHzNote 4,                                    | Normal               | VDD = 5.0 V      |            | 1.0       | 1.7       | mA       |                                                           |

|                                                              |                   |              |                              |                          | Resonator connection                                   | operation            | VDD = 1.8 V      |            | 1.0       | 1.7       |          |                                                           |

|                                                              |                   |              |                              |                          | fMX = 8 MHzNote 4,                                     | Normal               | VDD = 5.0 V      |            | 0.8       | 1.3       | mA       |                                                           |

|                                                              |                   |              |                              |                          | Square wave input                                      | operation            | VDD = 1.8 V      |            | 0.7       | 1.3       |          |                                                           |

|                                                              |                   |              |                              |                          | f <sub>MX</sub> = 8 MHzNote 4,                         | Normal               | VDD = 5.0 V      |            | 0.9       | 1.4       | mA       |                                                           |

| These are the specified                                      |                   |              |                              |                          | Resonator connection                                   | operation            | VDD = 1.8 V      |            | 0.8       | 1.4       |          |                                                           |

| conditions for the power supply current.                     | Note 1            | I. The liste | d currents a                 | re the total currents fl | owing into VDD and EVD                                 | oo, <b>including</b> | the input leaka  | age curr   | ents flov | ving whe  | en the   |                                                           |

|                                                              | 1                 |              |                              |                          | o or Vss, EVsso. The cur                               |                      |                  |            |           |           |          |                                                           |