# RZ/G3S SMARC Module Board

User's Manual: Hardware

Renesas Microprocessor RZ Family / RZ/G Series

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

#### **Notice**

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information.

- 2. Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You shall be responsible for determining what licenses are required from any third parties, and obtaining such licenses for the lawful import, export, manufacture, sales, utilization, distribution or other disposal of any products incorporating Renesas Electronics products, if required.

- 5. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- 6. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 7. No semiconductor product is absolutely secure. Notwithstanding any security measures or features that may be implemented in Renesas Electronics hardware or software products, Renesas Electronics shall have absolutely no liability arising out of any vulnerability or security breach, including but not limited to any unauthorized access to or use of a Renesas Electronics product or a system that uses a Renesas Electronics product. RENESAS ELECTRONICS DOES NOT WARRANT OR GUARANTEE THAT RENESAS ELECTRONICS PRODUCTS, OR ANY SYSTEMS CREATED USING RENESAS ELECTRONICS PRODUCTS WILL BE INVULNERABLE OR FREE FROM CORRUPTION, ATTACK, VIRUSES, INTERFERENCE, HACKING, DATA LOSS OR THEFT, OR OTHER SECURITY INTRUSION ("Vulnerability Issues"). RENESAS ELECTRONICS DISCLAIMS ANY AND ALL RESPONSIBILITY OR LIABILITY ARISING FROM OR RELATED TO ANY VULNERABILITY ISSUES. FURTHERMORE, TO THE EXTENT PERMITTED BY APPLICABLE LAW, RENESAS ELECTRONICS DISCLAIMS ANY AND ALL WARRANTIES, EXPRESS OR IMPLIED, WITH RESPECT TO THIS DOCUMENT AND ANY RELATED OR ACCOMPANYING SOFTWARE OR HARDWARE, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY, OR FITNESS FOR A PARTICULAR PURPOSE.

- 8. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions.

- 12. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 13. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 14. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

- (Note1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries.

- (Note2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Rev.5.0-1 October 2020)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan

www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit:

#### Renesas RZ SMARC CARRIER II Disclaimer

By using this RZ SMARC CARRIER II, the User accepts the following terms, which are in addition to, and control in the event of disagreement, with Renesas' General Terms and Conditions available at <a href="https://www.renesas.com/en-us/legal/disclaimer.html">https://www.renesas.com/en-us/legal/disclaimer.html</a>

The RZ SMARC CARRIER II is not guaranteed to be error free, and the entire risk as to the results and performance of the RZ SMARC CARRIER II is assumed by the User. The RZ SMARC CARRIER II is provided by Renesas on an "as is" basis without warranty of any kind whether express or implied, including but not limited to the implied warranties of good workmanship, fitness for a particular purpose, title, merchantability, and non-infringement of intellectual property rights. Renesas expressly disclaims any implied warranty.

Renesas does not consider the RZ SMARC CARRIER II to be a finished product and therefore the RZ SMARC CARRIER II may not comply with some requirements applicable to finished products, including, but not limited to recycling, restricted substances and electromagnetic compatibility regulations. Refer to Certifications section, for information about certifications and compliance information for the RZ SMARC CARRIER II. It is the kit User's responsibility to make sure the kit meets any local requirements applicable to their region.

Renesas or its affiliates shall in no event be liable for any loss of profit, loss of data, loss of contract, loss of business, damage to reputation or goodwill, any economic loss, any reprogramming or recall costs (whether the foregoing losses are direct or indirect) nor shall Renesas or its affiliates be liable for any other direct or indirect special, incidental or consequential damages arising out of or in relation to the use of this RZ SMARC CARRIER II, even if Renesas or its affiliates have been advised of the possibility of such damages.

Renesas has used reasonable care in preparing the information included in this document, but Renesas does not warrant that such information is error free nor does Renesas guarantee an exact match for every application or parameter to part numbers designated by other vendors listed herein. The information provided in this document is intended solely to enable the use of Renesas products. No express or implied license to any intellectual property right is granted by this document or in connection with the sale of Renesas products. Renesas reserves the right to make changes to specifications and product descriptions at any time without notice. Renesas assumes no liability for any damages incurred by you resulting from errors in or omissions from the information included herein. Renesas cannot verify, and assumes no liability for, the accuracy of information available on another company's website.

#### **Precautions**

This Evaluation Kit is only intended for use in a laboratory environment under ambient temperature and humidity conditions. A safe separation distance should be used between this and any sensitive equipment. Its use outside the laboratory, classroom, study area, or similar such area invalidates conformity with the protection requirements of the Electromagnetic Compatibility Directive and could lead to prosecution.

The product generates, uses, and can radiate radio frequency energy and may cause harmful interference to radio communications. There is no guarantee that interference will not occur in a particular installation. If this equipment causes harmful interference to radio or television reception, which can be determined by turning the equipment off or on, you are encouraged to try to correct the interference by one or more of the following measures:

- · Ensure attached cables do not lie across the equipment.

- · Reorient the receiving antenna.

- · Increase the distance between the equipment and the receiver.

- · Connect the equipment into an outlet on a circuit different from that which the receiver is connected.

- $\cdot\,$  Power down the equipment when not in use.

- · Consult the dealer or an experienced radio/TV technician for help.

Note: It is recommended that wherever possible shielded interface cables are used.

The product is potentially susceptible to certain EMC phenomena. To mitigate against them it is recommended that the following measures be undertaken:

- · The user is advised that mobile phones should not be used within 10 m of the product when in use.

- $\cdot\,$  The user is advised to take ESD precautions when handling the equipment.

The Evaluation Kit does not represent an ideal reference design for an end product and does not fulfill the regulatory standards for an end product.

# **General Precautions in the Handling of Microprocessing Unit and Microcontroller Unit Products**

The following usage notes are applicable to all Microprocessing unit and Microcontroller unit products from Renesas. For detailed usage notes on the products covered by this document, refer to the relevant sections of the document as well as any technical updates that have been issued for the products.

- 1. Precaution against Electrostatic Discharge (ESD)

- A strong electrical field, when exposed to a CMOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop the generation of static electricity as much as possible, and quickly dissipate it when it occurs. Environmental control must be adequate. When it is dry, a humidifier should be used. This is recommended to avoid using insulators that can easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors must be grounded. The operator must also be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions must be taken for printed circuit boards with mounted semiconductor devices.

- Processing at power-on

- The state of the product is undefined at the time when power is supplied. The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the time when power is supplied. In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the time when power is supplied until the reset process is completed. In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the time when power is supplied until the power reaches the level at which resetting is specified.

- 3. Input of signal during power-off state

- Do not input signals or an I/O pull-up power supply while the device is powered off. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Follow the guideline for input signal during power-off state as described in your product documentation.

- 4. Handling of unused pins

- Handle unused pins in accordance with the directions given under handling of unused pins in the manual. The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of the LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible

- 5. Clock signals

- After applying a reset, only release the reset line after the operating clock signal becomes stable. When switching the clock signal during program execution, wait until the target clock signal is stabilized. When the clock signal is generated with an external resonator or from an external oscillator during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Additionally, when switching to a clock signal produced with an external resonator or by an external oscillator while program execution is in progress, wait until the target clock signal is stable.

- 6. Voltage application waveform at input pin

- Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between  $V_{IL}$  (Max.) and  $V_{IH}$  (Min.) due to noise, for example, the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between  $V_{IL}$  (Max.) and  $V_{IH}$  (Min.).

- 7. Prohibition of access to reserved addresses

- Access to reserved addresses is prohibited. The reserved addresses are provided for possible future expansion of functions. Do not access these addresses as the correct operation of the LSI is not guaranteed.

- 8. Differences between products

- Before changing from one product to another, for example to a product with a different part number, confirm that the change will not lead to problems. The characteristics of a microprocessing unit or microcontroller unit products in the same group but having a different part number might differ in terms of internal memory capacity, layout pattern, and other factors, which can affect the ranges of electrical characteristics, such as characteristic values, operating margins, immunity to noise, and amount of radiated noise. When changing to a product with a different part number, implement a system-evaluation test for the given product.

## **Table of Contents**

| 1. | Intro  | ducti  | on                          | 7  |

|----|--------|--------|-----------------------------|----|

|    | 1.1    | Kit C  | ontents                     | 9  |

|    | 1.2    | Modu   | ıle Assembly                | 10 |

| 2. | Svst   | em D   | Description                 | 11 |

|    | 2.1    |        | SMARC EVK Functional Block  |    |

|    | 2.2    |        | SMARC EVK Interface Mapping |    |

|    | 2.3    |        | d Configuration and Status  |    |

|    |        | 3.1    | SW_CONFIG                   |    |

|    | 2.     | 3.2    | _<br>GPIO4_SEL              |    |

|    | 2.4    | List c | of Pin Functions            | 18 |

|    | 2.     | 4.1    | LED Indicators              | 18 |

|    | 2.5    | Reco   | mmended Operating Condition | 18 |

| 3. | Fund   | ctiona | al Specifications           | 19 |

|    | 3.1    | Proce  | essor                       | 19 |

|    | 3.2    | Powe   | er Supply                   | 20 |

|    | 3.3    | Clock  | <b>(</b>                    | 21 |

|    | 3.4    | Rese   | rt                          | 22 |

|    | 3.5    | LPDI   | DR4 SDRAM                   | 23 |

|    | 3.6    | xSPI   | Interface                   | 23 |

|    | 3.7    | еММ    | C Memory                    | 23 |

|    | 3.8    | uSD(   | Card Interface              | 23 |

|    | 3.9    | uSD2   | 2 Card Interface            | 24 |

|    | 3.10   | ADC    |                             | 24 |

|    | 3.11   | I3C    |                             | 25 |

|    | 3.12   | I2C    |                             | 25 |

|    | 3.13   | 26     |                             |    |

|    | 3.     | 13.1   | JTAG Adaptor                | 27 |

|    | 3.14   | Gigal  | bit Ethernet Interface      | 28 |

|    | 3.15   | Curre  | ent Monitor                 | 28 |

|    | 3.16   | SMA    | RC Edge Connector           | 29 |

|    | 3.     | 16.1   | Display Interfaces          | 29 |

|    | 3.     | 16.2   | Camera Interfaces           | 29 |

|    | 3.16.3 |        | SDIO Card (4 bit) Interface | 29 |

|    | 3.     | 16.4   | SPI Interfaces              |    |

|    |        | 16.5   | Audio                       |    |

|    | 3.     | 16.6   | I2C Interfaces              | 31 |

| 3.16.7        | Asynchronous Serial Ports | 31 |

|---------------|---------------------------|----|

| 3.16.8        | CAN Bus                   | 32 |

| 3.16.9        | USB Interfaces            | 32 |

| 3.16.10       | PCI Express               | 33 |

| 3.16.11       | SATA                      | 33 |

| 3.16.12       | Ethernet                  | 34 |

| 3.16.13       | GPIO                      | 35 |

| DEVICION LIII | CTORY                     | 20 |

| KENIOION HI   | STORY                     | 36 |

## RZ Family / RZ/G Series

#### RZ/G3S SMARC Module Board

### 1. Introduction

The RZ/G3S SMARC Module board (hereinafter referred to as "G3S SMARC Module") is a platform designed according to the SMARC 2.1.1 Specification providing evaluation of the Renesas RZ/G3S microcontroller R9A08G045S33GBG.

Basically, the G3S SMARC Module is connected to the Renesas RZ SMARC Series Carrier Board II (hereinafter referred to as "RZ SMARC Carrier II") and used as the RZ/G3S SMARC Evaluation Board (hereinafter referred to as "G3S SMARC EVK").

The G3S SMARC EVK is an entry-level development board, which helps designers to get familiar with the processor before investing a large amount of resources to more specific designs.

This guide includes system setup and configuration. This guide also provides detailed information on the overall design and use of the G3S SMARC Module from a hardware system perspective.

Figure 1.1 RZ/G3S SMARC Module Board

The key features of the G3S SMARC Module are as follows.

| Board Features                      | Details                                                                                  |  |  |

|-------------------------------------|------------------------------------------------------------------------------------------|--|--|

| Processor                           | RZ/G3S (P/N: R9A08G045S33GBG), 14 mm × 14 mm, 0.5-mm pitch, 456-pin PBGA                 |  |  |

| Memory                              | 1GB 512Mx16 LPDDR4 SDRAM supporting data rate up to 1600MT/s                             |  |  |

|                                     | Micro SD card slot with default, high-speed, UHS-I/SDRR50, SDR104 transfer modes support |  |  |

|                                     | 64GB eMMC flash with HS200 transfer mode support                                         |  |  |

|                                     | Micro SD card slot with default, high-speed transfer modes support                       |  |  |

|                                     | 128Mbit Quad SPI flash memory                                                            |  |  |

| Supported interface and peripherals | Supports 10-pin JTAG connection from a debugger                                          |  |  |

|                                     | Supports ADC connection for 8 channels                                                   |  |  |

|                                     | I3C interface                                                                            |  |  |

|                                     | 5x ISL28025FRZ for current monitoring                                                    |  |  |

|                                     | 2x Gigabit Ethernet Transceiver                                                          |  |  |

|                                     | 9-channel PMIC (P/N: RAA215300A2GNP#HA3)                                                 |  |  |

|                                     | 6-channel clock generator (P/N: 5L35023B-615NLGI)                                        |  |  |

| Board dimensions                    | 82mm(W) * 80mm(L), 6-layer                                                               |  |  |

The G3S SMARC Module may be used in any carrier board which follows the SMARC 2.1.1 Specification, however, Renesas recommends using the Renesas RZ SMARC Carrier II board.

The details of the RZ SMARC Carrier II board are to be found in the RZ SMARC Carrier II User Manual.

#### 1.1 Kit Contents

The following components are included in the RZ/G3S SMARC Module Board Kit (P/N: RTK9843S33C01000BE).

- RZ/G3S SMARC Module board

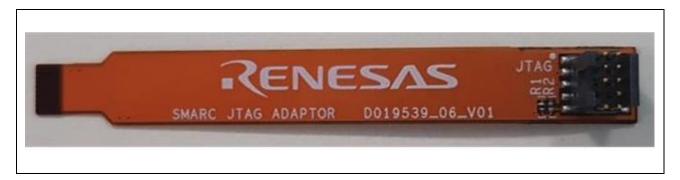

- RZ SMARC Series JTAG adaptor cable (P/N: RTK9SMCABJB00000BE) (hereinafter referred to as "SMARC JTAG Adaptor")

RZ SMARC Series JTAG adaptor cable

RZ/G3S SMARC Module board

Figure 1.2 RZ/G3S SMARC Module Board Kit Contents

If you have purchased the RZ/G3S SMARC Evaluation Board Kit, your contents will include:

- RZ/G3S SMARC Module Board Kit (P/N: RTK9843S33C01000BE)

- RZ/G3S SMARC Module board

- RZ SMARC Series JTAG adaptor cable

- RZ/G3S SMARC Carrier Board II Kit (P/N: RTK9SMCB02000BE)

- RZ SMARC Series Carrier Board II

- USB Type-A to USB Micro B cable for serial debug

- Accessories bag:

- 2off M2.5 x6mm pan-head machine screws (for securing M.2 cards)

- 1off 2.5mm spacer (for securing M.2 key B cards)

#### NOTE

The Module will have been fitted to the Carrier using 7off M2.5 x4mm pan-head machine screws.

## 1.2 Module Assembly

The G3S SMARC Module can only be used when fitted to a SMARC compliant Carrier board.

Secure the Module using 70ff M2.5 x4mm pan-head machine screws (these are provided with the RZ SMARC Carrier II).

If connection to the JTAG interface is required, it may be necessary to connect the SMARC JTAG Adaptor. Refer to the section heading **JTAG**.

## 2. System Description

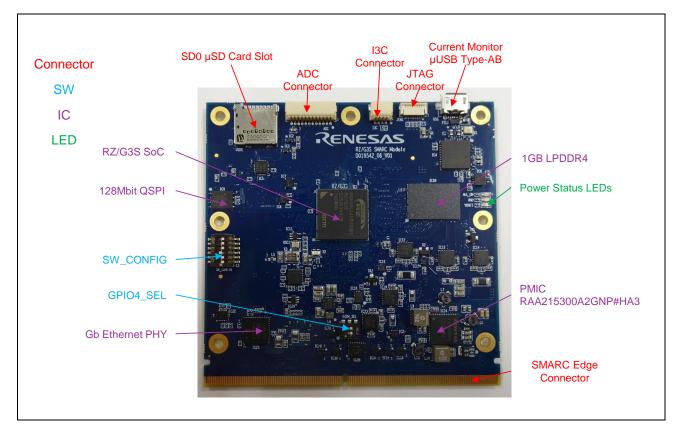

Figure 2.1 RZ/G3S SMARC Module Board Top View

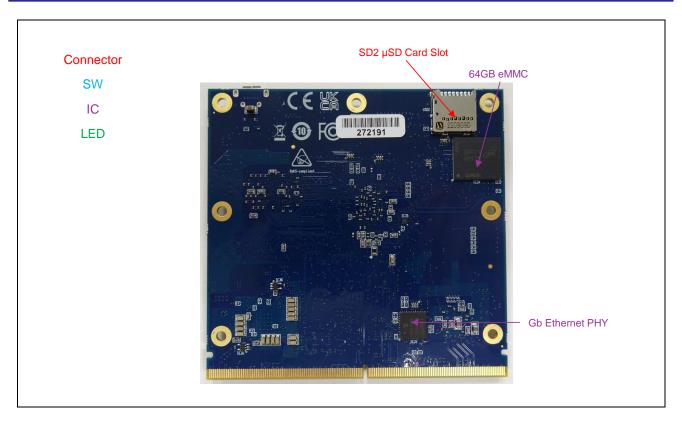

Figure 2.2 RZ/G3S SMARC Module Board Bottom View

The G3S SMARC Module has several switched configuration options and on-board interfaces. These are detailed in the following sections.

The default settings are highlighted.

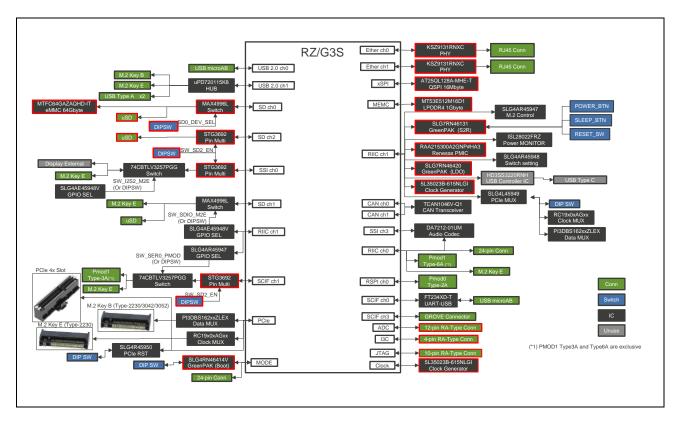

### 2.1 G3S SMARC EVK Functional Block

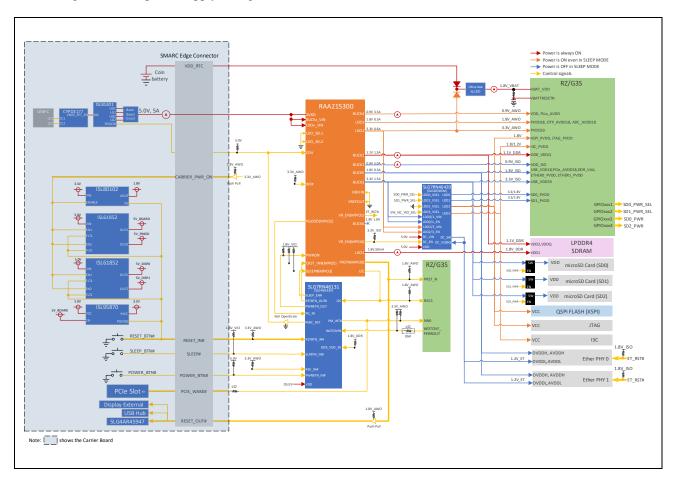

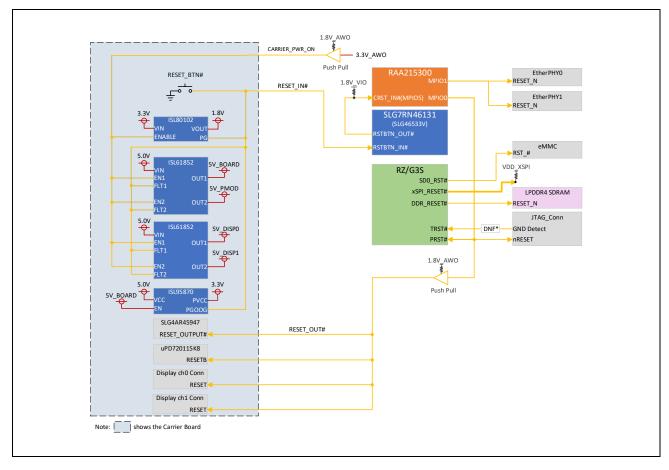

**Figure 2.3** shows the functional block diagram of the G3S SMARC EVK. ICs, connectors and switches surrounded by red frame indicate functions used on the G3S SMARC Module.

Figure 2.3 G3S SMARC EVK Block Diagram

## 2.2 G3S SMARC EVK Interface Mapping

Renesas parts are highlighted.

Table 2.1 Interface Mapping (1/2)

| SMARC<br>Interface Name | RZ/G3S I/F | Device Part Number    | Description                                                                                            |

|-------------------------|------------|-----------------------|--------------------------------------------------------------------------------------------------------|

| USB0                    | USB2.0 ch0 | 629105150921          | USB Type-microB receptacle                                                                             |

| USB1                    | USB2.0 ch1 | uPD720115K8-711-BAK-A | USB Hub IC                                                                                             |

|                         |            | 72309-8014BLF         | USB Type-A receptacle                                                                                  |

| CAN0                    | CAN ch0    | TCAN1046VDMTRQ1       | CAN transceiver                                                                                        |

|                         |            | SM03B-SRSS-TB(LF)(SN) | 3-pin connector                                                                                        |

| CAN1                    | CAN ch1    | SM03B-SRSS-TB(LF)(SN) | 3-pin connector                                                                                        |

| I2S0                    | SSI ch3    | DA7212-01UM           | Audio Codec                                                                                            |

|                         |            | STX-4335-5BGP-S1      | Stereo Headphone, Stereo Mic, Aux for connector                                                        |

|                         |            | M20-9990246           | Speaker for pin header                                                                                 |

| I2S2                    | SSI ch0    | MDT420B01001          | M.2 Key E for I2S interface                                                                            |

| SPI1                    | RSPI ch0   | SSW-106-02-T-D-RA     | PMOD Type-2A connector                                                                                 |

| SER0                    | SCIF ch1   | SSW-106-02-T-D-RA     | PMOD Type-3A connector                                                                                 |

| SER1                    | SCIF ch3   | 110990037             | Grove connector                                                                                        |

| SER3                    | SCIF ch0   | FT234XD-T             | USB to UART conversion IC                                                                              |

|                         |            | 629105150921          | UART Debug for USB Type-microB receptacle                                                              |

| PCIE_A                  | PCIe Gen2  | 10061913-111PLF       | PCIe 4x Slot                                                                                           |

|                         |            | MDT420B01001          | M. 2 Key B                                                                                             |

|                         |            | MDT420E01001          | M. 2 Key E                                                                                             |

|                         |            | 78646-3001            | SIM card for M. 2 Key B                                                                                |

|                         |            | MDT420B01001          | M. 2 Key B                                                                                             |

| GBE0                    | Ether ch0  | KSZ9131RNXC           | Ethernet PHY                                                                                           |

|                         |            | 2301997-7             | Stacked RJ45 connector                                                                                 |

| GBE1                    | Ether ch1  | KSZ9131RNXC           | Ethernet PHY                                                                                           |

| I2C_GP                  | RIIC ch0   | GRPB122VWQS-RC        | GPIO pin header                                                                                        |

|                         |            | MDT420B01001          | M. 2 Key E for I2C interface                                                                           |

|                         |            | DA7212-01UM           | Audio Codec for I2C interface                                                                          |

|                         |            | SSW-106-02-T-D-RA     | PMOD Type-6A connector                                                                                 |

| I2C_PM                  | RIIC ch1   | ISL28022FRZ           | Current monitor for measuring SMARC module                                                             |

|                         |            | SLG4L45949            | GreenPAK (PCIe Data Multiplexing Control, PCIe Slot Enable M.2 Key E Enable, M.2 Key B Enable)         |

|                         |            | SLG4R45950            | GreenPAK (PCIe Slot Reset, M.2 Key E Reset, M.2 Key B Reset)                                           |

|                         |            | SLG4AE45947           | GreenPAK (GPIO and SER0 Multiplexing Control, M.2 Key B Reset/Power off, M.2 Key E Disable)            |

|                         |            | SLG4AE45948           | GreenPAK (M.2 Key B Configuration Decoding, USB2, I2S2 and SDIO Multiplexing Control, USB1 Hub Enable) |

|                         |            | RAA215300A2GNP#HA3    | PMIC                                                                                                   |

|                         |            | SLG7RN46420           | GreenPAK (Power Regulator)                                                                             |

|                         |            | SLG7RN46131           | GreenPAK (Power/Reset control)                                                                         |

|                         |            | ISL28025FRZ           | Current monitor for measuring five power rails on SMARC module                                         |

| _                       | SD/MMC ch0 | 1040310811            | USB Type-microB receptacle                                                                             |

|                         |            | MTFC64GASAQHD-IT      | 64GB eMMC memory                                                                                       |

Table 2.1 Interface Mapping (2/2)

| SMARC          |            |                       |                                                                |

|----------------|------------|-----------------------|----------------------------------------------------------------|

| Interface Name | RZ/G3S I/F | Device Part Number    | Description                                                    |

| SDIO           | SD/MMC ch1 | 1040310811            | USB Type-microB receptacle                                     |

| _              | SD/MMC ch2 | 1040310811            | USB Type-microB receptacle                                     |

| _              | MEMC       | MT53E512M16D1FW-046WT | 1GB LPDDR4 SDRAM                                               |

| _              | xSPI       | AT25QL128A-MHE        | 128Mbit Quad SPI Flash memory                                  |

| _              | ADC        | SM12B-SRSS-TB(LF)(SN) | 12-pin connector                                               |

| _              | I3C        | SM04B-SRSS-TB(LF)(SN) | 4-pin connector                                                |

| _              | JTAG       | 10051922-1010EHLF     | 10-pin connector                                               |

| _              | CPG        | 5L35023B-615NLGI      | Clock Generator                                                |

|                |            | 830208214909          | AUDIO_CLK2 for oscillator                                      |

| _              | Power      | ISL28025FRZ           | Current monitor for measuring five power rails on SMARC module |

|                |            | FT232HQ-REEL          | USB to I2C conversion IC                                       |

|                |            | 629105150921          | USB Type-microB receptacle                                     |

## 2.3 Board Configuration and Status

This section provides details of the G3S SMARC Module switch settings.

### 2.3.1 SW\_CONFIG

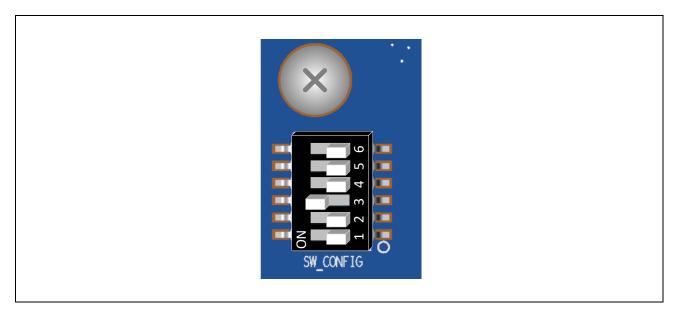

A bank of 6-switches is used to configure operating modes of the Module. The default settings are highlighted.

Figure 2.4 The Location and the Default Setting of the SW\_CONFIG

Table 2.2 DIP Switch "SW\_CONFIG" Settings

| SW_CONFIG[x] | Signal         | ON                                 | OFF                       |

|--------------|----------------|------------------------------------|---------------------------|

| 6            | RZ_BOOTCPUSEL  | Cold boot from Cortex-M33(w/o FPU) | Cold boot from Cortex-A55 |

| 5            | RZ_MD_CLKS     | SSCG is disabled                   | SSCG is enabled           |

| 4            | SW_I3C_VIO_SEL | I3C voltage is 1.2 V               | I3C voltage is 1.8 V      |

| 3            | SW_SD2_EN      | SD2 is disabled.                   | SD2 is enabled            |

| 2            | SW_SD0_DEV_SEL | SD0 connected to uSD0 card         | SD0 connected to eMMC     |

| 1            | RZ_DEBUGEN     | JTAG Debug is disabled             | JTAG Debug is enabled     |

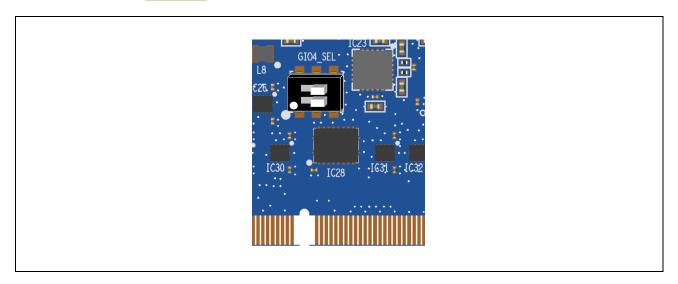

#### 2.3.2 **GPIO4\_SEL**

The SMARC GPIO4 signal from/to the Carrier II may be used for RZ\_TAMPIN as an alternative to the default port pin. The default settings are highlighted.

Figure 2.5 The Location and the Default Setting of the GPIO4\_SEL

Table 2.3 DIP Switch "GPIO4\_SEL" Settings (1/2)

| GPIO4_SEL | GPIO4 Function                               |  |

|-----------|----------------------------------------------|--|

| 1 – 2     | SMARC GPIO4 pin is connected to RZ_TAMPIN    |  |

| 2 – 3     | SMARC GPIO4 pin is connected to RZ/G3S P18_0 |  |

|           | Note: RZ_TAMPIN is pulled up to VBATT_VDD    |  |

Table 2.3 DIP Switch "GPIO4\_SEL" Settings (2/2)

| GPIO4_SEL | Function       |

|-----------|----------------|

| 4-5       | Spare – unused |

| 5 – 6     | Spare – unused |

#### 2.4 List of Pin Functions

#### 2.4.1 LED Indicators

The RZ/G3S has the following four power modes depending on the power on/off combination of the power domain. There are three Red LEDs on the G3S SMARC Module to provide indication of the RZ/G3S power modes.

Table 2.4 Indicator LEDs – Power Status

| ALL_ON | AWO | VBAT | Power Mode                                                                 |

|--------|-----|------|----------------------------------------------------------------------------|

| On     | On  | On   | ALL_ON                                                                     |

|        |     |      | All CPUs and peripheral modules are active                                 |

| Off    | On  | On   | AWO                                                                        |

|        |     |      | Cortex-M33 and peripheral modules in PD_VCC and PD_VBATT domain are active |

| Off    | Off | On   | VBATT                                                                      |

|        |     |      | Only RTC, tamper detection and backup registers are active                 |

| Off    | Off | Off  | ALL_OFF                                                                    |

|        |     |      | All CPUs and peripheral modules are disabled                               |

## 2.5 Recommended Operating Condition

**Table 2.5** lists operating conditions of the G3S SMARC Module.

Table 2.5 Operating Conditions of G3S SMARC Module

| Symbol | Item                             | Rated Value     | Note                                             |

|--------|----------------------------------|-----------------|--------------------------------------------------|

| VDD_IN | Power voltage *1                 | 3.0 V to 5.25 V | Reference: SMARC 2.1.1 Specification             |

| _      | Maximum power consumption        | 5 A             | Reference: SMARC 2.1.1 Specification             |

| Topr   | Operating ambient temperature *2 | 0°C to 40°C     | Do not expose to condensation or corrosive gases |

Note 1. Supplied from the connected RZ SMARC Carrier II.

Note 2. The ambient temperature is the air temperature at a point as close to the board as possible.

## 3. Functional Specifications

#### 3.1 Processor

The RZ/G3S (P/N: R9A08G045S33GBG,  $14 \text{ mm} \times 14 \text{ mm}$ , 0.5 -mm pitch, 456 -pin) includes a single ARM Cortex-A55 core with speeds up to 1.2 GHz. Dual Arm Cortex-M33 cores with speeds up to 250 MHz is for real-time and low-power processing. One Arm Cortex-M33 has FPU function. Low power mode is supported and realized low power consumption of micro ampere class. Also, dual 1 Gbit/s Ethernet controllers and PCI Express Gen2 drive gateway applications with low latency.

The RZ/G3S is useful for application such as:

• IoT gateway

For details on the processor, see the RZ SMARC Series Carrier Board II User's Manual: Hardware.

## 3.2 Power Supply

Figure 3.1 shows a block diagram of power system of the G3S SMARC EVK.

This board has one USB Type-C receptacle for power input with USB Power Delivery. The input voltage of VBUS can be selected among 5 V, 9 V, 15 V, and 20 V.

The 5 V power supply is supplied to the PMIC (RAA215300A2GNP#HA3) installed in the G3S SMARC Module, and the PMIC generates the power supply voltage for each interface.

Figure 3.1 Power System Circuitry of G3S SMARC EVK

#### 3.3 Clock

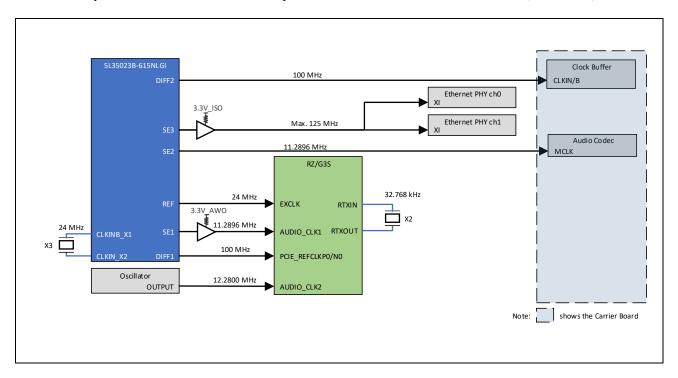

The clock generator (part number 5L35023B-615NLGI) provides the clock required for the G3S SoC and peripheral interfaces.

The 5L35023B is Renesas VersaClock@ 3S programmable clock generator and supports 6 unique frequency outputs.

The 5L35023B-615NLGI takes the 24 MHz crystal as a reference input and provides a 24 MHz reference clock output for the G3S SoC, two 11.2896 MHz LVCMOS clock outputs for the G3S SoC and Audio Codec, one 125 MHz LVCMOS clock output for two Ethernet PHYs, and two 100 MHz LPHSCL clock outputs for the G3S SoC and a PCI Express Card Module. One oscillator provides 12.2880 MHz clock output for the G3S SoC.

An external crystal is attached to the G3S SoC to provide clock to the RTC domain of the SoC (32.768 kHz).

Figure 3.2 Clock Architecture of G3S SMARC EVK

Clock inputs required for peripherals such as FT232HQ, USB Hub, M.2 Key E Card Module, HDMI Transmitter are generated locally using separate crystals or oscillators. The crystals or oscillators used to provide the reference clocks for the G3S SMARC EVK peripherals are shown in the table below.

Table 3.1 Clock Table

| Peripheral         | Device Part Number          | Frequency  |

|--------------------|-----------------------------|------------|

| FT232HQ Bridge     | FL2400022                   | 24.000 MHz |

| USB Hub*1          | FL2400022                   | 24.000 MHz |

| M.2 Key E*1        | 7XZ-32.768KBE               | 32.768 kHz |

| HDMI Transmitter*2 | SIT1602AI-23-18E-12.000000D | 12.000 MHz |

Note 1. RZ SMARC Carrier II

Note 2. SMARC MIPI-DSI to HDMI Adaptor. However, the SMARC MIPI-DSI to HDMI adaptor is not bundled with the RZ/G3S SMARC EVK.

#### 3.4 Reset

Figure 3.3 shows block diagrams of a reset control for the G3S SMARC EVK.

For the G3S SMARC EVK, the G3S SoC and Ethernet PHY on the G3S SMARC Module and some modules on the RZ SMARC Carrier II are controlled by the reset signal from the RAA215300.

There are two types of system resets.

- Cold reset by power-on reset

- Warm reset by the reset button switch

Figure 3.3 Reset Architecture of G3S SMARC EVK

#### 3.5 LPDDR4 SDRAM

The G3S SMARC Module supports LPDDR4 SDRAM. A LPDDR4 SDRAM from Micron Technology (part number MT53E512M16D1FW-046WT) is provided for connection to the RZ/G3S DDR IO.

#### 3.6 xSPI Interface

The G3S SMARC Module supports QSPI flash memory for xSPI interfaces. A QSPI flash memory from Renesas (part number AT25QL128A-MHE) is provided for connection to the RZ/G3S xSPI IO.

### 3.7 eMMC Memory

This eMMC is on the bottom side of the G3S SMARC Module. An eMMC from Micron Technology (part number MTFC64GASAQHD-IT) is provided for connection to the RZ/G3S MMC IO.

The RZ/G3S MMC IO may be used either for eMMC (SW\_CONFIG[2]=OFF) or for the uSD0 Card interface (SW\_CONFIG[2]=ON).

#### 3.8 uSD0 Card Interface

This uSD card interface is on the top side of the G3S SMARC Module. Cards must be inserted with the contacts facing down.

The connector is a push-pull type.

The RZ/G3S SD0 IO may be used either for eMMC (SW\_CONFIG[2]=OFF) or for the uSD0 Card interface (SW\_CONFIG[2]=ON).

Additional control of the uSD0 card using the RZG3S port pins is shown below.

Table 3.2 uSD0 Signals

| uSD Card Signals          | RZ Port Pin | Direction | Function           |

|---------------------------|-------------|-----------|--------------------|

| uSD0 Card Detect          | P0_0        | Input     | 0: Card present    |

|                           |             |           | 1: No card present |

| uSD0 Card Power Enable    | P2_1        | Output    | 0: Power disabled  |

|                           |             |           | 1: Power enabled   |

| uSD0 Card IO Power Select | P2_2        | Output    | 0: 1.8 V           |

|                           |             |           | 1: 3.3 V           |

#### 3.9 uSD2 Card Interface

This uSD card interface is on the bottom side of the G3S SMARC Module. Cards must be inserted with the contacts facing up.

The connector is a push-pull type.

The RZ/G3S SD2 IO may be used either for SCIF1, SSI3, IRQ0, IRQ1 (SW\_CONFIG[3]=ON) or for the uSD2 Card interface (SW\_CONFIG[3]=OFF).

The uSD2 card signals, using the RZG3S port pins, are shown below.

Table 3.3 uSD2 card Signals

| uSD Card Signals          | RZ Port Pin   | Direction | Function                              |

|---------------------------|---------------|-----------|---------------------------------------|

| uSD2 Data0                | P11_2         | In/Out    | uSD2 data                             |

| uSD2 Data1                | P11_3         | In/Out    | uSD2 data                             |

| uSD2 Data2                | P12_0         | In/Out    | uSD2 data                             |

| uSD2 Data3                | P12_1         | In/Out    | uSD2 data                             |

| uSD2 Command              | P11_1         | In/Out    | uSD2 CMD                              |

| uSD2 Clock                | P11_0         | Output    | uSD2 clock                            |

| uSD2 Card Detect          | P14_1         | Input     | 0: Card present 1: No card present    |

| uSD2 Card Power Enable    | P8_1          | Output    | 0: Power disabled<br>1: Power enabled |

| uSD2 Card IO Power Select | Not available | _         | Fixed at 3.3 V                        |

#### 3.10 ADC

A right angle, 12-pin, 1.0mm pitch connector from JST (part number SM12B-SRSS-TB) is provided for connection to the RZ/G3S ADC IO.

The ADC interface voltage is 1.8 V.

Table 3.4 ADC Pin Assignment

| Pin Number | Signal           |

|------------|------------------|

| 1          | RZ_ADC_CH0       |

| 2          | RZ_ADC_CH1       |

| 3          | RZ_ADC_CH2       |

| 4          | RZ_ADC_CH3       |

| 5          | RZ_ADC_CH4       |

| 6          | RZ_ADC_CH5       |

| 7          | RZ_ADC_CH6       |

| 8          | RZ_ADC_CH7       |

| 9          | RZ_ADC_TRG       |

| 10         | ADC_AVDD (1.8 V) |

| 11         | 3.3V_AWO (3.3 V) |

| 12         | Ground           |

#### 3.11 I3C

A right angle, 4-pin, 1.0mm pitch connector from JST (part number SM04B-SRSS-TB) is provided for connection to the RZ/G3S I3C IO.

Table 3.5 I3C Pin Assignment

| Pin Number | Signal                   |

|------------|--------------------------|

| 1          | RZ_I3C_SCL               |

| 2          | RZ_I3C_SDA               |

| 3 *1       | VDD_I3C (1.2 V or 1.8 V) |

| 4          | Ground                   |

Note 1. The I3C interface voltage is either 1.8 V (when SW\_CONFIG[4]=OFF) or 1.2 V (when SW\_CONFIG[4]=ON).

#### 3.12 I2C

There are two I2C interfaces connected to the SMARC Edge connector.

RIIC ch0 is connected to the general purpose "I2C\_GP" interface. RIIC ch1 is connected to the power management "I2C\_PM" interface.

RIIC0 is not connected to any devices on the G3S SMARC Module.

Table 3.6 Address Mapping for RIIC1

| RIIC1 Device                               | 7-bit Address |

|--------------------------------------------|---------------|

| Renesas RAA215300A2GNP#HA3 (PMIC)          | 0x12          |

| Renesas GreenPAK SLG7RN46420 (logic)       | 0x28          |

| Renesas GreenPAK SLG7RN46131 (logic)       | 0x38          |

| Renesas 5L35023B-615NLGI (clock generator) | 0x68          |

#### 3.13 **JTAG**

The G3S SMARC Module JTAG interface is implemented with a 10-pin, 0.5mm pitch, FPC connector from FCI (part number 10051922-1010EHLF). All JTAG IO are 1.8V levels.

Table 3.7 JTAG Pin Assignment

| JTAG Pin Number | SMARC Specification | Module Connection |

|-----------------|---------------------|-------------------|

| 1               | VDD_JTAG            | VDD_XSPI (1.8 V)  |

| 2               | JTAG_TRST#          | JTAG_TRST#_18 *1  |

| 3               | JTAG_TMS            | JTAG_TMS_18       |

| 4               | JTAG_TDO            | JTAG_TDO_18       |

| 5               | JTAG_TDI            | JTAG_TDI_18       |

| 6               | JTAG_TCK            | JTAG_TCK_18       |

| 7               | JTAG_RTCK           | Not connected     |

| 8               | JTAG_RESET_IN#      | RZ_PRST#          |

| 9               | MFG_MODE#           | Not connected     |

| 10              | GND                 | Ground            |

Note 1. To use the JTAG interface, RZ\_DEBUGEN must be high (SW\_CONFIG[1]=OFF). If RZ\_DEBUGEN is low (SW\_CONFIG[1]=ON), the TRST# pin is held low and the JTAG interface will not function.

This connector and its pinout are part of the SMARC specification, but since most JTAG tools require a 9-pin header, the Renesas SMARC JTAG Adaptor is included in the kit.

#### 3.13.1 JTAG Adaptor

The flexi SMARC JTAG Adaptor is required to convert the SMARC specified FPC connection to the 9-pin Cortex debug header.

Figure 3.4 SMARC JTAG Adaptor Top View

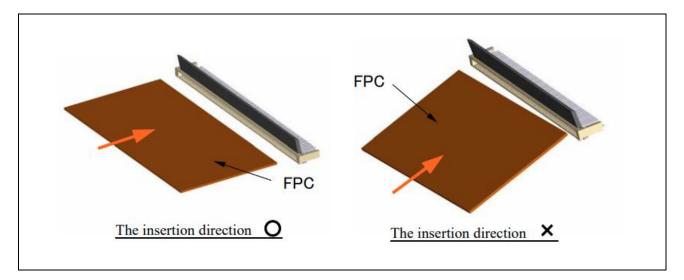

To insert the flexi SMARC JTAG Adaptor, first open the FPC connector by lifting the tab from behind. Then insert the flexi cable and close the tab to lock it in place. Ensure the connection is square and made with the flexi contacts facing down.

Figure 3.5 Caution When Connecting SMARC JTAG Adaptor to Connector

Table 3.8 JTAG Pin Assignment for SMARC JTAG Adaptor

| Cortex 9-Pin Header Pin<br>Number | Module Connection | Module Connection | Cortex 9-Pin Header Pin<br>Number |

|-----------------------------------|-------------------|-------------------|-----------------------------------|

| 1                                 | VDD_XSPI (1.8 V)  | JTAG_TMS_18       | 2                                 |

| 3                                 | Ground            | JTAG_TCK_18       | 4                                 |

| 5                                 | Ground            | JTAG_TDO_18       | 6                                 |

| 7                                 | No pin (key)      | JTAG_TDI_18       | 8                                 |

| 9 *1                              | Ground            | RZ_PRST#          | 10                                |

Note 1. By default, TRST# is not connected and pin 9 is ground. However, resistor options allow TRST# to be connected to pin 9.

## 3.14 Gigabit Ethernet Interface

Two gigabit Ethernet transceivers with RGMII support are mounted on the G3S SMARC Module.

There are RJ45 connectors to the SMARC Edge connector. Please refer to **Ethernet** for pin assignment.

#### 3.15 Current Monitor

The G3S SMARC Module includes current monitoring circuitry that is accessed through the on-board micro-USB connector

The current monitoring circuitry is powered from the USB and is completely independent of all other module and RZ/G3S functions.

A software application is required to execute on a host PC and provides current measurements for

- 0.9V\_AWO

- 0.9V\_ISO

- 1.1V\_DDR

- 1.8V\_DDR

- VBAT\_VDD

Table 3.9 I2C Address Mapping for Current Monitoring

| Device                          | 7-bit Address |

|---------------------------------|---------------|

| Renesas ISL28025FR12Z(0.9V_AWO) | 0xa0          |

| Renesas ISL28025FR12Z(0.9V_ISO) | 0x84          |

| Renesas ISL28025FR12Z(1.1V_DDR) | 0x86          |

| Renesas ISL28025FR12Z(1.8V_DDR) | 0x9c          |

| Renesas ISL28025FR12Z(VBAT_VDD) | 0x9e          |

## 3.16 SMARC Edge Connector

The SMARC edge connector has a Primary side (Pxx) and Secondary side (Sxx). The SMARC signal names and edge connector pin numbers are listed in the tables below along with the RZ/G3S port pin (if applicable) and signal name. The default settings are highlighted.

#### 3.16.1 Display Interfaces

The RZG3S does not support any display interfaces. None of the display signals are connected.

#### 3.16.2 Camera Interfaces

The RZG3S does not support any camera interfaces. None of the camera signals are connected.

#### 3.16.3 SDIO Card (4 bit) Interface

The SDIO signal is routed to the SMARC Edge Connector.

Table 3.10 SDIO Signals

| SMARC Signal Name | Pin # | RZ Port Pin  | Signal         |

|-------------------|-------|--------------|----------------|

| SDIO_D0           | P39   | SD1_DATA0    | RZ_SD1_D0      |

| SDIO_D1           | P40   | SD1_DATA1    | RZ_SD1_D1      |

| SDIO_D2           | P41   | SD1_DATA2    | RZ_SD1_D2      |

| SDIO_D3           | P42   | SD1_DATA3    | RZ_SD1_D3      |

| SDIO_WP           | P33   | <del>_</del> | Not connected  |

| SDIO_CMD          | P34   | SD1_CMD      | RZ_SD1_CMD     |

| SDIO_CD#          | P35   | P0_2         | RZ_SD1_CD#     |

| SDIO_CK           | P36   | SD1_CLK      | RZ_SD1_CLK     |

| SDIO_PWR_EN       | P37   | P2_3         | RZ_SDIO_PWR_EN |

|                   |       |              |                |

#### 3.16.4 SPI Interfaces

The SPI1 signal is routed to the SMARC Edge Connector.

The SPI0 signal is not connected to the SMARC Edge Connector.

Table 3.11 SPI0 and SPI1 Signals

| SMARC Signal Name | Pin # | RZ Port Pin | Signal        |

|-------------------|-------|-------------|---------------|

| SPI0_CS0#         | P43   | <u> </u>    | Not connected |

| SPI0_CS1#         | P31   | <u> </u>    | Not connected |

| SPI0_CK           | P44   | _           | Not connected |

| SPI0_DIN          | P45   | <u> </u>    | Not connected |

| SPI0_DO           | P46   | <u> </u>    | Not connected |

| SPI1_CS0#         | P54   | P15_3       | RZ_RSPI0_SSL  |

| SPI1_CS1#         | P55   | _           | Not connected |

| SPI1_CK           | P56   | P15_0       | RZ_RSPI0_CK   |

| SPI1_DIN          | P57   | P15_2       | RZ_RSPI_MISO  |

| SPI1_DO           | P58   | P15_1       | RZ_RSPI0_MOSI |

### 3.16.5 Audio

These signals are routed to the SMARC Edge Connector.

Table 3.12 I2S0 and I2S2 Signals

| SMARC Signal Name | Pin # | RZ Port Pin | Signal                         |

|-------------------|-------|-------------|--------------------------------|

| I2S0_LRCK         | S39   | P18_3       | RZ_SSI3_RCK                    |

| I2S0_SDOUT        | S40   | P18_4       | RZ_SSI3_TXD                    |

| I2S0_SDIN         | S41   | P18_5       | RZ_SSI3_RXD                    |

| I2S0_CK           | S42   | P18_2       | RZ_SSI3_BCK                    |

| AUDIO_MCK         | S38   | N/A         | AUDIO_MCK (clock generator)    |

| I2S2_LRCK *1      | S50   | P11_1       | RZ_SSI0_RCK                    |

|                   |       | _           | Not connected                  |

| 12S2_SDOUT *1     | S51   | P11_2       | RZ_SSI0_TXD                    |

|                   |       | _           | Not connected                  |

| I2S2_SDIN *1      | S52   | P11_3       | RZ_SSI0_RXD                    |

|                   |       | _           | Not connected                  |

| I2S2_CK *1        | S53   | P11_0       | RZ_SSI0_BCK                    |

|                   |       | _           | Not connected                  |

| AUDIO_MCK         | S38   | N/A         | AUDIO_MCK<br>(clock generator) |

Note 1. SW\_CONFIG[3] switch option on the G3S SMARC Module

#### 3.16.6 I2C Interfaces

The I2C\_GP and I2C PM signals are routed to the SMARC Edge Connector.

The I2C\_CAM0, I2C\_CAM1, and I2C\_LCD signals are not connected to the SMARC Edge Connector.

Table 3.13 I2C\_GP and I2C\_PM Signals

| SMARC Signal Name | Pin # | RZ Port Pin | Signal       |

|-------------------|-------|-------------|--------------|

| I2C_GP_CK         | S48   | RIIC0_SCL   | RZ_RIIC0_SCL |

| I2C_GP_DAT        | S49   | RIIC0_SDA   | RZ_RIIC0_SDA |

| I2C_PM_CK         | P121  | RIIC1_SCL   | RZ_RIIC1_SCL |

| I2C_PM_DAT        | P122  | RIIC1_SDA   | RZ_RIIC1_SDA |

#### NOTE

RZ\_RIIC1 bus is also used on the G3S SMARC Module itself for:

• Power/Reset Control: SLG7RN46131

• PMIC: RAA215300A2GNP#HA3

• Power Regulator: SLG7RN46420

• Clock Generator: 5L35023B-615NLGI

#### 3.16.7 Asynchronous Serial Ports

The SER0, SER1, and SER3 signals are routed to the SMARC Edge Connector.

The SER2 signal is not connected to the SMARC Edge Connector.

Table 3.14 SER0, SER2t, and SER3 Signals

| SMARC Signal Name | Pin # | RZ Port Pin | Signal        |

|-------------------|-------|-------------|---------------|

| SER0_TX           | P129  | P14_0       | RZ_SCIF1_TXD  |

| SER0_RX *1        | P130  | P14_1       | RZ_SCIF1_RXD  |

|                   |       | _           | Not connected |

| SER0_RTS#         | P131  | P16_1       | RZ_SCIF1_RTS# |

| SER0_CTS#         | P132  | P16_0       | RZ_SCIF1_CTS# |

| SER1_TX           | P134  | P17_3       | RZ_SCIF3_TXD  |

| SER1_RX           | P135  | P17_2       | RZ_SCIF3_RXD  |

| SER2_TX           | P136  | -           | Not connected |

| SER2_RX           | P137  | _           | Not connected |

| SER2_RTS#         | P138  | _           | Not connected |

| SER2_CTS#         | P139  | -           | Not connected |

| SER3_TX           | P140  | P6_4        | RZ_SCIF0_TXD  |

| SER3_RX           | P141  | P6_3        | RZ_SCIF0_RXD  |

Note 1. SW\_CONFIG[3] switch option on the G3S SMARC Module

#### 3.16.8 CAN Bus

These signals are routed to the SMARC Edge Connector.

Table 3.15 CAN0 and CAN1 Signals

| SMARC Signal Name | Pin # | RZ Port Pin | Signal     |

|-------------------|-------|-------------|------------|

| CAN0_TX           | P143  | P6_1        | RZ_CAN0_TX |

| CAN0_RX           | P144  | P6_2        | RZ_CAN0_RX |

| CAN1_TX           | P145  | P17_0       | RZ_CAN1_TX |

| CAN1_RX           | P146  | P17_1       | RZ_CAN1_RX |

#### 3.16.9 USB Interfaces

The USB channel 0 and 1 signals are routed to the SMARC Edge Connector.

The USB channel 2, 3, 4, and 5 signals are not connected to the SMARC Edge connector.

Table 3.16 USB0 and USB1 Signals

| SMARC Signal Name | Pin # | RZ Port Pin | Signal          |

|-------------------|-------|-------------|-----------------|

| USB0+             | P60   | _           | RZ_USB0_DP      |

| USB0-             | P61   | _           | RZ_USB0_DM      |

| USB0_EN_OC# *     | P62   | P5_0        | RZ_USB0_VBUSEN  |

|                   |       | P5_2        | RZ_USB0_OVRCUR# |

| USB0_VBUS_DET     | P63   | _           | RZ_USB0_VBUSIN  |

| USB0_OTG_ID       | P64   | P5_3        | RZ_USB0_OTG_ID  |

| USB1+             | P65   | _           | RZ_USB1_DP      |

| USB1-             | P66   | _           | RZ_USB1_DM      |

| USB1_EN_OC# *1    | P67   | P6_0        | RZ_USB1_VBUSEN  |

|                   |       | P5_4        | RZ_USB1_OVRCUR# |

Note 1. Logic circuitry is used to provide independent enable and overcurrent IO.

#### 3.16.10 PCI Express

The PCIE\_A signal is routed to the SMARC Edge Connector.

The PCIE\_B, PCIE\_C, and PCIE\_D signals are not connected to the SMARC Edge Connector.

Table 3.17 PCIE\_A Signals

| SMARC Signal Name | Pin # | RZ Port Pin | Signal          |

|-------------------|-------|-------------|-----------------|

| PCIE_A_TX+        | P89   | _           | PCIE_A_TX+      |

| PCIE_A_TX-        | P90   | _           | PCIE_A_TX-      |

| PCIE_A_RX+        | P86   | _           | PCIE_A_RX+      |

| PCIE_A_RX-        | P87   | _           | PCIE_A_RX-      |

| PCIE_A_REFCK+     | P83   | _           | RZ_PCIE_REFCLK+ |

| PCIE_A_REFCK-     | P84   | _           | RZ_PCIE_REFCLK- |

| PCIE_A_RST#       | P75   | P13_2       | PCIE_A_RST#     |

| PCIE_A_CKREQ#     | P78   | P13_3       | PCIE_A_CKREQ#   |

#### 3.16.11 SATA

The RZG3S does not support SATA interfaces. None of the SATA signals are connected.

#### 3.16.12 Ethernet

These signals are routed to the SMARC Edge Connector.

Table 3.18 GBE0 and GBE1 Signals

| SMARC Signal Name          | Pin # | RZ Port Pin  | Signal                         |

|----------------------------|-------|--------------|--------------------------------|

| GBE0_MDI0+                 | P30   | _            | These signals are provided by  |

| GBE0_MDI0-                 | P29   |              | the Ethernet PHY controlled by |

| GBE0_MDI1+                 | P27   |              | the RZ RGMII signals ET0_xxx   |

| GBE0_MDI1-                 | P26   |              |                                |

| GBE0_MDI2+                 | P24   |              |                                |

| GBE0_MDI2-                 | P23   |              |                                |

| GBE0_MDI3+                 | P20   |              |                                |

| GBE0_MDI3-                 | P19   |              |                                |

| GBE0_LINK100#              | P21   | N/A          | ET0_LED2 (ET0 PHY)             |

| GBE0_LINK1000#             | P22   | N/A          | ET0_LED2 (ET0 PHY)             |

| GBE0_LINK_ACT#             | P25   | N/A          | ET0_LED1 (ET0 PHY)             |

| GBE0_CTREF                 | P28   | _            | Not connected                  |

| GBE0_SDP                   | P6    | _            | Not connected                  |

| Ethernet PHY0 Interrupt *1 | n/a   | P12_0        | ET0_INT# (RZ_IRQ0)             |

|                            |       | _            | Not connected                  |

| GBE1_MDI0+                 | S17   | <del>_</del> | These signals are provided by  |

| GBE1_MDI0-                 | S18   |              | the Ethernet PHY controlled by |

| GBE1_MDI1+                 | S20   |              | the RZ RGMII signals ET1_xxx   |

| GBE1_MDI1-                 | S21   |              |                                |

| GBE1_MDI2+                 | S23   |              |                                |

| GBE1_MDI2-                 | S24   |              |                                |

| GBE1_MDI3+                 | S26   |              |                                |

| GBE1_MDI3-                 | S27   |              |                                |

| GBE1_LINK100#              | S19   | N/A          | ET1_LED2 (ET1 PHY)             |

| GBE1_LINK1000#             | S22   | N/A          | ET1_LED2 (ET1 PHY)             |

| GBE1_LINK_ACT#             | S31   | N/A          | ET1_LED1 (ET1 PHY)             |

| GBE1_CTREF                 | S28   | _            | Not connected                  |

| GBE1_SDP                   | P5    | _            | Not connected                  |

| Ethernet PHY1 Interrupt *1 | n/a   | P12_1        | ET1_INT# (RZ_IRQ1)             |

|                            | II/a  | 1 12_1       | LTI_INT# (NZ_INQT)             |

Note 1. SW\_CONFIG[3] switch option on the G3S SMARC Module

#### 3.16.13 GPIO

Table 3.19 GPIO Signals

| SMARC Signal Name | Pin # | RZ Port Pin  | Signal          |

|-------------------|-------|--------------|-----------------|

| GPIO0             | P108  | -            | Not connected   |

| GPIO1             | P109  | <del>-</del> | Not connected   |

| GPIO2             | P110  | _            | Not connected   |

| GPIO3             | P111  | <del>-</del> | Not connected   |

| GPIO4 *1          | P112  | P18_0        | RZ_IRQ2_GPIO4   |

|                   |       | TAMPIN       | RZ_TAMPIN       |

| GPIO5             | P113  | P13_4        | RZ_P13_4_GPIO5  |

| GPIO6             | P114  | P0_1         | RZ_P0_1_GPIO6   |

| GPIO7             | P115  | P0_3         | RZ_P0_3_GPIO7   |

| GPIO8             | P116  | P13_0        | RZ_P13_0_GPIO8  |

| GPIO9             | P117  | P13_1        | RZ_P13_1_GPIO9  |

| GPIO10            | P118  | P18_1        | RZ_IRQ3_GPIO10  |

| GPIO11            | P119  | P14_2        | RZ_P14_2_GPIO11 |

| GPIO12            | S142  | P8_2         | RZ_P8_2_GPIO12  |

| GPIO13            | S123  | P8_3         | RZ_P8_3_GPIO13  |

Note 1. GPIO4\_SEL switch option on the G3S SMARC Module

| REVISION HISTORY | RZ Family / RZ/G Series   |

|------------------|---------------------------|

|                  | RZ/G3S SMARC Module Board |

|      |              | Description |                      |  |

|------|--------------|-------------|----------------------|--|

| Rev. | Date         | Page        | Summary              |  |

| 1.00 | Nov 14, 2023 | _           | First edition issued |  |

RZ/G3S SMARC Module Board

Publication Date: Rev.1.00 Nov 14, 2023

Published by: Renesas Electronics Corporation

RZ Family / RZ/G Series