## **RENESAS TECHNICAL UPDATE**

TOYOSU FORESIA, 3-2-24, Toyosu, Koto-ku, Tokyo 135-0061, Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                                                                                                                                                                                                                                                                                                                                                |                                           | Document<br>No.                                    | TN-RA*-A0108A/E                                                                    | Rev.                            | 1.00      |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------|-----------|

| Title                 | Addition of note for Slave Bus Control Register in<br>Buses chapter                                                                                                                                                                                                                                                                                    |                                           | Information<br>Category                            | Technical Notification                                                             |                                 |           |

| Applicable<br>Product | RA4E1 Group<br>RA4M2 Group                                                                                                                                                                                                                                                                                                                             | Lot No.<br>All                            | Reference<br>Document                              | Renesas RA4E1 Grou<br>Hardware Rev.1.10<br>Renesas RA4M2 Grou<br>Hardware Rev.1.30 |                                 |           |

|                       | ve Bus Control Register in Buses chapter is ad<br>SCNT <slave> : Slave Bus Control Register</slave>                                                                                                                                                                                                                                                    |                                           |                                                    |                                                                                    |                                 |           |

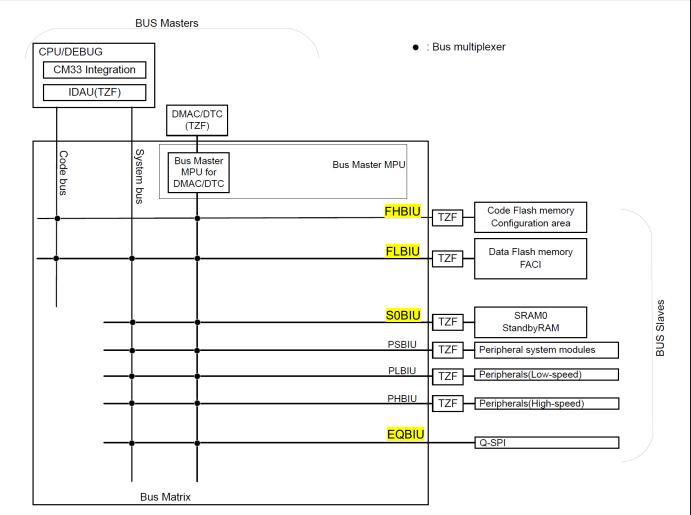

| trar<br>•<br>To       | ile both of the following two conditions are<br>insfer may not be prioritized.<br>Condition 1<br>DMAC/DTC accesses FHBIU, FLBIU, S<br>BUS slaves.<br>Condition 2<br>CPU instruction fetch loops through a sp<br>Example: loop1:subs r0,#1<br>cmp r0,#0<br>bne loop1<br>avoid this problem, set DMAC/DTC access<br>Example: DMAC/DTC accesses S0BIU (SF | 0BIU, EQB<br>becific addro<br>s bus and ( | IU, and CPU fo<br>ess. For exam<br>CPU instruction | etches instructions fro<br>ple, waiting time by so<br>n fetch to different BU      | om the s<br>oftware.<br>S Slave | ame<br>s. |

| F                     | ΉΒΙU.                                                                                                                                                                                                                                                                                                                                                  |                                           |                                                    |                                                                                    |                                 |           |

## RENESAS TECHNICAL UPDATE TN-RA\*-A0108A/E

Figure 14.1 Bus Connection

| 0xFFFF_FFFF                | System for Cortex®-M33                      |

|----------------------------|---------------------------------------------|

| 0×E000_0000                |                                             |

| 0x6800_0000                | Reserved area*2                             |

| _                          | External address space<br>(Quad SPI area)   |

| 0x6000_0000                | Reserved area*2                             |

| 0×4080_0000                | Flash I/O registers                         |

| 0x407F_C000                | Reserved area*2                             |

| 0x407F_0000                | Elech I/O engistere                         |

| 0x407E_0000                | Flash I/O registers                         |

| 0-4048-0000                | Reserved area*2                             |

| 0x4018_0000                | Peripheral I/O registers                    |

| 0x4000_0000                | Reserved area*2                             |

| 0x2800_0400                | Standby SRAM                                |

| 0x2800_0000                | Reserved area*2                             |

| 0x2002_0000                | SRAMD                                       |

| 0x2000_0000                | Reserved area*2                             |

| 0x0800_2000                | On-chip flash (data flash)                  |

| 0x0800_0000<br>0x0100_A300 | Reserved area*2                             |

| _                          | On-chip flash (option-setting memory)       |

| 0x0100_A100                | Reserved area*2                             |

| 0x0100_81B4<br>0x0100_80F0 | On-chip flash (Factory Flash)               |

| 0x0100_80F0                | Reserved area*2                             |

|                            | On-chip flash (code flash)<br>(read only)*1 |

| 0x0000_0000                |                                             |

| Figur                      | e 4.1 Memory map                            |