Date: Oct. 01, 2013

## RENESAS TECHNICAL UPDATE

1753, Shimonumabe, Nakahara-ku, Kawasaki-shi, Kanagawa 211-8668 Japan Renesas Electronics Corporation

| Product<br>Category   | MPU/MCU                                                          | Document<br>No.         | TN-SH7-A874A/E         | Rev.                                                                                 | 1.00 |  |

|-----------------------|------------------------------------------------------------------|-------------------------|------------------------|--------------------------------------------------------------------------------------|------|--|

| Title                 | SH7450 Group, SH7451 Group User's Manu<br>Hardware Errata Rev. B | Information<br>Category | Technical Notification |                                                                                      |      |  |

| Applicable<br>Product | SH7450 Group, SH7451 Group                                       | Lot No.                 | Reference<br>Document  | SH7450 Group, SH7451 Group<br>User's Manual: Hardware Rev. 1.10<br>(R01UH0286EJ0110) |      |  |

We inform you of the corrections of "SH7450 Group, SH7451 Group User's Manual: Hardware Rev. 1.10 (Published on September 27, 2011)".

When you use "SH7450 Group, SH7451 Group User's Manual: Hardware Rev. 1.10", should be used together the attached errata.

In addition, the corrections in the following are also included in the attached errata (Rev. B).

- Technical update TN-SH7-A826A/E: Errata (Rev. A)

- Technical update TN-SH7-A859A/E: Errata to User's Manual Regarding CAN Module

Attached document: "SH7450 Group, SH7451 Group User's Manual: Hardware Rev. 1.10" Errata Rev. B – 11 sheets

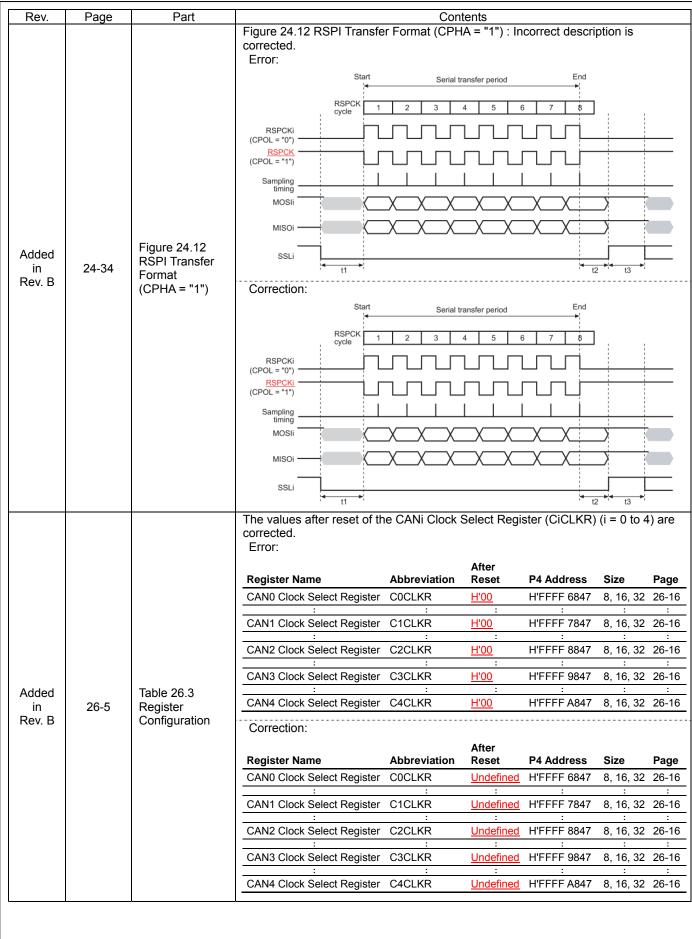

| Rev.         | Page                | Part                       | Contents                                                                                                                                                            |  |  |  |  |  |  |

|--------------|---------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|              |                     |                            | Revision History: Description of CAN is addedPage of Previous Edition: 26-49                                                                                        |  |  |  |  |  |  |

|              |                     |                            | -Description:  Description of the bit 1 (SDST bit) in the CANi Status Register (CiSTR) (i = 0 to 4) is corrected.                                                   |  |  |  |  |  |  |

|              |                     |                            | Error: The SDST bit is set to "1" when at least one SENTDATA bit in the CiMCTLj register is "1" regardless of the value of the CiMIER register.                     |  |  |  |  |  |  |

| Added<br>in  | Revision<br>History | 26.3.14<br>CANi Status     | Correction: The SDST bit is set to "1" when at least one SENTDATA bit in the CiMCTLj (j = 32 to 63) register is "1" regardless of the value of the CiMIER register. |  |  |  |  |  |  |

| Rev. A       | - xiii              | Register                   | -Page of Previous Edition: 26-49                                                                                                                                    |  |  |  |  |  |  |

|              |                     |                            | -Description: Description of the bit 0 (NDST bit) in the CANi Status Register (CiSTR) (i = 0 to 4)                                                                  |  |  |  |  |  |  |

|              |                     |                            | is corrected.                                                                                                                                                       |  |  |  |  |  |  |

|              |                     |                            | Error: The NDST bit is set to "1" when at least one NEWDATA bit in the CiMCTLj register is "1" regardless of the value of the CiMIER register.                      |  |  |  |  |  |  |

|              |                     |                            | Correction: The NDST bit is set to "1" when at least one NEWDATA bit in the CiMCTLj (j = 0 to 63) register is "1" regardless of the value of the                    |  |  |  |  |  |  |

|              |                     |                            | CiMIER register.                                                                                                                                                    |  |  |  |  |  |  |

|              |                     |                            | Revision History: Description of FlexRay is added.                                                                                                                  |  |  |  |  |  |  |

|              |                     |                            | -Page of Previous Edition: 32-17                                                                                                                                    |  |  |  |  |  |  |

|              |                     |                            | -Description: Description of the bit 24 (EDB bit) in the FlexRay Error Interrupt Register (FREIF                                                                    |  |  |  |  |  |  |

|              |                     |                            | is corrected.  Error: 0: No error detected on channel B RW                                                                                                          |  |  |  |  |  |  |

|              |                     |                            |                                                                                                                                                                     |  |  |  |  |  |  |

| Added        | Revision            | 32.5.1                     | Correction: 0: No error detected on channel B                                                                                                                       |  |  |  |  |  |  |

| in           | History             | FlexRay Error<br>Interrupt | -Page of Previous Edition: 32-18                                                                                                                                    |  |  |  |  |  |  |

| Rev. A       | - XV                | Register                   | -Description:                                                                                                                                                       |  |  |  |  |  |  |

|              |                     |                            | Description of the bit 9 (IIBA bit) in the FlexRay Error Interrupt Register (FREIR)                                                                                 |  |  |  |  |  |  |

|              |                     |                            | corrected.  Error: 0: No illegal CPU access to Output Buffer occurred                                                                                               |  |  |  |  |  |  |

|              |                     |                            | 1: Illegal CPU access to Output Buffer occurred                                                                                                                     |  |  |  |  |  |  |

|              |                     |                            | Correction: 0: No illegal CPU access to Input Buffer occurred                                                                                                       |  |  |  |  |  |  |

|              |                     |                            | 1: Illegal CPU access to Input Buffer occurred                                                                                                                      |  |  |  |  |  |  |

|              |                     |                            | Revision History: Description of Appendix A is added.                                                                                                               |  |  |  |  |  |  |

|              |                     |                            | -Page of Previous Edition: A-1                                                                                                                                      |  |  |  |  |  |  |

| Added        | Revision            | Appendix A CPU Operation   | -Description:  Value after reset of the bit 5 (RABD bit) in the CPU Operation Mode Register                                                                         |  |  |  |  |  |  |

| ın<br>Rev. A | History<br>- xvi    | Mode Register              | (CPUOPM) is revised.                                                                                                                                                |  |  |  |  |  |  |

|              |                     | ivious regists.            | Error: Value after reset of the RABD bit is "1"                                                                                                                     |  |  |  |  |  |  |

|              |                     |                            | Correction: Value after reset of the RABD bit is " 0"                                                                                                               |  |  |  |  |  |  |

| Added        |                     | 32.7.1                     | Description of the bit 29 to 24 (PSL5 to PSL0 bit) in the FlexRay CC Status Vector                                                                                  |  |  |  |  |  |  |

| in           | 32-76               | FlexRay CC                 | Register (FRCCSV) is corrected.                                                                                                                                     |  |  |  |  |  |  |

| Rev. A       |                     | Status Vector              | Error: Set to B'000100 when leaving HALT state.                                                                                                                     |  |  |  |  |  |  |

|              |                     | Register                   | Correction: Set to <u>B'000000</u> when leaving HALT state.  Table 38.26 RSPI Timing: Incorrect description is corrected.                                           |  |  |  |  |  |  |

|              |                     |                            | Error:                                                                                                                                                              |  |  |  |  |  |  |

|              |                     |                            | Item Symbol Min. Max. Unit Figures                                                                                                                                  |  |  |  |  |  |  |

| Added        |                     | Table 20.00                | Data input setup time Slave $t_{SU}$ $\frac{25 + 2 \times t_{cyc}}{25 + 2 \times t_{cyc}}$ - ns 38.28 to 38.31                                                      |  |  |  |  |  |  |

| in           | 38-33               | Table 38.26<br>RSPI Timing |                                                                                                                                                                     |  |  |  |  |  |  |

| Rev. A       |                     |                            | Correction:                                                                                                                                                         |  |  |  |  |  |  |

|              |                     |                            | ItemSymbolMin.Max.UnitFiguresData inputSlavet <sub>SU</sub> 25 - 2 x t <sub>cyc</sub> -ns38.28 to                                                                   |  |  |  |  |  |  |

|              |                     |                            | Slave t <sub>SU</sub> 25 - 2 x t <sub>cyc</sub> - ns 38.28 to 38.31                                                                                                 |  |  |  |  |  |  |

| Page 38-35    | Figure 38.30<br>RSPI Timing<br>(Slave,<br>CPHA = "0") | MOSID to MOSI2 Input  MSB IN  Correction:  SSL00, SSL10, SSL20, Input  RSPCKD to RSPCK2 CPOL - 0 Input  RSPCKD to RSPCK2 CPOL - 1 Input  MISOD to MISO2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Slave, CPHA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | A LS                      | BOUT LOR FOR              | I <sub>TD</sub> I <sub>TD</sub> I <sub>TD</sub> I <sub>TD</sub> | MSB IN  MSB OUT           |

|---------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------------|-----------------------------------------------------------------|---------------------------|

| 38-35         | RSPI Timing<br>(Slave,                                | Error:  SSL00, SSL10, SSL10, Input  RSPCKD to RSPCK2 CPCL = 0 Input  MISO0 to MISO2 Output  MOSID to MOSI2 Input  RSPCKD to RSPCK2 CPCL = 1 Input  MSB IN  Correction:  SSL00, SSL10, SSL20, Input  RSPCKD to RSPCK2 CPCL = 0 Input  MSB IN  M | SE OUT DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LSi                       | BOUT IOR FOR              | MSB IN                                                          | MSB CUT                   |

| 38-35         | RSPI Timing<br>(Slave,                                | SSL00, SSL10, SSL20, Input  RSPCK0 to RSPCK2 CPOL = 0 Input  MISO0 to MISO2 Output  MOSID to MOSI2 Input  RSPCK0 to RSPCK2 Input  MSB IN  COrrection:  SSL00, SSL10, SSL20, Input  RSPCK0 to RSPCK2 CPOL = 0 Input  MSB IN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | DATA SE OUT DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | LSi                       | BOUT IOR FOR              | MSB IN                                                          | MSB CUT                   |

| 38-35         | RSPI Timing<br>(Slave,                                | SSL10, SSL20, Input  RSPCKD to RSPCK2 CPCL - 0 Input  MISO0 to MISO2 Output  MOSID to MOSI2 Input  RSPCKD to RSPCK2 CPCL - 1 Input  MSB IN  Correction:  SSL00, SSL10, SSL20, Input  RSPCKD to RSPCK2 CPCL - 0 Input  MSB IN   | DATA SE OUT DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | LSi                       | BOUT IOR FOR              | MSB IN                                                          | MSB CUT                   |

| 38-35         | RSPI Timing<br>(Slave,                                | SSL20, Input  RSPCK0 to RSPCK2 CPOL = 0 Input  RSPCK0 to RSPCK2 CPOL = 1 Input  MISO0 to MISO2 Output  MSB IN  COrrection:  SSL00, SSL10, SSL20, Input  RSPCK0 to RSPCK2 CPOL = 0 Input  MSB IN  MSB IN  MSB IN  CORRECTION:  SSL00, SSL20, Input  RSPCK0 to RSPCK2 CPOL = 1 Input  MISO0 to MISO2 Output  MISO0 to MISO2 Output  MSD IN  MSD  | DATA SE OUT DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | LSi                       | BOUT IOR FOR              | MSB IN                                                          | MSB CUT                   |

| 38-35         | RSPI Timing<br>(Slave,                                | RSPCKD to RSPCK2 CPCL - D Input  RSPCKD to RSPCK2 CPCL - 1 Input  MISO0 to MISO2 Output  MOSID to MOSI2 Input  MSB IN  COrrection:  SSL00. SSL10. SSL20. Input  RSPCKD to RSPCK2 CPCL - D Input  RSPCKD to RSPCK2 CPCL - 1 Input  MISO0 to MISO2 Output  MISO0 to MISO2 Output  MSD IN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DATA SE OUT DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | LSi                       | LAS LOR OF                | MSB IN                                                          | MSB CUT                   |

| 38-35         | RSPI Timing<br>(Slave,                                | RSPCK0 to RSPCK2 CPOL = 1 Input  MISO0 to MISO2 Output  MOSID to MOSI2 Input  MSB IN  COrrection:  SSL00, SSL10, SSL20, Input  RSPCK0 to RSPCK2 CPOL = 0 Input  MISO0 to MISO2 Output  MISO0 to MISO2 Output  MISO0 to MISO2 Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DATA SE OUT DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | LSi                       | LAS LOR OF                | t <sub>rest</sub>                                               | MSB IN                    |

| 38-35         | RSPI Timing<br>(Slave,                                | MISO0 to MISO2 Output  MOSID to MOSI2 Input  MSB IN  Correction:  SSL00, SSL10, SSL20, Input  RSPCK0 to RSPCK2 CPOL = 0 Input  MISO0 to MISO2 Output  MISO0 to MISO2 Output  MOSID to MOSI2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | DATA SE OUT DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | LSi                       | LAS LOR OF                | t <sub>rest</sub>                                               | MSB IN                    |

| 38-35         | RSPI Timing<br>(Slave,                                | MISO0 to MISO2 Output  MOSID to MOSI2 Input  MSB IN  Correction:  SSL00. SSL10. SSL20. Input  RSPCKD to RSPCK2 CPOL = 0 Input  MISO0 to MISO2 Output  MISO0 to MISO2 Output  MOSID to MOSI2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | DATA SE OUT DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | LSi                       | LAS LOR OF                | t <sub>rest</sub>                                               | MSB IN                    |

| 38-35         | RSPI Timing<br>(Slave,                                | MISCO to MISO2 Output  MOSID to MOSI2 Input  MSB IN  COrrection:  SSL00, SSL10, SSL20, Input  RSPCKD to RSPCK2 CPOL = 0 Input  MISOD to MISO2 Output  MISOD to MOSI2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DATA SE OUT DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | LSi                       | LAS LOR OF                | t <sub>rest</sub>                                               | MSB IN                    |

| 38-35         | RSPI Timing<br>(Slave,                                | MOSID to MOSI2 Input  MSB IN  Correction:  SSL00, SSL10, SSL20, Input  RSPCKD to RSPCK2 CPCL = 0 Input  MISCO to MISO2 Output  MOSID to MOSI2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DATA BOUT DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | LSi                       | LAS LOR OF                | t <sub>rest</sub>                                               | MSB IN                    |

| 38-35         | RSPI Timing<br>(Slave,                                | MOSID to MOSI2 Imput  Correction:  SSLD0, SSL10, SSL20, Imput  RSPCKD to RSPCK2 CPOL = 0 Imput  RSPCKD to RSPCK2 CPOL = 1 Imput  MISCO to MISO2 Output  MOSID to MOSI2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SBOUT DAT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | l <sub>oo</sub>           | B OUT                     | t <sub>iact</sub>                                               | MSB CUT                   |

| 38-35         | RSPI Timing<br>(Slave,                                | MOSID to MOSI2 Imput  Correction:  SSLD0, SSL10, SSL20, Imput  RSPCKD to RSPCK2 CPOL = 0 Imput  RSPCKD to RSPCK2 CPOL = 1 Imput  MISCO to MISO2 Output  MOSID to MOSI2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SBOUT DAT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | l <sub>oo</sub>           | B OUT                     | t <sub>iact</sub>                                               | MSB CUT                   |

| 38-35         | RSPI Timing<br>(Slave,                                | COrrection:  SSLD0, SSL10, SSL20, Input  RSPCK0 to RSPCK2 CPCL = 0 Input  MISO0 to MISO2 Output  MOSID to MOSI2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SBOUT DAT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | l <sub>oo</sub>           | B OUT                     | t <sub>iact</sub>                                               | MSB CUT                   |

| 00 00         |                                                       | SSL00, SSL10, SSL20, Input RSPCK0 to RSPCK2 CPOL = 0 Input RSPCK0 to RSPCK2 CPOL = 1 Input MISO0 to MISO2 Output  MOSID to MOSI2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SB OUT DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LS                        | B OUT COR For             | t <sub>iact</sub>                                               | MSB CUT                   |

|               | CPHA = *0*)                                           | SSL00, SSL10, SSL20, Input RSPCK0 to RSPCK2 CPOL = 0 Input RSPCK0 to RSPCK2 CPOL = 1 Input MISO0 to MISO2 Output  MOSID to MOSI2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SB OUT DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LS                        | B OUT COR For             | t <sub>iact</sub>                                               | MSB CUT                   |

|               |                                                       | SSL10, SSL20, Input  RSPCKD to RSPCK2 CPCL = 0 Input  RSPCKD to RSPCK2 CPCL = 1 Input  MISOD to MISO2 Output  MOSID to MOSI2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SB OUT DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LS                        | B OUT COR For             | t <sub>iact</sub>                                               | MSB CUT                   |

|               |                                                       | RSPCKD to RSPCK2 CPOL = 0 Input RSPCKD to RSPCK2 CPOL = 1 Input MISOD to MISO2 Output  MOSID to MOSI2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SB OUT DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LS                        | B OUT COR For             | t <sub>iact</sub>                                               | MSB CUT                   |

|               |                                                       | CPCL - 0 Input  RSPCK0 to RSPCK2 CPCL - 1 Input  MISO0 to MISO2 Output  MOSID to MOSI2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SB OUT DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LS                        | tor, tor                  | t <sub>iact</sub>                                               | MSB CUT                   |

|               |                                                       | RSPCKD to RSPCK2 CPCL - 1 Input  MISCO to MISO2 Output  MOSID to MOSI2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SB OUT DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LS                        | tor, tor                  | 1                                                               |                           |

|               |                                                       | MOSID to MOSI2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SB OUT DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LS                        | tor, tor                  | 1                                                               |                           |

|               |                                                       | MISO0 to MISO2 Output  MOSID to MOSI2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SB OUT DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LS                        | tor, tor                  | 1                                                               |                           |

|               |                                                       | MISO0 to MISO2<br>Output  MOSID to MOSI2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SB OUT DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LS                        | tor, tor                  | MSB IN                                                          |                           |