PWM Doubler with Phase Shedding Function and Output Monitoring Feature

概览

简介

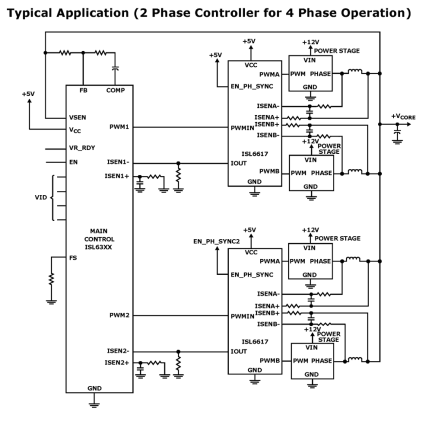

The ISL6617 utilizes Intersil's proprietary Phase Doubler scheme to modulate two-phase power trains with single PWM input. It doubles the number of phases that Intersil's multi-phase controllers ISL63xx can support. When the enable pin (EN_PH_SYNC) is pulled low, the PWM input is pulled high. This simplifies the phase shedding implementation for some Intersil controllers (VR10, VR11, VR11. 1, and VR12 family) that can disable the respective and higher phase(s) by pulling the respective PWM line high. The ISL6617 is designed to minimize the number of analog signals that interface between the controller and drivers in high phase count scalable applications. The common COMP signal, which is usually seen in conventional cascaded configuration, is not required; this improves noise immunity and simplifies the layout. Furthermore, the ISL6617 provides low part count and low cost advantage over the conventional cascaded technique. By cascading the ISL6617 with another ISL6617 or ISL6611A, it can quadruple the number of phases that Intersil's multi-phase controllers ISL63xx can support. The ISL6617 also features Tri-State input and outputs that recognize a high-impedance state, working together with Intersil multiphase PWM controllers and driver stages to prevent negative transients on the controlled output voltage when operation is suspended. This feature eliminates the need for the schottky diode that may be utilized in a power system to protect the load from excessive negative output voltage damage.

特性

- Proprietary Phase Doubler scheme with Phase Shedding Function (Patent Pending)

- Enhanced Light to Full Load Efficiency

- Double or Quadruple Phase Count

- Patented Current Balancing with DCR Current Sensing and Adjustable Gain

- Current Monitoring Output (IOUT) to Simplify System Interface and Layout

- Triple-Level Enable Input for Mode Selection

- Dual PWM Output Drives for Two Synchronous Rectified Bridges with Single PWM Input

- Channel Synchronization and Two Interleaving Options

- Tri-State PWM Input and Outputs for Output Stage Shutdown

- Phase Enable Input and PWM Forced High Output to Interface with Intersil's Controller for Phase Shedding

- Overvoltage Protection

- Dual Flat No-Lead (DFN) Package

- Near Chip-Scale Package Footprint; Improves PCB Utilization, Thinner Profile

- Pb-Free (RoHS Compliant)

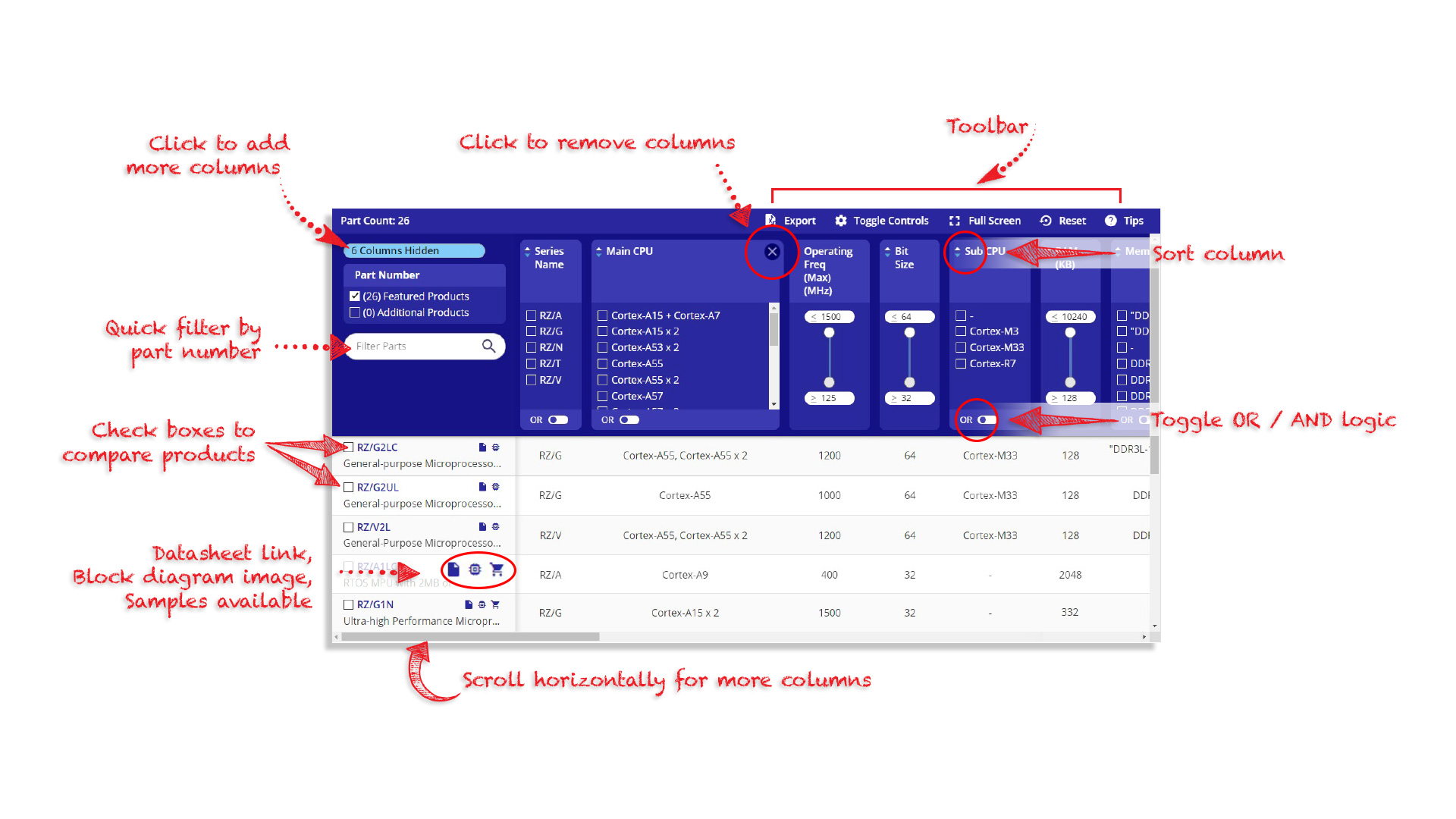

产品对比

应用

应用

- High Current Low Voltage DC/DC Converters

- High Frequency and High Efficiency VRM and VRD

- High Phase Count and Phase Shedding Applications

- 5V PWM Input Integrated Power Stage or DrMOS

文档

|

|

|

|

|---|---|---|

| 类型 | 文档标题 | 日期 |

| 数据手册 | PDF 884 KB | |

| 手册 | PDF 8.73 MB | |

| 产品变更通告 | PDF 326 KB | |

| 产品变更通告 | PDF 158 KB | |

| 其他 | PDF 293 KB | |

| 产品变更通告 | PDF 248 KB | |

| 应用文档 | PDF 509 KB | |

| 应用文档 | PDF 397 KB | |

| 应用文档 | PDF 576 KB | |

9 items

|

||

设计和开发

模型

ECAD 模块

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.