半導体業界において、技術革新の代表とも言えるRISC-V ISAの人気が急上昇しています。RISC-Vは設計者にこれまでにないフレキシビリティを提供し、組み込みシステムの現状をゆっくりではあるかもしれませんが着実に変革していくでしょう。ルネサスはこれまでに、Andes Technology社が開発したCPUコアを搭載した音声制御およびモータ制御用の32ビットASSPを発売し、RISC-Vテクノロジをリードしてきました。

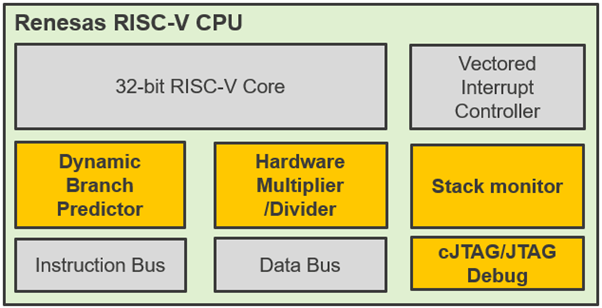

次のステップとして、ルネサスはRISC-V CPUコアを初めて自社開発しました。 そのCPUのブロック図は次の通りです。

このRISC-V CPUにはどんな特長があるのでしょうか?まず、このCPUは高いフレキシビリティを有し、さまざまなアプリケーションに適応することができ、マイコンのメインCPUとして、あるいはSoCに内蔵するサブコントローラや、特定用途向け汎用製品(ASSP)のコアとして採用することができます。次に、省スペース設計をしたことから、面積が小さく、コストへの影響が小さいというメリットがあり、動作電流とスタンバイ時のリーク電流も低減しています。加えて、小型の組み込みシステムをターゲットにしつつも、高い演算性能を実現し、昨今の組み込みアプリケーションのニーズに応えます。

それでは具体的なCPUの機能に目を向けてみましょう。CPUの設計者はRV32の'I'または'E'オプションを選択し、利用可能な汎用レジスタの数を最適化することができます。これは例えば、複雑なスタックやアプリケーションを処理する必要がなく、特定のペリフェラルの操作や単調なタスクに特化した小さなサブシステムの場合に有効な手法です。また、RISC-V ISAにおいて、標準のISAを使用するよりも優れた、あるいは効率的で特定の機能をサポートとするいくつかの「拡張(extension)」がオプションとして準備されています。今回ルネサスはそのうちのいくつかを実装することにしました。以下が実装したextensionの説明です。

- M extension - 乗算(および除算)演算を高速化・最適化し、ハードウェア乗算器とハードウェア除算器を活用して最速の命令実行を実現します。

- A extension - アトミックアクセス命令をサポートし、RTOSベースのシステムで一般的な並行処理や排他アクセス管理の基盤として役立ちます。

- C extension - 16ビットのみでエンコードされる圧縮命令を定義しており、一般的で頻繁に使用される命令のメモリ領域の節約に貢献します。

- B extension - ビット操作のための複数の命令を追加します。ビットフィールドでエンコードされた値に基づいて周辺レジスタ、プロトコル、データ構造を管理するアプリケーションでは、汎用命令で構成される機能を1つの専用命令で置き換えることができます。

これはRISC-V ISAコンセプトの優れた点であり、設計者がターゲットとするユースケースに応じてプロセッサに含める要素を選択できるように構築されています。これは設計者にとってもユーザにとっても、本当に実装したいものだけに「対価を支払う」ようにする非常に良い方法といえます。

また、アプリケーションソフトウェアの信頼性を高めるために、スタックモニタレジスタが追加されています。これは、スタックメモリオーバーフローを検出し、防止するのに非常に便利です。スタックメモリオーバーフ ローは、実際のアプリケーション実行時にはよくある問題ですが、テストの段階では発見しにくいことがあります。このような問題は、システムの完全性を損ない、実行時にアプリケーションの誤動作を発生させる可能性があります。こういったモニタ機能は予期せぬイベントを制御するための基本的なセーフティネットであり、システムの品質向上に役立ちます。

最も単純な制御システムにおいても、一般的にアプリケーションにサービスを提供し、いつでも適切な処理ルーチンを呼び出すために、いくつかの判断を下すパスを管理しなければなりません。あるいは、データ・バッファ上でいくつかの繰り返し計算を実行することもあるでしょう。つまり、実装されたコードは、コンテキストによってプログラムの流れが変わる可能性のある、分岐、ループ、および判断ポイントで構成されており、CPUにはこのような処理を効率化するための動的分岐予測ユニットが搭載されています。分岐予測ユニットの役割は、コードの挙動を観察し、制御ループ中に実行される可能性の高い次の命令を動的に推測することです。これがうまく機能すると、次に実行のためにフェッチする命令を選択する際に正しい推測を行うことで、平均的なコード実行スループットを向上させることができます。

デバッグ機能に関するアップデートもあります。標準的なJTAGの他に、CPUは2線式のコンパクトなJTAGデバッグインタフェースもサポートしており、ユーザアプリケーションピンの数が制限される小型パッケージ品に非常に適しています。CPUには複数のパフォーマンスモニタレジスタも実装されており、実行されたコードのランタイム動作を簡単にベンチマークすることができます。

組み込みシステムのもう1つの重要な要素は、イベントに対する応答性です。マイコンレベルの組み込みデバイスには、ハードリアルタイム動作が義務付けられています。応答レイテンシが低い場合、アプリケーションがより多くの同時イベントに対応できたり、適切なタスク処理を保証するために適切な時間的マージンを確保できたり、あるいはCPU速度を絞り込んで消費電力を削減できたりと、さまざまな利点があります。ルネサスは、アーキテクチャレベルでこのレイテンシを改善し、開発者がその利点を享受できるように、レジスタバンク機能を追加しました。CPUレジスタのバックアップとリストアが可能で、割り込み処理時や、組み込みRTOSがイベントに応じて現在実行中のスレッドをスワップアウトする場合に、コンテキストスイッチを高速化することができます。また、アプリケーションのベンチマークや動作の検証を行う開発者をさらに支援するために、効率的でコンパクトな命令トレースユニットも用意されています。

本ブログでは、ここまでCPUの機能詳細について紹介しましたが、このような新技術に基づく実際の製品を評価・開発し、生産するためには、他に何を考慮すべきでしょうか。それはまず、ソリューションの開発と展開に必要なインフラの一部として、適切なツールチェーンが利用可能であることです。お客様は、コンフィギュレーション・プラグインを備えたルネサスの統合開発環境 e2 studioか、RISC-Vベースのマイコンをサポートする主要なサードパーティのIDEのいずれかを利用できます。次に、CPUの実装が単なるシミュレーションではなく、当然ながら実際のシリコン製品として機能が検証されていることです。最初のベンチマークでは、オープンソースのLLVMベースのコンパイラツールチェーンを使用しながら、3.27 CoreMark/MHzという高い性能を示し、市場で入手可能な同等のアーキテクチャを凌駕しました。この優れたスコアの詳細については、2024年の初頭に先頭製品が発表され次第、EEMBCのウェブサイトに性能データが掲載されますのでご覧ください。また多くの人が注目しているように、自社のコンパイラの性能が検証されれば、よりよい性能が引き出されると考えています。

この新しいCPUは、ルネサスの既存のマイコンのポートフォリオに追加的かつ補完的な選択肢を生み出す、次のステップへの要となるものです。ルネサスは、革新的で成長を続けているRISC-Vアーキテクチャの搭載により、幅広いソリューションでお客様をサポートしてまいります。

詳細はrenesas.com/risc-vをご覧ください。