-

-

-

設計リソース

- 設計・開発

- 注目の設計ツール

- パートナー

- コンテンツ&トレーニング

-

サポート

-

サンプル&ご購入

-

ルネサスサイトからの直接購入

便利なルネサスからの直接購入を選択できるようになりました。

- 購入関連情報

-

ルネサスサイトからの直接購入

概要

説明

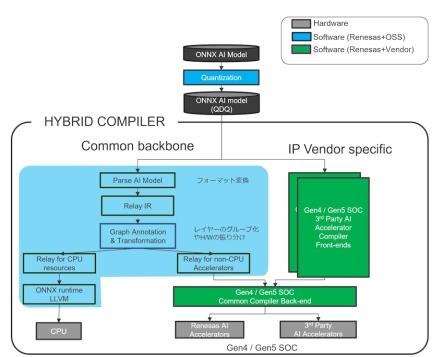

DNN compilerはSoC毎に専用であることが多く、世代にわたって継続的に設計されるお客様にとって導入の障壁になっていました。

DNN compilerはニューラルネットワークのグラフ構成を分析しグラフを圧縮・最適化するフロントエンド部と、ハードウェアの構造を元に最適な演算順序を決定しハードウェアの命令を生成するバックエンド部に分かれます。

我々Renesasは何世代もの設計経験から、このフロントエンド部はSoCの世代によらず非常に似た動作をしていることに着目しました。

そこで機能拡張に優れたOSSのTVMをフロントエンドとしてCommon Backboneに採用し、SoC毎に設計しているバックエンドとTVMを結合させることで、世代を超えて同じツールが使えるようにしていきます。

我々は従来通りの品質保証されたSoC専用のコンパイラと並行して、共通のバックエンドを利用して、TVMでもご利用出来るツールをご提供していきます。我々はこのセットをHybrid Compilerと名付けました。

2024年1月から順次リリース予定です。

特長

- Hybrid Compiler

- Open-Source Software のAI compilerを共通バッグボーン

- 品質保証されたIP vendor 固有のAI compiler

ターゲットデバイス

設計・開発

関連ページ

関連ページ

| Software title

|

Software type

|

会社名

|

|---|---|---|

| AI Workbench ルネサスR-Car SoCプラットフォームのAIモデルやアプリケーションの開発・検証が可能なクラウド環境へウェブブラウザ経由でアクセスできます。

|

Software Package | ルネサス |

1 item

|

||